# **High Voltage Multi-Topology LED Driver**

## **General Description**

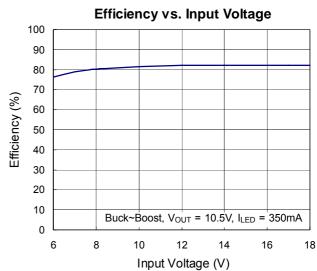

The RT8450/B is a current mode PWM regulator for LED driving applications. With an 1.5A switch on board and wide input (4.5V to 40V) and/or output (up to 50V)ranges the RT8450/B can operate in any of the three common topologies: Buck, Boost or Buck-Boost.

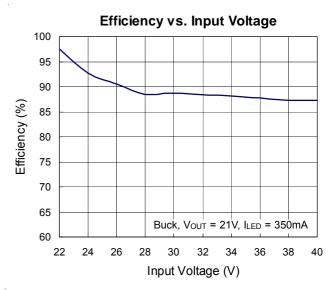

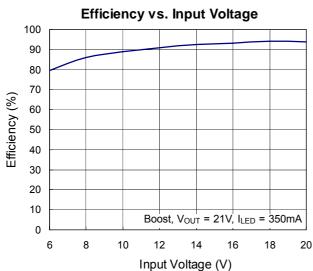

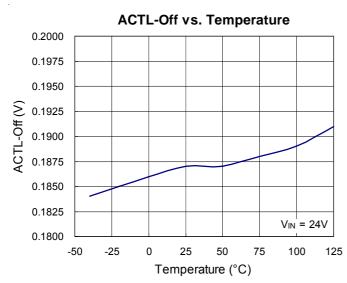

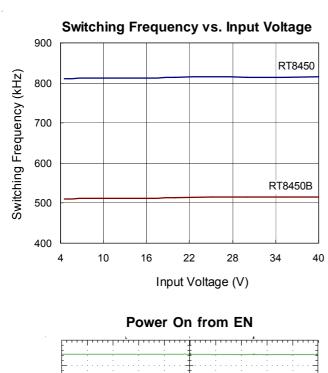

With 800k/500kHz operating frequency, the external PWM inductor and input/output capacitors can all be small. High efficiency is achieved by a 190mV current sensing.

Dimming can be done either analog or PWM signal. An unique built-in clampping comparator and filtering resistor allow easy low noise analog dimming conversion from PWM signal with only one external capacitor.

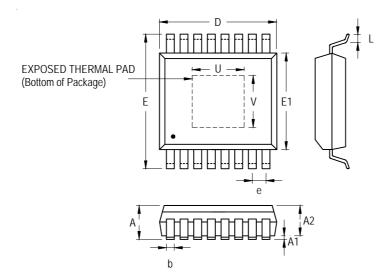

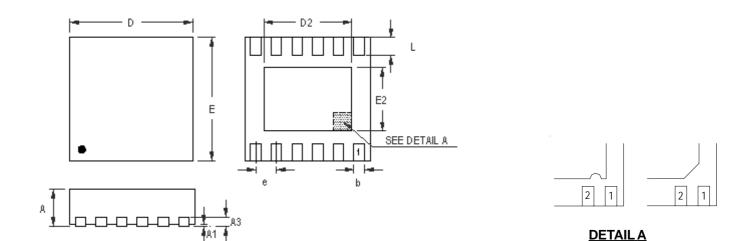

The RT8450/B is available in a TSSOP-16 (Exposed Pad) and WDFN-12L 3x3 packages.

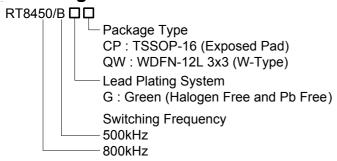

## **Ordering Information**

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

#### **Features**

- High Voltage: VIN Up to 40V, VOUT Up to 50V

- 1.5A Switch Current

- Buck, Boost or Buck-Boost Operation

- Current Mode PWM with 800kHz (RT8450) and 500kHz (RT8450B) Switching Frenquency

- Easy Dimming: Analog, PWM Digital or PWM Converting to Analog with One External Capacitor

- Programmable Soft-Start to Avoid Inrush Current

- Programmable Over Voltage Protection to Limit Output Voltage

- V<sub>IN</sub> Under Voltage Lockout and Thermal Shutdown

- RoHS Compliant and Halogen Free

## **Applications**

- GPS, Portable DVD Backlight

- · Desk Lights and Room Lighting

- Industrial Display Backlight

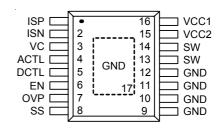

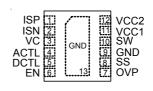

## **Pin Configurations**

(TOP VIEW)

TSSOP-16 (Exposed Pad)

WDFN-12L 3x3

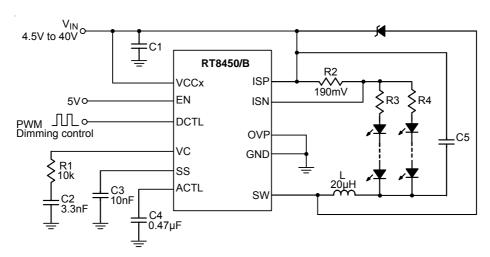

# **Typical Application Circuit**

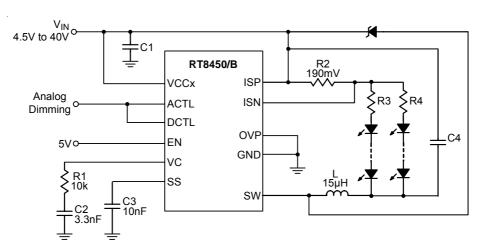

Figure 1. PWM to Analog Dimming Buck Configuration

Figure 2. Analog Dimming Buck Configuration

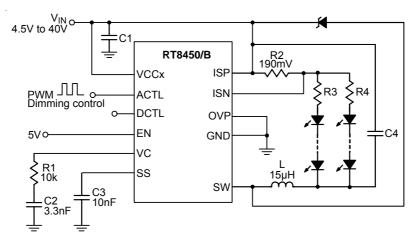

Figure 3. PWM Dimming Buck Configuration Through ACTL Pin

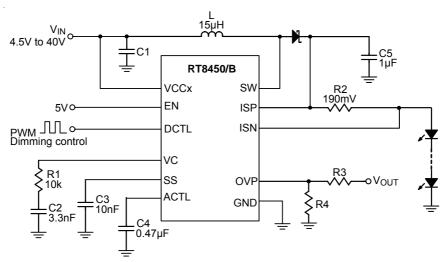

Figure 4. PWM to Analog Dimming Boost Configuration

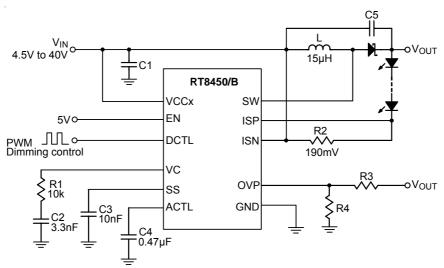

Figure 5. PWM to Analog Dimming Buck-Boost Configuration

# **Functional Pin Description**

| Pin No.                   |                 | Pin Name | Pin Function                                                                                                                                                                                                    |  |  |

|---------------------------|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TSSOP-16<br>(Exposed Pad) | \M \LK  49  9v9 |          |                                                                                                                                                                                                                 |  |  |

| 1                         | 1               | ISP      | Current Sense Amplifier Positive Input.                                                                                                                                                                         |  |  |

| 2                         | 2               | ISN      | Current Sense Amplifier Negative Input. Voltage threshold between ISP and ISN is 190mV.                                                                                                                         |  |  |

| 3                         | 3               | VC       | PWM Boost Converter Loop Compensation Node.                                                                                                                                                                     |  |  |

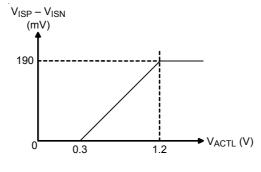

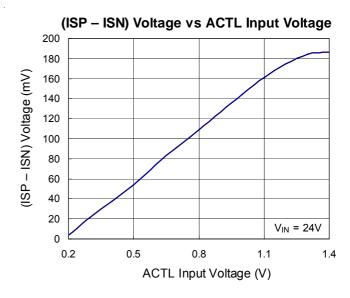

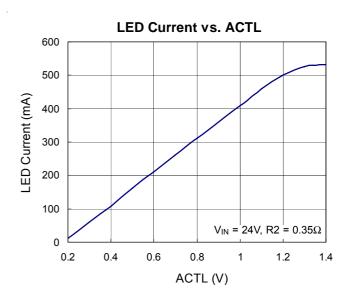

| 4                         | 4               | ACTL     | Analog Dimming Control. Effective programming range is between 0.3V and 1.2V.                                                                                                                                   |  |  |

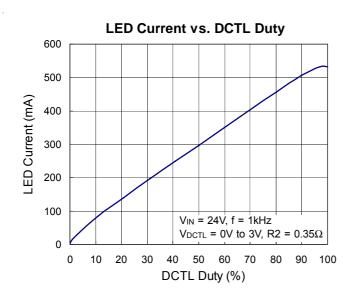

| 5                         | 5               | DCTL     | By Adding a $0.47\mu F$ Filtering Capacitor on ACTL Pin, the PWM dimming signal on DCTL pin will be averaged and converted into analog dimming signal on ACTL pin. $V_{ACTL}$ = 1.2V x PWM dimming duty cycle . |  |  |

| 6                         | 6               | EN       | Chip Enable (Active High), when low chip is in shutdown mode.                                                                                                                                                   |  |  |

| 7                         | 7               | OVP      | Over voltage protection. PWM boost converter turns off when V <sub>OVP</sub> goes higher than 1.2V.                                                                                                             |  |  |

|                           | To be continued |          |                                                                                                                                                                                                                 |  |  |

| Pin No.                            |                        |          |                                                                                                                                                                                                            |  |

|------------------------------------|------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TSSOP-16<br>(Exposed Pad)          | WDFN-12L 3x3           | Pin Name | Pin Function                                                                                                                                                                                               |  |

| 8                                  | 8                      | SS       | Soft-Start Pin, a capacitor of at least 10nF is required for soft-start.                                                                                                                                   |  |

| 9, 10, 11, 12,<br>17 (Exposed Pad) | 9,<br>13 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                |  |

| 13, 14                             | 10                     | SW       | PWM Boost Converter Switch Node.                                                                                                                                                                           |  |

| 15                                 | 12                     | VCC2     | Bipolar Power Switch Base Current Supply. VCC2 can be connected either to VCC1 or to a separate lower voltage, as low as 3V, for better system efficiency and/or heat concern. A good bypass is necessary. |  |

| 16                                 | 11                     | VCC1     | Power Supply of the Chip. For good bypass, a low ESR capacitor is required.                                                                                                                                |  |

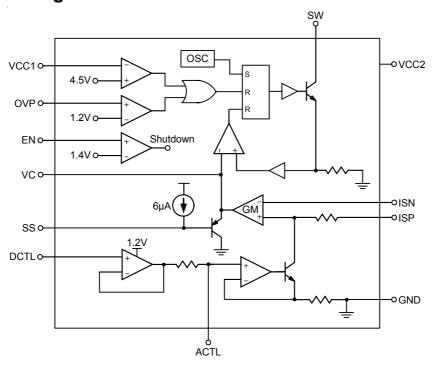

# **Function Block Diagram**

Figure 6

## Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, V <sub>CC1</sub> , V <sub>CC2</sub>                   | 45V         |

|-----------------------------------------------------------------------------|-------------|

| SW Pin Voltage at Switching Off, ISP, ISN                                   | 55V         |

| DCTL, ACTL, OVP Pin Voltage                                                 | 8V (Note 2) |

| • EN Pin Voltage                                                            | 20V         |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |             |

| TSSOP-16                                                                    | 2.66W       |

| WDFN-12L 3x3                                                                | 1.667W      |

| Package Thermal Resistance (Note 3)                                         |             |

| TSSOP-16, θ <sub>JA</sub>                                                   | 47°C/W      |

| WDFN-12L 3x3, $\theta_{JA}$                                                 | 60°C/W      |

| WDFN-12L 3x3, $\theta_{JC}$                                                 | 8.2°C/W     |

| Junction Temperature                                                        | 150°C       |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C       |

| Storage Temperature Range                                                   |             |

| • ESD Susceptibility (Note 4)                                               |             |

| HBM (Human Body Mode)                                                       | 2kV         |

| MM (Machine Mode)                                                           | 200V        |

|                                                                             |             |

## **Recommended Operating Conditions** (Note 5)

### **Electrical Characteristics**

( $V_{CC1}$  =  $V_{CC2}$  = 12V, No Load on any Output,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                                              | Symbol                 | Test Conditions                          | Min | Тур                 | Max                 | Unit |  |

|--------------------------------------------------------|------------------------|------------------------------------------|-----|---------------------|---------------------|------|--|

| Overall                                                |                        |                                          |     |                     |                     |      |  |

| Supply Voltage                                         | V <sub>CC1</sub>       |                                          | 4.5 |                     | 40                  | V    |  |

| Supply Voltage VCC2 for Switch Base Drive              | V <sub>CC2</sub>       |                                          | 3   |                     | 40                  | ٧    |  |

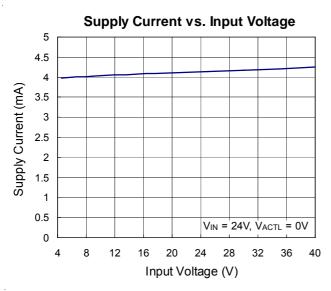

| Supply Current                                         | I <sub>VCC1</sub>      | VC ≤ 0.4V (Switching off)                |     | 4                   | 6                   | mA   |  |

| Supply Current                                         | lvcc2                  | $V_{CC1} = V_{CC2} = 24V, I_{SW} \le 1A$ | -   | I <sub>SW</sub> /70 | I <sub>SW</sub> /40 | Α    |  |

| Shutdown Current                                       | I <sub>SHDN_VCC1</sub> | $V_{EN} \leq 0.7V$                       |     | 12                  |                     | μΑ   |  |

| Shutdown Threshold                                     | V <sub>EN</sub>        |                                          | 1   | 1.4                 |                     | ٧    |  |

| EN Input Current                                       |                        | V <sub>EN</sub> = 3V                     | 1   |                     | 0.5                 | μΑ   |  |

| Current Sense Amplifier                                |                        |                                          |     |                     |                     |      |  |

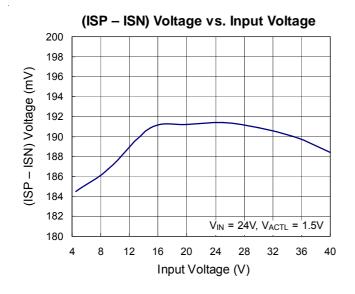

| Input Threshold (V <sub>ISP</sub> – V <sub>ISN</sub> ) |                        | $4.5V \le common mode \le 50V$           | 170 | 190                 | 210                 | mV   |  |

| Input Current                                          | I <sub>ISP</sub>       | V <sub>ISP</sub> = 24V                   | 1   | 100                 |                     | μА   |  |

| Input Current                                          | I <sub>ISN</sub>       | V <sub>ISN</sub> = 24V                   | 1   | 40                  |                     | μΑ   |  |

| Output Current                                         | I <sub>VC</sub>        | 2.4V > VC > 0.2V                         | -   | ±20                 |                     | μΑ   |  |

| VC Threshold for PWM Switch Off                        |                        |                                          |     | 0.7                 |                     | V    |  |

To be continued

| Parameter                    | Symbol              | Test Conditions              | Min  | Тур | Max  | Unit |  |

|------------------------------|---------------------|------------------------------|------|-----|------|------|--|

| LED Dimming                  |                     |                              |      |     |      |      |  |

| Analog Dimming ACTL Pin      | 1                   | 0.21/ <1/ < 1.21/            |      |     | 3    |      |  |

| Input Current                | I <sub>ACTL</sub>   | $0.3V \le V_{ACTL} \le 1.2V$ |      |     | 3    | μА   |  |

| LED Current Off Threshold at | V                   |                              |      | 0.2 |      | V    |  |

| ACTL                         | V <sub>ACTL</sub>   |                              |      | 0.2 |      | V    |  |

| DCTL Input Current           | I <sub>DCTL</sub>   | $0.3V \le V_{DCTL} \le 6V$   |      |     | 0.5  | μΑ   |  |

| PWM BOOST Converter          |                     |                              |      |     |      |      |  |

| Switching Frequency          | form                | RT8450                       | 600  | 800 | 1000 | kHz  |  |

| Switching Frequency          | f <sub>SW</sub>     | RT8450B                      | 400  | 500 | 600  | kHz  |  |

| Maximum Duty Cycle           | _                   | RT8450                       |      | 80  |      | %    |  |

| (Note 6)                     | D <sub>MAX</sub>    | RT8450B                      |      | 86  | _    |      |  |

| Minimum on Time              |                     |                              |      | 250 | _    | ns   |  |

| SW On-Voltage                | $V_{SW}$            | I <sub>SW</sub> = 0.5A       |      | 0.4 | _    | V    |  |

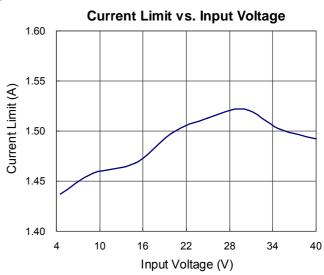

| SW Current Limit             | I <sub>LIM_SW</sub> |                              | 1.25 | 1.5 |      | Α    |  |

| OVP and Soft Start           |                     |                              |      |     |      |      |  |

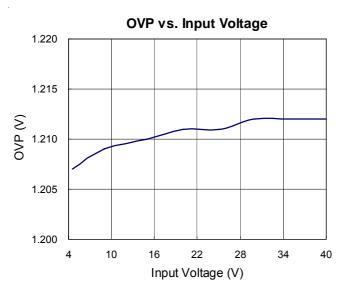

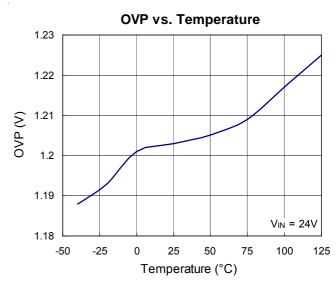

| OVP Threshold                | V <sub>OVP</sub>    |                              |      | 1.2 | -    | V    |  |

| OVP Input Current            | I <sub>OVP</sub>    | $0.7V \le V_{OVP} \le 1.5V$  |      |     | 0.5  | μА   |  |

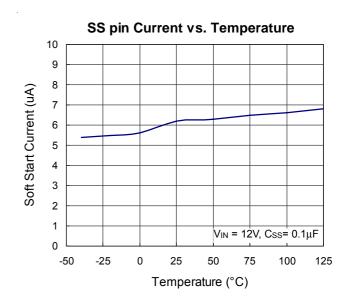

| Soft Start SS Pin Current    | I <sub>SS</sub>     | $V_{SS} \le 2V$              |      | 6   | -    | μА   |  |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Note 2. If connected with a  $20k\Omega$  serial resistor, ACTL and DCTL can go up to 40V.

- Note 3.  $\theta_{JA}$  is measured in the natural convection at  $T_A$  = 25°C on a high effective four layers thermal conductivity test board of JEDEC 51-7 thermal measurement standard.

- Note 4. Devices are ESD sensitive. Handling precaution is recommended.

- Note 5. The device is not guaranteed to function outside its operating conditions.

- **Note 6.** When the natural maximum duty cycle of the switching frequency is reached, the switching cycle will be skipped (not reset) as the operating condition requires to effectively stretch and achieve higher on cycle than the natural maximum duty cycle set by the switching frequency.

www.richtek.com DS8450/B-04 June 2011

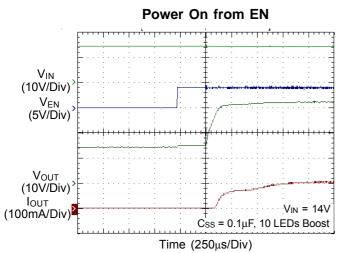

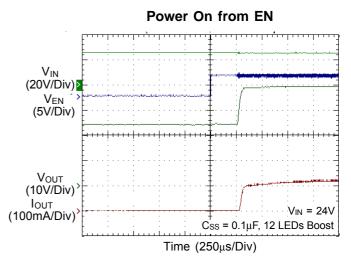

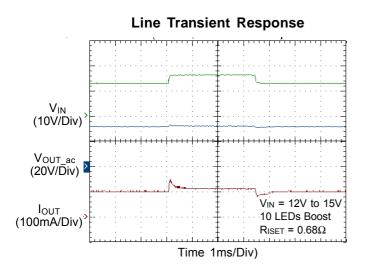

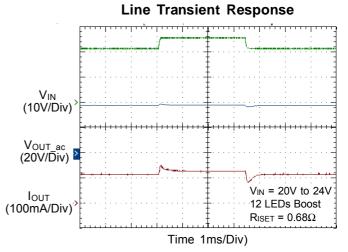

## **Typical Operating Characteristics**

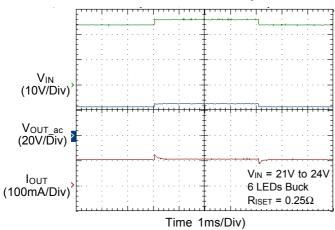

#### Line Transient Response

## **Application Information**

The RT8450/B is specifically designed to be operated in buck, buck -boost and boost converter applications. This device uses a fixed frequency, current mode control scheme to provide excellent line and load regulation. The control loop has a current sense amplifier to sense the voltage between the ISP and ISN pins and provides an output voltage at the VC pin. A PWM comparator then turns off the internal power switch when the sensed power switch current exceeds the compensated VC pin voltage. The power switch will not reset by the oscillator clock in each cycle. If the comparator does not turn off the switch in a cycle, the power switch is on for more than a full switching period until the comparator is tripped. In this manner, the programmed voltage across the sense resistor is regulated by the control loop.

The current through the sense resistor is set by the programmed voltage and the sense resistance. The voltage across the sense resistor can be programmed by either the analog or PWM signals at the ACTL pin, or the PWM signal at the DCTL pin.

The protection schemes in the RT8450/B include over temperature, input voltage under voltage, output voltage over-voltage, and switch current limit.

#### **Loop Compensation**

The RT8450/B has an external compensation pin (VC) allowing the loop response optimized for specific application. An external resistor in series with a capacitor is connected from the VC pin to GND to provide a pole and a zero for proper loop compensation. The recommended compensation resistance and capacitance for the RT8450/B are 10k and 3.3nF.

#### Soft-Start

The soft-start of the RT8450/B can be achieved by connecting a capacitor from the SS pin to GND. The built-in soft-start circuit reduces the start-up current spike and output voltage overshoot. The soft-start time is determined by the external capacitor charged by an internal  $6\mu A$  constant charging current. The SS pin directly limits the rate of voltage rise on the VC pin, which in turn limits the peak switch current. The value of the soft-start capacitor is user-defined to satisfy the designer's requirement.

#### **LED Current Setting**

The LED current could be calculated by the following equation:

$$I_{LED,MAX} = \frac{V(ISP-ISN)}{R2}$$

Where V(ISP-ISN) is the voltage between ISP and ISN (190mV typ. if ACTL or DCTL dimming is not applied) and the R2 is the resister between ISP and ISN.

#### **Brightness / Dimming Control**

The RT8450/B features both analog and digital dimming control. Analog dimming is linearly controlled by an external voltage ( $0.3V < V_{ACTL} < 1.2V$ ). With an on-chip output clamping amplifier and a resistor, PWM dimming signal fed at DCTL pin can be easily low-pass filtered to an analog dimming signal with one external capacitor from ACTL pin to GND for noise-free PWM dimming. A very high contrast ratio true digital PWM dimming can be achieved by driving ACTL pin with a PWM signal from 100Hz to 10kHz.

#### **Output Over Voltage Setting**

The RT8450/B is equipped with over voltage protection (OVP) function. When the voltage at OVP pin exceeds a threshold of approximately1.2V, the power switch is turned off. The power switch can be turned on again once the voltage at OVP pin drops below 1.2V.

For the Boost Application, the output voltage could be clamped at a certain voltage level. The OVP voltage can be set by the following equation:

$$V_{OUT,OVP} = 1.2 \text{ x } (1 + \frac{R3}{R4})$$

Where R3 and R4 are the voltage divider from  $V_{\text{OUT}}$  to GND with the divider center node connected to OVP pin.

#### **Current-Limit Protection**

The RT8450/B can limit the peak switch current by the internal over current protection feature. In normal operation, the power switch is turned off when the switch current hits the loop-set value. The over current protection function will turn off the power switch independent of the loop control when the peak switch current reaches around 1.5A.

#### **Over Temperature Protection**

The RT8450/B has over temperature protection (OTP) function to prevent the excessive power dissipation from overheating. The OTP function will shut down switching operation when the die junction temperature exceeds 150°C. The chip will automatically start to switch again when the die junction temperature cools off.

#### **Inductor Selection**

Choose an inductor that can handle the necessary peak current without saturating, and ensure that the inductor has a low DCR (copper-wire resistance) to minimize  $I^2R$  power losses. A 4.7 $\mu H$  to  $10\mu H$  inductor will meet the demand for most of the RT8450/B applications. Inductor manufacturers specify the maximum current rating as the current where the inductance falls to certain percentage of its nominal value typically 65%.

In Boost application where the transition between discontinuous and continuous modes occurs, the value of the required output inductor (L), can be approximated by the following equation:

$$L = \frac{V_{OUT} \times D \times (1-D)^2}{2 \times I_{OUT} \times f}$$

The Duty Cycle (D) could be calculated as follows:

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

Where  $V_{OUT}$  = maximum output voltage.

$V_{IN}$  = minimum input voltage.

f = operating frequency.

$I_{OUT}$  = sum of current from all LED strings.

The boost converter operates in discontinuous mode over the entire input voltage range can have inductor value L1 less than the calculated value L by the formula above. With an inductance value L2 greater than L, the converter will operate in continuous mode at the minimum input voltage and maybe operate in discontinuous mode at higher voltages.

The inductor must be selected with a saturation current rating greater than the peak current provided by the following equation:

$$I_{PEAK} = \frac{V_{OUT} \times I_{LED}}{\eta \times V_{IN}} + \frac{V_{IN} \times D \times T}{2 \times L}$$

Where ç is the efficiency of the power converter.

#### Schottky Diode Selection

The Schottky diode, with low forward voltage drop and fast switching speed, is necessary for the RT8450/B applications. In addition, power dissipation, reverse voltage rating and pulsating peak current are the important parameters of the Schottky diode that must be considered. Choose a suitable Schottky diode whose reverse voltage rating is greater than the maximum output voltage. The diode's average current rating must exceed the average output current. The diode conducts current only when the power switch is turned off (typically less than 50% duty cycle).

#### **Capacitor Selection**

The input capacitor reduces current spikes from the input supply and minimizes noise injection to the converter. For most RT8450/B applications, a  $4.7\mu F$  ceramic capacitor is sufficient. A value higher or lower may be used depending on the noise level from the input supply and the input current to the converter.

In Boost Application, the output capacitor is typically a ceramic capacitor and is selected based on the output voltage ripple requirements. The minimum value of the output capacitor  $C_{\text{OUT}}$  is approximately given by the following equation :

$$C_{OUT} = \frac{I_{LED} \times D \times T}{V_{RIPPLE}}$$

#### **Layout Consideration**

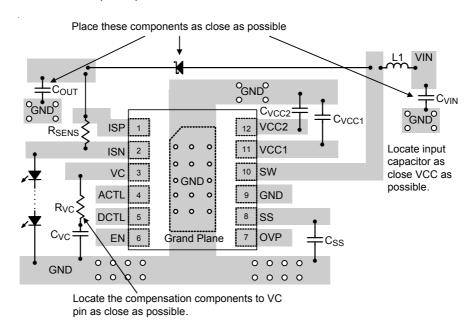

PCB layout is very important to design power switching converter circuits. Some recommended layout guidelines are suggested as follows:

- ➤ The power components L1, D1, C<sub>VIN</sub>, and C<sub>OUT</sub> must be placed as close to each other as possible to reduce the ac current loop area. The PCB trace between power components must be as short and wide as possible due to large current flow through these traces during operation.

- Place L1 and D1 connected to SW pin as close as possible. The trace should be as short and wide as possible.

- ➤ The input capacitors C<sub>VCC1</sub> and C<sub>VCC2</sub> must be placed as close to VCC1 and VCC2 pin as possible.

Place the compensation components to the VC pin as close as possible to avoid noise pick up.

Figure 7. PCB Layout Guide

# **Outline Dimension**

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min          | Max           | Min                  | Max   |  |

| А      | 1.000        | 1.200         | 0.039                | 0.047 |  |

| A1     | 0.000        | 0.150         | 0.000                | 0.006 |  |

| A2     | 0.800        | 1.050         | 0.031                | 0.041 |  |

| b      | 0.190        | 0.300         | 0.007                | 0.012 |  |

| D      | 4.900        | 5.100         | 0.193                | 0.201 |  |

| е      | 0.65         |               | 0.026                |       |  |

| Е      | 6.300        | 6.500         | 0.248                | 0.256 |  |

| E1     | 4.300        | 4.500         | 0.169                | 0.177 |  |

| L      | 0.450        | 0.750         | 0.018                | 0.030 |  |

| U      | 2.000        | 3.000         | 0.079                | 0.118 |  |

| V      | 2.000        | 3.000         | 0.079                | 0.118 |  |

16-Lead TSSOP (Exposed Pad) Plastic Package

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

Pin #1 ID and Tie Bar Mark Options

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| Α      | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b      | 0.150        | 0.250         | 0.006                | 0.010 |  |

| D      | 2.950        | 3.050         | 0.116                | 0.120 |  |

| D2     | 2.300        | 2.650         | 0.091                | 0.104 |  |

| Е      | 2.950        | 3.050         | 0.116                | 0.120 |  |

| E2     | 1.400        | 1.750         | 0.055                | 0.069 |  |

| е      | 0.4          | 50            | 0.0                  | )18   |  |

| L      | 0.350        | 0.450         | 0.014                | 0.018 |  |

W-Type 12L DFN 3x3 Package

### **Richtek Technology Corporation**

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

### **Richtek Technology Corporation**

Taipei Office (Marketing)

5F, No. 95, Minchiuan Road, Hsintien City

Taipei County, Taiwan, R.O.C.

Tel: (8862)86672399 Fax: (8862)86672377

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.