# Description

The 9ZXL0831E / 9ZXL0851E are second-generation enhanced performance DB800ZL differential buffers. The parts are pin-compatible upgrades to the 9ZXL0831A and 9ZXL0851A, while offering a much improved phase jitter performance. A fixed external feedback maintains low drift for critical QPI/UPI applications.

### PCIe Clocking Architectures Supported

- Common Clocked (CC)

- Independent Reference (IR) with and without spread spectrum

# **Typical Application**

- Servers

- Storage

- Networking

- SSDs

# **Output Features**

- 8 Low-Power (LP) HCSL output pairs (0831E)

- 8 Low-Power (LP) HCSL output pairs with 85Ω Zout (0851E)

### Features

- LP-HCSL outputs; eliminate 16 resistors, save 27mm<sup>2</sup> of area (0831E)

- LP-HCSL outputs with 85 $\Omega$  Zout; eliminate 32 resistors, save 64mm<sup>2</sup> of area (0851E)

- 8 OE# pins; hardware control of each output

- Selectable PLL BW; minimizes jitter peaking in cascaded PLL topologies

- Hardware/SMBus control of PLL bandwidth and bypass; change mode without power cycle

- Spread spectrum compatible; tracks spreading input clock for EMI reduction

- 100MHz & 133.33MHz PLL mode; UPI and legacy QPI support

- 6 × 6 mm 48-VFQFPN package; small board footprint

# **Key Specifications**

- Cycle-to-cycle jitter < 50ps</li>

- Output-to-output skew < 50ps</li>

- Input-to-output delay: Fixed at 0ps

- Input-to-output delay variation < 50ps</li>

- Phase jitter: PCIe Gen4 < 0.5ps rms</li>

- Phase jitter: QPI/UPI > = 9.6GB/s < 0.2ps rms</p>

- Phase jitter: IF-UPI < 1.0ps rms</li>

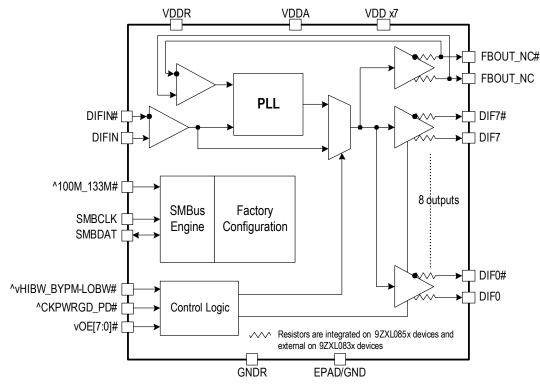

# Block Diagram

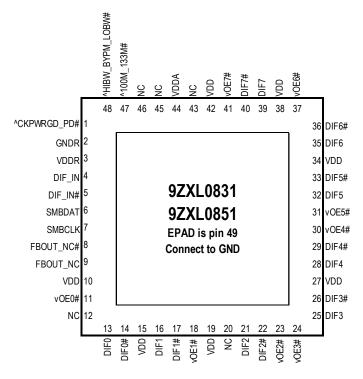

### **Pin Assignments**

48-VFQFPN, 6 x 6 mm, 0.4mm pitch

#### **Power Management Table**

|             |         | SMBus  |        |         | PLL State if not |

|-------------|---------|--------|--------|---------|------------------|

| CKPWRGD_PD# | DIF_IN  | EN bit | OE[x]# | DIF[x]  | in Bypass Mode   |

| 0           | Х       | Х      | Х      | Low/Low | OFF              |

| 1           | Running | 0      | 0      | Low/Low | ON               |

|             |         | 0      | 1      | Low/Low | ON               |

|             |         | 1      | 0      | Running | ON               |

|             |         | 1      | 1      | Low/Low | ON               |

#### PLL Operating Mode Table

| HiBW_BypM_LoBW# | MODE      |

|-----------------|-----------|

| Low             | PLL Lo BW |

| Mid             | Bypass    |

| High            | PLL Hi BW |

NOTE: PLL is OFF in Bypass Mode

#### PLL Operating Mode Readback Table

| HiBW_BypM_LoBW# | Byte0, bit 7 | Byte 0, bit 6 |

|-----------------|--------------|---------------|

| Low (Low BW)    | 0            | 0             |

| Mid (Bypass)    | 0            | 1             |

| High (High BW)  | 1            | 1             |

#### **SMBus Address**

| Address | + Read/Write bit |

|---------|------------------|

| 1101100 | Х                |

#### **Power Connections**

| Pin                      | Number | Description  |

|--------------------------|--------|--------------|

| VDD                      | GND    | Description  |

| 44                       | 49     | Analog PLL   |

| 3                        | 2      | Analog input |

| 10,15,19,<br>27,34,38,42 | 49     | DIF clocks   |

#### Functionality at Power Up (PLL Mode)

|            | DIF_IN |        |

|------------|--------|--------|

| 100M_133M# | MHz    | DIF[x] |

| 1          | 100.00 | DIF_IN |

| 0          | 133.33 | DIF_IN |

# **Pin Descriptions**

| Pin # | Pin Name     | Туре | Description                                                                                                                                                                             |

|-------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ^CKPWRGD_PD# | IN   | Input notifies device to sample latched inputs and start up on first high assertion. Low enters Power Down Mode,                                                                        |

|       |              |      | subsequent high assertions exit Power Down Mode. This pin has internal pull-up resistor.                                                                                                |

| 2     | GNDR         | GND  | Analog ground pin for the differential input (receiver).                                                                                                                                |

| 3     | VDDR         | PWR  | Power supply for differential input clock (receiver). This VDD should be treated as an analog power rail and                                                                            |

| Ŭ     |              |      | filtered appropriately. Nominally 3.3V.                                                                                                                                                 |

| 4     | DIF_IN       | IN   | HCSL true input.                                                                                                                                                                        |

| 5     | DIF_IN#      | IN   | HCSL complementary input                                                                                                                                                                |

| 6     | SMBDAT       | I/O  | Data pin of SMBUS circuitry                                                                                                                                                             |

| 7     | SMBCLK       | IN   | Clock pin of SMBUS circuitry                                                                                                                                                            |

| 8     | FBOUT_NC#    | OUT  | Complementary half of differential feedback output. This pin should NOT be connected to anything outside the chip. It exists to provide delay path matching to get 0 propagation delay. |

| 9     | FBOUT_NC     | OUT  | True half of differential feedback output. This pin should NOT be connected to anything outside the chip. It exists to provide delay path matching to get 0 propagation delay.          |

| 10    | VDD          | PWR  | Power supply, nominally 3.3V.                                                                                                                                                           |

| 11    | vOE0#        | IN   | Active low input for enabling output 0. This pin has an internal pull-down.                                                                                                             |

|       |              |      | 1 = disable outputs, 0 = enable outputs.                                                                                                                                                |

| 12    | NC           | N/A  | No connection.                                                                                                                                                                          |

| 13    | DIF0         | OUT  | Differential true clock output.                                                                                                                                                         |

| 14    | DIF0#        | OUT  | Differential complementary clock output.                                                                                                                                                |

| 15    | VDD          | PWR  | Power supply, nominally 3.3V.                                                                                                                                                           |

| 16    | DIF1         | OUT  | Differential true clock output.                                                                                                                                                         |

| 17    | DIF1#        | OUT  | Differential complementary clock output.                                                                                                                                                |

| 18    | vOE1#        | IN   | Active low input for enabling output 1. This pin has an internal pull-down.<br>1 = disable outputs, 0 = enable outputs.                                                                 |

| 19    | VDD          | PWR  | Power supply, nominally 3.3V.                                                                                                                                                           |

| 20    | NC           | N/A  | No connection.                                                                                                                                                                          |

| 21    | DIF2         | OUT  | Differential true clock output.                                                                                                                                                         |

| 22    | DIF2#        | OUT  | Differential complementary clock output.                                                                                                                                                |

| 00    |              | INI  | Active low input for enabling output 2. This pin has an internal pull-down.                                                                                                             |

| 23    | vOE2#        | IN   | 1 = disable outputs, 0 = enable outputs.                                                                                                                                                |

| 04    |              | INI  | Active low input for enabling output 3. This pin has an internal pull-down.                                                                                                             |

| 24    | vOE3#        | IN   | 1 = disable outputs, 0 = enable outputs.                                                                                                                                                |

| 25    | DIF3         | OUT  | Differential true clock output.                                                                                                                                                         |

| 26    | DIF3#        | OUT  | Differential complementary clock output.                                                                                                                                                |

| 27    | VDD          | PWR  | Power supply, nominally 3.3V.                                                                                                                                                           |

| 28    | DIF4         | OUT  | Differential true clock output.                                                                                                                                                         |

| 29    | DIF4#        | OUT  | Differential complementary clock output.                                                                                                                                                |

| 30    | vOE4#        | IN   | Active low input for enabling output 4. This pin has an internal pull-down.<br>1 = disable outputs, 0 = enable outputs.                                                                 |

| 31    | vOE5#        | IN   | Active low input for enabling output 5. This pin has an internal pull-down.<br>1 = disable outputs, 0 = enable outputs.                                                                 |

| 32    | DIF5         | OUT  | Differential true clock output.                                                                                                                                                         |

|       | DIF5#        | OUT  | Differential complementary clock output.                                                                                                                                                |

| 34    | VDD          | PWR  | Power supply, nominally 3.3V.                                                                                                                                                           |

|       | DIF6         | OUT  | Differential true clock output.                                                                                                                                                         |

|       | DIF6#        | OUT  | Differential complementary clock output.                                                                                                                                                |

|       |              |      | Active low input for enabling output 6. This pin has an internal pull-down.                                                                                                             |

| 37    | vOE6#        | IN   | 1 = disable outputs, 0 = enable outputs.                                                                                                                                                |

| 38    | VDD          | PWR  | Power supply, nominally 3.3V.                                                                                                                                                           |

| Pin # | Pin Name         | Туре    | Description                                                                                                    |

|-------|------------------|---------|----------------------------------------------------------------------------------------------------------------|

| 39    | DIF7             | OUT     | Differential true clock output.                                                                                |

| 40    | DIF7#            | OUT     | Differential complementary clock output.                                                                       |

| 41    | vOE7#            | IN      | Active low input for enabling output 7. This pin has an internal 120kohm pull-down.                            |

|       | VOL7#            |         | 1 = disable outputs, 0 = enable outputs.                                                                       |

| 42    | VDD              | PWR     | Power supply, nominally 3.3V.                                                                                  |

| 43    | NC               | N/A     | No connection.                                                                                                 |

| 44    | VDDA             | PWR     | Power supply for PLL core.                                                                                     |

| 45    | NC               | N/A     | No connection.                                                                                                 |

| 46    | NC               | N/A     | No connection.                                                                                                 |

| 47    | ^100M 133M#      | LATCHED | 3.3V Input to select operating frequency. This pin has an internal 120kohm pull-up resistor. See Functionality |

| 77    | 100101_100101#   | IN      | Table for definition.                                                                                          |

| 48    | ^HIBW BYPM LOBW# | LATCHED | Tri-level input to select High BW, Bypass or Low BW Mode. Has an internal 120kohm pull up resistor. See PLL    |

| 40    |                  | IN      | Operating Mode Table for details.                                                                              |

| 49    | EPAD             | PWR     | Ground                                                                                                         |

### **Pin Descriptions (cont.)**

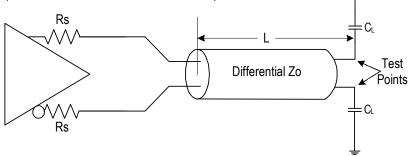

# Test Loads

Low-Power HCSL Output Test Load (standard PCIe source-terminated test load)

### Parameters for Low-Power HCSL Output Test Load

| Device    | Rs (Ω)   | Ζο (Ω) | L (Inches) | CL (pF) |

|-----------|----------|--------|------------|---------|

| 9ZXL083x  | 27       | 85     | 10         | 2       |

|           | 33       | 100    | 10         | 2       |

| 9ZXL085x* | Internal | 85     | 10         | 2       |

|           | 7.5      | 100    | 10         | 2       |

\*Contact factory for versions of this device with Zo=100 $\Omega$

# **Alternate Terminations**

The LP-HCSL output can easily drive other logic families. See <u>"AN-891 Driving LVPECL, LVDS, and CML Logic with IDT's</u> <u>"Universal" Low-Power HCSL Outputs</u>" for termination schemes for LVPECL, LVDS, CML and SSTL.

## **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 9ZXL0831E / 9ZXL0851E. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Parameter            | Symbol          | Conditions                 | Minimum | Typical | Maximum              | Units | Notes |

|----------------------|-----------------|----------------------------|---------|---------|----------------------|-------|-------|

| Supply Voltage       | VDDx            |                            |         |         | 3.9                  | V     | 1,2   |

| Input Low Voltage    | VIL             |                            | GND-0.5 |         |                      | V     | 1     |

| Input High Voltage   | V <sub>IH</sub> | Except for SMBus interface |         |         | V <sub>DD</sub> +0.5 | V     | 1,3   |

| Input High Voltage   | VIHSMB          | SMBus clock and data pins  |         |         | 3.9                  | V     | 1     |

| Storage Temperature  | Ts              |                            | -65     |         | 150                  | °C    | 1     |

| Junction Temperature | Tj              |                            |         |         | 125                  | C°    | 1     |

| Input ESD Protection | ESD prot        | Human Body Model           | 2500    |         |                      | V     | 1     |

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

<sup>3</sup>Not to exceed 3.9V.

### **Electrical Characteristics-DIF\_IN Clock Input Parameters**

T<sub>AMB</sub> = over the specified operating range. Supply voltages per normal operation conditions; see Test Loads for loading conditions

| Parameter                        | Symbol             | Conditions                             | Minimum | Typical | Maximum | Units | Notes |

|----------------------------------|--------------------|----------------------------------------|---------|---------|---------|-------|-------|

| Input Crossover Voltage - DIF_IN | V <sub>CROSS</sub> | Cross over voltage                     | 150     |         | 900     | mV    | 1     |

| Input Swing - DIF_IN             | V <sub>SWING</sub> | Differential value                     | 300     |         |         | mV    | 1     |

| Input Slew Rate - DIF_IN         | dv/dt              | Measured differentially                | 0.4     |         | 8       | V/ns  | 1,2   |

| Input Leakage Current            | I <sub>IN</sub>    | $V_{IN} = V_{DD}$ , $V_{IN} = GND$     | -5      |         | 5       | μA    |       |

| Input Duty Cycle                 | $d_{tin}$          | Measurement from differential waveform | 45      |         | 55      | %     | 1     |

| Input Jitter - Cycle to Cycle    | $J_{DIFIn}$        | Differential measurement               | 0       |         | 125     | ps    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Slew rate measured through +/-75mV window centered around differential zero

### **Electrical Characteristics-SMBus**

T<sub>AMB</sub> = over the specified operating range. Supply voltages per normal operation conditions; see Test Loads for loading conditions

| Parameter                 | Symbol              | Conditions                                                     | Minimum | Typical | Maximum            | Units | Notes |

|---------------------------|---------------------|----------------------------------------------------------------|---------|---------|--------------------|-------|-------|

| SMBus Input Low Voltage   | VILSMB              |                                                                |         |         | 0.8                | V     |       |

| SMBus Input High Voltage  | VIHSMB              |                                                                | 2.1     |         | V <sub>DDSMB</sub> | V     |       |

| SMBus Output Low Voltage  | V <sub>OLSMB</sub>  | at I <sub>PULLUP</sub>                                         |         |         | 0.4                | V     |       |

| SMBus Sink Current        | I <sub>PULLUP</sub> | at V <sub>OL</sub>                                             | 4       |         |                    | mA    |       |

| Nominal Bus Voltage       | V <sub>DDSMB</sub>  |                                                                | 2.7     |         | 3.6                | V     | 1     |

| SCLK/SDATA Rise Time      | <b>t</b> RSMB       | (Max V <sub>IL</sub> - 0.15V) to (Min V <sub>IH</sub> + 0.15V) |         |         | 1000               | ns    | 1     |

| SCLK/SDATA Fall Time      | t <sub>FSMB</sub>   | (Min V <sub>IH</sub> + 0.15V) to (Max V <sub>IL</sub> - 0.15V) |         |         | 300                | ns    | 1     |

| SMBus Operating Frequency | <b>f</b> MAXSMB     | Maximum SMBus operating frequency                              |         |         | 500                | kHz   | 5     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

$^2$  Control input must be monotonic from 20% to 80% of input swing.

$^3$  Time from deassertion until outputs are > 200mV.

<sup>4</sup>DIF\_IN input.

<sup>5</sup> The differential input clock must be running for the SMBus to be active.

### **Electrical Characteristics-Input/Supply/Common Output Parameters**

T<sub>AMB</sub> = over the specified operating range. Supply voltages per normal operation conditions; see Test Loads for loading conditions

| Symbol                         | Parameter                             | Conditions                                                                                               | Minimum   | Typical | Maximum               | Units | Notes |

|--------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------|-----------|---------|-----------------------|-------|-------|

| VDDx                           | Supply Voltage                        | Supply voltage for core and analog                                                                       | 3.135     | 3.3     | 3.465                 | V     |       |

| VDDIO                          | Output Supply Voltage                 | Supply voltage for DIF outputs, if present                                                               | 0.9975    | 1.05    | 3.465                 | V     |       |

| T <sub>AMB</sub>               | Ambient Operating<br>Temperature      | Industrial range (T <sub>IND</sub> )                                                                     | -40       | 25      | 85                    | °C    |       |

| VIH                            | Input High Voltage                    | Single-ended inputs, except SMBus, tri-level inputs                                                      | 2         |         | V <sub>DD</sub> + 0.3 | V     |       |

| V <sub>IL</sub>                | Input Low Voltage                     | Single-ended inputs, except SMBus, tri-level inputs                                                      | GND - 0.3 |         | 0.8                   | V     |       |

| V <sub>IH</sub>                | Input High Voltage                    | Tri-level inputs                                                                                         | 2.2       |         | V <sub>DD</sub> + 0.3 | V     |       |

| VIL                            | Input Mid Voltage                     | Tri-level inputs                                                                                         | 1.2       | VDD/2   | 1.8                   | V     |       |

| VIL                            | Input Low Voltage                     | Tri-level inputs                                                                                         | GND - 0.3 |         | 0.8                   | V     |       |

| I <sub>IN</sub>                |                                       | Single-ended inputs, $V_{IN}$ = GND, $V_{IN}$ = $V_{DD}$                                                 | -5        |         | 5                     | μA    |       |

| I <sub>INP</sub>               | Input Current                         | Single-ended inputs<br>V <sub>IN</sub> = 0 V; inputs with internal pull-up resistors                     | -50       |         | 50                    | μA    |       |

|                                |                                       | $V_{IN}$ = $V_{DD}$ ; inputs with internal pull-down resistors                                           |           |         |                       |       |       |

| F <sub>ibyp</sub>              |                                       | V <sub>DD</sub> = 3.3 V, Bypass Mode                                                                     | 1         |         | 400                   | MHz   |       |

| F <sub>ipll</sub>              | Input Frequency                       | V <sub>DD</sub> = 3.3 V, 100MHz PLL Mode                                                                 | 98.5      | 100.00  | 102.5                 | MHz   |       |

| F <sub>ipll</sub>              |                                       | V <sub>DD</sub> = 3.3 V, 133.33MHz PLL Mode                                                              | 132       | 133.33  | 135                   | MHz   |       |

| L <sub>pin</sub>               | Pin Inductance                        |                                                                                                          |           |         | 7                     | nH    | 1     |

| C <sub>IN</sub>                |                                       | Logic inputs, except DIF_IN                                                                              | 1.5       |         | 5                     | pF    | 1     |

| $C_{\text{INDIF}_{\text{IN}}}$ | Capacitance                           | DIF_IN differential clock inputs                                                                         | 1.5       |         | 2.7                   | pF    | 1,4   |

| C <sub>OUT</sub>               |                                       | Output pin capacitance                                                                                   |           |         | 6                     | pF    | 1     |

| T <sub>STAB</sub>              | Clk Stabilization                     | From V <sub>DD</sub> power-up and after input clock stabilization<br>or de-assertion of PD# to 1st clock |           | 1.0     | 1.8                   | ms    | 1,2   |

| f <sub>MODINPCIe</sub>         | Input SS Modulation<br>Frequency PCIe | Allowable frequency for PCIe applications<br>(Triangular modulation)                                     |           | 33      | kHz                   |       |       |

| t⊥atoe#                        | OE# Latency                           | DIF start after OE# assertion 4 5<br>DIF stop after OE# deassertion                                      |           | 10      | clocks                | 1,2,3 |       |

|                                | Tdrive_PD#                            | DIF output enable after 49<br>PD# de-assertion                                                           |           |         |                       | μs    | 1,3   |

| t⊨                             | Tfall                                 | Fall time of control inputs                                                                              |           |         | 5                     | ns    | 2     |

| t <sub>R</sub>                 | Trise                                 | Rise time of control inputs                                                                              |           |         | 5                     | ns    | 2     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

$^2$  Control input must be monotonic from 20% to 80% of input swing.

$^{3}$  Time from deassertion until outputs are > 200mV.

<sup>4</sup> DIF\_IN input.

### **Electrical Characteristics-Current Consumption**

T<sub>AMB</sub> = over the specified operating range. Supply voltages per normal operation conditions; see Test Loads for loading conditions

| Symbol             | Parameter                | Conditions                                     | Minimum | Typical | Maximum | Units | Notes |

|--------------------|--------------------------|------------------------------------------------|---------|---------|---------|-------|-------|

| I <sub>DDA</sub>   | Operating Supply Current | $V_{\text{DDA}}$ , PLL M ode at 100M Hz        |         | 37      | 45      | mA    | 1     |

| I <sub>DD</sub>    | Operating Supply Current | All other $V_{\text{DD}}$ pins at 100M Hz      |         | 55      | 68      | mA    |       |

| I <sub>DDAPD</sub> | Powerdown Current        | $V_{DDA}$ , CKPWRGD_PD# = 0                    |         | 3       | 4       | mA    | 1     |

| I <sub>DDPD</sub>  | Powerdown Current        | rrent All other $V_{DD}$ pins, CKPWRGD_PD# = 0 |         | 1       | 2       | mA    |       |

<sup>1.</sup> Includes VDDR if applicable.

### **Electrical Characteristics-HCSL/LP-HCSL Outputs**

T<sub>AMB</sub> = over the specified operating range. Supply voltages per normal operation conditions; see Test Loads for loading conditions

| Symbol     | Parameter              | Conditions                               | Minimum | Typical | Maximum | Specification<br>Limit | Units | Notes   |

|------------|------------------------|------------------------------------------|---------|---------|---------|------------------------|-------|---------|

| dV/dt      | Slew Rate              | Scope averaging on.                      | 2       | 2.9     | 4       | 1 – 4                  | V/ns  | 1, 2, 3 |

| ∆dV/dt     | Slew Rate Matching     | Single-ended measurement.                |         | 7.1     | 20      | 20                     | %     | 1, 4, 7 |

| Vmax       | Max Voltage            | Measurement on single-ended signal using | 660     | 792     | 850     | 1150                   | mV    | 7       |

| Vmin       | Min Voltage            | absolute value (scope averaging off).    | -150    | -35     | 150     | -300                   | IIIV  | 7       |

| Vcross_abs | Crossing Voltage (abs) | Scope averaging off.                     | 250     | 372     | 550     | 250 – 550              | mV    | 1, 5, 7 |

| ∆-Vcross   | Crossing Voltage (var) | Scope averaging off.                     |         | 15      | 140     | 140                    | mV    | 1, 6, 7 |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Measured from differential waveform.

<sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

<sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

<sup>7</sup> At default SMBus settings.

### **Electrical Characteristics-Skew and Differential Jitter Parameters**

T<sub>AMB</sub> = over the specified operating range. Supply voltages per normal operation conditions; see Test Loads for loading conditions

| Symbol              | Parameter                       | Conditions                                                                                                                       | Minimum | Typical | Maximum | Units       | Notes     |

|---------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------------|-----------|

| tspo_pll            | CLK_IN, DIF[x:0]                | Input-to-output skew in PLL Mode<br>at 100MHz, nominal temperature and voltage                                                   | -100    | -21.3   | 100     | ps          | 1,2,4,5,8 |

| ₽D_BYP              | CLK_IN, DIF[x:0]                | Input-to-output skew in Bypass Mode<br>at 100MHz, nominal temperature and voltage                                                | 2       | 2.6     | 4       | ns          | 1,2,3,5,8 |

| tospo_pll           | CLK_IN, DIF[x:0]                | Input-to-output skew variation in PLL Mode<br>at 100MHz, across voltage and temperature                                          | -50     | 0.0     | 50      | ps          | 1,2,3,5,8 |

| реро вур            | CLK_IN, DIF[x:0]                | Input-to-output skew variation in Bypass Mode<br>at 100MHz, across voltage and temperature,<br>T <sub>AMB</sub> = 0 to 70°C      | -250    |         | 250     | ps          | 1,2,3,5,8 |

| 0010_011            |                                 | Input-to-output skew variation in Bypass Mode<br>at 100MHz, across voltage and temperature,<br>T <sub>AMB</sub> = -40°C to 105°C | -350    |         | 350     | ps          | 1,2,3,5,8 |

| <b>İ</b> DTE        | CLK_IN, DIF[x:0]                | Random differential tracking error between two 9ZX devices in Hi BW Mode                                                         |         | 3       | 5       | ps<br>(rms) | 1,2,3,5,8 |

| <b>t</b> dsste      | CLK_IN, DIF[x:0]                | Random differential spread spectrum tracking error<br>between two 9ZX devices in Hi BW Mode                                      |         | 23      | 50      | ps          | 1,2,3,5,8 |

| tskew_all           | DIF[x:0]                        | Output-to-output skew across all outputs, common to PLL and Bypass Mode, at 100MHz                                               |         |         | 50      | ps          | 1,2,3,8   |

| jpeak-hibw          | PLL Jitter Peaking              | LOBW#_BYPASS_HIBW = 1                                                                                                            | 0       | 1.3     | 2.5     | dB          | 7,8       |

| jpeak-lobw          | PLL Jitter Peaking              | LOBW#_BYPASS_HIBW = 0                                                                                                            | 0       | 1.3     | 2       | dB          | 7,8       |

| рII <sub>нвw</sub>  | PLL Bandwidth                   | LOBW#_BYPASS_HIBW = 1                                                                                                            | 2       | 2.6     | 4       | MHz         | 8,9       |

| pll <sub>LOBW</sub> | PLL Bandwidth                   | LOBW#_BYPASS_HIBW = 0                                                                                                            | 0.7     | 1.0     | 1.4     | MHz         | 8,9       |

| toc 🛛               | Duty Cycle                      | Measured differentially, PLL Mode                                                                                                | 45      | 50.3    | 55      | %           | 1         |

| toco                | Duty Cycle Distortion           | Measured differentially, Bypass Mode at 100MHz                                                                                   | -1      | 0       | 1       | %           | 1,10      |

| tjcyc-cyc           | Jitter, Cycle to Cycle PLL Mode |                                                                                                                                  |         | 14      | 50      | ps          | 1,11      |

|                     |                                 | Additive jitter in Bypass Mode                                                                                                   |         | 0.1     | 5       | ps          | 1,11      |

Notes for preceding table:

<sup>1</sup> Measured into fixed 2 pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

<sup>2</sup> Measured from differential cross-point to differential cross-point. This parameter can be tuned with external feedback path, if present.

<sup>3</sup> All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

<sup>4</sup> This parameter is deterministic for a given device.

$^{\rm 5}\,$  Measured with scope averaging on to find mean value.

<sup>6</sup>t is the period of the input clock.

<sup>7</sup> Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

<sup>8.</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>9</sup> Measured at 3 db down or half power point.

<sup>10</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

<sup>11</sup> Measured from differential waveform.

### Electrical Characteristics-Filtered Phase Jitter Parameters - PCIe Common Clocked (CC) Architectures

| $T_{AMB}$ = over the specified operating range | Supply Voltages per normal operation condi | tions, See Test Loads for Loading Conditions |

|------------------------------------------------|--------------------------------------------|----------------------------------------------|

|                                                |                                            |                                              |

| Symbol        | Parameter                                             | Conditions                                                                                       | Minimum | Typical | Maximum | Specification<br>Limit | Units       | Notes      |

|---------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------|---------|---------|------------------------|-------------|------------|

| tjphPCleG1-CC |                                                       | PCIe Gen 1                                                                                       |         | 13.4    | 30      | 86                     | ps (p-p)    | 1, 2, 3    |

|               |                                                       | PCIe Gen 2 Low Band<br>10kHz < f < 1.5MHz<br>(PLL BW of 5-16MHz, 8-16MHz, CDR = 5MHz)            |         | 0.2     | 0.7     | 3                      | ps<br>(rms) | 1, 2       |

| ₿phPCleG2-CC  | Phase Jitter,<br>PLL Mode                             | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)<br>(PLL BW of 5-16MHz, 8-16MHz, CDR = 5MHz) |         | 1.0     | 1.5     | 3.1                    | ps<br>(rms) | 1, 2       |

| tjphPCleG3-CC |                                                       | PCIe Gen 3<br>(PLL BW of 2-4MHz, 2-5MHz, CDR = 10MHz)                                            |         | 0.2     | 0.4     | 1                      | ps<br>(rms) | 1, 2       |

| tjphPCleG4-CC |                                                       | PCIe Gen 4<br>(PLL BW of 2-4MHz, 2-5MHz, CDR = 10MHz)                                            |         | 0.2     | 0.4     | 0.5                    | ps<br>(rms) | 1, 2       |

| tjphPCleG1-CC |                                                       | PCIe Gen 1                                                                                       |         | 0.01    | 0.06    |                        | ps (p-p)    | 1, 2, 3, 4 |

|               |                                                       | PCIe Gen 2 Low Band<br>10kHz < f < 1.5MHz<br>(PLL BW of 5-16MHz, 8-16MHz, CDR = 5MHz)            |         | 0.01    | 0.06    |                        | ps<br>(rms) | 1, 2, 3, 4 |

| ṫjphPCleG2-CC | Additive Phase<br>Jitter, Bypass<br>mode              | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)<br>(PLL BW of 5-16MHz, 8-16MHz, CDR = 5MHz) |         | 0.01    | 0.06    | Not Applicable         | ps<br>(rms) | 1, 2, 3, 4 |

| tjphPCleG3-CC |                                                       | PCIe Gen 3<br>(PLL BW of 2-4MHz, 2-5MHz, CDR = 10MHz)                                            |         | 0.01    | 0.06    |                        | ps<br>(rms) | 1, 2, 3, 4 |

| tjphPCleG4-CC | PCIe Gen 4<br>(PLL BW of 2-4MHz, 2-5MHz, CDR = 10MHz) |                                                                                                  |         | 0.01    | 0.06    |                        | ps<br>(rms) | 1, 2, 3, 4 |

### Electrical Characteristics-Filtered Phase Jitter Parameters - PCIe Independent Reference (IR) Architectures

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| Symbol          | Parameter                        | Conditions                                    | Minimum | Typical | Maximum | Industry Limit | Units       | Notes   |

|-----------------|----------------------------------|-----------------------------------------------|---------|---------|---------|----------------|-------------|---------|

| tjphPCleG2-SRIS | Phase Jitter, PLL                | PCIe Gen 2<br>(PLL BW of 16MHz , CDR = 5MHz)  |         | 0.9     | 1.1     | 2              | ps<br>(rms) | 1, 2, 5 |

| tjphPCleG3-SRIS | Mode                             | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz) |         | 0.6     | 0.65    | 0.7            | ps<br>(rms) | 1, 2, 5 |

| tjphPCleG2-SRIS | Additive Phase<br>Jitter, Bypass | PCIe Gen 2<br>(PLL BW of 16MHz , CDR = 5MHz)  |         | 0.01    | 0.05    | Not Applicable | ps<br>(rms) | 2, 4, 5 |

| tjphPCleG3-SRIS | mode                             | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz) |         | 0.01    | 0.05    |                | ps<br>(rms) | 2, 4, 5 |

#### Notes for PCIe Filtered Phase Jitter tables (CC) and (IR)

<sup>1</sup> Applies to all differential outputs, guaranteed by design and characterization.

<sup>2</sup> Calculated from Intel-supplied Clock Jitter Tool, when driven by 9SQL495x or equivalent with spread on and off.

<sup>3</sup> Sample size of at least 100K cycles. This figure extrapolates to 108ps pk-pk at 1M cycles for a BER of 1<sup>-12</sup>.

<sup>4</sup> For RMS values, additive jitter is calculated by solving for b [ $b = sqrt(c^2 - a^2)$ ], where "a" is rms input jitter and "c" is rms total jitter.

<sup>5</sup> IR is the new name for Separate Reference Independent Spread (SRIS) and Separate Reference no Spread (SRNS) PCIe clock architectures. According to the PCIe Base Specification Rev 4.0 version 0.7 draft, the jitter transfer functions and corresponding jitter limits are not defined for the IR clock architecture. Widely accepted industry limits using widely accepted industry filters are used to populate this table. There are no accepted filters or limits for IR clock architectures at PCIe Gen1 or Gen4 data rates.

### **Electrical Characteristics-Filtered Phase Jitter Parameters - QPI/UPI**

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| Symbol      | Parameter                               | Conditions                                             | Minimum | Typical     | Maximum     | Specification<br>Limit | Units       | Notes   |

|-------------|-----------------------------------------|--------------------------------------------------------|---------|-------------|-------------|------------------------|-------------|---------|

|             |                                         | QPI & UPI<br>(100MHz or 133MHz, 4.8Gb/s, 6.4Gb/s 12UI) |         | 0.14        | 0.30        | 0.5                    | ps<br>(rms) | 1, 2    |

| tjphQPI_UPI | Phase Jitter, PLL                       | QPI & UPI<br>(100MHz, 8.0Gb/s, 12UI)                   |         | 0.07        | 0.13        | 0.3                    | ps<br>(rms) | 1, 2    |

|             | Mode                                    | QPI & UPI<br>(100MHz, ?9.6Gb/s, 12UI)                  |         | 0.06        | 0.1         | 0.2                    | ps<br>(rms) | 1, 2    |

| tjphIF-UPI  |                                         | IF-UPI                                                 |         | 0.1<br>0.17 | 0.14<br>0.2 | 1                      | ps<br>(rms) | 1, 4, 5 |

|             |                                         | QPI & UPI<br>(100MHz or 133MHz, 4.8Gb/s, 6.4Gb/s 12UI) |         | 0.0         | 0.01        |                        | ps<br>(rms) | 1, 2, 3 |

| tjphQPI_UPI | <i>Additive</i> Phase<br>Jitter, Bypass | QPI & UPI<br>(100MHz, 8.0Gb/s, 12UI)                   |         | 0.0         | 0.01        | Not Applicable         | ps<br>(rms) | 1, 2, 3 |

|             | mode                                    | QPI & UPI<br>(100MHz, ?9.6Gb/s, 12UI)                  |         | 0.0         | 0.01        | NotApplicable          | ps<br>(rms) | 1, 2, 3 |

| tjphIF-UPI  |                                         | IF-UPI                                                 |         | 0.06        | 0.07        |                        | ps<br>(rms) | 1, 4    |

<sup>1</sup>Applies to all differential outputs, guaranteed by design and characterization.

<sup>2</sup> Calculated from Intel-supplied Clock Jitter Tool, when driven by 9SQL495x or equivalent with spread on and off.

<sup>3</sup> For RMS values, additive jitter is calculated by solving for b [ $b = sqrt(c^2 - a^2)$ ], where "a" is rms input jitter and "c" is rms total jitter.

<sup>4</sup> Calculated from phase noise analyzer when driven by Wenzel Associates source with Intel-specified brick-wall filter applied.

<sup>5</sup> Top number is when the buffer is in Low BW mode, bottom number is when the buffer is in High BW mode.

# Electrical Characteristics-Unfiltered Phase Jitter Parameters - 12kHz to 20MHz

T<sub>AMB</sub> = over the specified operating range. Supply voltages per normal operation conditions; see Test Loads for loading conditions

| Symbol        | Parameter                                       | Conditions                   | Minimum | Typical | Maximum | Industry Limit | Units       | Notes   |

|---------------|-------------------------------------------------|------------------------------|---------|---------|---------|----------------|-------------|---------|

| tjph12k-20MHi | Phase Jitter, PLL<br>Mode                       | PLL High BW, SSC OFF, 100MHz |         | 171     | 225     |                | fs<br>(rms) | 1, 2    |

| tjph12k-20MLo | Phase Jitter, PLL<br>Mode                       | PLL Low BW, SSC OFF, 100MHz  |         | 184     | 225     | Not Applicable | fs<br>(rms) | 1, 2    |

| ţph12k-20МВур | <i>Additive</i> Phase<br>Jitter, Bypass<br>Mode | Bypass Mode, SSC OFF, 100MHz |         | 107     | 125     |                | fs<br>(rms) | 1, 2, 3 |

<sup>1</sup> Applies to all outputs when driven by Wenzel Associates source.

<sup>2</sup> 12kHz to 20MHz brick wall filter.

<sup>3</sup> For RMS values, additive jitter is calculated by solving for b [ $b = sqrt(c^2 - a^2)$ ], where "a" is rms input jitter and "c" is rms total jitter.

### **Clock Periods-Differential Outputs with Spread Spectrum Disabled**

|         |                  |                                  |                                          | Me                                       | easurement Win          | dow                                      |                                          |                                  |       |       |

|---------|------------------|----------------------------------|------------------------------------------|------------------------------------------|-------------------------|------------------------------------------|------------------------------------------|----------------------------------|-------|-------|

|         | Center           | 1 Clock                          | 1µs                                      | 0.1s                                     | 0.1s                    | 0.1s                                     | 1µs                                      | 1 Clock                          |       |       |

| SSC OFF | Frequency<br>MHz | -c2c jitter<br>AbsPer<br>Minimum | -SSC<br>Short-Term<br>Average<br>Minimum | - ppm<br>Long-Term<br>Average<br>Minimum | 0 ppm Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Maximum | +SSC<br>Short-Term<br>Average<br>Maximum | +c2c jitter<br>AbsPer<br>Maximum | Units | Notes |

| DIF     | 100.00           | 9.94900                          |                                          | 9.99900                                  | 10.00000                | 10.00100                                 |                                          | 10.05100                         | ns    | 1,2,3 |

|         | 133.33           | 7.44925                          |                                          | 7.49925                                  | 7.50000                 | 7.50075                                  |                                          | 7.55075                          | ns    | 1,2,4 |

### Clock Periods-Differential Outputs with Spread Spectrum Enabled

|        |                  |                                  |                                          | Me                                       | easurement Win          | dow                                      |                                          |                                  |       |       |

|--------|------------------|----------------------------------|------------------------------------------|------------------------------------------|-------------------------|------------------------------------------|------------------------------------------|----------------------------------|-------|-------|

|        | Center           | 1 Clock                          | 1µs                                      | 0.1s                                     | 0.1s                    | 0.1s                                     | 1µs                                      | 1 Clock                          |       |       |

| SSC ON | Frequency<br>MHz | -c2c jitter<br>AbsPer<br>Minimum | -SSC<br>Short-Term<br>Average<br>Minimum | - ppm<br>Long-Term<br>Average<br>Minimum | 0 ppm Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Maximum | +SSC<br>Short-Term<br>Average<br>Maximum | +c2c jitter<br>AbsPer<br>Maximum | Units | Notes |

| DIF    | 99.75            | 9.94906                          | 9.99906                                  | 10.02406                                 | 10.02506                | 10.02607                                 | 10.05107                                 | 10.10107                         | ns    | 1,2,3 |

|        | 133.00           | 7.44930                          | 7.49930                                  | 7.51805                                  | 7.51880                 | 7.51955                                  | 7.53830                                  | 7.58830                          | ns    | 1,2,4 |

Notes:

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with CK420BQ accuracy requirements (+/-100ppm). The buffer itself does not contribute to ppm error.

<sup>3</sup> Driven by SRC output of main clock, 100MHz PLL Mode or Bypass Mode.

<sup>4</sup> Driven by CPU output of main clock, 133MHz PLL Mode or Bypass Mode.

# **General SMBus Serial Interface Information**

#### How to Write

**()** IDT.

- Controller (host) sends a start bit

- Controller (host) sends the write address

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will **acknowledge**

- Controller (host) sends the byte count = X

- IDT clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- IDT clock will acknowledge each byte one at a time

- Controller (host) sends a stop bit

|           | Index Block Write Operation |        |                      |  |  |  |  |  |  |  |

|-----------|-----------------------------|--------|----------------------|--|--|--|--|--|--|--|

| Controll  | er (Host)                   |        | IDT (Slave/Receiver) |  |  |  |  |  |  |  |

| Т         | starT bit                   |        |                      |  |  |  |  |  |  |  |

| Slave A   | Address                     |        |                      |  |  |  |  |  |  |  |

| WR        | WRite                       |        |                      |  |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |  |

| Beginning | g Byte = N                  |        |                      |  |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |  |

| Data Byte | Count = X                   |        |                      |  |  |  |  |  |  |  |

|           |                             | 1      | ACK                  |  |  |  |  |  |  |  |

| Beginnin  | g Byte N                    |        |                      |  |  |  |  |  |  |  |

|           |                             | 1      | ACK                  |  |  |  |  |  |  |  |

| 0         |                             | $\sim$ |                      |  |  |  |  |  |  |  |

| 0         |                             | X Byte | 0                    |  |  |  |  |  |  |  |

| 0         |                             | te     | 0                    |  |  |  |  |  |  |  |

|           |                             |        | 0                    |  |  |  |  |  |  |  |

| Byte N    | + X - 1                     | 1      |                      |  |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |  |

| Р         | stoP bit                    |        |                      |  |  |  |  |  |  |  |

#### How to Read

- Controller (host) will send a start bit

- Controller (host) sends the write address

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) will send a separate start bit

- Controller (host) sends the read address

- IDT clock will acknowledge

- IDT clock will send the data byte count = X

- IDT clock sends Byte N+X-1

- IDT clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

|      | Index Block R   | lead O | peration             |

|------|-----------------|--------|----------------------|

| Cor  | troller (Host)  |        | IDT (Slave/Receiver) |

| Т    | starT bit       |        |                      |

|      | ave Address     |        |                      |

| WR   | WRite           |        |                      |

|      |                 |        | ACK                  |

| Begi | nning Byte = N  |        |                      |

|      |                 |        | ACK                  |

| RT   | Repeat starT    |        |                      |

|      | ave Address     |        |                      |

| RD   | ReaD            |        |                      |

|      |                 |        | ACK                  |

|      |                 |        |                      |

|      |                 |        | Data Byte Count=X    |

|      | ACK             |        |                      |

|      |                 |        | Beginning Byte N     |

|      | ACK             |        |                      |

|      |                 | X Byte | 0                    |

|      | 0               |        | 0                    |

|      | 0               | ×      | 0                    |

|      | 0               |        |                      |

|      |                 |        | Byte N + X - 1       |

| N    | Not acknowledge |        |                      |

| Р    | stoP bit        |        |                      |

#### SMBus Table: PLL Mode and Frequency Select Register

| Byte 0 | Pin # | Name       | Control Function             | Туре | 0                | 1                | Default |

|--------|-------|------------|------------------------------|------|------------------|------------------|---------|

| Bit 7  | 48    | PLL Mode 1 | PLL Operating Mode Rd back 1 | R    | See PLL Operatir | ng Mode Readback | Latch   |

| Bit 6  | 48    | PLL Mode 0 | PLL Operating Mode Rd back 0 | R    | Та               | able             | Latch   |

| Bit 5  |       |            | Reserved                     |      |                  | 0                |         |

| Bit 4  |       |            | Reserved                     |      |                  | 0                |         |

| Bit 3  |       | PLL_SW_EN  | Enable S/W control of PLL BW | RW   | HW Latch         | SMBus Control    | 0       |

| Bit 2  |       | PLL Mode 1 | PLL Operating Mode 1         | RW   | See PLL Operatir | ng Mode Readback | 1       |

| Bit 1  |       | PLL Mode 0 | PLL Operating Mode 1         | RW   | Table            |                  | 1       |

| Bit 0  | 47    | 100M_133M# | Frequency Select Readback    | R    | 133MHz           | 100MHz           | Latch   |

Note: Setting bit 3 to '1' allows the user to override the latch value from pin 5 via use of bits 2 and 1. Use the values from the PLL Operating Mode Readback Table. Note that Bits 7 and 6 will keep the value originally latched on pin 5. If the user changes these bits, a warm reset of the system will have to be accomplished.

#### SMBus Table: Output Control Register

| Byte 1 | Pin # | Name     | Control Function | Туре | 0       | 1               | Default |

|--------|-------|----------|------------------|------|---------|-----------------|---------|

| Bit 7  | 32/33 | DIF_5_En | Output Enable    | RW   |         |                 | 1       |

| Bit 6  | 28/29 | DIF_4_En | Output Enable    | RW   | Low/Low | OE# Pin Control | 1       |

| Bit 5  | 25/26 | DIF_3_En | Output Enable    | RW   |         |                 | 1       |

| Bit 4  | 21/22 | DIF_2_En | Output Enable    | RW   |         |                 | 1       |

| Bit 3  |       |          | Reserved         | -    |         | •               | 0       |

| Bit 2  | 16/17 | DIF_1_En | Output Enable    | RW   | Low/Low | OE# Pin Control | 1       |

| Bit 1  | 13/14 | DIF_0_En | Output Enable    | RW   | LOW/LOW |                 | 1       |

| Bit 0  |       | Reserved |                  |      |         | 0               |         |

#### SMBus Table: Output Control Register

| Byte 2 | Pin #    | Name     | Control Function | Туре | 0       | 1               | Default |

|--------|----------|----------|------------------|------|---------|-----------------|---------|

| Bit 7  | Reserved |          |                  |      |         | 0               |         |

| Bit 6  |          |          | Reserved         |      |         |                 | 0       |

| Bit 5  |          |          | Reserved         |      |         |                 | 0       |

| Bit 4  |          |          | Reserved         |      |         |                 | 0       |

| Bit 3  |          |          | Reserved         |      |         |                 | 0       |

| Bit 2  | 39/40    | DIF_7_En | Output Enable    | RW   | Low/Low | OE# Pin Control | 1       |

| Bit 1  |          | Reserved |                  |      | 0       |                 |         |

| Bit 0  | 35/36    | DIF_6_En | Output Enable    | RW   | Low/Low | OE# Pin Control | 1       |

#### SMBus Table: Reserved Register

| Byte 3 | Pin # | Name     | Control Function | Туре | 0 | 1 | Default |

|--------|-------|----------|------------------|------|---|---|---------|

| Bit 7  |       |          | Reserved         |      |   |   | 0       |

| Bit 6  |       |          | Reserved         |      |   |   | 0       |

| Bit 5  |       |          | Reserved         |      |   |   | 0       |

| Bit 4  |       |          | Reserved         |      |   |   | 0       |

| Bit 3  |       |          | Reserved         |      |   |   | 0       |

| Bit 2  |       | Reserved |                  |      |   | 0 |         |

| Bit 1  |       |          | Reserved         |      |   |   | 0       |

| Bit 0  |       |          | Reserved         |      |   |   | 0       |

#### SMBus Table: Reserved Register

| Byte 4 | Pin # | Name     | Control Function | Туре | 0 | 1 | Default |

|--------|-------|----------|------------------|------|---|---|---------|

| Bit 7  |       |          | Reserved         |      |   |   | 0       |

| Bit 6  |       |          | Reserved         |      |   |   | 0       |

| Bit 5  |       |          | Reserved         |      |   |   | 0       |

| Bit 4  |       |          | Reserved         |      |   |   | 0       |

| Bit 3  |       |          | Reserved         |      |   |   | 0       |

| Bit 2  |       | Reserved |                  |      |   | 0 |         |

| Bit 1  |       |          | Reserved         |      |   |   | 0       |

| Bit 0  |       |          | Reserved         |      |   |   | 0       |

#### SMBus Table: Vendor & Revision ID Register

| Byte 5 | Pin # | Name | Control Function | Туре | 0            | 1 | Default |

|--------|-------|------|------------------|------|--------------|---|---------|

| Bit 7  | -     | RID3 |                  | R    |              |   | 0       |

| Bit 6  | -     | RID2 | REVISION ID      | R    | E rev = 0100 |   | 1       |

| Bit 5  | -     | RID1 |                  | R    |              |   | 0       |

| Bit 4  | -     | RID0 |                  | R    |              | 0 |         |

| Bit 3  | -     | VID3 |                  | R    | -            | - | 0       |

| Bit 2  | -     | VID2 | VENDOR ID        | R    | -            | - | 0       |

| Bit 1  | -     | VID1 |                  | R    | -            | - | 0       |

| Bit 0  | -     | VID0 |                  | R    | -            | - | 1       |

#### SMBus Table: DEVICE ID

| Byte 6 | Pin # | Name | Control Function  | Туре | 0              | 1        | Default |

|--------|-------|------|-------------------|------|----------------|----------|---------|

| Bit 7  | -     |      | Device ID 7 (MSB) | R    |                |          | 1       |

| Bit 6  | -     |      | Device ID 6       | R    |                |          | 1       |

| Bit 5  | -     |      | Device ID 5       | R    |                |          | 1       |

| Bit 4  | -     |      | Device ID 4       | R    | 0831 is E5 Hex |          | Х       |

| Bit 3  | -     |      | Device ID 3       | R    |                | s F5 Hex | Х       |

| Bit 2  | -     |      | Device ID 2       | R    | 0001 8         | S FO HEX | Х       |

| Bit 1  | -     |      | Device ID 1       |      |                |          | Х       |

| Bit 0  | -     |      | Device ID 0       | R    |                |          | Х       |

#### SMBus Table: Byte Count Register

| Byte 7 | Pin #      | Name | Control Function                                                                                                                                      | Туре | 0                  | 1                    | Default |

|--------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|----------------------|---------|

| Bit 7  | 7 Reserved |      |                                                                                                                                                       |      |                    |                      | 0       |

| Bit 6  |            |      | Reserved                                                                                                                                              |      |                    |                      | 0       |

| Bit 5  |            |      | Reserved                                                                                                                                              |      |                    |                      |         |

| Bit 4  | -          | BC4  |                                                                                                                                                       | RW   |                    |                      |         |

| Bit 3  | -          | BC3  | Writing to this register configures how many                                                                                                          | RW   | Defaultivalue is 8 | hex so 9 hytes (0 to | 1       |

| Bit 2  | -          | BC2  | Writing to this register configures how many<br>bytes will be read back. RW Default value is 8 hex, so 9 bytes (0<br>8) will be read back by default. |      |                    | 0                    |         |

| Bit 1  | -          | BC1  |                                                                                                                                                       |      | DAUK DY UERUIL     | 0                    |         |

| Bit 0  | -          | BC0  |                                                                                                                                                       | RW   |                    |                      | 0       |

#### SMBus Table: Reserved Register

| Byte 8 | Pin # | Name     | Control Function | Туре | 0 | 1 | Default |

|--------|-------|----------|------------------|------|---|---|---------|

| Bit 7  |       |          | Reserved         |      |   |   | 0       |

| Bit 6  |       | Reserved |                  |      |   | 0 |         |

| Bit 5  |       |          | Reserved         |      |   |   | 0       |

| Bit 4  |       |          | Reserved         |      |   |   | 0       |

| Bit 3  |       |          | Reserved         |      |   |   | 0       |

| Bit 2  |       |          | Reserved         |      |   |   | 0       |

| Bit 1  |       |          | Reserved         |      |   |   | 0       |

| Bit 0  |       |          | Reserved         |      |   |   | 0       |

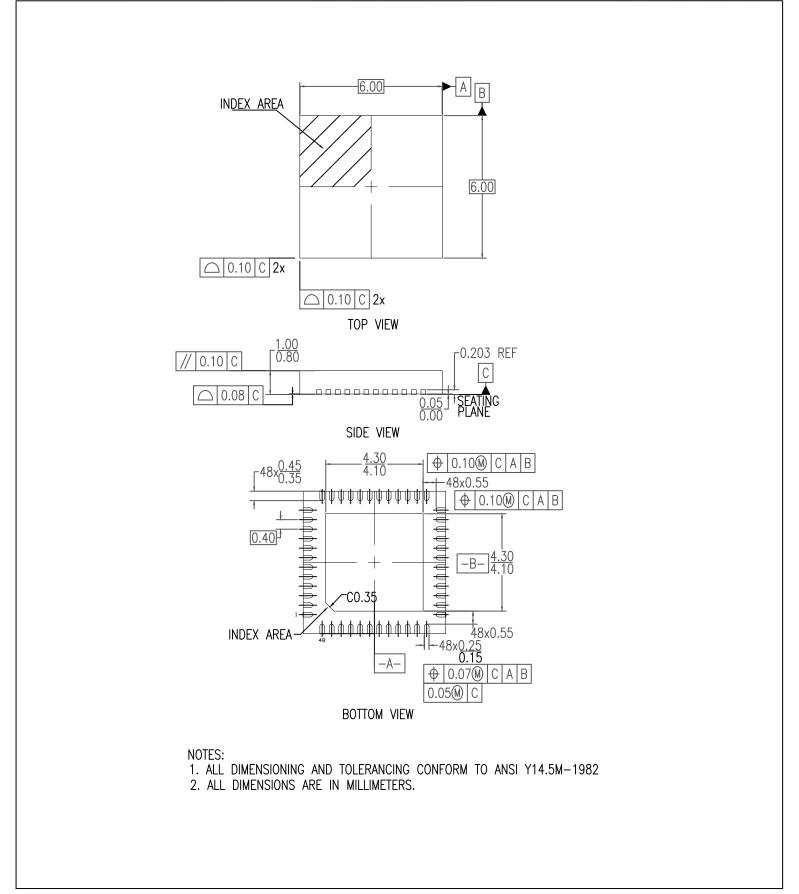

### Package Outline Drawings

The package outline drawings are appended at the end of this document and are accessible from the link below. The package information is the most current data available.

www.idt.com/document/psc/ndndg-48-package-outline-60-x-60-mm-body-040-mm-pitch-qfn-epad-size-420-x-420-mm

# **Ordering Information**

| Orderable Part Number | Package                          | Carrier Type | Temperature    |

|-----------------------|----------------------------------|--------------|----------------|

| 9ZXL0831EKILF         | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Tray         | -40° to +85°C  |

| 9ZXL0831EKILFT        | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Reel         | -40° to +85°C  |

| 9ZXL0851EKILF         | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Tray         | -40° to +85°C  |

| 9ZXL0851EKILFT        | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Reel         | -40° to +85°C  |

| 9ZXL0831EKKLF         | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Tray         | -40° to +105°C |

| 9ZXL0831EKKLFT        | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Reel         | -40° to +105°C |

| 9ZXL0851EKKLF         | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Tray         | -40° to +105°C |

| 9ZXL0851EKKLFT        | 6 x 6 mm, 0.40mm pitch 48-VFQFPN | Reel         | -40° to +105°C |

"LF" designates PB-free configuration, RoHS compliant.

"E" is the device revision designator (will not correlate with the datasheet revision).

### **Marking Diagrams**

- 1. "I" denotes industrial temperature range

- 2. "K" denotes extended temperature range.

- 3. "L" denotes RoHS compliant package.

$\ensuremath{\mathsf{4.``YYWW"}}$  denotes the last two digits of the year and week the part was assembled.

- 5. "COO" denotes country of origin.

- 6. "LOT" denotes the lot number.

### **Revision History**

| Revision Date      | Description of Change                                              |  |  |  |

|--------------------|--------------------------------------------------------------------|--|--|--|

| August 14, 2018    | Updated block diagram.                                             |  |  |  |

| July 17, 2018      | Corrected typos in Byte 1, bits 1 and 2.                           |  |  |  |

| April 12, 2018     | Updated absolute maximum supply voltage rating and VIHSMB to 3.9V. |  |  |  |

| December 1, 2017   | Removed "5V tolerant" reference in pins 6 and 7 descriptions.      |  |  |  |

| September 29, 2017 | Initial release.                                                   |  |  |  |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 USA www.IDT.com

#### Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

Tech Support www.idt.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as "IDT") reserve the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. Integrated Device Technology, Inc. All rights reserved.

6.0 x 6.0 x 0.90 mm Body, Epad 4.2 x 4.2 mm, 0.40mm Pitch NDG48P2, PSC-4212-02, Rev 02, Page 1

© Integrated Device Technology, Inc.

# **48-VFQFPN Package Outline Drawing**

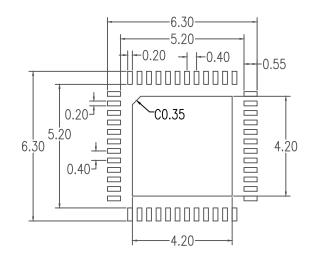

6.0 x 6.0 x 0.90 mm Body, Epad 4.2 x 4.2 mm, 0.40mm Pitch NDG48P2, PSC-4212-02, Rev 02, Page 2

#### RECOMMENDED LAND PATTERN DIMENSION

#### NOTES:

- 1. ALL DIMENSION ARE IN MM. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW. AS VIEWED ON PCB.

- 3. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

| Package Revision History |         |                                                           |

|--------------------------|---------|-----------------------------------------------------------|

| Date Created             | Rev No. | Description                                               |

| July 24, 2018            | Rev 02  | New Format Change QFN to VFQFPN, Recalculate Land Pattern |

| Sept 9, 2014             | Rev 01  | Add Chamfer                                               |

© Integrated Device Technology, Inc.