**TDF8590TH** 2 × 80 W SE (4  $\Omega$ ) or 1 × 160 W BTL (8  $\Omega$ ) class-D amplifier

Rev. 02 — 23 April 2007

**Product data sheet**

### 1. General description

The TDF8590TH is a high-efficiency class-D audio power amplifier with low power dissipation for application in car audio systems. The typical output power is  $2 \times 80$  W into 4  $\Omega$ .

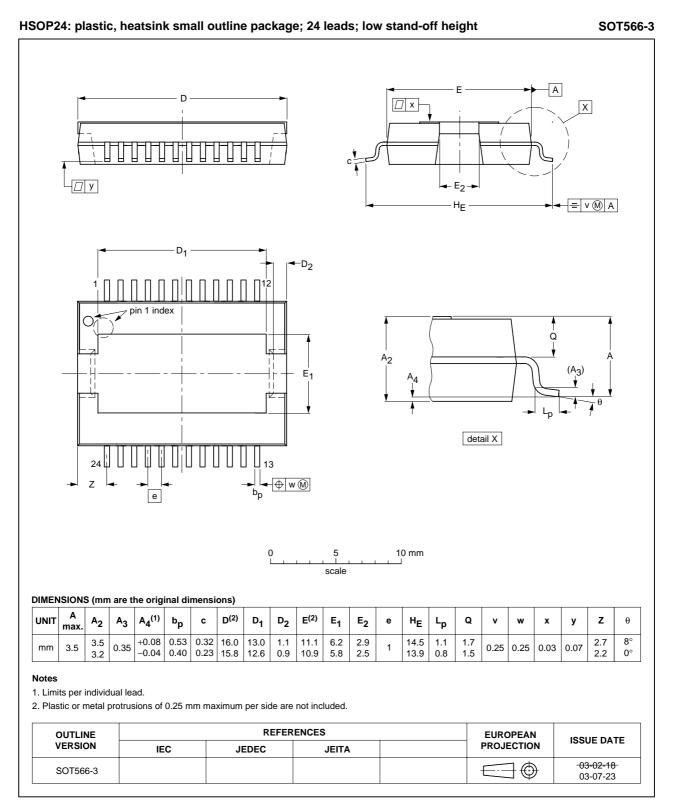

The TDF8590TH is available in an HSOP24 power package with a small internal heat sink. Depending on the supply voltage and load conditions, a small or even no external heat sink is required. The amplifier operates over a wide supply voltage range from  $\pm$ 14 V to  $\pm$ 29 V and consumes a low quiescent current.

### 2. Features

- Zero dead time switching

- Advanced output current protection

- No DC offset induced pop noise at mode transitions

- High efficiency

- Supply voltage from ±14 V to ±29 V

- Low quiescent current

- Usable as a stereo Single-Ended (SE) amplifier or as a mono amplifier in Bridge-Tied Load (BTL)

- Fixed gain of 26 dB in SE and 32 dB in BTL

- High BTL output power: 160 W into 8  $\Omega$ , 120 W into 4  $\Omega$

- Suitable for speakers in the range of 2  $\Omega$  to 8  $\Omega$

- High supply voltage ripple rejection

- Internal oscillator or synchronized to an external clock

- Full short-circuit proof outputs across load and to supply lines

- Thermal foldback and thermal protection

### 3. Ordering information

| Table 1. | Orde | ring | inf | formati | ion |

|----------|------|------|-----|---------|-----|

|          |      |      |     |         |     |

| Type number | Package |                                                                            |          |

|-------------|---------|----------------------------------------------------------------------------|----------|

|             | Name    | Description                                                                | Version  |

| TDF8590TH   | HSOP24  | plastic, heatsink small outline package; 24 leads;<br>low stand-off height | SOT566-3 |

2  $\times$  80 W SE (4  $\Omega$ ) or 1  $\times$  160 W BTL (8  $\Omega$ ) class-D amplifier

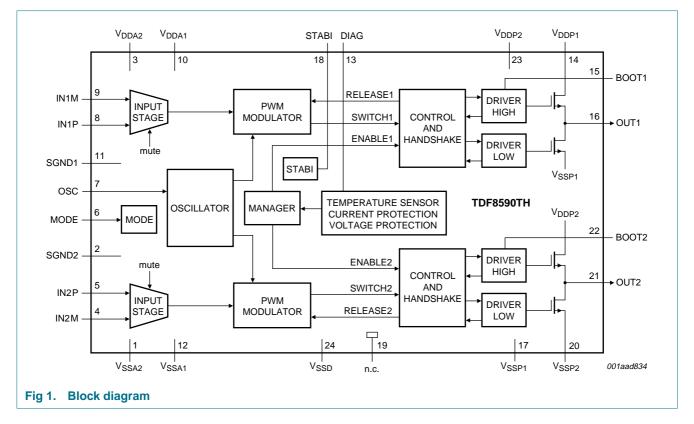

### 4. Block diagram

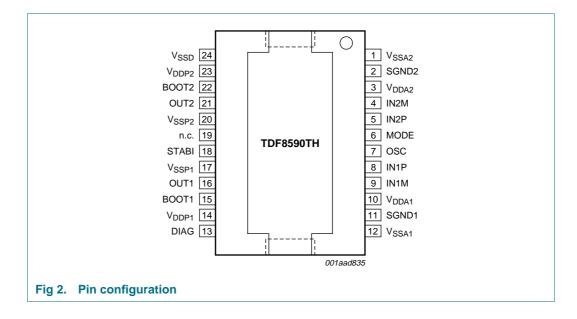

### 5. Pinning information

### 5.1 Pinning

2  $\times$  80 W SE (4  $\Omega)$  or 1  $\times$  160 W BTL (8  $\Omega)$  class-D amplifier

### 5.2 Pin description

| Table 2.          | Pin description |                                                    |

|-------------------|-----------------|----------------------------------------------------|

| Symbol            | Pin             | Description                                        |

| V <sub>SSA2</sub> | 1               | negative analog supply voltage for channel 2       |

| SGND2             | 2               | signal ground for channel 2                        |

| V <sub>DDA2</sub> | 3               | positive analog supply voltage for channel 2       |

| IN2M              | 4               | negative audio input for channel 2                 |

| IN2P              | 5               | positive audio input for channel 2                 |

| MODE              | 6               | mode selection input: standby, mute or operating   |

| OSC               | 7               | oscillator frequency adjustment or tracking input  |

| IN1P              | 8               | positive audio input for channel 1                 |

| IN1M              | 9               | negative audio input for channel 1                 |

| V <sub>DDA1</sub> | 10              | positive analog supply voltage for channel 1       |

| SGND1             | 11              | signal ground for channel 1                        |

| V <sub>SSA1</sub> | 12              | negative analog supply voltage for channel 1       |

| DIAG              | 13              | diagnostic for activated current protection        |

| V <sub>DDP1</sub> | 14              | positive power supply voltage for channel 1        |

| BOOT1             | 15              | bootstrap capacitor for channel 1                  |

| OUT1              | 16              | PWM output from channel 1                          |

| V <sub>SSP1</sub> | 17              | negative power supply voltage for channel 1        |

| STABI             | 18              | decoupling of internal stabilizer for logic supply |

| n.c.              | 19              | not connected                                      |

| V <sub>SSP2</sub> | 20              | negative power supply voltage for channel 2        |

| OUT2              | 21              | PWM output from channel 2                          |

| BOOT2             | 22              | bootstrap capacitor for channel 2                  |

| V <sub>DDP2</sub> | 23              | positive power supply voltage for channel 2        |

| V <sub>SSD</sub>  | 24              | negative digital supply voltage <sup>[1]</sup>     |

[1] The heatsink is internally connected to pin  $V_{SSD}$ .

## 6. Functional description

### 6.1 Introduction

The TDF8590TH is a dual channel audio power amplifier using class-D technology. The audio input signal is converted into a Pulse Width Modulated (PWM) signal via an analog input stage and PWM modulator. To enable the output power transistors to be driven, this digital PWM signal is applied to a control and handshake block and driver circuits for both the high-side and low-side. An external 2nd-order low-pass filter converts the PWM output signal to an analog audio signal across the loudspeakers.

#### **2** $\times$ 80 W SE (4 $\Omega$ ) or 1 $\times$ 160 W BTL (8 $\Omega$ ) class-D amplifier

The TDF8590TH contains two independent amplifier channels with a differential input stage, high output power, high efficiency (90 %), low distortion and a low quiescent current. The amplifier channels can be connected in the following configurations:

- Mono Bridge-Tied Load (BTL) amplifier

- Dual Single-Ended (SE) amplifiers

The TDF8590TH also contains circuits common to both channels such as the oscillator, all reference sources, the mode functionality and a digital timing manager. For protection a thermal foldback, temperature, current and voltage protection are built in.

### 6.2 Mode selection

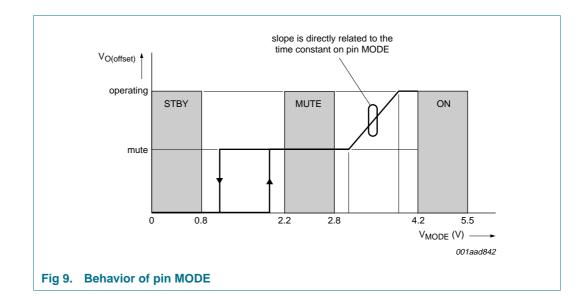

The TDF8590TH can be switched in three operating modes via pin MODE:

- · Standby mode; the amplifiers are switched off to achieve a very low supply current

- Mute mode; the amplifiers are switching idle (50 % duty cycle), but the audio signal at the output is suppressed by disabling the VI-converter input stages

- Operating mode; the amplifiers are fully operational with output signal

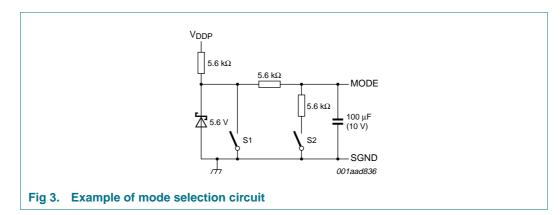

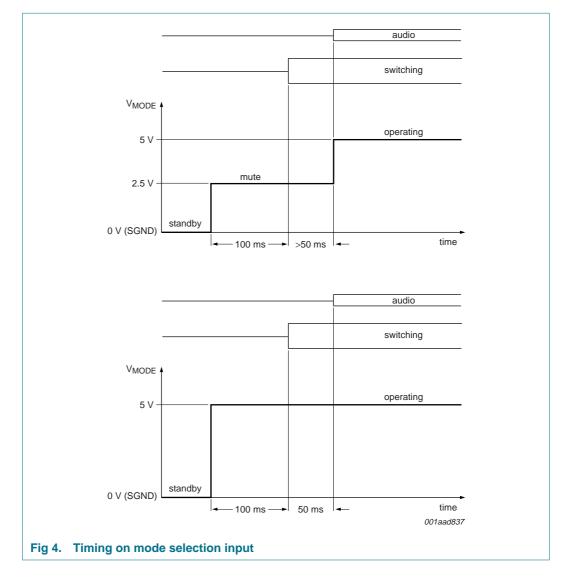

The input stage (see Figure 1) contributes to the DC offset measured at the amplifier output. To avoid pop noise the DC output offset voltage should be increased gradually at a mode transition from mute to operating, or vice versa, by limiting the  $dV_{MODE}/dt$  on pin MODE, resulting in a small  $dV_{O(offset)}/dt$  for the DC output offset voltage. The required time constant for a gradually increase of the DC output offset voltage between mute and operating is generated via an RC network on pin MODE. An example of a switching circuit for driving pin MODE is illustrated in Figure 3 and explained in Table 3.

#### Table 3.Mode selection

| S1     | S2     | Mode selection |

|--------|--------|----------------|

| closed | closed | Standby mode   |

| closed | open   | Standby mode   |

| open   | closed | Mute mode      |

| open   | open   | Operating mode |

### 2 $\times$ 80 W SE (4 $\Omega$ ) or 1 $\times$ 160 W BTL (8 $\Omega$ ) class-D amplifier

The value of the RC time constant should be dimensioned for 500 ms. If the 100  $\mu$ F capacitor is left out of the application the voltage on pin MODE will be applied with a much smaller time constant, which might result in audible pop noises during start-up (depending on DC output offset voltage and used loudspeaker).

In order to fully charge the coupling capacitors at the inputs, the amplifier will remain automatically in Mute mode for approximately 150 ms before switching to Operating mode. A complete overview of the start-up timing is given in Figure 4.

### 6.3 Pulse width modulation frequency

The output signal of the amplifier is a PWM signal with a switching frequency that is set by an external resistor  $R_{ext(OSC)}$  connected between pins OSC and  $V_{SSA}$ . An optimum setting for the carrier frequency is between 300 kHz and 350 kHz. An external resistor  $R_{ext(OSC)}$  of 30 k $\Omega$  sets the frequency to 310 kHz.

If two or more class-D amplifiers are used in the same audio application, it is recommended to synchronize the switching frequency of all devices to an external clock (see Section 12.3).

### 6.4 Protections

The following protections are included in TDF8590TH:

- Thermal Foldback (TF)

- OverTemperature Protection (OTP)

- OverCurrent Protection (OCP)

- Window Protection (WP)

- Supply voltage protections

- UnderVoltage Protection (UVP)

- OverVoltage Protection (OVP)

- Unbalance Protection (UBP)

The reaction of the device on the different fault conditions differs per protection and is described in <u>Section 6.4.1</u> to <u>Section 6.4.5</u>.

### 6.4.1 Thermal foldback

If the junction temperature  $T_j > 145$  °C, then the TF gradually reduced the gain, resulting in a smaller output signal and less dissipation. At  $T_j = 155$  °C the outputs are fully muted.

### 6.4.2 Overtemperature protection

If  $T_i > 160$  °C, then the OTP will shut down the power stage immediately.

### 6.4.3 Overcurrent protection

The OCP will detect a short-circuit between the loudspeaker terminals or if one of the loudspeaker terminals is short-circuited to one of the supply lines.

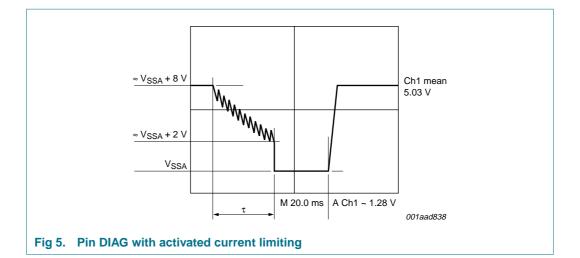

If the output current tends to exceed the maximum output current of 8 A, the output voltage of the TDF8590TH will be regulated to a level where the maximum output current is limited to 8 A while the amplifier outputs remain switching, the amplifier does not shut down. When this active current limiting continues longer than a time  $\tau$  (see Figure 5) the capacitor on pin DIAG is discharged below a threshold value and the TDF8590TH shuts down. Activation of current limiting and the triggering of the OCP is observed at pin DIAG (see Figure 5).

A maximum value for the capacitor on pin DIAG is 47 pF. The reference voltage on pin DIAG is  $V_{SSA}$ . Pin DIAG should not be connected to an external pull-up.

2  $\times$  80 W SE (4  $\Omega$ ) or 1  $\times$  160 W BTL (8  $\Omega$ ) class-D amplifier

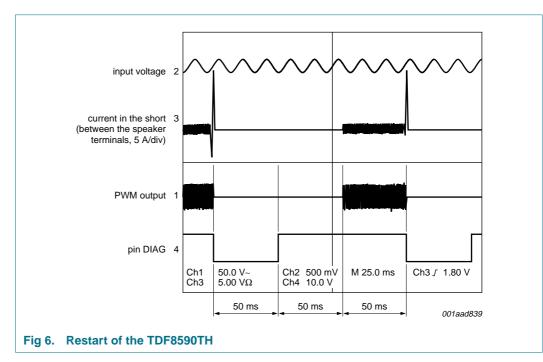

When the loudspeaker terminals are short-circuited and the OCP is triggered the TDF8590TH is switched off completely and will try to restart every 100 ms (see Figure 6):

- 50 ms after switch off pin DIAG will be released

- 100 ms after switch off the amplifier will return to mute

- 150 ms after switch off the amplifier will return to operation. If the short-circuit condition is still present after this time this cycle will be repeated. The average dissipation will be low because of the small duty cycle

A short of the loudspeaker terminals to one of the supply lines will also trigger the activation of the OCP and the amplifier will shut down. During restart the window protection will be activated. As a result the amplifier will not start up after 100 ms and pin DIAG will remain LOW until the short to the supply lines is removed.

### 6.4.4 Window protection

The WP checks the conditions at the output terminals of the power stage and is activated:

- During the start-up sequence, when pin MODE is switched from standby to mute. In the event of a short-circuit at one of the output terminals to V<sub>DD</sub> or V<sub>SS</sub> the start-up procedure is interrupted and the TDF8590TH waits until the short to the supply lines has been removed. Because the test is done before enabling the power stages, no large currents will flow in the event of a short-circuit.

- When the amplifier is completely shut down due to activation of the OCP because a short to one of the supply lines is made, then during restart (after 100 ms) the window protection will be activated. As a result the amplifier will not start up until the short to the supply lines is removed.

### 6.4.5 Supply voltage protections

If the supply voltage drops below  $\pm 12.5$  V, the UVP circuit is activated and the TDF8590TH switch-off will be silent and without pop noise. When the supply voltage rises above  $\pm 12.5$  V, the TDF8590TH is restarted again after 100 ms.

If the supply voltage exceeds  $\pm 33$  V the OVP circuit is activated and the power stages will shut down. It is re-enabled as soon as the supply voltage drops below  $\pm 33$  V. So in this case no timer of 100 ms is started. The maximum operating supply voltage is  $\pm 29$  V and if the supply voltage is above the maximal allowable voltage of  $\pm 34$  V (see Section 7), the TDF8590TH can be damaged, irrespective of an activated OVP. See Section 12.6 "Pumping effects" for more information about the use of the OVP.

An additional UBP circuit compares the positive analog ( $V_{DDA}$ ) and the negative analog ( $V_{SSA}$ ) supply voltages and is triggered if the voltage difference between them exceeds the unbalance threshold level, which is expressed as follows:

$$V_{th(unb)} \approx 0.15 \times (V_{DDA} - V_{SSA})$$

V

When the supply voltage difference  $V_{DDA} - V_{SSA}$  exceeds  $V_{th(unb)}$ , the TDF8590TH switches off and is restarted again after 100 ms.

Example: With a symmetrical supply of  $V_{DDA} = 20$  V and  $V_{SSA} = -20$  V, the unbalance protection circuit will be triggered if the unbalance exceeds approximately 6 V.

In Table 4 an overview is given of all protections and the effect on the output signal.

| Protection name | Complete shut down | Restart directly | Restart every 100 ms | DIAG |

|-----------------|--------------------|------------------|----------------------|------|

| TF              | Ν                  | Y <u>[1]</u>     | Ν                    | Ν    |

| OTP             | Y                  | Y[2]             | N <sup>[2]</sup>     | Ν    |

| OCP             | N <sup>[3]</sup>   | Y <u>[3]</u>     | N[ <u>3]</u>         | Υ    |

| WP              | Y <u>[4]</u>       | Y                | Ν                    | Υ    |

| UVP             | Υ                  | Ν                | Y                    | Ν    |

| OVP             | Υ                  | Y                | Ν                    | Ν    |

| UBP             | Y                  | Ν                | Υ                    | Ν    |

#### Table 4.Overview protections TDF8590TH

[1] Amplifier gain will depend on junction temperature and heat sink size.

[2] Thermal foldback will influence restart timing depending on heat sink size.

- [3] Only complete shut down of amplifier in case of a short-circuit. In all other cases current limiting resulting in clipping output signal.

- [4] Fault condition detected during (every) transition between standby-to-mute and during restart after activation of OCP (short to one of the supply lines).

### 6.5 Diagnostic output

Pin DIAG is pulled LOW when the OCP is triggered. With a continuous shorted load a switching pattern in the voltage on pin DIAG is observed (see Figure 6). A permanent LOW on pin DIAG indicates a short to the supply lines whereas a shorted load causes a switching DIAG pin (see Section 6.4.3).

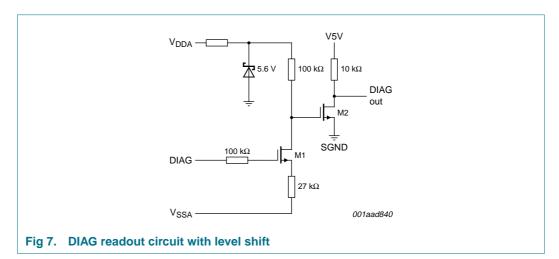

The pin DIAG reference voltage is  $V_{SSA}$ . Pin DIAG should not be connected to an external pull-up. An example of a circuit to read out and level shift the diagnostic data is given in Figure 7. V5V represents a logic supply that is used in the application by the microprocessor that reads out the DIAG data.

### 6.6 Differential inputs

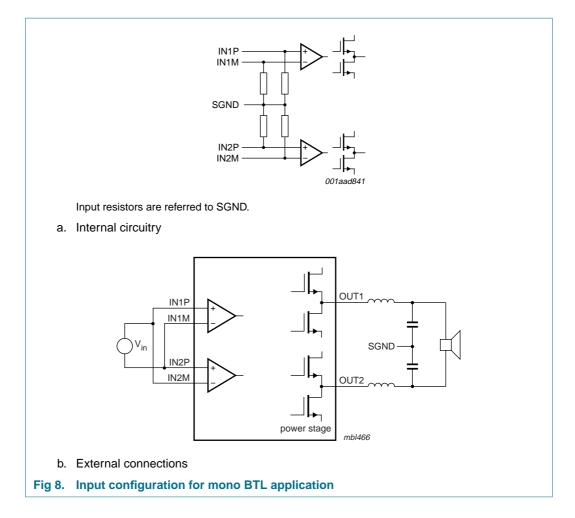

For a high Common Mode Rejection Ratio (CMRR) and a maximum of flexibility in the application, the audio inputs are fully differential. By connecting the inputs anti-parallel the phase of one of the channels can be inverted, so that a load can be connected between the two output filters. In this case the system operates as a mono BTL amplifier.

The input configuration for a mono BTL application is illustrated in Figure 8.

In the stereo SE configuration it is also recommended to connect the two differential inputs in anti-phase. This has advantages for the current handling of the power supply at low signal frequencies (supply pumping).

## **TDF8590TH**

### 2 $\times$ 80 W SE (4 $\Omega$ ) or 1 $\times$ 160 W BTL (8 $\Omega$ ) class-D amplifier

## 7. Limiting values

### Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol             | Parameter                          | Conditions                                                                               | Min          | Max          | Unit                     |

|--------------------|------------------------------------|------------------------------------------------------------------------------------------|--------------|--------------|--------------------------|

| V <sub>DD</sub>    | supply voltage                     | $V_{DDP1}$ and $V_{DDA1}$ referred to SGND1; $V_{DDP2}$ and $V_{DDA2}$ referred to SGND2 | -0.3         | +34          | V                        |

| $V_{SS}$           | negative supply voltage            | $V_{SSP1}$ and $V_{SSA1}$ referred to SGND1; $V_{SSP2}$ and $V_{SSA2}$ referred to SGND2 | -34          | +0.3         | V                        |

| V <sub>P</sub>     | supply voltage                     |                                                                                          | -0.3         | +66          | V                        |

| I <sub>OSM</sub>   | non-repetitive peak output current |                                                                                          | -            | 12           | А                        |

| T <sub>stg</sub>   | storage temperature                |                                                                                          | -55          | +150         | °C                       |

| T <sub>amb</sub>   | ambient temperature                |                                                                                          | -40          | +85          | °C                       |

| Tj                 | junction temperature               |                                                                                          | -40          | +150         | °C                       |

| V <sub>BOOT1</sub> | voltage on pin BOOT1               | referred to OUT1                                                                         | <u>[1]</u> 0 | 14           | V                        |

| V <sub>BOOT2</sub> | voltage on pin BOOT2               | referred to OUT2                                                                         | <u>[1]</u> 0 | 14           | V                        |

| V <sub>STABI</sub> | voltage on pin STABI               | referred to $V_{SSD}$                                                                    | [2] _        | 14           | V                        |

| TDF8590TH_2        |                                    |                                                                                          |              | © NXP B.V. 2 | 007. All rights reserved |

### 2 $\times$ 80 W SE (4 $\Omega)$ or 1 $\times$ 160 W BTL (8 $\Omega)$ class-D amplifier

| Symbol            | Parameter           | Conditions                   | Min                    | Max                    | Unit |

|-------------------|---------------------|------------------------------|------------------------|------------------------|------|

| V <sub>MODE</sub> | voltage on pin MODE | referred to SGND2            | 0                      | 8                      | V    |

| V <sub>OSC</sub>  | voltage on pin OSC  | referred to V <sub>SSD</sub> | 0                      | 40                     | V    |

| V <sub>IN1M</sub> | voltage on pin IN1M | referred to SGND1            | -5                     | +5                     | V    |

| V <sub>IN1P</sub> | voltage on pin IN1P | referred to SGND1            | -5                     | +5                     | V    |

| V <sub>IN2M</sub> | voltage on pin IN2M | referred to SGND2            | -5                     | +5                     | V    |

| V <sub>IN2P</sub> | voltage on pin IN2P | referred to SGND2            | -5                     | +5                     | V    |

| V <sub>DIAG</sub> | voltage on pin DIAG | referred to V <sub>SSD</sub> | <u>3]</u> 0            | 9                      | V    |

| Vo                | output voltage      |                              | V <sub>SSP</sub> – 0.3 | V <sub>DDP</sub> + 0.3 | V    |

#### Table 5. Limiting values ... continued

[1] Pin BOOT should not be loaded by any other means than the boot capacitor. Shorting pin BOOT to V<sub>SS</sub> will damage the device.

[2] Pin STABI should not be loaded by an external circuit. Shorting pin STABI to a voltage source or V<sub>SS</sub> will damage the device.

Pin DIAG should not be connected to a voltage source or to a pull-up resistor. An example of a circuit that can be used to read out [3] diagnostic data is given in Figure 7.

#### Thermal characteristics 8.

| Table 6.             | Thermal characteristics                     |             |     |      |

|----------------------|---------------------------------------------|-------------|-----|------|

| Symbol               | Parameter                                   | Conditions  | Тур | Unit |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |             | 1.1 | K/W  |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 35  | K/W  |

#### **Static characteristics** 9.

#### **Static characteristics** Table 7.

$V_P = \pm 27 V$ ;  $f_{osc} = 310 \text{ kHz}$ ;  $T_{amb} = -40 \degree C$  to  $+85 \degree C$ ;  $T_i = -40 \degree C$  to  $+150 \degree C$ ; unless otherwise specified.

| Symbol              | Parameter                     | Conditions                                       | Mi              | n Typ | Max | Unit |

|---------------------|-------------------------------|--------------------------------------------------|-----------------|-------|-----|------|

| Supply              |                               |                                                  |                 |       |     |      |

| VP                  | supply voltage                |                                                  | [ <u>1]</u> ±1  | 4 ±27 | ±29 | V    |

| I <sub>q(tot)</sub> | total quiescent current       | no load, no filter, no snubber network connected | -               | 50    | 65  | mA   |

| I <sub>stb</sub>    | standby current               | $T_j = -40 \ ^{\circ}C$ to +85 $^{\circ}C$       | -               | 150   | 500 | μA   |

| Mode selec          | ct input; pin MODE (reference | e to SGND2)                                      |                 |       |     |      |

| I <sub>MODE</sub>   | current on pin MODE           | $V_{MODE} = 5.5 V$                               | -               | 100   | 300 | μA   |

| V <sub>MODE</sub>   | voltage on pin mode           | Standby mode                                     | <u>[2][3]</u> 0 | -     | 0.8 | V    |

|                     |                               | Mute mode                                        | [2][3] 2.2      | 2 -   | 2.8 | V    |

|                     |                               | Operating mode                                   | [2][3] 4.2      | 2 -   | 6   | V    |

| Diagnostic          | output; pin DIAG (reference   | to V <sub>SSD</sub> )                            |                 |       |     |      |

| V <sub>OL</sub>     | LOW-level output voltage      | activated OCP or WP                              | [4] _           | -     | 0.8 | V    |

| V <sub>OH</sub>     | HIGH-level output voltage     | no activated OCP or WP                           | [4] _           | 8.4   | 9   | V    |

| Audio inpu          | ts; pins IN1M, IN1P (referenc | e to SGND1), IN2P and IN2M (ref                  | erence to S     | GND2) |     |      |

| VI                  | input voltage                 |                                                  | [2] _           | 0     | -   | V    |

### 2 $\times$ 80 W SE (4 $\Omega$ ) or 1 $\times$ 160 W BTL (8 $\Omega$ ) class-D amplifier

#### Table 7. Static characteristics ...continued

$V_P = \pm 27 \text{ V}$ ;  $f_{osc} = 310 \text{ kHz}$ ;  $T_{amb} = -40 \degree C$  to  $+85 \degree C$ ;  $T_j = -40 \degree C$  to  $+150 \degree C$ ; unless otherwise specified.

| •                      | unio                                    | . )                                                  |              |      |     |      |

|------------------------|-----------------------------------------|------------------------------------------------------|--------------|------|-----|------|

| Symbol                 | Parameter                               | Conditions                                           | Min          | Тур  | Max | Unit |

| Amplifier ou           | utputs; pins OUT1 and OUT2              |                                                      |              |      |     |      |

| V <sub>O(offset)</sub> | output offset voltage                   | SE; mute                                             | -            | -    | 20  | mV   |

|                        |                                         | SE; operating                                        | <u>[5]</u>   | -    | 170 | mV   |

|                        |                                         | BTL; mute                                            | -            | -    | 30  | mV   |

|                        |                                         | BTL; operating                                       | <u>[5]</u>   | -    | 240 | mV   |

| Stabilizer of          | utput; pin STABI (reference to          | o V <sub>SSP1</sub> )                                |              |      |     |      |

| Vo                     | output voltage                          | mute and operating; with respect to $V_{\mbox{SSD}}$ | 11           | 12.5 | 14  | V    |

| Temperatur             | e protection                            |                                                      |              |      |     |      |

| T <sub>prot</sub>      | protection temperature                  |                                                      | -            | 160  | 180 | °C   |

| $T_{act(th_{fold})}$   | thermal foldback activation temperature | closed loop SE voltage gain<br>reduced with 6 dB     | <u>6</u> 145 | 150  | -   | °C   |

[1] The circuit is DC adjusted at V<sub>P</sub> =  $\pm 12.5$  V to  $\pm 30$  V.

[2] Refers to usage in a symmetrical supply application (see <u>Section 12.7</u>). In an asymmetrical supply application the SGND voltage should be defined by an external circuit.

[3] The transition between Standby and Mute mode contains hysteresis, while the slope of the transition between Mute and Operating mode is determined by the time constant on pin MODE (see Figure 9).

[4] Pin DIAG should not be connected to an external pull-up.

[5] DC output offset voltage is applied to the output during the transition between Mute and Operating mode in a gradual way. The dV<sub>O(offset</sub>/dt caused by any DC output offset is determined by the time constant on pin MODE.

[6] At a junction temperature of approximately T<sub>act(th\_fold)</sub> - 5 °C the gain reduction will commence and at a junction temperature of approximately T<sub>act(th\_fold)</sub> + 5 °C the amplifier mutes.

### **10.** Dynamic characteristics

### **10.1** Dynamic characteristics (SE)

### Table 8. Dynamic characteristics (SE)

$V_P = \pm 27 \text{ V}$ ;  $R_L = 4 \Omega$ ;  $f_i = 1 \text{ kHz}$ ;  $f_{osc} = 310 \text{ kHz}$ ;  $R_{s(L)} < 0.1 \Omega [1]$ ;  $T_{amb} = -40 \degree \text{C}$  to  $+85 \degree \text{C}$ ;  $T_j = -40 \degree \text{C}$  to  $+150 \degree \text{C}$ ; unless otherwise specified. See Section 12.7 for the SE application schematics. The 2nd-order demodulation filter coil is referred to as L and the capacitor as C.

| Symbol              | Parameter                       | Conditions                                                                                                                                                                                                  |     | Min | Тур  | Max | Unit |

|---------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-----|------|

| Po                  | output power                    | $ \begin{array}{l} L=10 \ \mu \text{H}; \ C=1 \ \mu \text{F}; \ \text{T}_{j}=85 \ ^{\circ}\text{C}; \ \text{R}_{L}=2 \ \Omega; \\ \text{V}_{\text{P}}=\pm18 \ \text{V}; \ \text{THD}=0.5 \ \% \end{array} $ | [2] | -   | 48   | -   | W    |

|                     |                                 | $\label{eq:L} \begin{array}{l} L=10~\mu\text{H};~C=1~\mu\text{F};~T_{j}=85~^{\circ}\text{C};~\text{R}_{L}=2~\Omega;\\ \text{V}_{\text{P}}=\pm18~\text{V};~\text{THD}=10~\% \end{array}$                     | [2] | -   | 60   | -   | W    |

|                     |                                 | L = 22 μH; C = 680 nF; T <sub>j</sub> = 85 °C;<br>R <sub>L</sub> = 4 Ω; V <sub>P</sub> = $\pm$ 27 V; THD = 0.5 %                                                                                            | [2] | -   | 65   | -   | W    |

|                     |                                 | $ \begin{array}{l} L = 22 \; \mu H; \; C = 680 \; nF; \; T_{j} = 85 \; ^{\circ}C; \\ R_{L} = 4 \; \Omega; \; V_{P} = \pm 27 \; V; \; THD = 10 \; \% \end{array} $                                           | [2] | -   | 80   | -   | W    |

| I <sub>OM</sub>     | peak output current             | current limiting, see Section 6.4.3                                                                                                                                                                         |     | 8   | -    | -   | А    |

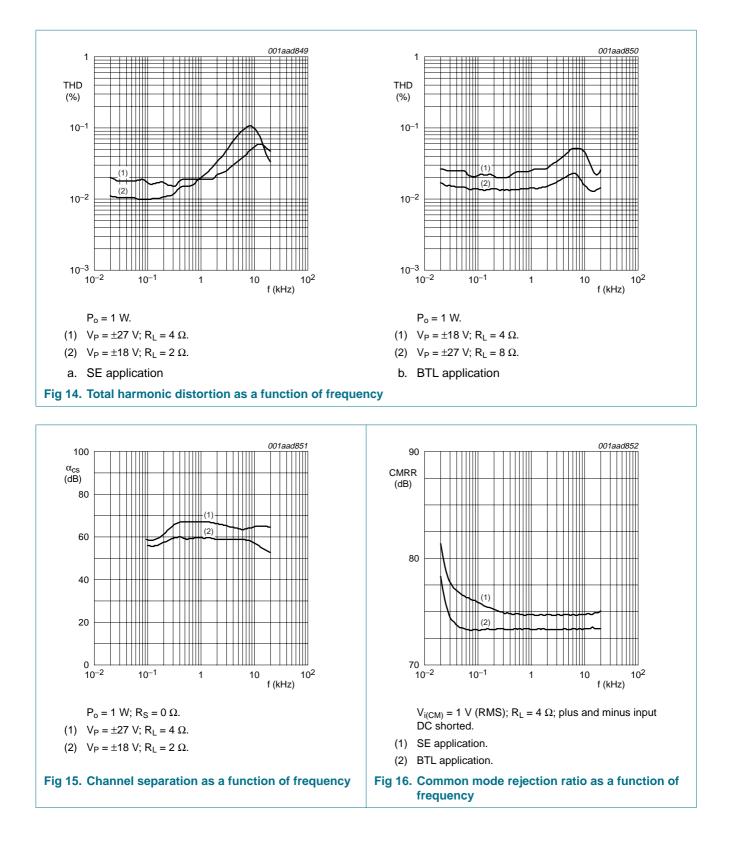

| THD                 | total harmonic distortion       | $P_o = 1 W; f_i = 1 kHz$                                                                                                                                                                                    | [3] | -   | 0.02 | 0.2 | %    |

|                     |                                 | $P_{o} = 1 W; f_{i} = 10 \text{ kHz}$                                                                                                                                                                       | [3] | -   | 0.10 | -   | %    |

| G <sub>v(cl)</sub>  | closed-loop voltage gain        |                                                                                                                                                                                                             |     | 25  | 26   | 27  | dB   |

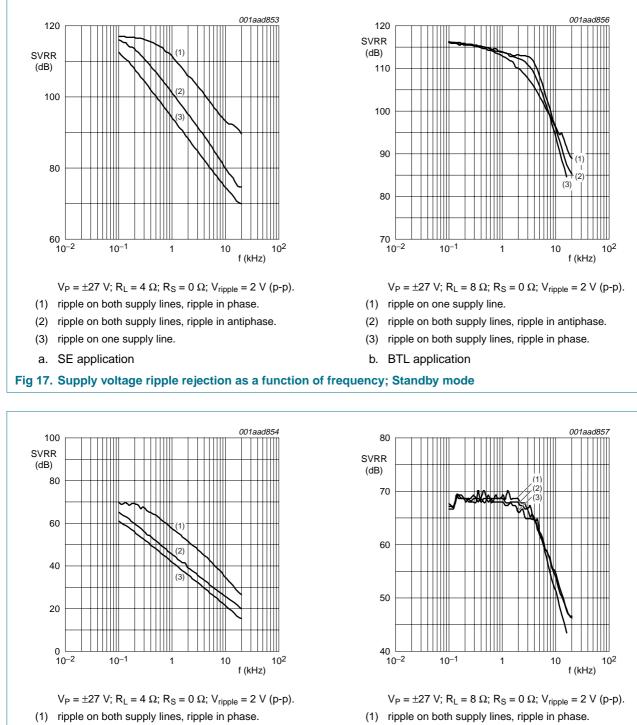

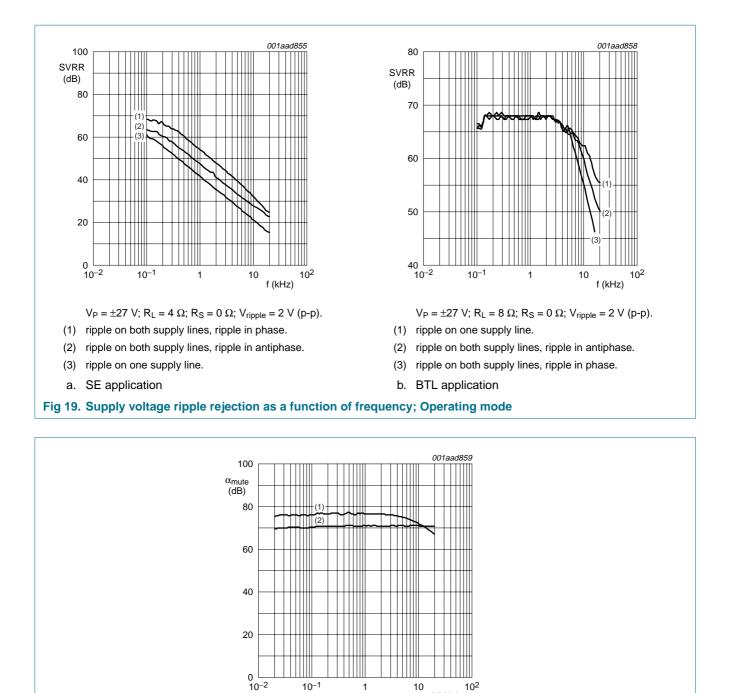

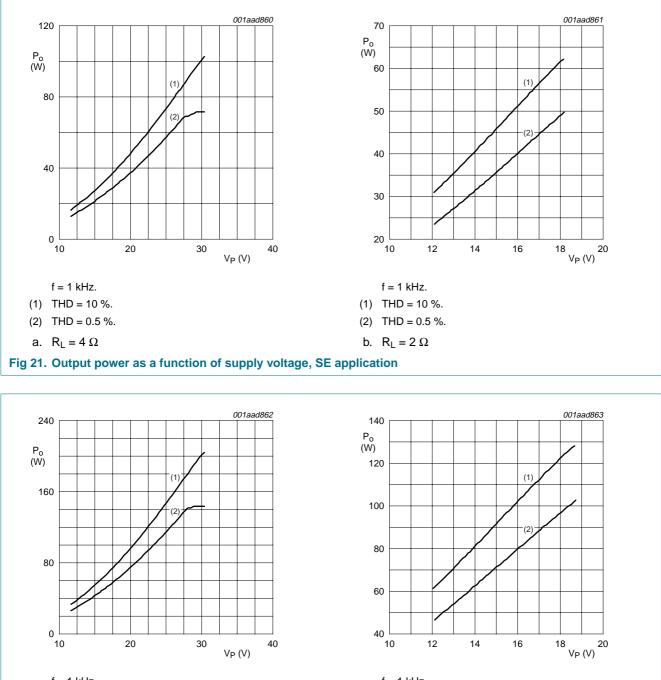

| SVRR                | supply voltage rejection ratio  | operating; f <sub>ripple</sub> = 100 Hz                                                                                                                                                                     | [4] | -   | 55   | -   | dB   |

|                     |                                 | operating; f <sub>ripple</sub> = 1 kHz                                                                                                                                                                      | [4] | 40  | 50   | -   | dB   |

|                     |                                 | mute; $f_{ripple} = 1 \text{ kHz}$                                                                                                                                                                          | [4] | -   | 55   | -   | dB   |

|                     |                                 | standby; f <sub>ripple</sub> = 100 Hz                                                                                                                                                                       | [4] | -   | 80   | -   | dB   |

| Z <sub>i(dif)</sub> | differential input<br>impedance | between the input pins INP and INM                                                                                                                                                                          |     | 45  | 68   | -   | kΩ   |

| V <sub>n(o)</sub>   | noise output voltage            | operating; V <sub>P</sub> = $\pm 27$ V; R <sub>S</sub> = 0 $\Omega$                                                                                                                                         | [5] | -   | 170  | -   | μV   |

|                     |                                 | operating; V <sub>P</sub> = $\pm$ 18 V; R <sub>S</sub> = 0 $\Omega$                                                                                                                                         | [5] | -   | 145  | -   | μV   |

|                     |                                 | mute; $V_P = \pm 27 V$                                                                                                                                                                                      | [6] | -   | 125  | -   | μV   |

|                     |                                 | mute; $V_P = \pm 18 V$                                                                                                                                                                                      | [6] | -   | 85   | -   | μV   |

| $\alpha_{cs}$       | channel separation              | $P_o = 1 \text{ W}; \text{ R}_S = 0 \Omega; \text{ f}_i = 1 \text{ kHz}$                                                                                                                                    |     | -   | 70   | -   | dB   |

| ∆G <sub>v</sub>     | voltage gain difference         |                                                                                                                                                                                                             |     | -   | -    | 1   | dB   |

| $\alpha_{mute}$     | mute attenuation                | $f_i = 1 \text{ kHz}; V_{in} = 1 \text{ V} (\text{RMS value})$                                                                                                                                              |     | -   | 73   | -   | dB   |

| CMRR                | common mode rejection ratio     | $f_{i(CM)} = 1 \text{ kHz}; V_{i(CM)} = 1 \text{ V} (RMS \text{ value})$                                                                                                                                    | [7] | -   | 75   | -   | dB   |

[1]  $R_{s(L)}$  is the series resistance of inductor of low-pass LC filter in the application.

[2] Output power is measured indirectly; based on R<sub>DSon</sub> measurement (see Section 12.3).

[3] THD is measured in a bandwidth of 22 Hz to 20 kHz, AES brick wall. Maximum limit is guaranteed but may not be 100 % tested.

[5] Frequency bandwidth B = 22 Hz to 20 kHz, AES brick wall (see Section 12.4).

[6] B = 22 Hz to 20 kHz, AES brick wall, independent of  $R_S$  (see Section 12.4).

[7]  $V_{i(CM)}$  is the input common mode voltage.

### 2 $\times$ 80 W SE (4 $\Omega)$ or 1 $\times$ 160 W BTL (8 $\Omega)$ class-D amplifier

### 10.2 Dynamic characteristics (BTL)

#### Table 9. Dynamic characteristics (BTL)

$V_P = \pm 27 \text{ V}$ ;  $R_L = 8 \Omega$ ;  $f_i = 1 \text{ kHz}$ ;  $f_{osc} = 310 \text{ kHz}$ ;  $R_{s(L)} < 0.1 \Omega [1]$ ;  $T_{amb} = -40 \degree \text{C}$  to  $+85 \degree \text{C}$ ;  $T_j = -40 \degree \text{C}$  to  $+150 \degree \text{C}$ ; unless otherwise specified. See <u>Section 12.7</u> for the BTL application schematics. The 2nd order demodulation filter coil is referred to as L and the capacitor as C.

| Symbol              | Parameter                       | Conditions                                                                                                                                                         | Min           | Тур  | Max | Unit |

|---------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|-----|------|

| Po                  | output power                    | L = 10 $\mu$ H, C = 1 $\mu$ F; T <sub>j</sub> = 85 °C; R <sub>L</sub> = 4 $\Omega$ ;<br>V <sub>P</sub> = ±18 V; THD = 0.5 %                                        | [2] _         | 97   | -   | W    |

|                     |                                 | $\label{eq:L} \begin{array}{l} L=10 \ \mu H; \ C=1 \ \mu F; \ T_{j}=85 \ ^{\circ}C; \ R_{L}=4 \ \Omega; \\ V_{P}=\pm 18 \ V; \ THD=10 \ \% \end{array}$            | [2] _         | 120  | -   | W    |

|                     |                                 | $ \begin{array}{l} L = 22 \; \mu H; \; C = 680 \; nF; \; T_{j} = 85 \; ^{\circ}C; \\ R_{L} = 8 \; \Omega; \; V_{P} = \pm 27 \; V; \; THD = 0.5 \; \% \end{array} $ | [2] _         | 130  | -   | W    |

|                     |                                 | L = 22 μH; C = 680 nF; T <sub>j</sub> = 85 °C;<br>R <sub>L</sub> = 8 Ω; V <sub>P</sub> = $\pm$ 27 V; THD = 10 %                                                    | [2] _         | 160  | -   | W    |

| I <sub>OM</sub>     | peak output current             | current limiting, see Section 6.4.3                                                                                                                                | 8             | -    | -   | А    |

| THD                 | total harmonic distortion       | $P_o = 1 W; f_i = 1 kHz$                                                                                                                                           | <u>[3]</u> _  | 0.02 | 0.2 | %    |

|                     |                                 | $P_{o} = 1 \text{ W}; f_{i} = 10 \text{ kHz}$                                                                                                                      | [3] _         | 0.15 | -   | %    |

| G <sub>v(cl)</sub>  | closed-loop voltage gain        |                                                                                                                                                                    | 31            | 32   | 33  | dB   |

| SVRR                | supply voltage rejection ratio  | operating; f <sub>ripple</sub> = 100 Hz                                                                                                                            | [4] _         | 68   | -   | dB   |

|                     |                                 | operating; f <sub>ripple</sub> = 1 kHz                                                                                                                             | <u>[4]</u> 50 | 68   | -   | dB   |

|                     |                                 | mute; $f_{ripple} = 1 \text{ kHz}$                                                                                                                                 | <u>[4]</u> _  | 68   | -   | dB   |

|                     |                                 | standby; f <sub>ripple</sub> = 100 Hz                                                                                                                              | [4]           | 80   | -   | dB   |

| Z <sub>i(dif)</sub> | differential input<br>impedance | measured between the input pins INP and INM                                                                                                                        | 22            | 34   | -   | kΩ   |

| V <sub>n(o)</sub>   | noise output voltage            | operating; Vp = $\pm 27$ V; R <sub>S</sub> = 0 $\Omega$                                                                                                            | [5] _         | 240  | -   | μV   |

|                     |                                 | operating; $V_{P} = \pm 18 \text{ V}; \text{ R}_{S} = 0 \Omega$                                                                                                    | [5] _         | 200  | -   | μV   |

|                     |                                 | mute; $V_P = \pm 27 V$                                                                                                                                             | [6] _         | 180  | -   | μV   |

|                     |                                 | mute; $V_P = \pm 18 V$                                                                                                                                             | [6] _         | 125  | -   | μV   |

| $\alpha_{mute}$     | mute attenuation                | f <sub>i</sub> = 1 kHz; V <sub>in</sub> = 1 V (RMS value)                                                                                                          | -             | 70   | -   | dB   |

| CMRR                | common mode rejection ratio     | $f_{i(CM)}$ = 1 kHz; $V_{i(CM)}$ = 1 V (RMS value)                                                                                                                 | -             | 75   | -   | dB   |

[1]  $R_{s(L)}$  is the series resistance of inductor of low-pass LC filter in the application.

[2] Output power is measured indirectly; based on R<sub>DSon</sub> measurement (see <u>Section 12.3</u>).

[3] THD is measured in a bandwidth of 22 Hz to 20 kHz, AES brick wall. Maximum limit is guaranteed but may not be 100 % tested.

[5] B = 22 Hz to 20 kHz, AES brick wall (see <u>Section 12.4</u>).

[6] B = 22 Hz to 20 kHz, AES brick wall, independent on  $R_S$  (see Section 12.4).

2  $\times$  80 W SE (4  $\Omega)$  or 1  $\times$  160 W BTL (8  $\Omega)$  class-D amplifier

### **11. Switching characteristics**

### Table 10. Switching characteristics

$V_{DD} = 27 V$ ;  $T_{amb} = -40 \circ C$  to  $+85 \circ C$ ;  $T_j = -40 \circ C$  to  $+150 \circ C$ ; unless otherwise specified.

|                                    | ,                                           | -                                              |     |     |     |      |

|------------------------------------|---------------------------------------------|------------------------------------------------|-----|-----|-----|------|

| Symbol                             | Parameter                                   | Conditions                                     | Min | Тур | Max | Unit |

| Internal of                        | scillator                                   |                                                |     |     |     |      |

| f <sub>osc</sub>                   | oscillator frequency                        | typical; $R_{ext(OSC)} = 30.0 \text{ k}\Omega$ | 290 | 310 | 344 | kHz  |

|                                    |                                             | maximum; $R_{ext(OSC)}$ = 15.4 k $\Omega$      | -   | 560 | -   | kHz  |

|                                    |                                             | minimum; $R_{ext(OSC)}$ = 48.9 k $\Omega$      | -   | 200 | -   | kHz  |

| External o                         | scillator or frequency tracking             |                                                |     |     |     |      |

| V <sub>H(OSC)min</sub>             | minimum HIGH-level voltage on pin OSC       | referred to SGND                               | 4   | -   | 6   | V    |

| V <sub>L(OSC)max</sub>             | maximum LOW-level voltage on pin OSC        | referred to SGND                               | 0   | -   | 1   | V    |

| $\Delta \mathbf{f}_{\text{track}}$ | tracking frequency range                    |                                                | 210 | -   | 600 | kHz  |

| Drain sou                          | rce on-state resistance of the output trans | istors                                         |     |     |     |      |

| R <sub>DSon(Is)</sub>              | low-side drain-source on-state resistance   | $T_j = 85 \ ^{\circ}C; \ I_{DS} = 6 \ A$       | -   | 250 | 275 | mΩ   |

|                                    |                                             | $T_j = 25 \ ^{\circ}C; \ I_{DS} = 6 \ A$       | -   | 190 | 210 | mΩ   |

| R <sub>DSon(hs)</sub>              | high-side drain-source on-state resistance  | $T_j = 85 \ ^{\circ}C; \ I_{DS} = 6 \ A$       | -   | 300 | 330 | mΩ   |

|                                    |                                             | $T_j = 25 \ ^{\circ}C; \ I_{DS} = 6 \ A$       | -   | 220 | 240 | mΩ   |

|                                    |                                             |                                                |     |     |     |      |

## **12.** Application information

### **12.1 BTL application**

When using the power amplifier in a mono BTL application the inputs of both channels must be connected in parallel and the phase of one of the inputs must be inverted (see Figure 7). The loudspeaker is connected between the outputs of the two single-ended demodulation filters.

### 12.2 Output power estimation

The achievable output powers in SE and BTL applications can be estimated using the following expressions:

SE:

$$P_{o(0.5\%)} = \frac{\left(\frac{R_L}{R_L + R_{DSon(hs)} + R_{s(L)}} \times V_P \times (1 - t_{w(min)} \times f_{osc})\right)^2}{2 \times R_L}$$

W

BTL:

$$P_{o(0.5\%)} = \frac{\left(\frac{R_L}{R_L + (R_{DSon(hs)} + R_{DSon(ls)}) + 2R_{s(L)}} \times 2V_P \times (1 - t_{w(min)} \times f_{osc})\right)^2}{2 \times R_L} W$$

### 2 $\times$ 80 W SE (4 $\Omega)$ or 1 $\times$ 160 W BTL (8 $\Omega)$ class-D amplifier

Peak output current, internally limited to 8 A:

SE:

$$I_{OM} = \frac{V_P \times (1 - t_{w(min)} \times f_{osc})}{R_L + R_{DSon(hs)} + R_{s(L)}} A$$

BTL:

$$I_{OM} = \frac{2V_P - (1 - t_{w(min)} \times f_{osc})}{R_L + (R_{DSon(hs)} + R_{DSon(ls)}) + 2R_{s(L)}} A$$

Variables:

R<sub>L</sub> = load resistance

$R_{s(L)}$  = series resistance of the filter coil

R<sub>DSon(hs)</sub> = high side drain source on-state resistance (temperature dependent)

R<sub>DSon(Is)</sub> = low side drain source on-state resistance (temperature dependent)

fosc = oscillator frequency

t<sub>w(min)</sub> = minimum pulse width (typical 150 ns, temperature dependent)

$V_P$  = supply voltage [or 0.5 ( $V_{DD}$  +  $V_{SS}$ )]

$P_{o(0.5\%)}$  = output power at the onset of clipping

$I_{OM}$  should be below 8 A (see <u>Section 7</u>).  $I_{OM}$  is the sum of the current through the load and the ripple current. The value of the ripple current is dependent on the coil inductance and voltage drop over the coil.

### 12.3 External clock

If two or more class-D amplifiers are used it is recommended that all devices run at the same switching frequency. This can be realized by connecting all OSC pins together and feed them from an external oscillator.

The internal oscillator requires an external R<sub>ext(OSC)</sub> and C<sub>ext(OSC)</sub> between pins OSC and V<sub>SSA</sub>. For application of an external oscillator it is necessary to force OSC to a DC level above SGND. The internal oscillator is disabled and the PWM modulator will switch with the external frequency. The duty cycle of the external clock should be between 47.5 % and 52.5 %.

The noise contribution of the internal oscillator is supply voltage dependent. In low noise applications running at high supply voltage an external low noise oscillator is recommended.

### 12.4 Noise

Noise should be measured using a high-order low-pass filter with a cut-off frequency of 20 kHz. The standard audio band pass filters used in audio analyzers do not suppress the residue of the carrier frequency sufficiently to ensure a reliable measurement of the audible noise. Noise measurements should preferably be carried out using AES 17 (Brick Wall) filters or the Audio Precision AUX 0025 filter, which was designed especially for measuring switching (class-D) amplifiers.

### **2** $\times$ 80 W SE (4 $\Omega$ ) or 1 $\times$ 160 W BTL (8 $\Omega$ ) class-D amplifier

### 12.5 Heat sink requirements

In some applications it may be necessary to connect an external heat sink to the TDF8590TH. The thermal foldback activates on  $T_j = 140$  °C. The expression below shows the relationship between the maximum power dissipation before activation of the thermal foldback and the total thermal resistance from junction to ambient:

$$R_{th(j-a)} = \frac{T_j - T_{amb}}{P} \ \Omega$$

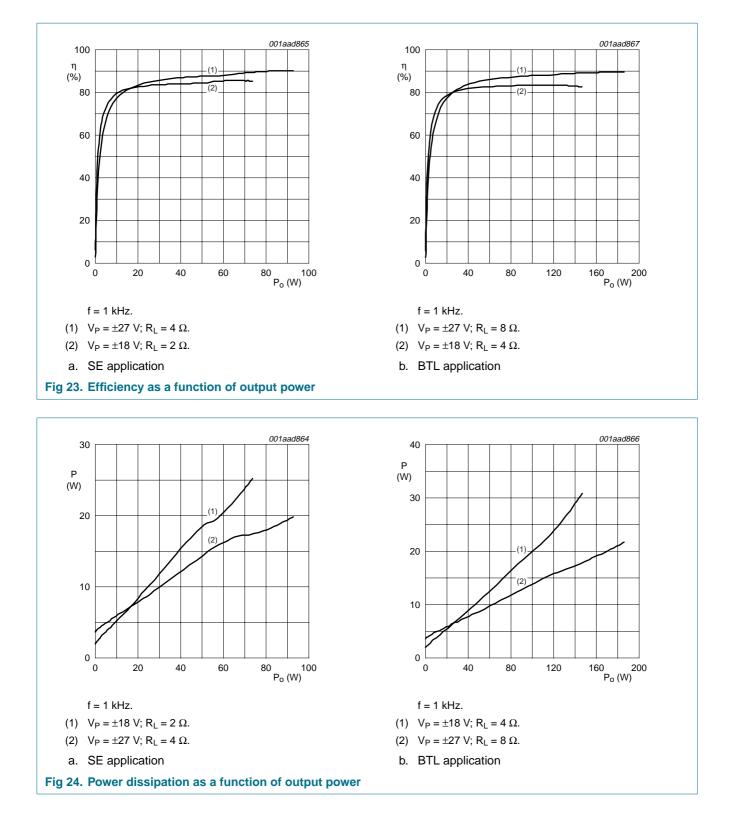

The power dissipation is determined by the efficiency  $\eta$  of the TDF8590TH. The efficiency measured as a function of output power is given in Figure 23. The power dissipation can be derived as function of output power (see Figure 24).

Example of a heatsink calculation for the 8  $\Omega$  BTL application with ±27 V supply:

- An audio signal with a crest factor of 10 (the ratio between peak power and average power is 10 dB), this means that the average output power is 1/10th of the peak power

- The peak RMS output power level is 130 W (0.5 % THD level)

- The average power is  $0.1 \times 130$  W = 13 W

- The dissipated power at an output power of 13 W is approximately 5 W

- The total R<sub>th(i-a)</sub> = (140 85) / 5 = 11 K/W, if the maximum expected T<sub>amb</sub> = 85 °C

- The total thermal resistance R<sub>th(j-a)</sub> = R<sub>th(j-c)</sub> + R<sub>th(c-h)</sub> + R<sub>th(h-a)</sub>

- R<sub>th(j-c)</sub> = 1.1 K/W, R<sub>th(c-h)</sub> = 0.5 K/W to 1 K/W (dependent on mounting), so R<sub>th(h-a)</sub> would then be: 11 (1.1 + 1) = 8.9 K/W

### 12.6 Pumping effects

When the TDF8590TH is used in a SE configuration, a so-called pumping effect can occur. During one switching interval, energy is taken from one supply (e.g.  $V_{DDA1}$ ), while a part of that energy is delivered back to the other supply line (e.g.  $V_{SSA1}$ ) and visa versa. When the voltage supply source cannot sink energy, the voltage across the output capacitors of that voltage supply source will increase: the supply voltage is pumped to higher levels. The voltage increase caused by the pumping effect depends on:

- Speaker impedance

- Supply voltage

- Audio signal frequency

- Value of decoupling capacitors on supply lines

- Source and sink currents of other channels

### 2 $\times$ 80 W SE (4 $\Omega)$ or 1 $\times$ 160 W BTL (8 $\Omega)$ class-D amplifier

The pumping effect should not cause a malfunction of either the audio amplifier and/or the voltage supply source. For instance, this malfunction can be caused by triggering of the UVP, OVP or UBP of the amplifier. Best remedy for pumping effects is to use the TDF8590TH in a mono full-bridge application. In case of dual half-bridge application adapt the power supply (e.g. increase supply decoupling capacitors).

### **12.7 Application schematics**

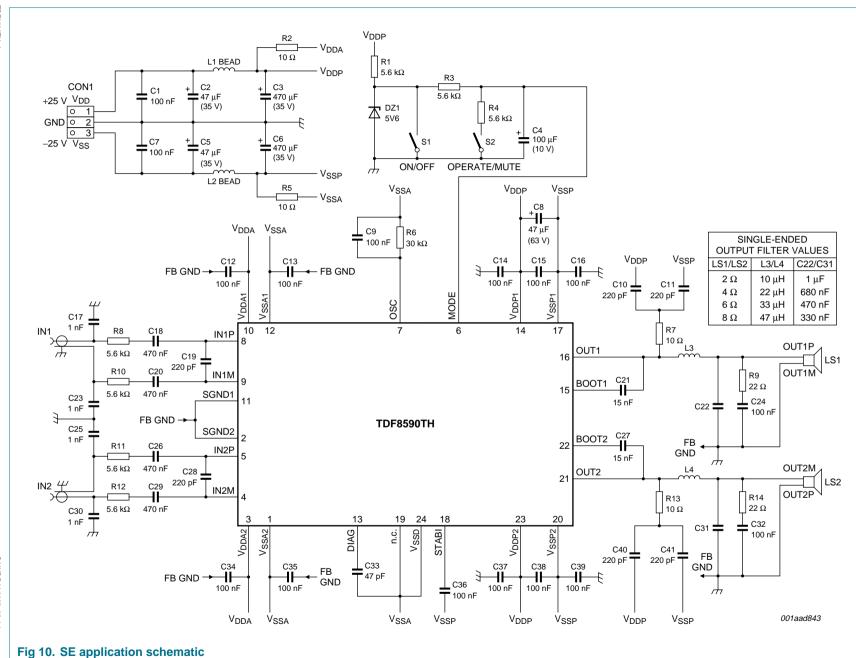

For SE application (see Figure 10):

- A solid ground plane around the TDF8590TH is necessary to prevent emission

- 100 nF SMD capacitors must be placed as close as possible to the power supply pins of the TDF8590TH

- The heatsink of the HSOP24 package of the TDF8590TH is connected to pin V<sub>SSD</sub>

- The external heatsink must be connected to the ground plane

- Use a thermal conductive, electrically isolating Sil-Pad between the backside of the TDF8590TH and the external heatsink

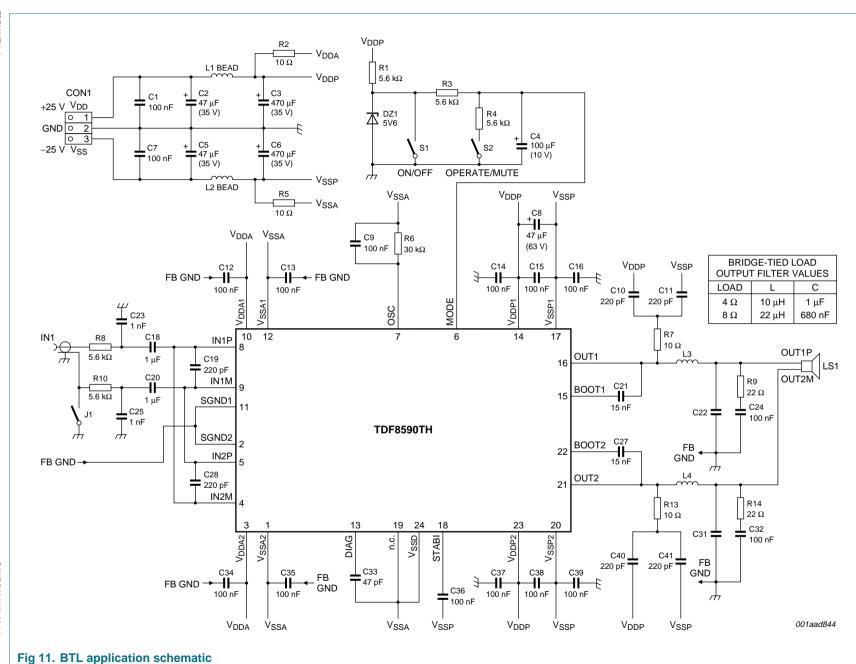

For BTL application (see Figure 11):

- A solid ground plane around the TDF8590TH is necessary to prevent emission

- 100 nF SMD capacitors must be placed as close as possible to the power supply pins of the TDF8590TH

- The heatsink of the HSOP24 package of the TDF8590TH is connected to pin V<sub>SSD</sub>

- The external heatsink must be connected to the ground plane

- Use a thermal conductive, electrically isolating Sil-Pad between the backside of the TDF8590TH and the external heatsink

- The differential inputs enable the best system level audio performance with unbalanced signal sources. In case of hum due to floating inputs connect the shielding or source ground to the amplifier ground. The jumper J1 is open on set level and is closed on the stand-alone demo board

- Minimum total required capacity per power supply line is 3300 μF

Rev. 02 — 23 April 2007

NXP Semiconductors

**TDF8590TH** 2 × 80 W SE (4 Ω) or 1 × 160 W BTL (8 Ω) class-D amplifier

Rev. 02 — 23 April 2007

NXP Semiconductors

**TDF8590TH** 2 × 80 W SE (4 Ω) or 1 × 160 W BTL (8 Ω) class-D amplifier

2  $\times$  80 W SE (4  $\Omega)$  or 1  $\times$  160 W BTL (8  $\Omega)$  class-D amplifier

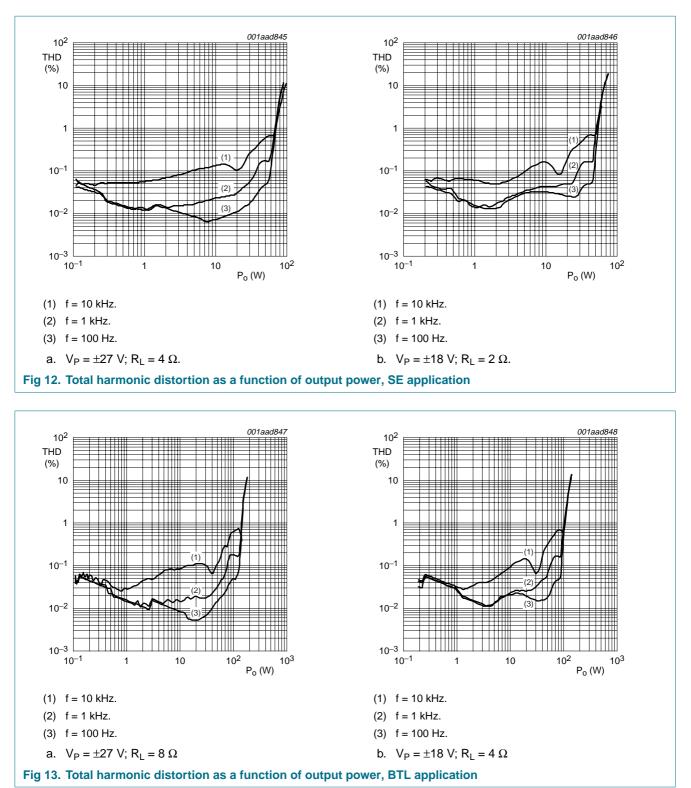

### 12.8 Curves measured in reference design

TDF8590TH\_2 Product data sheet

### 2 $\times$ 80 W SE (4 $\Omega$ ) or 1 $\times$ 160 W BTL (8 $\Omega$ ) class-D amplifier

# **TDF8590TH**

### 2 $\times$ 80 W SE (4 $\Omega)$ or 1 $\times$ 160 W BTL (8 $\Omega)$ class-D amplifier

- (2) ripple on both supply lines, ripple in antiphase.

- (3) ripple on one supply line.

- b. BTL application

Fig 18. Supply voltage ripple rejection as a function of frequency; Mute mode

(2) ripple on both supply lines, ripple in antiphase.

(3) ripple on one supply line.

a. SE application

# **TDF8590TH**

### 2 $\times$ 80 W SE (4 $\Omega)$ or 1 $\times$ 160 W BTL (8 $\Omega)$ class-D amplifier

#### $V_I = 1 V (RMS).$

- (1) SE application;  $V_P = \pm 27 \text{ V}$ ;  $R_L = 4 \Omega$ .

- (2) BTL application; V<sub>P</sub> =  $\pm 18$  V; R<sub>L</sub> = 4  $\Omega$ .

Fig 20. Mute attenuation as a function of frequency

f (kHz)

# **TDF8590TH**

2  $\times$  80 W SE (4  $\Omega$ ) or 1  $\times$  160 W BTL (8  $\Omega$ ) class-D amplifier

f = 1 kHz. f = 1 kHz.

(1) THD = 10 %.

(1) THD = 10 %.

(2) THD = 0.5 %.

(2) THD = 0.5 %.

a.  $R_L = 8 \Omega$  b.  $R_L = 4 \Omega$

Fig 22. Output power as a function of supply voltage, BTL application

# **TDF8590TH**

### 2 $\times$ 80 W SE (4 $\Omega)$ or 1 $\times$ 160 W BTL (8 $\Omega)$ class-D amplifier

## **TDF8590TH**

2  $\times$  80 W SE (4  $\Omega)$  or 1  $\times$  160 W BTL (8  $\Omega)$  class-D amplifier

### 13. Package outline

### Fig 25. Package outline SOT566-3 (HSOP24)

## 14. Revision history

| Document ID    | Release date                                                                        | Data sheet status                              | Change notice            | Supersedes                    |  |  |

|----------------|-------------------------------------------------------------------------------------|------------------------------------------------|--------------------------|-------------------------------|--|--|

| TDF8590TH_2    | 20070423                                                                            | Product data sheet                             | -                        | TDF8590TH_1                   |  |  |

| Modifications: |                                                                                     | of this data sheet has been i<br>miconductors. | redesigned to comply wit | h the new identity guideline: |  |  |

|                | <ul> <li>Legal texts</li> </ul>                                                     | have been adapted to the n                     | ew company name whe      | e appropriate.                |  |  |

|                | <ul> <li>All I<sup>2</sup>C-relation</li> </ul>                                     | ted items were removed.                        |                          |                               |  |  |

|                | • Figure 7 wa                                                                       | as modified.                                   |                          |                               |  |  |

|                | <ul> <li>In <u>Section 2 "Features"</u> 80 W BTL was changed into 120 W.</li> </ul> |                                                |                          |                               |  |  |

| TDF8590TH 1    | 20060613                                                                            | Preliminary data sheet                         | -                        | -                             |  |  |

## **15. Legal information**

### 15.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### **15.2 Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### 15.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

malfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

### 15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### 16. Contact information

For additional information, please visit: http://www.nxp.com

For sales office addresses, send an email to: salesaddresses@nxp.com

## **TDF8590TH**

2  $\times$  80 W SE (4  $\Omega)$  or 1  $\times$  160 W BTL (8  $\Omega)$  class-D amplifier

### **17. Contents**

| 1                                                                                                                   | General description                                                                                                                                                                                                                                                                                                                                                                     | . 1                                                                                          |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 2                                                                                                                   | Features                                                                                                                                                                                                                                                                                                                                                                                | . 1                                                                                          |

| 3                                                                                                                   | Ordering information                                                                                                                                                                                                                                                                                                                                                                    | . 1                                                                                          |

| 4                                                                                                                   | Block diagram                                                                                                                                                                                                                                                                                                                                                                           | . 2                                                                                          |

| 5                                                                                                                   | Pinning information                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

| 5.1                                                                                                                 | Pinning                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 5.2                                                                                                                 | Pin description                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 6                                                                                                                   | Functional description                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 6.1                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 6.2                                                                                                                 | Mode selection                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 6.3                                                                                                                 | Pulse width modulation frequency                                                                                                                                                                                                                                                                                                                                                        | . 5                                                                                          |

| 6.4                                                                                                                 | Protections                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 6.4.1                                                                                                               | Thermal foldback                                                                                                                                                                                                                                                                                                                                                                        | . 6                                                                                          |

| 6.4.2                                                                                                               | Overtemperature protection                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 6.4.3                                                                                                               | Overcurrent protection                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 6.4.4                                                                                                               | Window protection                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 6.4.5                                                                                                               | Supply voltage protections                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 6.5                                                                                                                 | Diagnostic output                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 6.6                                                                                                                 | Differential inputs                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

| 7                                                                                                                   | Limiting values                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                           |

| 8                                                                                                                   | Thermal characteristics                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                                           |

| 9                                                                                                                   | Static characteristics                                                                                                                                                                                                                                                                                                                                                                  | 11                                                                                           |

| 10                                                                                                                  | Dynamic characteristics                                                                                                                                                                                                                                                                                                                                                                 | 13                                                                                           |

| 10.1                                                                                                                | Dynamic characteristics (SE)                                                                                                                                                                                                                                                                                                                                                            | 13                                                                                           |

| 10.2                                                                                                                | Dynamic characteristics (BTL)                                                                                                                                                                                                                                                                                                                                                           | 14                                                                                           |