# **TCPP03-M20**

# Datasheet

# USB-C protection for dual role power (DRP)

QFN-20L 4.0 x 4.0 x 0.75 mm

#### Product labels

| Product      | status link                   |

|--------------|-------------------------------|

| TCPF         | P03-M20                       |

| Order code   | TCPP03-M20                    |

|              |                               |

| Expans       | ion board                     |

| X-NUCLE      | O-DRP1M1                      |

|              |                               |

| SW expansion | for STM32Cube                 |

| X-CUE        | BE-TCPP                       |

|              |                               |

| STM32-UCPD c | ompanion chips <sup>(1)</sup> |

|              | 122004 CTM221 E               |

STM32G0, STM32G4, STM32L5, STM32U5

1. Any MCU with USB-C PD SW stack

#### I2C address 0110 10x (LSB = 'x')

#### **Features**

- Externally programmable VBUS OVP (over voltage protection) and OCP (over current protection) for provider and consumer power paths with fast turn-off

- Two integrated N-MOSFETs gate drivers for VBUS OVP and OCP

- Very low power in "unattached" state during DRP toggling: 3 µA max. at 125 °C

- Compliant with PPS (programmable power supply) for fast charging, up to 100 W

- Integrated discharge on VBUS and VCONN

- Current sense on VBUS with analog output

- ESD protection for CC1, CC2, compliant with IEC 61000-4-2 Level 4 (±8 kV contact discharge, ±15 kV air discharge)

- V<sub>CONN</sub> OCP (100 mW max), OVP (6 V max)

- Over voltage protection on CC lines against short-to-V<sub>BUS</sub>

- Over temperature protection (150 °C typ.)

- Integrated "Dead Battery" management

- I<sup>2</sup>C communication, with two I<sup>2</sup>C addresses available

- Junction temperature from -40 °C to 125 °C

- Compliant with USB-C power delivery standard 3.1, standard power range (SPR), up to 100 W

- ECOPACK2 compliant

## **Applications**

- USB type-C power delivery used in dual role power (DRP) or dual role data (DRD) configuration

- USB type-C used in Sink configuration requiring current sense on V<sub>BUS</sub>

- USB type-C sourcing devices

#### **Description**

The TCPP03-M20 is an MCU companion chip enabling cost-effective USB-C power delivery dual role power implementation. It provides protections and functionalities to safely comply with the USB-C Power Delivery specification.

TCPP03-M20 drives external N-MOSFETs on VBUS connector pin in the source and sink power path for over voltage and over current protection. It provides an analog current sense output accessible for an MCU ADC, thus minimizing system cost.

The TCPP03-M20 features 24 V tolerant ESD protection as per IEC61000-4-2 level 4 on USB type-C connector communication channel pins (CC). The TCPP03-M20 provides overvoltage protection on CC1 and CC2 pins when these pins are subjected to short circuit with the VBUS pin that may happen when removing the USB type-C cable from its receptacle.

TCPP03-M20 helps to minimize power consumption during DRP toggling states thanks to its three programmable power modes allowing a power consumption as low as 3  $\mu$ A maximum, up to 125 °C and thanks to enable pin that wake up the MCU.

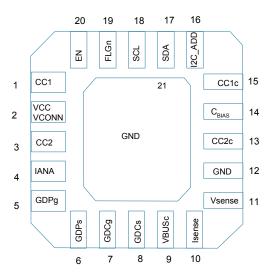

# 1 Pinout and functions

57

#### Figure 1. QFN-20L 4.0 x 4.0 x 0.75 mm (top view)

#### Table 1. Pinout and functions

| Name               | Pin # | Туре           | Description                                                                   |

|--------------------|-------|----------------|-------------------------------------------------------------------------------|

| CC1                | 1     | Input / Output | Configuration channel 1 pin on power delivery controller side.                |

| VCC_VCONN          | 2     | Power          | Power supply for $V_{CONN}$ power pin. Connect to 3.3 V or 5.5 V.             |

| CC2                | 3     | Input / Output | Configuration channel 2 pin on power delivery controller side.                |

| I <sub>ANA</sub>   | 4     | Output         | V <sub>BUS</sub> current analog measurement.                                  |

| GDPg               | 5     | Output         | Gate driver provider: gate pin of external N-channel MOSFET on source path.   |

| GDPs               | 6     | Input          | Gate driver provider: source pin of external N-channel MOSFET on source path. |

| GDCg               | 7     | Output         | Gate driver consumer: gate pin of external N-channel MOSFET on sink path.     |

| GDCs               | 8     | Input          | Gate driver consumer: source pin of external N-channel MOSFET on sink path.   |

| VBUSc              | 9     | Input          | VBUS connector side.                                                          |

| I <sub>sense</sub> | 10    | Input          | VBUS current measurement.                                                     |

| V <sub>sense</sub> | 11    | Input          | VBUS voltage measurement.                                                     |

| GND                | 12    | GND            | Ground.                                                                       |

| CC2c               | 13    | Input / Output | Configuration channel 2 pin on USB-C connector side.                          |

| C <sub>BIAS</sub>  | 14    | Output         | ESD capacitor                                                                 |

| CC1c               | 15    | Input / Output | Configuration channel 1 pin on USB-C connector side.                          |

| I2C_ADD            | 16    | Input          | Least significant bit on I2C address. Connected to GND or 1.8 V / 3.3 V.      |

| SDA                | 17    | Input / Output | Serial data line on I2C bus                                                   |

| SCL                | 18    | Input / Output | Serial clock line on I2C bus                                                  |

| FLGn               | 19    | Output         | Open-drain output flag (active low). Floating when not connected.             |

| EN                 | 20    | Input          | Enable pin.                                                                   |

| GND                | EP    | GND            | Ground exposed pad.                                                           |

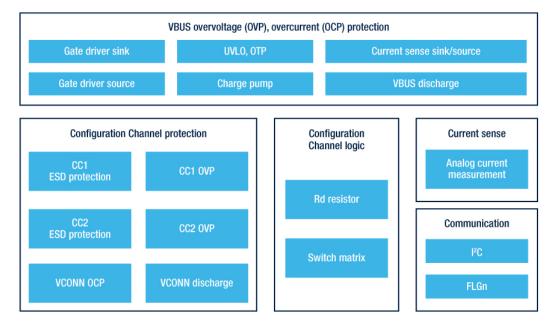

# 2 Block diagram

57

#### Figure 2. Functional block diagram

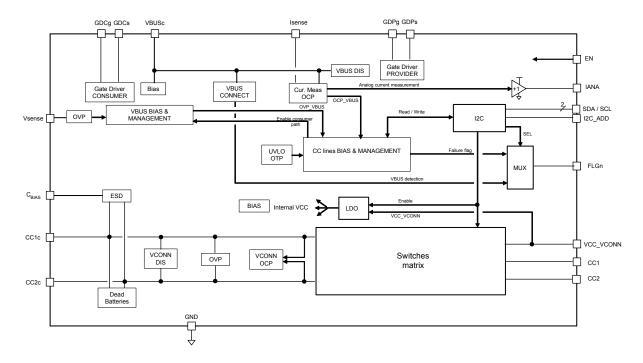

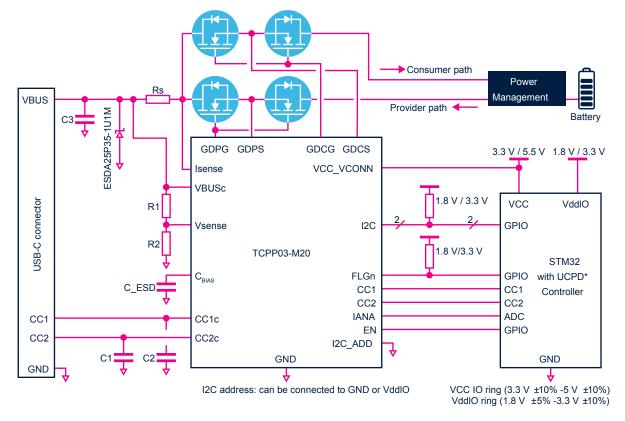

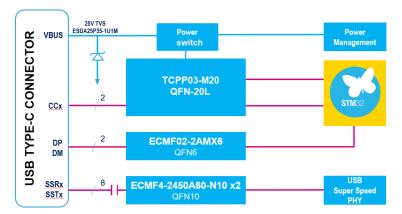

# 3 Typical USB-C DRP, DRD application block diagram

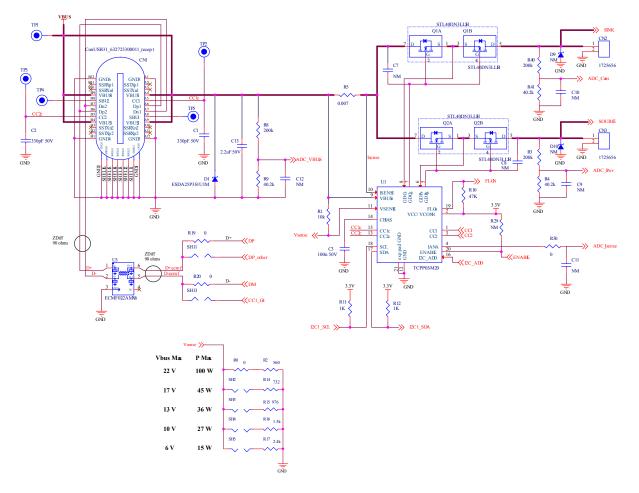

#### Figure 4. Application block diagram example

Note: \* UCPD stands for USB Type-C and Power Delivery

#### Note:

57/

#### UCPD stands for USB type-C and power delivery interface.

External components are described in Section 8.1 External components description.

Please refer to TA0357 for an overview of USB type-C and power delivery technologies.

Please refer to AN5225 for more informations related to USB type-C power delivery using STM32xx Series MCUs and STM32xxx series MPUs.

For more information on EMI filtering and ESD protection of USB datalines, please refer to AN4871: USB type-C protection and filtering.

# 4 Electrical specification

#### 4.1 Parameter conditions

57/

Unless otherwise specified:

- All voltages are referenced to GND

- The minimum and maximum values are guaranteed in the worst conditions of operating temperature, supply voltage and frequencies, by tests in production on 100 % of the devices

- Typical values are given only as design guidelines and are not tested

- All typical curves are given only as design guidelines and are not tested

#### 4.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in the tables below, may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol             | Parameter                                       | Pin name                               | Value       | Unit            |

|--------------------|-------------------------------------------------|----------------------------------------|-------------|-----------------|

| V <sub>POWER</sub> | Voltage for power pins                          | VCC_VCONN                              | 7           | V <sub>DC</sub> |

| M                  |                                                 | EN, V <sub>sense</sub> , I2C_ADD       | 7           | V               |

| V <sub>IN</sub>    | V <sub>IN</sub> Voltage for input pins          | VBUSc, I <sub>sense</sub> , GDPs, GDCs | 24          | V <sub>DC</sub> |

|                    | V <sub>OUT</sub> Voltage for output pins        | I <sub>ANA</sub> , FLGn                | 7           | V <sub>DC</sub> |

| VOUT               |                                                 | C <sub>BIAS</sub> , GDPg, GDCg         | 24          |                 |

| Mus                | Voltago for input, output pipo                  | SDA,SCL, CC1,CC2                       | 7           | VDC             |

| V I/O              | V <sub>I/O</sub> Voltage for input, output pins | CC1c,CC2c                              | 24          | • DC            |

| R <sub>thj-a</sub> | j-a Junction to ambient thermal resistance      |                                        | 150         | °C/W            |

| TJ                 | Junction temperature range                      |                                        | -40 to +125 | °C              |

| T <sub>STG</sub>   | Storage temperature range                       |                                        | -55 to +150 | °C              |

#### Table 2. Absolute maximum ratings (across junction temperature range)

#### Table 3. ESD ratings (across junction temperature range)

| Symbol             | Description                                                             | Pins       | Value | Unit |

|--------------------|-------------------------------------------------------------------------|------------|-------|------|

|                    | System level ESD robustness on USB Type-C connector side <sup>(1)</sup> |            |       |      |

| V <sub>ESD_c</sub> | IEC61000-4-2 Level 4, contact discharge                                 | CC1c, CC2c | 8     | kV   |

|                    | IEC61000-4-2 Level 4, air discharge                                     |            | 15    |      |

| V <sub>HBM</sub>   | V <sub>ESD</sub> ratings human body model (JESD22-A114D, level 2)       | All pins   | 2     | kV   |

1. Internal ESD protection functionality is associated with external capacitor connected on pin C<sub>BIAS</sub>.

for more information on IEC61000-4-2 standard testing, please refer to AN3353.

Note:

# 4.3 Recommended operating conditions

#### Table 4. Recommended operating condition, across junction temperature range

| Pin name                                              | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|------|------|------|------|

| VCC_VCONN, CC1,<br>CC2, V <sub>SENSE</sub>            | 2.7  |      | 5.5  | V    |

| EN, I <sub>ANA</sub> , I2C_ADD,<br>SDA, SCL, FLGn     | 1.7  |      | 3.6  | V    |

| CC1c, CC2c, VBUSc,<br>I <sub>SENSE</sub> , GDPs, GDCs | 0    |      | 22   | V    |

# 4.4 Power supply (VCC\_VCONN, VBUSc)

#### Table 5. Electrical characteristics – Power supply (VCC\_VCONN, VBUSc) across $T_j$

| Symbol                                    | Parameter                                | Test condition across T <sub>OP</sub> |      | Unit |      |      |  |

|-------------------------------------------|------------------------------------------|---------------------------------------|------|------|------|------|--|

| Symbol                                    | Farameter                                |                                       | Min. | Тур. | Max. | Unit |  |

|                                           | V <sub>cc</sub> supply current           | Normal mode                           |      | -    | 2.7  | mA   |  |

|                                           | ICC_VCONN V <sub>cc</sub> supply current | Low power mode                        |      | -    | 1    | μA   |  |

| 1                                         | Supply current of EN pin                 | Low power mode 1,7 V-2,7 V            |      | -    | 3    | μA   |  |

| lenable                                   | Supply current of EN pill                | Low power mode 2,7 V-3,6 V            |      | -    | 10   | μA   |  |

|                                           |                                          | V <sub>BUSc</sub> = 22 V              |      | -    | 2    | mA   |  |

| I <sub>L_VBUSc</sub> VBUSc Supply current | VBUSC Supply current                     | V <sub>BUSc</sub> = 5 V               |      | -    | 0.7  |      |  |

| T <sub>DIS_VBUSc</sub>                    | VBUSc discharge time                     | ·                                     |      | -    | 220  | ms   |  |

# VBUS OVP, OCP

#### Table 6. Electrical characteristics for V<sub>BUS</sub> (OVP, OCP, gate driver, current monitoring) across T<sub>j</sub>

| Symbol                    | Parameter                                            | Test condition across T <sub>OP</sub> |      | Unit |      |      |

|---------------------------|------------------------------------------------------|---------------------------------------|------|------|------|------|

| Symbol                    |                                                      |                                       | Min. | Тур. | Max. | Onit |

| VBUS_UVLO                 | VBUS under voltage lock out                          |                                       | 1.9  | 2.4  | 2.9  | V    |

| V <sub>GS</sub>           | Gate to source voltage consumer VBL                  | JSc = 5 V - 20 V                      | 4.5  | 5    | 5.5  | V    |

| V <sub>OVP_TH</sub>       | OVP V <sub>BUS</sub> threshold voltage               | Vsense pin voltage                    | 1.1  | 1.16 | 1.25 | V    |

| T <sub>OVP_ON_VBUS</sub>  | OVP V <sub>BUS</sub> turn-on time                    |                                       |      | 95   | 145  | ns   |

| V <sub>TH_OCP_VBUS</sub>  | V <sub>BUS</sub> OCP threshold voltage               | Across sense resistor Rs              | 35   | 42   | 45   | mV   |

| T <sub>OFF_OCP_VBUS</sub> | V <sub>BUS</sub> OCP response time                   |                                       |      | 3    | 8    | μs   |

| l <sub>ana_gain</sub>     | Current sensing gain                                 |                                       | 39   | 42   | 45   | V/V  |

| V <sub>IANA</sub>         | Output maximum voltage during OCP event on VBUS line |                                       |      |      | 1.7  | V    |

| T <sub>ON</sub>           | V <sub>BUS</sub> turn-on time                        |                                       |      | 1    | 3    | ms   |

4.5

# 4.6 CC lines OVP and ESD

57

| Symbol              | Parameter                                            | Test condition across T <sub>OP</sub> |      | Unit |      |      |

|---------------------|------------------------------------------------------|---------------------------------------|------|------|------|------|

| Symbol              | Faranieler                                           |                                       | Min. | Тур. | Max. | Unit |

| Roy or              | R <sub>ON_CC</sub> ON resistance of CC OVP FET       | Normal mode                           |      | 0.7  | 1.5  | Ω    |

| NON_CC              |                                                      | Low power mode                        | 8    | 17   | 28   | 12   |

| C <sub>ON_CC</sub>  | Equivalent ON capacitance of CCx line in normal mode | 0 - 1.2 V, f = 400 kHz                | 40   | 60   | 100  | pF   |

| V <sub>TH_CC</sub>  | CC OVP threshold voltage                             |                                       | 5.5  | 5.75 | 6    | V    |

| V <sub>MIN</sub>    | Minimum voltage on CC1c, CC2c                        | Current on CC1c or CC2c < 60 µA       | 0.7  |      |      | V    |

| R <sub>DB</sub>     | DB resistor                                          | Measured at 400 µA on CC1c / CC2c     | 4.1  | 5.1  | 5.6  | kΩ   |

| T <sub>OVP_CC</sub> | OVP response time on the CC pins                     |                                       |      | 60   | 100  | ns   |

| BW <sub>CCx</sub>   | Bandwidth on CCx pins                                | at -3dB and 0 - 1.2 V                 |      | 10   |      | MHz  |

#### Table 8. Typical clamping voltage on CC lines after IEC61000-4-2 ±8kV contact discharge

| TCPP03-M20 and<br>STM32G071 | ESD   | First peak | V <sub>CL</sub> 30 ns |

|-----------------------------|-------|------------|-----------------------|

| OFF                         | +8 kV | 9.2 V      | 3.3 V                 |

| OFF                         | -8 kV | -7.7 V     | -1.0 V                |

| ON                          | +8 kV | 14.8 V     | 6.3 V                 |

| ON                          | -8 kV | -11.8 V    | -1.5 V                |

# Note:

Measurements are performed on X-NUCLEO-DRP1M1 board plugged on top of NUCLEO-G071RB. Ten ESD discharge are applied on connector (CC1c and CC2c) and the voltage measurement is done on MCU side (CC1 and CC2), STM32 still functional after the ESD discharge.

# 4.7 VCONN OCP, discharge

#### Table 9. Electrical characteristics $V_{CONN}$ switch (OCP, discharge) across $T_j$

| Symbol                  | Parameter                                                                                        | Test condition across TOP | Value |      |      | Unit |

|-------------------------|--------------------------------------------------------------------------------------------------|---------------------------|-------|------|------|------|

| Symbol                  | Falameter                                                                                        |                           | Min.  | Тур. | Max. | Unit |

| R <sub>ON_VCONN</sub>   | ON resistance of VCONN FET                                                                       |                           | 2.1   | 3    | 5.5  | Ω    |

| I <sub>VCONN</sub>      | Current thru V <sub>CONN</sub> FET max operating current VCONN = $3.0 \text{ V} - 5.5 \text{ V}$ |                           |       |      | 40   | mA   |

| R <sub>dis-vconn</sub>  | V <sub>CONN</sub> discharge resistor                                                             |                           | 2.5   | 4    | 5    | kΩ   |

| OCP <sub>TH_VCONN</sub> | OCP threshold on V <sub>CONN</sub>                                                               |                           | 40    | 47   | 55   | mA   |

| T <sub>OCP_VCONN</sub>  | V <sub>CONN</sub> OCP response time                                                              |                           |       | 0.9  | 2    | μs   |

# 4.8 I2C slave

| Table 10. Electrical characteristics I2C adressing acros | as Tj |

|----------------------------------------------------------|-------|

|----------------------------------------------------------|-------|

| Symbol    | Symbol Parameter Test condition acros | Test condition across To- |      | Unit |      |      |

|-----------|---------------------------------------|---------------------------|------|------|------|------|

| Symbol    |                                       |                           | Min. | Тур. | Max. |      |

| I2C speed |                                       |                           |      | -    | 1    | Mbps |

# 5 Typical electrical characteristics curves

57

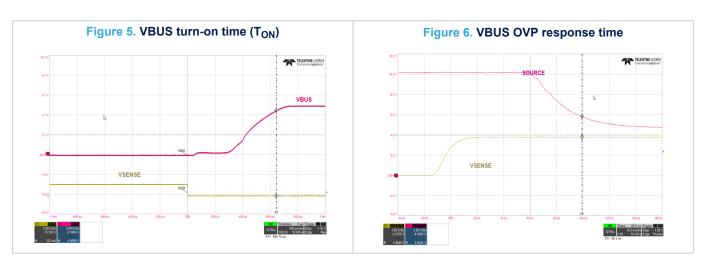

Test conditions for Figure 5 and Figure 6: TCPP03-M20 is in hibernate mode VCC\_VCONN = ENABLE = 0 V, VBUS = 5 V.

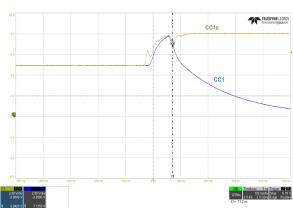

#### Figure 7. CC line (CC1 or CC2) OVP response time

Note: Test conditions for Figure 7: TCPP03-M20 in normal mode VCC\_VCONN = +5 V, ENABLE = 3.3 V, VBUS = 0 V.

# 6 Functional description

#### 6.1 Overview

The TCPP03-M20 is a cost effective solution to protect microcontrollers featuring built-in USB-C power delivery (UCPD) controller or other low voltage power delivery controller. It is especially adapted to dual role power, dual role data applications but also for sink applications requiring a current sense functionality.

Please refer to TA0357 for an overview of USB type-C and power delivery technologies.

Please refer to AN5225 for more informations related to USB type-C power delivery using STM32xx Series MCUs and STM32xxx series MPUs.

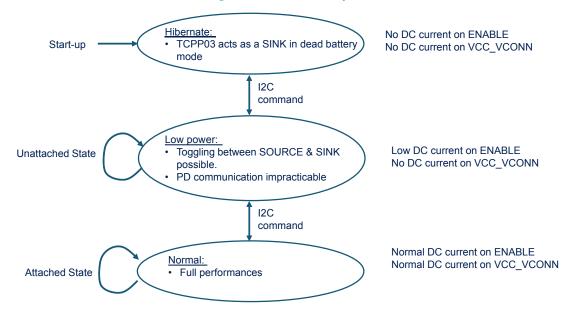

#### 6.2 Power modes

The TCPP03-M20 embeds three distinct power modes controlled by the UCPD controller via the I2C bus.

#### Figure 8. Power modes process

| VCC_VCONN  | ENABLE       | I <sub>DC</sub><br>VCC_VCONN | I <sub>DC</sub> ENABLE       | Mode                                  | Comments                                      |

|------------|--------------|------------------------------|------------------------------|---------------------------------------|-----------------------------------------------|

|            |              |                              |                              |                                       | Dead batteries enabled                        |

| Х          | 0 V          | 0 µA <sup>(2)</sup>          | 0 µA <sup>(1)(2)</sup>       | OFF<br>(reset)                        | FLGn indicates VBUS voltage                   |

|            |              |                              |                              | , , , , , , , , , , , , , , , , , , , | I2C inactive / I2C registers reset            |

|            | 1.8 V        | 1.8 V                        |                              |                                       | Dead batteries enabled                        |

| X          | ±5%          | Hibernate                    | FLGn indicates VBUS voltage  |                                       |                                               |

|            |              | Thernate                     | I2C active                   |                                       |                                               |

|            |              |                              |                              |                                       | Default state at start-up                     |

|            |              |                              | < 10 µA <sup>(1)(2)(3)</sup> |                                       | Dead batteries disabled                       |

|            | 1.8 V<br>±5% |                              |                              | Low<br>power                          | High ohmic CC => No PD communication possible |

| Х          | 3.3 V        | 0 µA <sup>(2)</sup>          |                              |                                       | OVP protection by clamping                    |

|            | ±10%         |                              |                              |                                       | FLGn indicates VBUS voltage                   |

|            |              |                              |                              |                                       | I2C active                                    |

|            | 1.8 V        |                              |                              |                                       | Dead batteries disabled                       |

| 3.3 V ±10% | ±5%          | 2.7 mA                       | < 30 µA <sup>(1)(2)</sup>    | Normal                                | Full performance mode                         |

| 5 V ±10%   | 3.3 V        | 2.7 MA                       | > 50 µA(*//=/                | Normai                                | I2C active                                    |

|            | ±10%         |                              |                              |                                       | FLGn indicates failures                       |

Table 11. Power mode versus power supply

1. Dynamic current of I2C interface have to be added to the values indicated when the I2C bus is used.

2. ESD leakage current have to be added to the values indicated.

3. For pin EN voltage between 1.7 V and 3.6 V.

#### Table 12. TCPP03-M20 states versus power modes

| Power<br>mode | CC<br>switches | OVP<br>CC     | Dead<br>batteries | Gate<br>driver<br>consumer | Gate<br>driver<br>provider | OVP<br>VBUS | FLGn             | I2C | I <sub>ANA</sub> | OCP<br>VBUS | V <sub>CONN</sub><br>VBUS<br>Dis. | Comment                       |

|---------------|----------------|---------------|-------------------|----------------------------|----------------------------|-------------|------------------|-----|------------------|-------------|-----------------------------------|-------------------------------|

| OFF           | OFF            | NA            | ON                | ON <sup>(1)</sup>          | OFF                        | ON          | VBUS<br>connect  | OFF | OFF              | OFF         | OFF                               | TCPP not powered              |

| Hibernate     | OFF            | NA            | ON                | Controlled<br>by I2C       | OFF                        | ON          | VBUS<br>connect  | ON  | OFF              | OFF         | OFF                               | Default state<br>at start-up  |

| Low<br>power  | High<br>ohmic  | 5 V<br>clamp  | OFF               | Controlled<br>by I2C       | OFF                        | ON          | VBUS<br>connect  | ON  | OFF              | OFF         | OFF                               | Signaling only                |

| Normal        | Full perf.     | Active<br>OVP | OFF               | Controlled                 | d by I2C                   | ON          | Failure<br>flags | ON  | ON               | ON          | Controlled<br>by I2C              | PD<br>communication<br>active |

1. Consumer (sink) gate driver is self biased with VBUSc voltage

#### 6.3 **I2C registers**

57

The I2C address used by TCPP03-M20 is 0110 10x, with LSB = 'x'.

The LSB bit of the I2C address is set when connecting TCPP03-M20 pin I2C\_ADD to GND (for LSB = '0') or to 1.8 V or 3.3 V (for LSB = '1').

#### Figure 9. I2C registers

|                                                                              |                                   |                                  | <u>l2</u>            | C add         | <u>ress</u> : 0110 10 | x, x=LSB                                   |                                              |      |                |             |                |

|------------------------------------------------------------------------------|-----------------------------------|----------------------------------|----------------------|---------------|-----------------------|--------------------------------------------|----------------------------------------------|------|----------------|-------------|----------------|

|                                                                              |                                   |                                  |                      |               |                       |                                            |                                              |      |                | VCONN       | switch         |

|                                                                              |                                   | PM2                              | PM2 PM1              | Power<br>Mode |                       |                                            | V2                                           | V1 - | VC2            | VC1         |                |

|                                                                              | VCONND=1:<br>• VCONN              | VBUSD=1:<br>• VBUS               | 0                    | 0             | Hibernate             | GDC=1:                                     | GDP=1:<br>• Switch load                      | 0    | 0              | Open        | Open           |

|                                                                              | discharge ON<br>VCONND=0:         | discharge ON<br>VBUSD=0:         | 1                    | 0             | Low power             | <ul> <li>Switch load<br/>opened</li> </ul> | closed                                       | 1    | 0              | Close       | Open           |

|                                                                              | VCONN<br>discharge OFF            | <ul> <li>VBUS</li> </ul>         | 0                    | 1             | Normal                | GDC=0:<br>• Switch load                    | <ul><li>GDP=0:</li><li>Switch load</li></ul> | 0    | 1              | Open        | Close          |

|                                                                              | discharge OFF                     | discharge OFF                    | 1                    | 1             | Not Used              | closed                                     | opened                                       | 1    | 1              | Open        | Open           |

| Writing register<br>(address = 0)                                            | VCONN<br>DISCHARGE<br>(VCONND)    | VBUS<br>DISCHARGE<br>(VBUSD)     | PM2<br>Power Me      | -             | PM1<br>Power Mode 1   | Gate Driver<br>Consumer<br>(GDC)           | Gate Driver<br>Provider<br>(GDP)             | V    | /2             | ١           | /1             |

| Reading register n°1<br>(address = 1)<br>Flags are set to '1'<br>when active | VCONN<br>DISCHARGE<br>Acknowledge | VBUS<br>DISCHARGE<br>Acknowledge | PM2<br>Acknow        | -             | PM1<br>Acknowledge    | Gate Driver<br>Consumer<br>Acknowledge     | Gate Driver<br>Provider<br>Acknowledge       |      | ONN2<br>wledge | VCO<br>Ackn | NN1<br>owledge |

| Reading register n°2<br>(address = 2)<br>Flags are set to '1'                | 0 => TCPP03<br>1 => TCPP02        | 0                                | FLG<br>VBUS <u>-</u> |               | FLGn<br>OVP_CC        | FLGn<br>OTP                                | FLGn<br>OVP_VBUS                             |      | _Gn<br>_VBUS   |             | .Gn<br>VCONN   |

| when active                                                                  | Bit 7                             | Bit 6                            | Bit 5                |               | Bit 4                 | Bit 3                                      | Bit 2                                        | Bit  | 1              | Bit         | : 0            |

Reading re (address = Flags are so when active

Reading re (addres Flags are s

# 7 **Protection features**

TCPP03-M20 embeds protection features for dual role power (DRP), dual role data (DRD) applications, as required by:

- USB-C specification

- USB power delivery specification 3.1

- International electrotechnical commission (IEC)

# 7.1 FLGn pin description

FLGn pin is an open-drain output flag in steady state, it must be left floating when not connected. In hibernate and low power modes FLGn indicates voltage presence on VBUS.

In normal mode, FLGn indicates an error (OVP, OCP or OTP): I2C registers must be read to identify the error. Recovery for each error type is described in each section of below paragraphs.

# 7.2 How to protect against ESD (electrostatic discharge) applied on the USB-C connector ?

Electrostatic discharges can be conducted by the USB Type-C connector and damage the electronic circuitry of the application.

The ESD surge waveform is modelized by the international electrotechnical commission in the specification IEC61000-4-2.

The TCPP03-M20 integrates ESD protection for CC1 and CC2 lines up to +8 kV contact discharge , associated with an external 100 nF - 50 V capacitor on  $C_{BIAS}$  pin.

Please refer to AN4871 USB type-C protection and filtering to apply required protections to comply with the IEC61000-4-2 specification.

For more information on IEC61000-4-2 standard testing, please refer to STMicroelectronics application note AN3353.

## 7.3 VBUS management

An overvoltage protection is required on VBUS when the absolute maximum ratings of your power management integrated circuit is below the maximum voltage that can be applied on VBUS.

Until now, it was common to find the protection circuit inside a controller dedicated to USB-C power delivery. However, by supporting USB-C PD with an embedded module inside an MCU and a companion Type-C port protection device, you can lower your bill of material and facilitate the transition, without requiring an expensive USB-C PD ASIC controller. One of the reasons the MCU and TCPP03-M20 bundle is such a compelling financial proposition is that the latter device integrates the VBUS gate drivers, which enables the use of cheaper and smaller N-MOSFETs, instead of the P-MOSFETs usually used by ASIC controllers.

This is an added value of TCPP03-M20, specially when VBUS line is compromised if a defective charger is stuck at a higher voltage than negociated or a defective cable is inserted.

Overvoltage protection is always required on the VBUS line to prevent a voltage higher than negociated is applied on the VBUS.

This use case can occur even when power delivery is not used i.e when VBUS voltage is 5 V.

#### 7.3.1 VBUS turn-on

VBUS turn-on time after I2C command is achieved in  $T_{ON}$  = 1 ms typical (see Figure 5).

#### 7.3.2 VBUS UVLO (under voltage lock out)

This block continuously monitors VBUS voltage. It acts as:

- An UVLO (under voltage lock out) for the VBUS circuitry: OVP\_VBUS and consumer gate driver are enabled once the VBUS voltage reaches VBUS\_UVLO voltage level (2.4 V typ.)

- It signals to the I2C block the presence of a voltage on VBUS when the VBUS voltage reach VBUS\_UVLO voltage level (2.4 V typ.)

#### 7.3.3 VBUS OVP turn-on and turn-off

When  $V_{SENSE}$  pin voltage goes above  $V_{OVP_TH}$ , OVP is turned ON in less than 95 ns ( $T_{OVP_ON_VBUS}$  typical value), and FLGn pin goes to 'low-Z' state.

Fast shut-down is enabled by TCPP03-M20 gate driver by shorting the MOSFET gate and source pin. As a result, source pin goes safely to 0 V and I2C register is updated with relevant value.

OVP recovery is ensured after a typical delay of 64 µs: the external power mosfet is turned-on and Flag pin FLGn goes back to Hi-Z state after the end of the ovp condition.

# 7.3.4 How to set TCPP03-M20 OVP threshold according to VBUS maximum voltage allowed by the application

As shown in Figure 4, R1 / R2 bridge gives an image of VBUS voltage to set TCPP03-M20 OVP threshold. With fixed R1 value (10 k $\Omega$ ), the table provides R2 values for various TCPP03-M20 OVP threshold according to VBUS maximum voltage allowed by the application.

#### Table 13. R2 values versus VBUS OVP threshold when R1 = 10 k $\Omega$

| R2     | VBUS max. | P max. |

|--------|-----------|--------|

| 2.4 kΩ | 6 V       | 15 W   |

| 1.3 kΩ | 10 V      | 27 W   |

| 976 Ω  | 13 V      | 36 W   |

| 732 Ω  | 17 V      | 45 W   |

| 560 Ω  | 22 V      | 100 W  |

Note:

R2 selected in accordance with input AMR on consumer path.

# 7.4 VBUS current sense (I<sub>ANA</sub> pin)

The I<sub>ANA</sub> output pin is active only in normal mode.

The I<sub>ANA</sub> output can be connected directly to the STM32 ADC input because it is internally biased by EN pin. The I<sub>ANA</sub> output voltage level is about 1.7 V at the OCP tripping level allowing connection to 1.8 V MCU I/O pin.

# 7.5 V<sub>BUS</sub> analog current measurement and bidirectional OCP

The over current protection on VBUS is bidirectional i.e active for both consumer (i.e sink or UFP application) and provider (i.e source or DFP application) power path.

VBUS OCP threshold is set by external serial resistor on VBUS. The gain for the analog reading is set to 42 V/V. The OCP threshold is set to 0.042 V across Rs.

The OCP VBUS is biased by VCC\_VCONN and works only in normal mode.

Equivalent block diagram in TCPP03-M20 for V<sub>BUS</sub> analog current measurement and OCP is given here after:

#### Figure 10. Equivalent block diagram in TCPP03-M20

High side amplifier OCP IANA DIR I.8 V VBUSC VBUSC VBUSC (\*) OCP IANA FLT\_OCP Consumer path Consumer path VCC\_VCONN VBUSC

#### Table 14. Recommended values

| Typical current | VBUS OCP threshold | Rs - Sense resistor (normalized values) |

|-----------------|--------------------|-----------------------------------------|

| 0.5 A           | 0.9 A              | 47 mΩ                                   |

| 1.5 A           | 1.9 A              | 22 mΩ                                   |

| 3.0 A           | 4.2 A              | 10 mΩ                                   |

| 5.0 A           | 6.0 A              | 7 mΩ                                    |

The OCP is biased continuously: inrush current magnitude is controlled by the user through an external capacitor. Please refer to the X-NUCLEO-DRP1M1 user manual for more informations on external capacitor to control the insrush current magnitude.

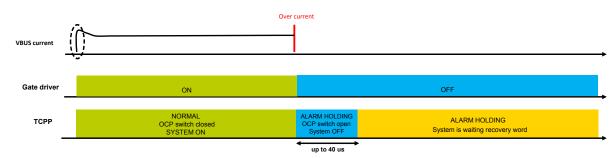

If an OCP event occurs:

- V<sub>CONN</sub> switches, CC switches and gate drivers are shutting down

- During up to 40 µs typ., this OCP alarm is held (no recovery is possible)

- After this delay, CC switches are turned ON but V<sub>CONN</sub> switches and gate drivers are held OFF

The system can be restarted only with a recovery word send by the MCU via the I2C bus.

The FLGn signal stays low while the recovery word has not been sent

The recovery word is described in next paragraph

51

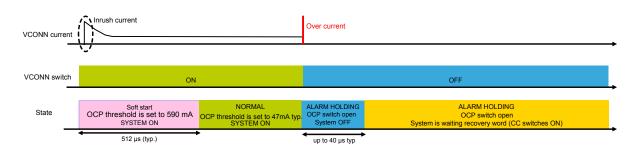

#### Figure 11. Typical chronograms of TCPP03-M20 VBUS OCP

Note:

In case of VBUS OCP event, the TCPP03-M20 switches OFF all active functions except CC switches:

- V<sub>CONN</sub> switches

- VBUS gate driver (provider and consumer)

- V<sub>CONN</sub> and V<sub>BUS</sub> discharge paths are activated

- It is signaled to the user by several ways:

- I2C corresponding state bits are cleared (i.e. VCONN1\_ACK = 0, VCONN2\_ACK = 0...)

- I2C relevant OCP flag is set (FLGn\_OCP\_VBUS is the OCP event coming from VBUS switch for example)

- Failure flag pin (FLGn) is active (i.e. in LowZ state)

- After a delay of up to 40 μs, to recover, the below bit sequence has to be written and after recovery, the user can resume a start-up procedure:

#### Table 15. VBUS OCP recovery bit sequence table

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | PM2  | PM1  | 1    | 0    | 0    | 0    |

#### 7.6 V<sub>CONN</sub> OCP

- At start-up, a soft start sets the tripping current to about 590 mA during 512 μs min. (1ms max.)

- After this delay, the soft start is ended and the normal OCP threshold occurs (50 mA).

- If an OCP event occurs:

- V<sub>CONN</sub> switches, CC switches and gate drivers are shutting down

- During up to 40 µs typical, this OCP alarm is held (no recovery is possible)

- After this delay, CC switches are turned ON but V<sub>CONN</sub> switches and gate drivers are held OFF. The system can be restarted only with a recovery word send by the MCU via the I2C bus.

- The FLGn signal stays low as long as the recovery word has not been sent

#### Figure 12. V<sub>CONN</sub> OCP chronograms

To recover, the below bit sequence has to be written and after recovery, the user can resume a start-up procedure:

#### Table 16. VBUS OCP recovery bit sequence table

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | PM2  | PM1  | 1    | 0    | 0    | 0    |

# 7.7 V<sub>CONN</sub> CC line OVP

#### 7.7.1 CC lines short to VBUS

This happens when VBUS high voltage short circuit to the CC lines when hot unplug is done with a poor mechanical quality connector. Over voltage protection is needed on the CC lines because VBUS typical voltage can be as high as 20 V when CC pins are usually 5 V tolerant I/Os on low voltage USB-PHY controllers. TCPP03-M20 integrate this protection against CC lines short to VBUS thanks to an overvoltage protection (integrated FET).

When the voltage on CC line goes above  $V_{TH_CC}$ , the OVP on CC line turns-on in less than 60ns ( $T_{OVP_CC}$  typical value) and FLGn pin goes to '0' state.

When the OVP event disappear, OVP on CC line is turned-off and the FLGn pin goes back to 'Hi-Z' state.

#### 7.8 VBUS discharge

VBUS discharge is activated via I2C bus and controlled via firmware by the USB-C power delivery controller. The VBUS discharge feature integrated in TCPP03-M20 allows to discharge 10  $\mu$ F in less than 220 ms (T<sub>DIS\_VBUS</sub>).

This discharge time is in line with USB-C specification, extracted below for VBUS discharge:

| Table 17. Common source | sink electrical para | meters from USB-C specification |

|-------------------------|----------------------|---------------------------------|

|-------------------------|----------------------|---------------------------------|

| Parameter | Description                | Min. | Тур. | Max. | Units |

|-----------|----------------------------|------|------|------|-------|

| tSafe0V   | Time to reach vSafe0V max. | -    | -    | 650  | ms    |

| tSafe0V   | Time to reach vSafe0V max. | -    | -    | 275  | ms    |

To avoid short-circuit, the VBUS discharge cannot be activated if the consumer or the provider gate driver is active.

## 7.9 V<sub>CONN</sub> discharge

$V_{CONN}$  discharge is activated via I2C bus and controlled via firmware by the USB-C power delivery controller. The  $V_{CONN}$  discharge feature integrated in TCPP03-M20 allows to discharge  $V_{CONN}$  in  $R_{DIS_VCONN} < 5.5 \text{ k}\Omega$ , as per USB-C specification table extracted below:

#### Table 18. V<sub>CONN</sub> source characteristics from USB-C power delivery specification

|                  | Minimum | Maximum | Notes                                                                                                    |

|------------------|---------|---------|----------------------------------------------------------------------------------------------------------|

| R <sub>dch</sub> | 30 Ω    | 6120 Ω  | Discharge resistance applied<br>in UnattachedWait.SRC<br>between the CC pin being<br>discharged and GND. |

Note:

Note:

• V<sub>CONN</sub> discharge is activated and stopped via I2C commands from USB-PD controller

To avoid short-circuit,  $V_{CONN}$  discharge cannot be activated if  $V_{CONN}$  switch are closed

The CCxc pin discharged is the last one acting as V<sub>CONN</sub>

# 7.10 OTP (over temperature protection)

Above 150°C typ., the OTP triggers the FLGn pin. OVP and OCP on VCONN, CC lines, VBUS are shut down. Auto recovery is ensured when the temperature goes back below OTP threshold.

# 8 USB-C dual role power schematic example

#### Figure 13. Partial schematic extract of nucleo expansion board X-NUCLEO-DRP1M1 using TCPP03-M20

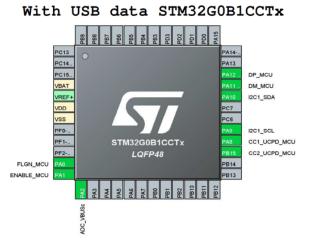

Figure 14. STM32 configuration with CubeMX

# Prerelease product(s)

57

#### 8.1 **External components description**

| Component reference                         | Component name or value | Description                                                                                                                                            |

|---------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1                                          | ESDA25P35-1U1M          | TVS protecting against 25 A 8/20 µs<br>surge waveforms and ESD transients <sup>(1)</sup><br>(see Section 8.2 Transient Voltage<br>suppressor on VBUS). |

| C1, C2                                      | 330 pF typ., 25 V       | EMI capacitor, required to comply with USB-C specification.                                                                                            |

| C3                                          | 100 nF, 50 V            | X7R ESD protection capacitance with<br>low ESL required to comply with USB-C<br>specification.                                                         |

| C13                                         | 2,2 µF, 50 V            | VBUSc bulk capacitance, required in the USB-C power delivery specification.                                                                            |

| R5                                          | 0.007 Ω                 | Serial resistor which value sets the VBUS OCP threshold.                                                                                               |

| R1 and R2 or R14, or R15, or R16, or<br>R17 | See Table 13            | Resistor bridge to set VBUS OVP threshold.                                                                                                             |

Table 19. Schematic description

1. For more informations on USB type-C protection and filtering, cf AN4871, and AN3353 for informations related to IEC 61000-4-2 standard testing.

# **Transient Voltage suppressor on VBUS**

The D1 diode ESDA25P35-1U1M is used to comply with the international electrotechnical commission specification IEC61000-4-5 on the VBUS power line when it is subjected to switching and lightning transients. These surges are defined in 8/20 µs waveform. For more information, please refer to AN4275: IEC61000-4-5 standard overview.

8.2

57

# 8.3 Configuration channel: line capacitance on CC1c and CC2c

USB-C PD has a specification for the total amount of capacitance for proper operation on CC lines. This specification is given here after.

#### Table 20. USB-C PD specification

| Description             | Minimum | Maximum |  |

|-------------------------|---------|---------|--|

| CC receiver capacitance | 200 pF  | 600 pF  |  |

Therefore, the capacitance added by the TCPP03-M20 and by the MCU or LV controller must fall within limits. The next table shows the analysis involved in choosing the correct external capacitor for the system.

| CC capacitance                     | Min.   | Max.   | Comment                                                          |

|------------------------------------|--------|--------|------------------------------------------------------------------|

| CC line target capacitor 200 pF    |        | 600 pF | From USB PD Specification section 5.8.6                          |

| TCPP03-M20 capacitance             | 40 pF  | 100 pF |                                                                  |

| MCU or low voltage capacitance     | 60 pF  | 90 pF  | Typical value. To be adapted following the exact reference used. |

| Proposed capacitance for C1,<br>C2 | 120 pF | 390 pF | 25 VDC min. of rated voltage.<br>0402 or smaller<br>recommended. |

#### Table 21. Table analysis

C1 and C2 must be placed as close as possible to the USB-C connector to optimize the electromagnetic immunity.

# 8.4

#### Bulk capacitance

USB-C power delivery specification defines cSnkBulk and cSrcBulk capacitances as the sum of bulk capacitances on both sides of the ohmic path of VBUSc.

To insure compliance with the standard and TCPP03-M20 protection performances, it is mandatory to place this capacitance on VBUSc, as close as possible to the USB-C connector with a value of 2,2  $\mu$ F - 50 V.

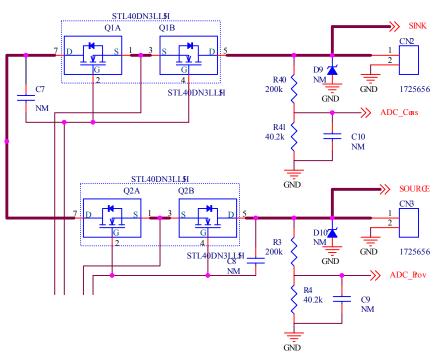

#### 8.5 N-channel MOSFET

57

The TCPP03-M20 ensures a V<sub>GS</sub> voltage between 5 V and 6 V when the N-channel MOSFET is ON. The user must choose a N-channel MOSFET fully specified (for example: STL40DN3LLH5 in source to source configuration ) with 5 V of V<sub>GS</sub>. Maximum current in USB-PD applications can raises up to  $I_{DS}$  = 5 A. As shown in Figure 15, C7 and C8 external capacitor may be associated to other N-channel MOSFET reference to avoid OCP trigger due to inrush current on VBUS pin.

#### Figure 15. Schematic example from X-NUCLEO-DRP1M1

# 8.6 Complementary products for USB dataline ESD protection for pins DP, DM, SSRX, SSTX

For applications requiring USB dataline protection, STMicroelectronics recommends the implementation shown in picture below:

#### Figure 16. USB dataline ESD protection for pins DP, DM, SSRX, SSTX

#### Table 22. Product recommendations

| Part Number              | Description                                       | USB-C<br>connector pin                                 | Protection features                                                                                                                                                        |

|--------------------------|---------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCPP03-M20               | Type-C port protection                            | VBUS, CC1, CC2,<br>V <sub>CONN</sub>                   | ESD protection as per IEC61000-4-2 Level 4<br>Overvoltage, overcurrent and discharge on<br>VBUS<br>Overvoltage, overcurrent and discharge on<br>CC1/CC2, V <sub>CONN</sub> |

| ESDA25P35-1U1M           | Power line transient voltage suppressor (TVS)     | VBUS                                                   | ESD protection as per IEC61000-4-2 Level 4<br>IEC61000-4-5 (8/20µs surge waveform)                                                                                         |

| ECMF02-2AMX6             | Common mode filter with integrated ESD protection | D+, D-                                                 | ESD protection as per IEC61000-4-2 Level 4<br>RF antenna desense due to high speed<br>differential link EMI radiation                                                      |

| ECMF4-2450A60N10<br>(x2) | Common mode filter with integrated ESD protection | TX1+, TX1-, RX1+,<br>RX1-<br>TX2+, TX2-, RX2+,<br>RX2- | ESD protection as per IEC61000-4-2 Level 4<br>RF antenna desense due to high speed<br>differential link EMI radiation                                                      |

For more information on USB Type-C protection for datalines, please refer to <u>AN4871</u>, USB Type-C protection and filtering.

For more information on RF antenna desense due to high speed differential link EMI radiation, please refer to <u>AN4356</u>, Antenna desense on handheld equipment.

# 9 PCB design recommendation

## 9.1 PCB routing

.

When routing the TCPP03-M20, please respect the following recommendation:

- Place the circuit as close as possible to the USB-C connector in order to maximize the efficiency of the ESD protection for CC lines

- Place the ESD capacitor as close as possible to the TCPP03-M20

# **10** USB type-C port protection (TCPP) comparison table

| Table 23. Device comparison table |  |

|-----------------------------------|--|

|-----------------------------------|--|

| Part number | Expansion board | SW expansion board | USB type-C application               | Package  |

|-------------|-----------------|--------------------|--------------------------------------|----------|

| TCPP01-M12  | X-NUCLEO-SNK1M1 |                    | Sink, UFP, consumer                  | µQFN-12L |

| TCPP02-M18  | X-NUCLEO-SRC1M1 |                    | Source, DFP, provider                | µQFN-18L |

|             |                 | X-CUBE-TCPP        | DRP, dual role power                 |          |

| TCPP03-M20  | X-NUCLEO-DRP1M1 |                    | DRD, dual role data                  | µQFN-20L |

|             |                 |                    | Sink requiring current sense and OCP |          |

# **11 Package information**

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

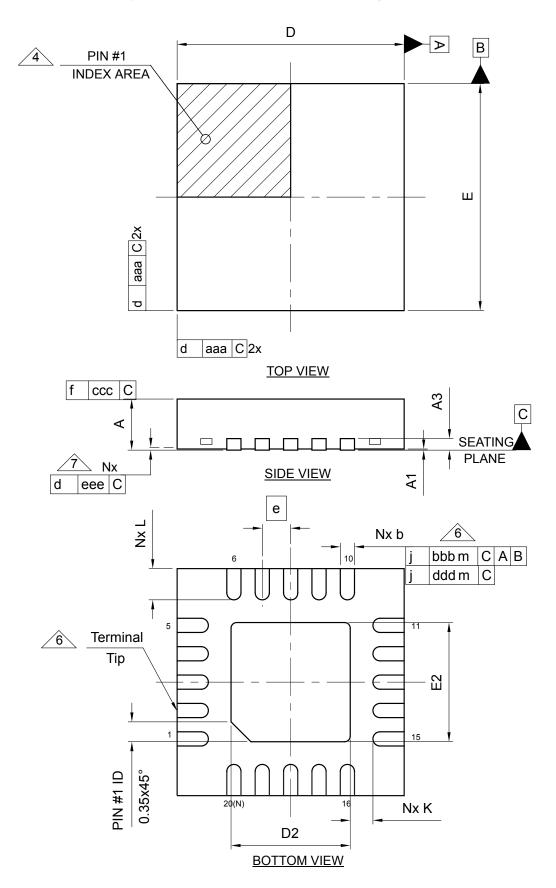

# 11.1 QFN-20L 4.0 x 4.0 x 0.75 mm package information

#### Figure 17. QFN-20L 4.0 x 4.0 x 0.75 mm package outline

57

|      |             | Dimensions |      |  |

|------|-------------|------------|------|--|

| Ref. | Millimeters |            |      |  |

|      | Min.        | Тур.       | Max. |  |

| А    | 0.70        | 0.75       | 0.80 |  |

| A1   |             | 0.02       | 0.05 |  |

| A3   |             | 0.20 REF.  |      |  |

| b    | 0.18        | 0.25       | 0.30 |  |

| D    | 3.95        | 4.00       | 4.05 |  |

| D2   | 1.95        | 2.10       | 2.20 |  |

| E    | 3.95        | 4.00       | 4.05 |  |

| E2   | 1.95        | 2.10       | 2.20 |  |

| е    | 0.50 BSC    |            |      |  |

| L    | 0.50        | 0.55       | 0.60 |  |

| К    | 0.20        |            |      |  |

| Ν    | 20          |            |      |  |

| ND   |             | 5          |      |  |

| NE   | 5           |            |      |  |

| aaa  | 0.05        |            |      |  |

| bbb  | 0.10        |            |      |  |

| bbb  | 0.10        |            |      |  |

| ddd  | 0.05        |            |      |  |

| eee  | 0.08        |            |      |  |

#### Table 24. QFN-20L 4.0 x 4.0 x 0.75 mm package mechanical data

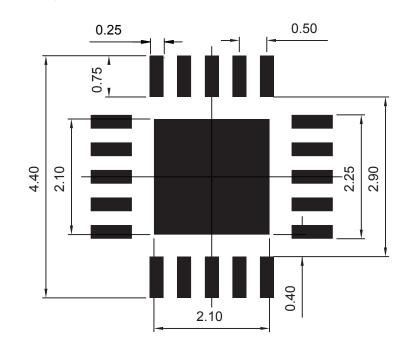

Figure 18. recommended footprint (dimensions are in mm)

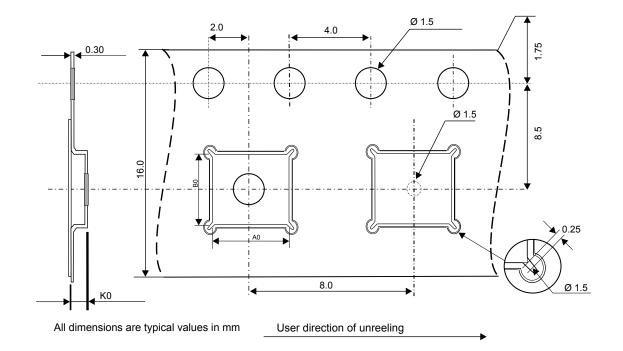

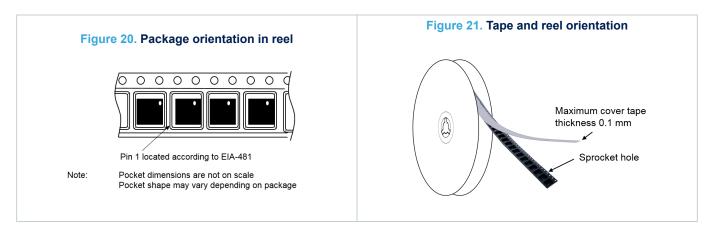

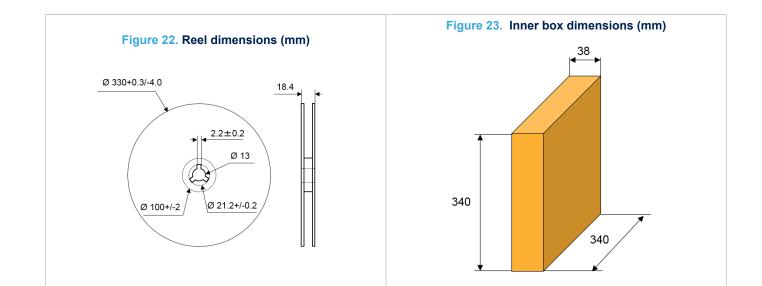

Table 25. Tape and reel mechanical data

|      | Dimensions  |      |      |  |

|------|-------------|------|------|--|

| Ref. | Millimeters |      |      |  |

|      | Min.        | Тур. | Max. |  |

| A0   | 4.25        | 4.35 | 4.45 |  |

| B0   | 4.25        | 4.35 | 4.45 |  |

| К0   | 1.00        | 1.10 | 1.20 |  |

57

57

# 12 Ordering information

Table 26. Ordering information

| 0  | rder code | Marking | Package                     | Weight | Base qty. | Delivery mode |

|----|-----------|---------|-----------------------------|--------|-----------|---------------|

| тс | CPP03-M20 | TCPP03  | QFN-20L 4.0 x 4.0 x 0.75 mm | 44 mg  | 3000      | Tape and reel |

# **Revision history**

#### Table 27. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 21-Jun-2021 | 1        | Initial release. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved