# Sensor-less Three-phase Brushless DC Motor Controller, with Gate Drivers, for Automotive

# LV8961HUW

# Overview

The LV8961H is a high performance, AEC–Q100 qualified, sensor-less three-phase BLDC motor controller with integrated gate drivers for driving external N–MOSFETs. An on-chip two–stage charge pump provides required gate voltage for a wide range of low  $R_{DS(ON)}$  type external N–MOSFETs. The device offers a rich set of system protection and diagnostic functions such as over-current, over-voltage, short-circuit, under-voltage, over-temperature and many more. It supports open–loop as well as closed-loop speed control with user configurable startup, speed setting and proportional/integral (PI) control coefficients, making it suitable for a wide range of motor and load combinations. With a built-in linear regulator for powering external circuits and a watchdog timer, the LV8961H offers a very small system solution.

The LV8961H stores system parameters in embedded one-time programmable (OTP) non-volatile memory in addition to RAM system memory. An SPI interface is provided for parameter setting and monitoring the system status. With the operating junction temperature tolerance up to 175°C and wide range (voltage and frequency) PWM input, the LV8961H is an ideal solution for stand-alone BLDC motor control systems.

# Features

- AEC-Q100 Qualified and PPAP Capable

- Operating Junction Temperature up to 175°C

- Operating Voltage Range from 5.5 V to 28 V with Tolerance from 4.5 V to 40 V

- Embedded Proprietary Sensor-less Trapezoidal and Sinusoidal Commutation

- Selectable Number of BEMF Zero-cross Detection Window from 6, 3, 2, and 1 per Electrical Cycle

- Simple and Effective Lead Angle Adjustment Setting by Register

- Supports Open-loop as well as Closed-loop Speed Control

- Integrated Gate Drivers for Driving Six N-MOSFETs

- Two-stage Charge Pump for Continuous 100% Duty Cycle Operation

- 5 V / 3.3 V Regulator and Watchdog Timer Applications Using an External Microcontroller

- Configurable Speed Settings with Linear Characteristic

- PI Control Include Acceleration/Deceleration Adjustment

- Direct Access to PWM Duty and FG Cycle via SPI Interface

- Various System Protection Features Including:

- Shoot through Protection Using Configurable Dead-time

- Drain-source Short Detection

# **ON Semiconductor®**

www.onsemi.com

- VVV = Work Week Number

- LV8961H = Specific Device Code

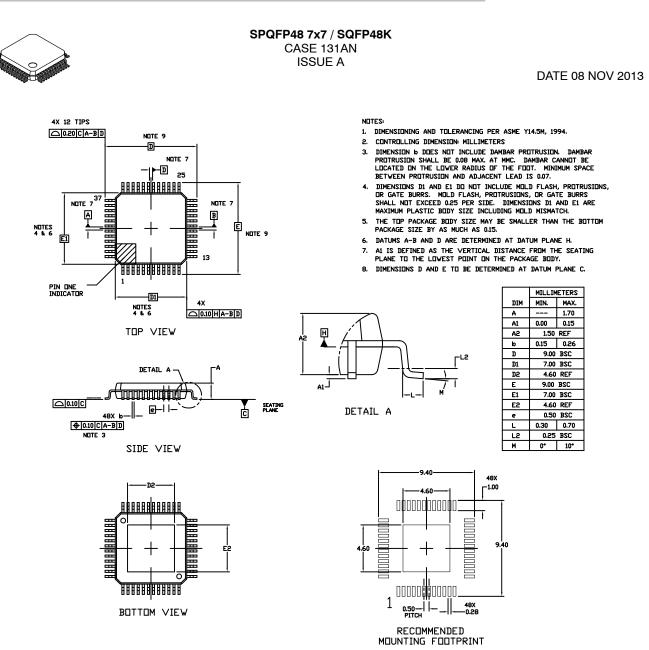

# **ORDERING INFORMATION**

| Device       | Package              | Shipping <sup>†</sup>  |  |

|--------------|----------------------|------------------------|--|

| LV8961HUWR2G | SQFP48K<br>(Pb–Free) | 2,500 /<br>Tape & Reel |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

- Cycle-by-cycle Current Limit and Over-current Shutdown (Threshold Value can be Selectable by Register)

- Over-voltage and Under-voltage Shutdown

- Over-temperature Warning and Shutdown

- Input PWM Fault Detection

- Abnormal FG Cycle Monitoring

- Motor Pin Open Detection

## **Typical Applications**

- Automotive Pumps (Fuel, Oil, and Hydraulic)

- Fans (Radiator, Battery Cooling, LED Headlight Cooling)

- White Goods and Industrial BLDC Motor Control

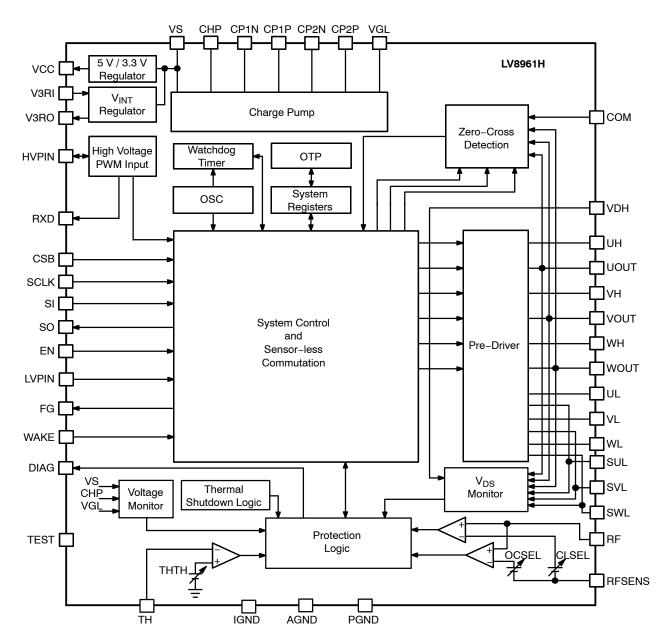

# LV8961H BLOCK DIAGRAM

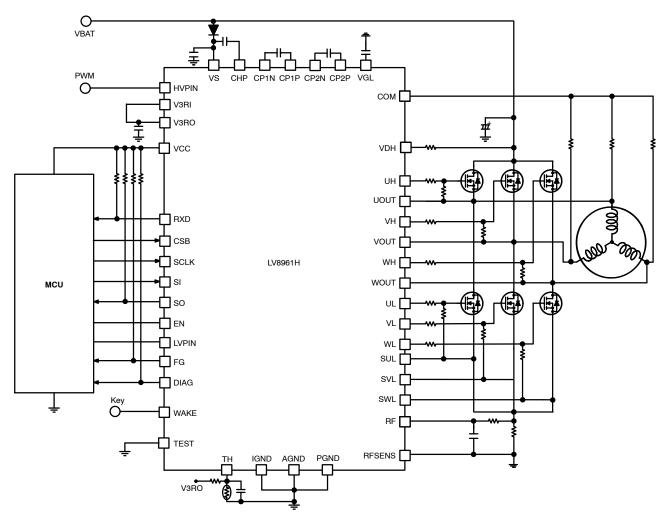

# **APPLICATION BLOCK DIAGRAMS**

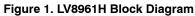

Figure 2. Example of Standalone Configuration

Figure 3. Example of MCU Based Control Configuration

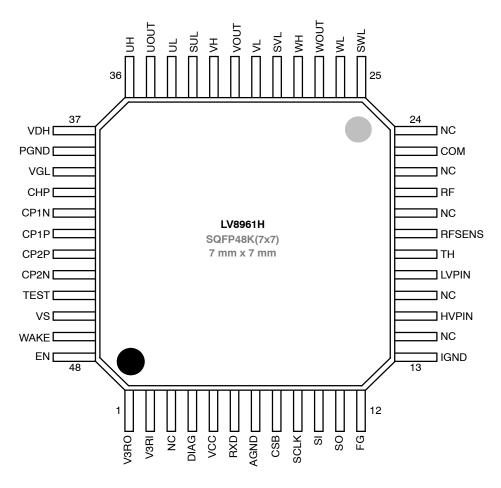

# **PIN ASSIGNMENTS**

Figure 4. LV8961H Pinout

# **PIN DESCRIPTION**

| Pin Name             | Pin No                   | TYPE                       | Description                                                                                                                                                                                         | Page |

|----------------------|--------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V3RO                 | 1                        | TYPE 2                     | 3 V regulator output pin. Connect capacitor between this pin and AGND                                                                                                                               | 19   |

| V3RI                 | 2                        | TYPE 1                     | 3 V regulator input pin (internally connected to control, and logic circuits). Connect to V3RO pin                                                                                                  | 19   |

| NC                   | 3, 14, 16,<br>20, 22, 24 |                            | No Connections                                                                                                                                                                                      |      |

| DIAG                 | 4                        | TYPE 4                     | Programmable open drain diagnostic output                                                                                                                                                           | 21   |

| VCC                  | 5                        | TYPE 2                     | 5 V or 3.3 V regulator output pin. (Selected by internal register setting) Power supply for microcontroller. Connect capacitor to AGND for stability                                                | 19   |

| RXD                  | 6                        | TYPE 4                     | Open drain logic level output of HVPIN received data. Use pull-up to a voltage less than or equal to VS                                                                                             | 21   |

| AGND                 | 7                        |                            | Analog GND pin                                                                                                                                                                                      |      |

| CSB                  | 8                        | TYPE 5                     | Active low SPI interface chip selection pin                                                                                                                                                         | 26   |

| SCLK                 | 9                        | TYPE 3                     | SPI interface clock input pin                                                                                                                                                                       | 26   |

| SI                   | 10                       | TYPE 3                     | Active high SPI interface serial data input pin                                                                                                                                                     | 26   |

| SO                   | 11                       | TYPE 4                     | Open drain SPI interface serial data output pin                                                                                                                                                     | 26   |

| FG                   | 12                       | TYPE 4                     | Open drain back-EMF transition output pin. The frequency division ratio is selectable via register settings                                                                                         | 21   |

| IGND                 | 13                       | TYPE 12                    | HV PWMIN Block GND pin. Must be connected to AGND on the PCB                                                                                                                                        |      |

| HVPIN                | 15                       | TYPE 12                    | High voltage PWM input with a $V_{VS}/2$ threshold                                                                                                                                                  | 21   |

| LVPIN                | 17                       | TYPE 3                     | Digital level PWM input pin for direct drive or speed register selection details. Input<br>polarity can be programmed for either active high or active low                                          | 21   |

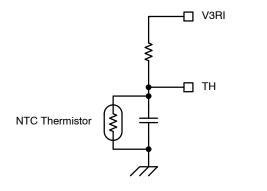

| TH                   | 18                       | TYPE 1                     | Thermistor input pin for power stage temperature detection. If the input voltage is below the threshold voltage, an error is triggered. The error threshold is programmable. To disable tie to V3RO | 23   |

| RFSENS               | 19                       | TYPE 13                    | Shunt resistance reference pin. Connect this pin to the GND side of the Shunt resistor with Kelvin leads                                                                                            | 22   |

| RF                   | 21                       | TYPE 13                    | Output current detect pin. Connect this pin to higher terminal of the shunt resistor with Kelvin leads                                                                                              | 22   |

| COM                  | 23                       | TYPE 9                     | COM input pin. Connect this pin to the motor neutral point if available. This point may be derived from a resistive network with 1 k resistors to the phases                                        | 15   |

| SWL<br>SVL<br>SUL    | 25<br>29<br>33           | TYPE 8<br>TYPE 8<br>TYPE 8 | Current return path for low-side gate drive. Short circuit shutoff level is measured between this pin and its corresponding phase pin                                                               | 21   |

| WL<br>VL<br>UL       | 26<br>30<br>34           | TYPE 8<br>TYPE 8<br>TYPE 8 | Gate driver output pin for the low-side Nch Power FET. Use gate resistors for wave-shaping                                                                                                          | 21   |

| WOUT<br>VOUT<br>UOUT | 27<br>31<br>35           | TYPE 7<br>TYPE 7<br>TYPE 7 | Current return path for high-side gate drive and reference for high-side short circuit shut-off                                                                                                     | 21   |

| WH<br>VH<br>UH       | 28<br>32<br>36           | TYPE 7<br>TYPE 7<br>TYPE 7 | Gate driver output pin for the high-side Nch Power FET. Use gate resistors for wave-shaping                                                                                                         | 21   |

| VDH                  | 37                       | TYPE 14                    | Sense input for supply voltage and short circuit detection of high side power Fets. Connect through 100 $\Omega$ resistor to common drain of the power bridge                                       | 21   |

| PGND                 | 38                       | TYPE 10,<br>11             | GND pin for the charge pump                                                                                                                                                                         |      |

| VGL                  | 39                       | TYPE 10                    | Power supply pin for low-side gate drive. Connect decoupling capacitor between this pin and GND                                                                                                     | 19   |

| CHP                  | 40                       | TYPE 11                    | Power supply pin for high-side gate drive. Connect decoupling capacitor between this pin and VS                                                                                                     | 19   |

# PIN DESCRIPTION (continued)

| Pin Name | Pin No | TYPE    | Description                                                                                                                                                                                      | Page |

|----------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CP1N     | 41     | TYPE 10 | Charge transfer pin of the Charge pump (1N). Connect capacitor between CP1P and CP1N                                                                                                             | 19   |

| CP1P     | 42     | TYPE 10 | Charge transfer pin of the Charge pump (1P). Connect capacitor between CP1P and CP1N                                                                                                             | 19   |

| CP2P     | 43     | TYPE 11 | Charge transfer pin of the Charge pump (2P). Connect capacitor between CP2P and CP2N                                                                                                             | 19   |

| CP2N     | 44     | TYPE 11 | Charge transfer pin of the Charge pump (2N). Connect capacitor between CP2P and CP2N                                                                                                             | 19   |

| TEST     | 45     | TYPE 15 | Factory test pin. Connect to GND                                                                                                                                                                 |      |

| VS       | 46     |         | Power supply pin                                                                                                                                                                                 |      |

| WAKE     | 47     | TYPE 6  | WAKE pin. "H" = Operating mode, "L" or "Open" = Sleep mode. In Sleep mode all gate drivers are high-impedance. To protect the power stage, pull-down resistors on the gate lines may be required | 18   |

| EN       | 48     | TYPE 3  | Motor stage Enable pin. "H" = Normal enabled mode; "L" or "Open" = Standby mode. In Standby mode all gate drivers driven low. Motor freewheeling                                                 | 18   |

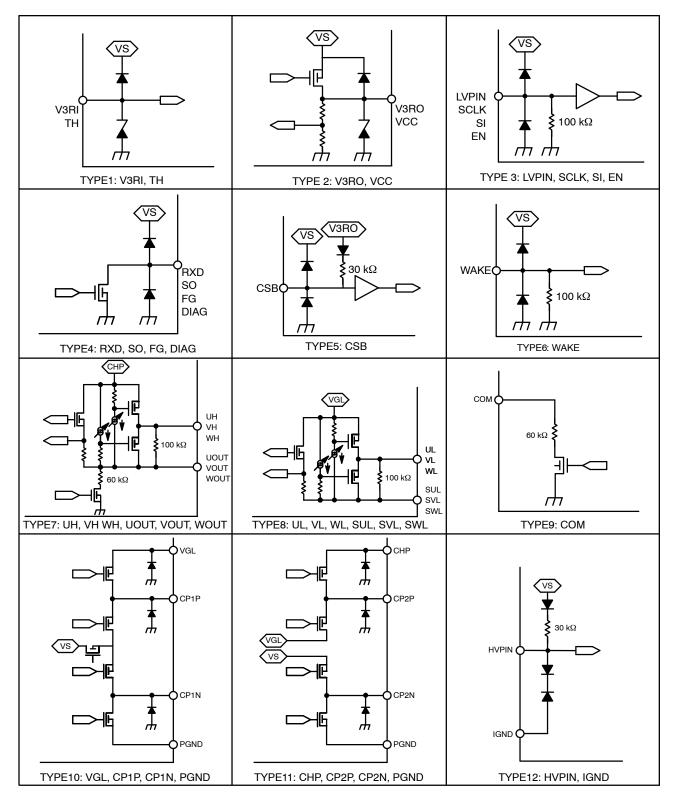

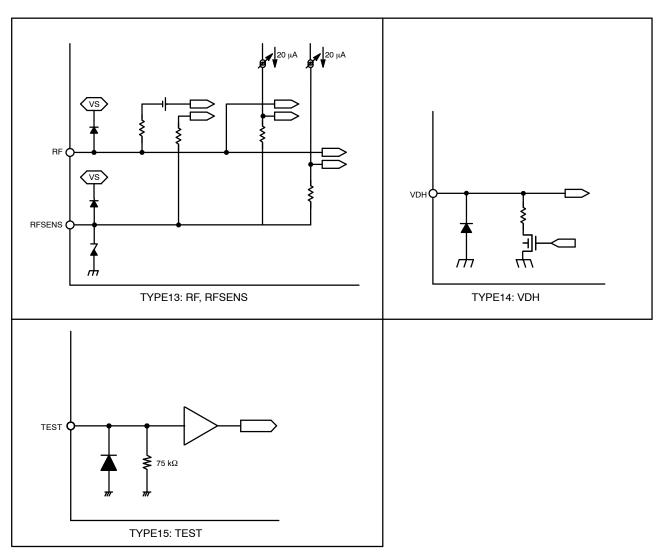

# **PIN CIRCUIT**

Figure 5. Pin Circuit

# PIN CIRCUIT (continued)

Figure 6. Pin Circuit (continued)

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                              | Pins                                  | Ratings     | Unit |

|----------------------------------------|---------------------------------------|-------------|------|

| Supply Voltage                         | VS                                    | -0.3 to 40  | V    |

| Sense Input for Supply Voltage         | VDH                                   | -0.3 to 40  | V    |

| Charge Pump Voltage (High Side)        | CHP                                   | -0.3 to 40  | V    |

| Charge Pump Voltage (Low Side)         | VGL                                   | -0.3 to 16  | V    |

| Logic Power Supply                     | VR3I, VR3O                            | -0.3 to 3.6 | V    |

| 5 V Regulator Voltage                  | VCC                                   | -0.3 to 5.5 | V    |

| Digital I/O Voltage1                   | WAKE,EN                               | -0.3 to 40  | V    |

| Digital I/O Voltage2                   | CSB, SCLK, SI, LVPIN, TEST            | -0.3 to 5.5 | V    |

| Digital Output Voltage                 | DIAG, FG, SO, RXD                     | -0.3 to 40  | V    |

| High Voltage PWMIN Voltage             | HVPIN                                 | -10 to 40   | V    |

| RF Input Voltage                       | RF                                    | -3 to 3.6   | V    |

| RFSENS Input Voltage                   | RFSENS                                | –0.3 to 1.0 | V    |

| TH Input Voltage                       | TH                                    | -0.3 to 3.6 | V    |

| Voltage Tolerance                      | UOUT, VOUT, WOUT, COM                 | –3 to 40    | V    |

| High-side Output                       | UH, VH, WH                            | –3 to 40    | V    |

| Low-side Output                        | UL, VL, WL                            | –3 to 16    | V    |

| Low-side Source Output Voltage         | SUL, SVL, SWL                         | -3 to 3.6   | V    |

| Voltage between HS Gate and Phase      | UH–UOUT,VH–VOUT,WH–WOUT               | -0.3 to 40  | V    |

| Voltage between LS Gate and Source     | UL-SUL, VL-SVL, WL-SWL                | –0.3 to 16  | V    |

| Output Current                         | UH,VH,WH,UL,VL,WL<br>pulsed (duty 5%) | 50<br>400   | mA   |

| Open Drain Output Current              | DIAG, FG, SO, RXD                     | 10          | mA   |

| Thermal Resistance ( $R_{\theta jA}$ ) | with Board (Note 1)                   | 47          | °C/W |

| ESD Human Body Model                   | AEC Q100-002                          | 2           | kV   |

| ESD Charged Device Model               | AEC Q100-011                          | 750         | V    |

| Storage Temperature                    |                                       | –55 to 150  | °C   |

| Junction Temperature                   |                                       | -40 to 150  | °C   |

| F                                      | (Note 2)                              | 150 to 175  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

76.2 × 114.3 × 1.6 mm, glass epoxy board.

Operation outside the Operating Junction temperature is not guaranteed. Operation above 150°C should not be considered without a written agreement from ON Semiconductor Engineering staff.

# **ELECTRICAL CHARACTERISTICS**

(Valid at a junction temperature range from  $-40^{\circ}$ C to  $150^{\circ}$ C, for supply Voltage 6.0 V  $\leq$  VS  $\leq$  28 V. Typical values at 25°C and VS = 12 V unless specified otherwise)

| Parameter                           | Symbol          | Condition                                     | Min   | Тур  | Max   | Unit |

|-------------------------------------|-----------------|-----------------------------------------------|-------|------|-------|------|

| Supply-voltage Range                | VS              | Normal mode                                   | 6     | 12   | 28    | V    |

|                                     |                 | Device fully functional                       | 5.5   | -    | 28    | V    |

|                                     |                 | Full logic functionality,<br>driver stage off | 4.5   | _    | 40    | V    |

| Supply Current into VS              | I <sub>s1</sub> | V3RO = V3RI<br>EN = L                         | -     | 15   | 25    | mA   |

|                                     | ls <sub>2</sub> | Sleep Mode                                    | -     | 40   | 80    | μΑ   |

| Operational junction<br>Temperature | Торј            |                                               | -40   | -    | 150   | °C   |

| OUTPUT BLOCK (UH, VH, WH            | I, UL, VL, WL)  | •                                             |       | •    | •     |      |

| Low-side Output<br>On-resistance 1  | RON(L1)         | "L" level lo = 10mA                           | -     | 6    | 15    | Ω    |

| Low-side Output<br>On-resistance 2  | RON(L2)         | "H" level lo = -10mA                          | -     | 12   | 22    | Ω    |

| High-side Output<br>On-resistance 1 | RON(H1)         | "L" level lo = 10mA                           | -     | 6    | 15    | Ω    |

| High–side Output<br>On–resistance 2 | RON(H2)         | "H" level lo = -10mA                          | -     | 12   | 22    | Ω    |

| DRIVE OUTPUT BLOCK (PWN             | A BLOCK)        |                                               |       |      |       |      |

| Drive Output<br>PWM Frequency       | fPWMO           |                                               | 18.5  | 19.5 | 20.5  | kHz  |

| Output PWM Duty Cycle<br>Resolution | ΔPWMDUTY        | (Note 3)                                      | -     | -    | 0.1   | %    |

| 3 V CONSTANT VOLTAGE OU             | TPUT            |                                               |       |      |       |      |

| Output Voltage                      | V3RO            |                                               | 3.135 | 3.3  | 3.465 | V    |

| Voltage Regulation                  | ΔV3R1           | VS = 6.0 to 28 V                              | -     | -    | 50    | mV   |

| Load Regulation                     | ΔV3REG2         | lo = 5 mA to 25 mA                            | -     | -    | 50    | mV   |

| Current Limit                       | IV3RO           | Not for external loads > 5 mA                 | 50    | -    | -     | mA   |

| VCC 5 V CONSTANT VOLTAG             | E OUTPUT        |                                               |       |      |       |      |

| Output Voltage                      | VC5RO           | VS = 6.0 to 28 V                              | 4.75  | 5.00 | 5.25  | V    |

| Voltage Regulation                  | ∆VC5R1          | VS = 6.0 to 28 V                              | -     | -    | 50    | mV   |

| Load Regulation                     | ΔVC5R2          | lo = 5 mA to 25 mA                            | -     | -    | 50    | mV   |

| Current Limit                       | IVCC5V          |                                               | 50    | -    | -     | mA   |

| VCC 3 V CONSTANT VOLTAG             | E OUTPUT        |                                               |       |      |       |      |

| Output Voltage                      | VC3RO           |                                               | 3.135 | 3.3  | 3.465 | V    |

| Voltage Regulation                  | ∆VC3R1          | VS = 6.0 to 28 V                              | -     | -    | 50    | mV   |

| Load Regulation                     | ∆VC3R2          | lo = 5 mA to 25 mA                            | -     | -    | 50    | mV   |

| Current Limit                       | IVCC3V3         |                                               | 50    | -    | -     | mA   |

| LOW-SIDE GATE VOLTAGE C             | OUTPUT (VGL PI  | N)                                            |       |      |       |      |

| Low-side Output Voltage1            | VGLH1           | $6.0 <\!\!VS \leq 8.0$ V lo = $-10$ mA        | 8.0   | 12.0 | 14.0  | V    |

| Low-side Output Voltage2            | VGLH2           | $8.0 < VS \le 20 V lo = -10 mA$               | 10.0  | 12.0 | 14.0  | V    |

| Low-side Output Voltagez            | VGENZ           |                                               |       |      |       |      |

# ELECTRICAL CHARACTERISTICS (continued)

(Valid at a junction temperature range from  $-40^{\circ}$ C to  $150^{\circ}$ C, for supply Voltage 6.0 V  $\leq$  VS  $\leq$  28 V. Typical values at 25°C and VS = 12 V unless specified otherwise)

| Parameter                                    | Symbol      | Condition                                                                    | Min        | Тур         | Max         | Unit |

|----------------------------------------------|-------------|------------------------------------------------------------------------------|------------|-------------|-------------|------|

| HIGH-SIDE OUTPUT VOLTAGE                     | E (CHP PIN) |                                                                              |            |             |             |      |

| Internal Charge Pump<br>Oscillator frequency | FCP         | SSCG = 0                                                                     | 49.6       | 52.1        | 54.6        | kHz  |

| Boost Voltage1                               | VGHH1       | $6.0 \le VS \le 8.0 V$<br>lo = -10 mA                                        | VS<br>+6.0 | VS<br>+12.0 | VS<br>+14.0 | V    |

| Boost Voltage2                               | VGHH2       | $8.0 < VS \le 20 V$<br>lo = -10 mA                                           | Vs<br>+9.0 | VS<br>+12.0 | VS<br>+14.0 | V    |

| Boost Voltage3                               | VGHH3       | $\begin{array}{l} 20 < VS \leq 28 \ V \\ Io = -10 \ mA \end{array}$          | VS<br>+6.0 | -           | -           | V    |

| CHP Voltage Limit                            | VCHPLIM     | VS = 28 V                                                                    | 34         | 36.5        | 38          | V    |

| PWMIN INPUT PIN IN LOW FRE                   | EQUENCY MOD | )E                                                                           |            |             |             |      |

| Input PWM Frequency Range                    | fLPWM       | PWMF = 0<br>Low frequency mode                                               | 5.3        | -           | 1000        | Hz   |

| PWM Signal Timeout                           | TLPWMIN     | PWMF = 0<br>Low frequency mode                                               | -          | 210         | 220         | ms   |

| PWMIN INPUT PIN IN HIGH FR                   | EQUENCY MOI | DE                                                                           |            |             | - <b>-</b>  |      |

| Input PWM Frequency Range                    | fHPWM       | PWMF = 1<br>High frequency mode<br>PWMINSEL=1<br>LVPIN is used for PWM input | 5.3        | -           | 18500       | Hz   |

| DIGITAL INPUT PIN (CSB)                      |             |                                                                              |            |             |             |      |

| High-level Input Voltage                     | VIH1        |                                                                              | 0.8×V3RO   | -           | -           | V    |

| Low-level Input Voltage                      | VIL1        |                                                                              | -          | _           | 0.2×V3RO    | V    |

| Input Hysteresis Voltage                     | VIHYS1      |                                                                              | 0.1        | 0.35        | 0.6×V3RO    | V    |

| Pull-up Resistance                           | RDVI1       |                                                                              | 15         | 30          | 60          | kΩ   |

| DIGITAL INPUT PIN (SCLK, SI,                 | LVPIN)      |                                                                              |            |             |             |      |

| High-level Input Voltage                     | VIH2        |                                                                              | 0.8×V3RO   | -           | -           | V    |

| Low-level Input Voltage                      | VIL2        |                                                                              | -          | -           | 0.2×V3RO    | V    |

| Input Hysteresis Voltage                     | VIHYS2      |                                                                              | 0.1        | 0.35        | 0.6×V3RO    | V    |

| Pull-down Resistance                         | RDVI2       |                                                                              | 50         | 100         | 200         | kΩ   |

| WAKE INPUT PIN                               |             |                                                                              |            |             |             |      |

| High-level Input Voltage                     | VIH3        |                                                                              | 2.5        | -           | -           | V    |

| Low-level Input Voltage                      | VIL3        |                                                                              | -          | -           | 0.6         | V    |

| Internal Pull-down Resistance                | RDVI3       |                                                                              | 50         | 100         | 200         | kΩ   |

| EN INPUT PIN                                 |             |                                                                              |            |             |             |      |

| High-level Input Voltage                     | VIH4        |                                                                              | 0.8×V3RO   | -           | -           | V    |

| Low-level Input Voltage                      | VIL4        |                                                                              | -          | -           | 0.2×V3RO    | V    |

| Input Hysteresis Voltage                     | VIHYS4      |                                                                              | 0.1        | 0.35        | 0.6×V3RO    | V    |

| Pull-down Resistance                         | RDVI4       |                                                                              | 50         | 100         | 200         | kΩ   |

| TEST INPUT PIN                               |             |                                                                              |            |             |             |      |

| High-level Input Voltage                     | VIH5        |                                                                              | 0.8×V3RO   |             |             | V    |

| Low-level Input Voltage                      | VIL5        |                                                                              |            |             | 0.2×V3RO    | V    |

| Input Hysteresis Voltage                     | VIHYS5      |                                                                              | 0.1        | 0.35        | 0.6×V3RO    | V    |

| Pull-down Resistance                         | RDVI5       |                                                                              | 37.5       | 75          | 150         | kΩ   |

# ELECTRICAL CHARACTERISTICS (continued)

(Valid at a junction temperature range from  $-40^{\circ}$ C to 150°C, for supply Voltage 6.0 V  $\leq$  VS  $\leq$  28 V. Typical values at 25°C and VS = 12 V unless specified otherwise)

| Parameter                                     | Symbol                       | Condition                                                                                                                       | Min        | Тур                      | Max     | Unit |

|-----------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------|---------|------|

| DIGITAL OUTPUT PIN (SO, FG,                   | DIAG, RXD)                   |                                                                                                                                 |            |                          |         |      |

| Output Voltage                                | VOL                          | lo = 1 mA pull-up current                                                                                                       | -          | -                        | 0.2     | V    |

| Output Leakage Current                        | ILOLK                        |                                                                                                                                 | -          | -                        | 10      | μA   |

| CURRENT LIMIT / OVER-CURF                     | RENT PROTEC                  | TION (RF, RFSENS)                                                                                                               |            |                          |         |      |

| Current Limit Voltage 1                       | VRF11                        | Voltage between RF and RFSENS,<br>CLSEL = 0                                                                                     | 40         | 50                       | 60      | mV   |

| Current Limit Voltage 2                       | VRF12                        | Voltage between RF and RFSENS,<br>CLSEL = 1                                                                                     | 90         | 100                      | 110     | mV   |

| Over-current Detection<br>Voltage Threshold 1 | VRF21                        | Voltage between RF and RFSENS,<br>OCSEL = 00<br>The difference voltage between<br>VRF21 and the actual current limit<br>voltage | 15         | 25                       | 35      | mV   |

| Over-current Detection<br>Voltage Threshold 2 | VRF22                        | Voltage between RF and RFSENS,<br>OCSEL = 01<br>The difference voltage between<br>VRF22 and the actual current limit<br>voltage | 40         | 50                       | 60      | mV   |

| Over-current Detection<br>Voltage Threshold 3 | VRF23                        | Voltage between RF and RFSENS,<br>OCSEL = 10<br>The difference voltage between<br>VRF23 and the actual current limit<br>voltage | 65         | 75                       | 85      | mV   |

| Over-current Detection<br>Voltage Threshold 4 | VRF24                        | Voltage between RF and RFSENS,<br>OCSEL = 11<br>The difference voltage between<br>VRF24 and the actual current limit<br>voltage | 90         | 100                      | 110     | mV   |

| EXTERNAL THERMAL PROTEC                       | CTION (TH)                   | •                                                                                                                               |            |                          |         |      |

| Threshold Voltage Falling                     | VTH0<br>VTH1<br>VTH2<br>VTH3 | THTH[1:0] = 00<br>THTH[1:0] = 01<br>THTH[1:0] = 10<br>THTH[1:0] = 11                                                            | Тур –35    | 350<br>300<br>250<br>200 | Тур +35 | mV   |

| Hysteresis Range                              | VTHHYS                       |                                                                                                                                 | 25         | 50                       | 75      | mV   |

| THERMAL PROTECTION                            |                              |                                                                                                                                 |            |                          |         |      |

| Thermal Warning Temperature                   | TTW0<br>TTW1                 | (Junction Temperature) (Note 3)<br>TSTS = 0<br>TSTS = 1                                                                         | 125<br>150 | _                        | -       | °C   |

| Thermal Warning Temperature<br>Hysteresis     | TTWHYS                       | (Junction Temperature) (Note 3)                                                                                                 | -          | 25                       | -       | °C   |

| Thermal Shutdown<br>Temperature               | TTSD0<br>TTSD1               | (Junction Temperature) (Note 3)<br>TSTS = 0<br>TSTS = 1                                                                         | 150<br>175 | _                        | -       | °C   |

| Thermal Shutdown<br>Temperature Hysteresis    | TTSDHYS                      | (Junction Temperature) (Note 3)                                                                                                 |            | 25                       | -       | °C   |

| VOLTAGE MONITORING (VS, C                     | HP, VGL, VCC)                |                                                                                                                                 |            |                          | •       |      |

| VS Under-voltage Detection                    | VSLV                         |                                                                                                                                 | 4.8        | _                        | 5.1     | V    |

|                                               | 1                            |                                                                                                                                 | 0.1        | 0.25                     | 0.4     | V    |

| VS Under-voltage Detection<br>Hysteresis      | VSLVHYS                      |                                                                                                                                 |            |                          |         |      |

| VS Under-voltage Detection                    | VSLVHYS<br>VSHV              |                                                                                                                                 | 30.5       | -                        | 35.5    | V    |

# ELECTRICAL CHARACTERISTICS (continued)

(Valid at a junction temperature range from  $-40^{\circ}$ C to  $150^{\circ}$ C, for supply Voltage 6.0 V  $\leq$  VS  $\leq$  28 V. Typical values at 25°C and VS = 12 V unless specified otherwise)

| Parameter                                    | Symbol         | Condition                           | Min     | Тур  | Мах    | Unit |

|----------------------------------------------|----------------|-------------------------------------|---------|------|--------|------|

| VOLTAGE MONITORING (VS, C                    | CHP, VGL, VCC) | •                                   |         |      |        |      |

| VDH Over-voltage Detection                   | VDHHV          |                                     | 30.5    | _    | 35.5   | V    |

| VDH Over-voltage Detection<br>Hysteresis     | VDHHVHYS       |                                     | 1.5     | 2.0  | 2.5    | V    |

| CHP Under-voltage Detection                  | CHPLV          |                                     | VS+4.5  | _    | VS+5.5 | V    |

| CHP under-voltage Detection<br>Hysteresis    | CHPLVHYS       |                                     | 0.2     | 0.4  | 0.7    | V    |

| VGL Under-voltage Detection                  | VGLLV          |                                     | 4.5     | _    | 5.5    | V    |

| VGL Under-voltage Detection<br>Hysteresis    | VGLLVHYS       |                                     | 0.2     | 0.4  | 0.7    | V    |

| VCC3.3 under-voltage<br>Detection            | VCLV3          | REGSEL = 0, VCEN = 1,<br>VCLVPO = 0 | 2.3     | -    | 2.7    | V    |

| VCC3.3 under-voltage<br>Detection Hysteresis | VCLVHYS3       | REGSEL = 0,<br>VCLVPO = 0           | 0.1     | 0.25 | 0.4    | V    |

| VCC5.0 under-voltage<br>Detection            | VCLV5          | REGSEL = 1, VCEN = 1,<br>VCLVPO = 0 | 3.8     | -    | 4.2    | V    |

| VCC5.0 under-voltage<br>Detection Hysteresis | VCLVHYS5       | REGSEL = 1,<br>VCLVPO = 0           | 0.1     | 0.25 | 0.4    | V    |

| hvpin pin                                    | •              | •                                   |         |      |        |      |

| Internal Pull-up Resistance                  | RI5            |                                     | 15      | 30   | 60     | kΩ   |

| High-level Input Voltage                     | VIH5           |                                     | 0.6×VS  | _    | VS     | V    |

| Low-level Input Voltage                      | VIL5           |                                     | 0       | _    | 0.4×VS | V    |

| Input Hysteresis Voltage                     | VIHYS5         |                                     | 0.05×VS | _    | 0.2×VS | V    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.3. Not tested in production. Guaranteed by design.

# DETAILED FUNCTIONAL DESCRIPTION

The LV8961H integrates full sensor-less brushless DC motor commutation and Proportional/Integral (PI) speed control. A robust startup algorithm combined with OTP registers for important system parameters make this IC a solution of choice for many BLDC applications which need to turn a motor in one direction only such as pumps, fans, etc. No detailed BLDC commutation knowledge is necessary.

Building a BLDC application with the LV8961H is even simpler than building a DC motor. Only a PWM pulse train is necessary to control the motor – either directly or via speed control. Switch–only applications are also possible. Speed and error information can be fed back to the control unit via FG and DIAG outputs.

If more complex operation and flexibility are required the LV8961H can be combined with a small microcontroller. The LV8961H implements motor commutation and includes all necessary support circuitry for the microcontroller such as:

- 5 V / 3.3 V Power supply

- Integrated watchdog timer

- External Temperature Sensor

In case of system errors such as a missing control signal, or a watchdog error, the LV8961H includes auto-run settings. If one of those errors occur and connection to the microcontroller is lost, the motor can continue running at a pre-defined fixed duty cycle of 25%, 50%, 75% or 100% and TAG\_L or TAG\_H.

#### Motor Commutation

Motor position is detected using the BEMF of the un-driven phase of a rotating three-phase motor relative to its neutral point connected to COM. BEMF monitoring can be detected at 2 points in each phase of U/V/WOUT, and there are 6 zero crossing signal in 3 phase in total with 6 un-driven windows. Once an adequate BEMF level has been detected voltages applied via PWM to the other two phases of the motor maintain rotation. The digital equivalent of the BEMF signal appears at FG.

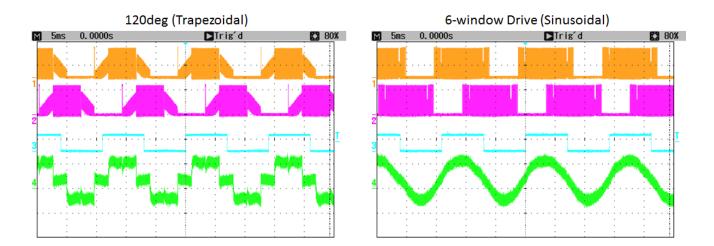

Two different PWM patterns can be selected via register SLMD to match motors with trapezoidal or sinusoidal BEMF.

Figure 7. Trapezoidal vs. Sinusoidal Drive (CH1, 2 = U, V Phase Voltage, CH3 = FG, CH4 = U Phase Current)

The sinusoidal drive each phase is driven with 6 windows for BEMF monitoring. This results in sinusoidal drive current with lower total harmonic distortion, reducing both torque ripple and noise. Trapezoidal drive results in a higher voltage across the motor phases and may be preferable for high torque and high speed operation.

## **Rotor Position Detection**

The rotor position is detected with BEMF zero cross timing. To detect the BEMF, the short window is opened by making the phase current zero or the phase float. Four types of the window mode are provided.

• 6-window mode

All zero crosses (rising and falling) for all three phases will be detected by opening 6 windows per electrical cycle. It gives best robustness to secure the all zero cross detection. However, the current waveform distortion will be higher. At the start–up, this 6–window mode is automatically selected.

• 3-window mode

One rising zero cross for each phase will be detected by opening 3 windows per electrical cycle. Balanced (or same) waveform is applied among three phases.

# • 1-window mode

Rising zero cross of only phase U will be detected by opening one window per electrical cycle. Only phase U has the window, and the others (V and W) doesn't. Therefore, the current waveform distortion will be minimized for the other phases.

# • 2-window mode

Rising and falling zero crosses of only phase U will be

detected by opening one window per electrical cycle. Only phase U has the windows, and the others (V and W) doesn't.

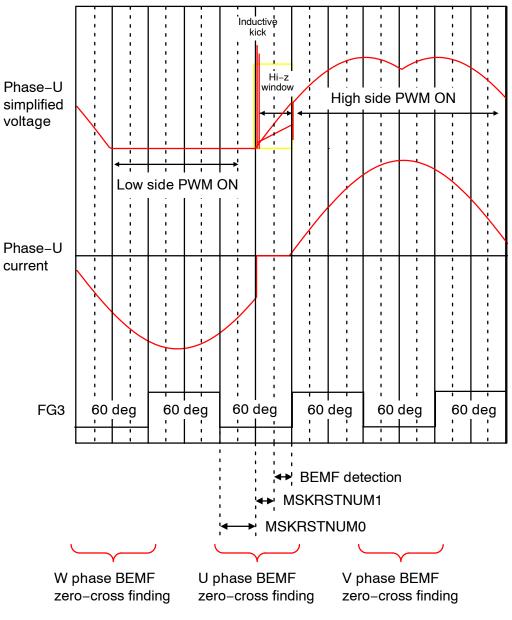

# BEMF Window Timing

Figure 8 shows a timing chart of the BEMF window with simplified phase voltage and current waveform illustrations. It is the case of 3–window mode particularly as an example.

Figure 8. BEMF Window Timing Parameters

(1) MSKRSTNUM0\_\*\*\*

Where, \*\*\* is ONE (for 1-window mode), TWO (for 2-window mode), THR (for 3-window mode), SIX (for 6-window mode), or INI (for start-up 6-window mode).

MSKRSTNUM0 defines the time from the previous BEMF detection to the start of the Hiz window where the phase output turns off.

MSKRSTNUM0\_THR[3:0] = x

$$x < 8 \rightarrow (15 + x * 3.75) \text{ deg}$$

$x \ge 8 \rightarrow (41.25 + (x - 7) * 1.875) \text{ deg}$

Example:

$x = 4 \rightarrow (15 + x * 3.75) \text{ deg} \rightarrow (15 + 4 * 3.75) \text{ deg} = 30 \text{ deg}$

### (2) MSKRSTNUM1\_\*\*\*

Where, \*\*\* is ONE (for 1-window mode), TWO (for 2-window mode), THR (for 3-window mode), SIX (for 6-window mode), or INI (for start-up 6-window mode).

MSKRSTNUM1 is a blanking (or ignoring) period from the start of the Hiz window defined by MSKTRTNUM0

#### Table 1.

until BEMF sensing. This blanking time prevents faulty zero cross detection due to the flyback caused by the window opening.

$MSKRSTNUM1\_THR[3:0] = x$ ((x + 1) + 1.875) deg

Example:

$x = 2 \rightarrow ((x + 1) + 1.875) \text{ deg} \rightarrow ((2 + 1) + 1.875) \text{ deg} = 5.625 \text{ deg}$

These window parameters are used commonly with the sinusoidal waveform shaping mode and trapezoidal waveform shaping mode.

|         | The Number              |                        |                                  |

|---------|-------------------------|------------------------|----------------------------------|

| WINDSEL | SLMD = L<br>Trapezoidal | SLMD = H<br>Sinusoidal | Window Timing Parameters         |

| 0       | 6                       | 6                      | MSKRSTNUM1_SIX<br>MSKRSTNUM0_SIX |

| 1       | 6                       | 3                      | MSKRSTNUM1_THR<br>MSKRSTNUM0_THR |

| 2       | 6                       | 2                      | MSKRSTNUM1_TWO<br>MSKRSTNUM0_TWO |

| 3       | 6                       | 1                      | MSKRSTNUM1_ONE<br>MSKRSTNUM0_ONE |

#### Maximum Motor Speed

The maximum physical motor speed of the application is limited by the internal clock to approximately 48000 electrical RPM. If this is exceeded the LV8961H coasts the motor until BEMF detection and drive can resume.

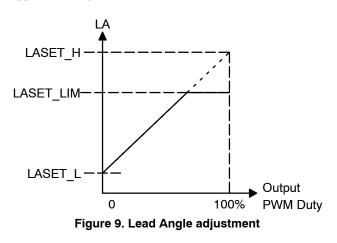

#### Lead Angle Setting

LV8961H can adjust the lead angle according to the output Duty.

Lead angle has the characteristic in Figure 8. It is set by the registers LASET\_L, LASET\_H and LASET\_LIM.

LASET\_L sets lead angle when the output duty is 0%, and LASET H sets lead angle when the output duty is 100%.

And then LASET\_LIM sets the upper limit when an application requires it.

#### Motor Startup

BEMF is used for rotor position sensing but for BEMF generation the motor has to be rotating. A stopped motor will initially be driven open-loop until BEMF can be detected.

Open-loop operation is motor parameter dependent. The most critical parameters depend on load and motor inertia. They are initial commutation frequency and PWM duty cycle (which affects motor flux density).

In the LV8961H, the initial commutation frequency is programmed with register STOSC. Flux density is regulated by limiting startup current with a current ramp. During this ramp the current limit is increased in 16 steps from 0 to the maximum current defined by the external shunt. The ramp time from 102 ms to 6.55 s is defined in register SSTT. Register CLREFEN\_STOP allows to disable the current ramp if necessary.

Fixed motor speed will be applied until either a valid BEMF has been detected in all three phases or the startup timer expires.

#### Motor Lock

This timer begins after the end of the current ramp and can be programmed from 400 ms to 6.4 s in register CPTM. If the timer expires a locked rotor error is flagged. In automatic retry mode, the LV8961H will restart after standby mode for time of eight times of CPTM.

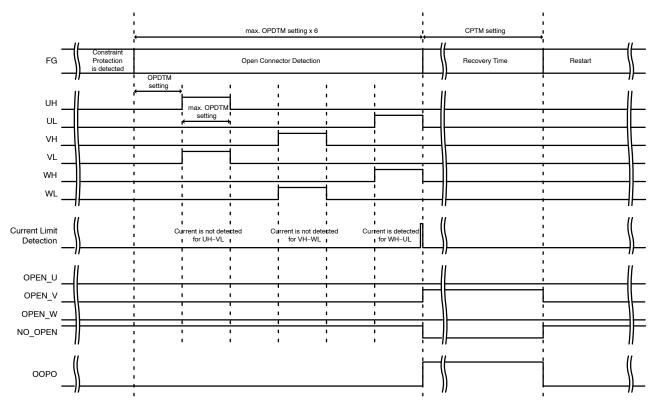

#### Motor Connect Open Detection

When the motor cannot be started for a certain period of time and it is in the startup mode, this IC flows current to

each coil, then determines IC is in a constraint state when current flows, or an open state when no current flows. The detection time for the current to flow can be selected by OPDTM register.

### Spin-up of Rotating Motors

The LV8961H can perform free–wheeling detection before applying the open loop spin–up algorithm described above. If the motor is already turning in the right direction the IC will continue with closed loop commutation. If the motor is turning in the wrong direction, the IC will wait for the motor to stop and then perform open–loop startup.

There are two scenarios where this behavior might not be desirable:

- 1. Fast Startup is required

- Free-wheeling detection takes up to one electrical revolution of the motor, which may be inacceptable for some applications. In this case free-wheeling detection can be disabled by setting FRREN

- 2. Wind–milling backwards

Should the motor be driven by some external force as it is freewheeling in the wrong direction the LV8961H will potentially wait forever. Should start-up under these conditions be required, free-wheeling detection must be disabled as well

#### Chip Activation, Shutdown and System States

After power up of VS and WAKE above 2.5 V the LV8961H wakes up. Standby mode is entered after VS has exceeded 5.5 V (min.).

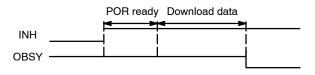

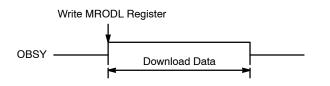

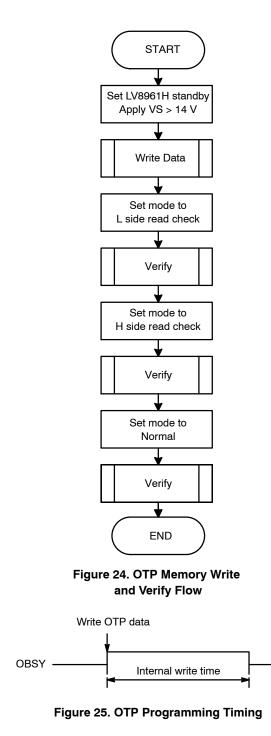

A high level on WAKE > 2.5 V (max.) activates the IC from sleep mode which enables the internal linear regulator at V3RO. Once the voltage on V3RO as sensed on V3RI has passed the power on reset (POR) threshold the system oscillator starts, and after 32 counts of the system clock

(1.6 µs typical) releases the internal digital reset which simultaneously starts the external regulator VCC and the charge–pump, and loads the system register contents from OTP into the internal registers. During the entire wake–up sequence of 8 ms (typ.) DIAG is masked for charge–pump and VCC under–voltage. After wake–up is complete, the IC enters Standby mode and DIAG is activated to display internal errors. During Standby mode full SPI access is possible.

A high on EN takes the LV8961H from Standby to Normal mode. Normal mode allows motor control and SPI access is limited. A low on EN disables the motor stage regardless of the PWM input and returns the part back to Standby mode.

The IC is shut down by taking WAKE below 0.6 V (min.). WAKE has priority over the state of EN, if EN hold functionality is desired; it needs to be implemented with an external diode from EN to WAKE.

## System States

LV8961H has three operating modes. The operating modes are controlled by WAKE and EN.

#### Sleep Mode

Sleep mode is a power saving mode. All circuits are powered down, charge pump is inactive and the SPI port is unusable. Activating WAKE allows the transition from the sleep mode to either Standby or Normal mode.

## Standby Mode

In Standby mode the OTP content has been transferred into the main registers. In this mode all outputs are turned off. Any internal writable register that is not locked can be configured by SPI interface.

## Normal Mode

In normal mode, outputs can be controlled and all blocks are active. All registers can be read through the SPI interface.

| Mode    | WAKE | EN | Internal Bias | Logic  | VCC     | Charge Pump | Drivers |

|---------|------|----|---------------|--------|---------|-------------|---------|

| Sleep   | L    | х  | Disable       | Reset  | Disable | Disable     | High–Z  |

| Standby | Н    | L  | Enable        | Active | Enable  | Enable      | Low     |

| Normal  | Н    | Н  | Enable        | Active | Enable  | Enable      | Enable  |

## **Supply Voltage Transients**

The LV8961H is well suited to operate during typical automotive transients. It is fully functional during start–stop transients, as it maintains all specified parameters for supply voltages from 6 V < VS < 28 V. If the supply voltage falls below 5 V, for example during cold–cranking, under–voltage error is flagged, but digital functionality is maintained until the internal regulator falls below its under–voltage lockout level of 2.2 V. The VCC regulator must be configured for 3.3 V if low transient operation is desired.

If over-voltage protection is enabled in MRCONF8 an over-voltage error is indicated if the supply rises beyond 28 V(min). In both under- and over-voltage error modes,

the power stage drivers UH, VH, WH and UL, VL, and WL go low, turning the external power stage high–impedance and letting the motor freewheel. The LV8961H will re–engage the motor after conditions have returned to normal.

## **System Power Supplies**

Three power supplies are integrated into the LV8961H:

- An internal 3.3 V regulator provides power to the digital and interface section

- The VCC regulator can be configured to provide 5 V or 3.3 V to an external processor and other loads

• A dual stage charge-pump allows 100% duty cycle operation and maintains full enhancement to the power stage at low input voltages

### Internal Regulator V3RO, V3RI

The internal regulator is supplied from VS, provides 3.3 V at V3RO. V3RI is connected to the power supply inputs of the control and logic circuit blocks. V3RO and V3RI need to be connected externally and bypassed to the GND plane for stability. V3RO must not be used for external loads.

## VCC Regulator

The VCC regulator may power external loads up to 50 mA (max). VCC becomes active during Standby mode and can be configured via register REGSEL to provide 5 V or 3.3 V. The wrong bit selection has a possibility to damage the microcontroller. Please make sure the appropriate selection. Under-voltage error is flagged if the output voltage drops below 4.2 V in 5 V operation, or 2.7 V in 3.3 V operation.

C<sub>CP1</sub>

The VCC regulator can be enabled or disabled with register VCEN.

## Charge Pump Circuit for CHP and VGL

C<sub>CP2</sub>

LV8961H has an integrated charge pump circuit for low-side and high-side pre-driver supply. Low side drive voltage at VGL is 12 V(typ.) and high side drive voltage at CHP is VS + 12 V(typ.). For functionality see Figure 10.

Under-voltage protection for the low side drivers activates if VGL falls below 4.8 V in which case the output FET's will be turned off and VGL under-voltage error is flagged in register MRDIAG. Over-voltage protection for the high side drivers activates if VS becomes greater than 28 V(min). In that event the driver stage is disabled, over-voltage error is flagged in register MRDIAG, and both VGL and CHP are discharged to prevent output circuit destruction.

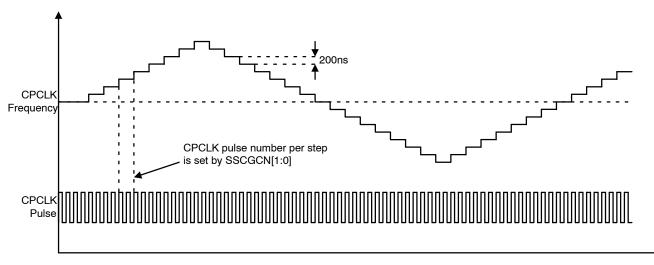

The charge pump circuit operates nominally at 52.1 kHz. A SSCG function is provided to add a spread–spectrum component for EMI reduction.

C<sub>VGL</sub> CCHP vs Current limitation Voltage clamping CP2F CP2N CP1 CP1N VGL CHP Supply for Supply for HS Pre-Drivers LS Pre-Drivers Buf Buf Figure 10. Charge Pump Circuit VGL(V) CHP(V) VCHPLIM CHE 20⊻ ίνs 12<u>V</u> VGI VS 12V 8V VS(V) VS(V) 30.5V 20V 30.5V 5.1V 6.0V 8.0V 5.1V 6.0V 8.0V 201/ ≁ CP ON VS over CP ON VS under VS under CP ON VGL=12V CP ON VS over voltage (max) CHP=VS+VGL CHP=VS+VGL voltage (max) VGL=VS\*2 voltage (min) voltage (min) Figure 11. High Side and Low Side Gate Voltages

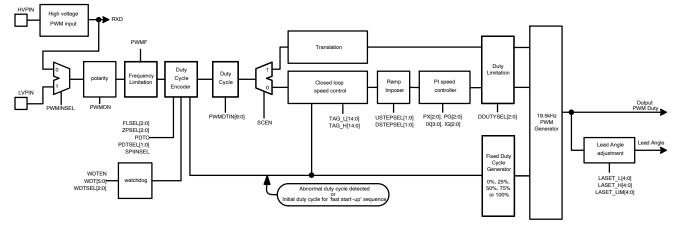

### INPUT PWM and SPEED CONTROL

The LV8961H provides three speed control methods through the input PWM signal:

- 1. Indirect PWM translation

- 2. Closed loop speed control

- 3. Direct register command

### Indirect PWM Translation

This is the preferred mode for stand-alone operation. The frequency range has two modes, high and low frequency. In the high frequency mode, it corresponds to frequency input up to 18.5 kHz. In the low frequency mode, it is limited to the frequency input up to 1 kHz, and when the frequency input is above 1 kHz, it is ignored. Frequency mode can be configured in high frequency mode by setting register PWMF to 1. In both modes the input PWM signal is compared against minimum PWM frequency thresholds to allow for more robust operation. Frequencies below 5.3 Hz (typ.) are considered as 0% or 100% duty cycle (no frequency).

The duty cycle of the PWM input signal is measured with a resolution of 10 bits. There is an inherent delay to detect and utilize this duty cycle information. It is the delay time from input PWM input signal to output PWM. The delay time is determined by

#### T<sub>PWM</sub> + 19.8 μs (max.)

Where,  $T_{PWM}$  is the period of the PWM input signal. 19.8  $\mu$ s is fixed value.

If faster start–up is necessary, see section "<u>Fast Startup</u>" below. If no frequency is detected after 210ms (typ.) the PWMPO flag is set in system warning register MRDIAG1. Even without PWM input the LV8961H can run as described below in section "<u>Fast Startup</u>".

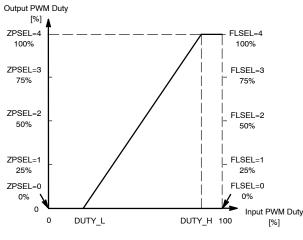

If a valid frequency was detected, the LV8961H evaluates the input duty cycle and translates it into an output duty cycle as shown in Figure 12. The output PWM frequency is fixed to 19.5 kHz (typ.).

Figure 12. Duty Cycle Translation

Input duty cycles lower than the minimum Duty setting by DUTY\_L register are considered a motor-off command and

will also reset the error registers. Input duty cycles higher than the maximum Duty setting by DUTY\_H register are considered a full drive command. Input to output duty cycle translation is described by the following formula:

|                    | 0                                                                                         | $0 \le d_{IN} \le DUTY_L$         |

|--------------------|-------------------------------------------------------------------------------------------|-----------------------------------|

| d <sub>OUT</sub> = | $\frac{100}{\text{DUTY}_H - \text{DUTY}_L} \times (\text{d}_{\text{IN}} - \text{DUTY}_L)$ | DUTY_L < d <sub>IN</sub> < DUTY_H |

|                    | 100                                                                                       | $DUTY_H \le d_{IN} \le 100$       |

#### Closed Loop Speed Control

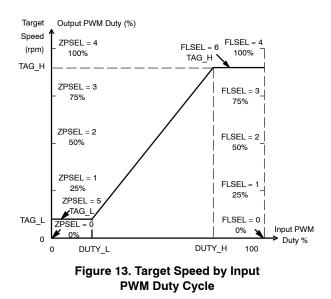

For stand-alone operation, the LV8961H offers a PI controller for motor speed which is activated by clearing bit SCEN. Frequencies below 5.3 Hz(typ.) are considered as 0% or 100% duty cycle (no frequency). The output PWM frequency is fixed to 19.5 kHz (typ.).

LV8961H provides Linear characteristic target speed setting as shown in Figure 13.

#### Direct Register Command

LV8961H allows user to access the register directly, which is connected to the control logic, and set the PWM duty cycle command from the PWMDTIN register. This mode can be configured by setting register SPIINSEL to 1. Also, FG frequency information can be obtained from the STATUS register by setting register STATSEL to 0h, and It can minimize delay that occurs when the PWM frequency is low.

#### The Control Algorithm

The LV8961H controls the motor speed by comparing the selected target speed to the actual motor speed and incorporating a PI controller with configurable gains for the P, I and T components which are stored in register MRSPCT7, MRSPCT8 and MRSPCT9 respectively.

## Ramping of Speed Control Values

While tight control is required for optimal speed tracking, it may be undesirable during large input changes as it may lead to sudden supply loading, increasing noise and motor wear. To limit the slope of the control signal, register USTEPSEL and DSTEPSEL imposes a ramp on an input step to slew the speed response of the motor.

Decreasing motor speed too fast results in energy recuperation back into the system. To limit over-voltage

during energy recuperation, the variable DWNSET allows to prevent energy recuperation entirely by the synchronous rectification off.

Figure 14. PWM Command Flow and Related Registers

#### Fast Startup

It may be desirable to have the motor start immediately after EN goes high and not wait for PWM input duty cycle evaluation. Two register settings enable motor operation during this evaluation time: bit PDTC determines if the motor should be running during this time at all, and PDTSEL selects a motor duty cycle of 25, 50, 75 or 100%. This is used as the initial value of the duty cycle command for the closed loop speed control mode. To guarantee smooth transition from fast startup to PWM operation it is important to apply a comparable external PWM duty cycle at startup.

#### Abnormal Duty Cycle Operation (100% or 0%)

For normal duty cycle controlled operation the PWM signal is expected to have a frequency between 5.3 Hz or more. If no frequency is detected, the LV8961H will flag PWMPO error and enter 0% or 100% duty cycle mode depending on the level of the PWM signal (all low or all high). Operation during this mode can be selected to be either no motor operation, or motor operation at a fixed motor duty cycle of 25, 50, 75 or 100% and TAG\_L or TAG\_H as defined by the variables FLSEL or ZPSEL. These PWM values do not enter into the speed control loop.

#### Limit the Amount of Change of Output Duty

LV8961H is possible to limit the amount of change in output duty to avoid sudden acceleration and deceleration by setting register DDUTYSEL. Limited duty can be selected from  $\pm 20.3, \pm 17.8, \pm 15.2, \pm 12.7, \pm 10.2, \pm 7.6$  and  $\pm 5.1\%$ .

#### Speed Feedback FG

The motor speed is shown at open drain output FG where the transitions are direct representations of the BEMF signal transitions on the motor. The relationship between motor rotation and FG pulses is defined in register FGOF.

#### Fault Output DIAG

A low on open drain output DIAG indicates a system fault and a shutdown of the driver stage. Per default all system faults self-recover when the fault condition is removed. For some potentially destructive faults such as over-current, FET-short circuit and locked rotor conditions, it is possible to latch the fault condition. For more information on system diagnostics see section "System Errors and Warnings".

#### **High Voltage PWM Interface**

The PWM interface translates a VS level signal with a threshold of 50%(Typ) VS to a digital signal appearing at RXD pin. This signal can be used for input PWM translation from outside units to the microcontroller.

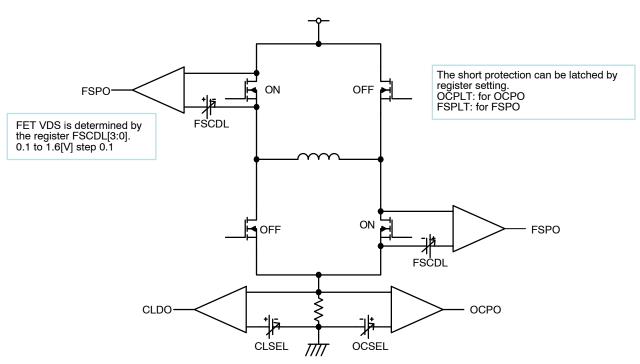

#### **Gate Drive Circuit**

The gate drive circuit of the LV8961H includes 3 half-bridge drivers which control external N-Channel FETs for the motor phases U, V and W. The high side drivers UH, VH, WH switch their gate connection either to CHP or the respective phase connection UOUT, VOUT and WOUT. The low-side drivers are switched from VGL to the corresponding source connection SUL, SVL, SWL. Both high and low side switches are not current controlled. Slope control has to be implemented with external components.

Current shoot-through protection of the bridge-drivers is implemented by a dead-time counter that delays the turning- on of the complementary switch. The dead-time can be programmed from 200 ns <  $t_{FDTI}$  < 6.4 µs into 5bit parameter FDTI. To protect against external shorts the drain–source voltage of the active external Power FETs is monitored as well. 4 bit register FSCDL selects a short–circuit shutoff voltage  $100 \text{ mV} < V_{FSCLD} < 1.6 \text{ V}$ . To suppress false triggering during the rising edge of FET activation, FSCDT selects the masking time.

#### Current Limit and Over-current Shutoff

An integrated current sense amplifier implements current limiting and over-current shutoff by measuring the motor phase current across a single shunt between RF and RFSENS.

Figure 15 shows a summary of the current limit and the over-current shutoff, and the descriptions for each function are in the following sections.

In Sleep mode, the Hi-side gate output and Low-side gate output of each U, V, W phase become Hi-Z.

A 100 K $\Omega$  pull-down resistor is built in between UH and UOUT of the Hi-side gate driver output so that the gate and source of the external FET do not become Hi-Z.

The low side output also has a built-in  $100 \text{ k}\Omega$  pull-down resistor between the UL and SUL terminals. (V and W phases also have  $100 \text{ K}\Omega$  built-in)

**Table 2. SUMMARY OF POWER STAGE PROTECTIONS**

As an external component of the application circuit, the resistance between the gate and source of the FET can be reduced.

### Cycle-by-cycle Current Limit

If the voltage between RF and RFSENS exceeds VRF1, the active bridge is turned off until the next PWM period. VRF1 can be selectable 100 mV(Typ) or 50 mV(Typ) by register CLSEL. To suppress switching transients a current limit blanking time 0.2  $\mu$ s < t<sub>CLMASK</sub> < 3.2  $\mu$ s can be programmed into register CLMASK.

During soft-start this current limit is ramped from 0 to VRF1 in 16 steps during a programmable time 102 ms  $< t_{SSTT} < 6.55$  s as defined in register SSTT.

#### Over-current Shutoff

If the bit OCPEN is set and the voltage between RF and RFSENS exceeds VRF2, the LV8961H goes into over-current shutoff and all gate drivers are driving low turning the power FETs high–impedance. VRF2 can be selectable VRF1 + 25 mV, +50 mV, +75 mV and +100 mV by register OCSEL. To suppress switching transients an over-current shutoff blanking time 0.2  $\mu$ s < t<sub>OCMASK</sub> < 3.2  $\mu$ s can be programmed into register OCMASK.

| Current        | Purpose   | Flag | Sense point        | Threshold                                | Turn-off | Recovery       |

|----------------|-----------|------|--------------------|------------------------------------------|----------|----------------|

| Cycle-by-cycle | Limiter   | CLDO | Sense Resistor VRF | VRF1 100 mV or 50 mV                     | PWM FET  | Next PWM cycle |

| Short to VS    | Protector | OCPO | Sense Resistor VRF | VRF1+25 mV, +50 mV,<br>+75 mV and 100 mV | All FET  | 50 ms later    |

|                |           | FSPO | FET VDS MOUT-SXL   | Configurable                             |          |                |

| Short to GND   | Protector | FSPO | FET VDS VDH-MOUT   | Configurable                             | All FET  | 50 ms later    |

Figure 15. Current Limit vs. Over-current Shutoff

### **Temperature Sensing**

The LV8961H measures internal die temperature and implements internal thermal warning and shutoff. It is also possible to protect external devices by monitoring the voltage at pin TH. Internal and external over-temperature can shut down the driver section.

#### Internal Over-temperature Measurement

A thermal warning is issued if the internal temperature of the device reaches approximately  $25^{\circ}$ C below the over-temperature shutoff level. The shutoff level is selected by bit TSTS as  $150^{\circ}$ C or  $175^{\circ}$ C(min).

#### External Over-temperature Shutoff

An analog comparator triggers external over–temperature error if the voltage at pin TH falls below the two bit programmable level 0.2 V <  $V_{THTH}$  < 0.35 V as defined by register THTH. For external temperature measurement connect a resistor between V3RO and TH and an NTC between TH and AGND. The programmed threshold voltage at  $V_{THTH}$  should be reached at the intended thermal shutdown temperature of the external component to be protected. During the over–temperature condition, the gate drivers are disabled and a flag, THPO in MRDIAG0 is set.

Figure 16. Example Circuit for External Temperature Sensing

## Watchdog Operation

The LV8961H includes a watchdog timer to monitor a companion microcontroller and disable the motor if the

microcontroller stops working properly. Bit WDTEN enables and disables the watchdog timer. Access to this bit can be blocked – see section "OTP Register" for details. The enabled watchdog will issue an error whenever the watchdog time 1.6 ms <  $t_{WDT}$  < 102.4 ms expires. A write of 00h to register MRRST resets the watchdog timer.

A watchdog timeout can result in either a motor stop, or motor operation at four predefined duty cycles of 25%, 50%, 75% or 100% and TAG\_L or TAG\_H as defined by WDTSEL. The duty cycle is directly applied to the power stage, not through the speed selection registers. The microprocessor is not re-set.

#### System Errors and Warnings

All system errors and most warnings cause a transition on DIAG. The polarity of this transition can be selected in bit DIAGSEL. The ability of stand–alone applications without microcontroller to react to errors and warnings is limited. For this case various auto–retry strategies are implemented.

If a companion microcontroller exists, more complex error handling is possible and DIAG should be connected to an interrupt input of the microcontroller. Errors that may cause serious damage such as short–circuit, over–current and locked rotor can be latched by enabling the corresponding latch bit in MRCONF9. In this case the LV8961H will keep the output stage disabled until the latch is cleared by one of the following actions:

- Power on reset

- EN low

- Input the output duty 0% or 0 rpm command

- SPI write of FFh to MRRST

If bit DLTO is set ONLY latched errors will cause a transition of DIAG. To detect the other less serious errors and warnings, the diagnostic registers MRDIAG0 /MRDIAG1/MRDIAG2 have to be read regularly via SPI access.

| ADDR  | Bit | Error   | Description        | Enabled Set | Latched<br>Set | Self-Recovery Timing                         |

|-------|-----|---------|--------------------|-------------|----------------|----------------------------------------------|

| 0201h | 0   | OCPO    | Over-current Error | OCPEN       | OCPLT          | After 50 ms (typ.) the motor will re-start   |

| 0201h | 1   | VSLVPO  | VS Under-voltage   | N/A         | N/A            | Motor is re-started when voltage recovers    |

| 0201h | 2   | VSOVPO  | VS Over-voltage    | OVPEN       | N/A            | Motor is re-started when voltage<br>recovers |

| 0201h | 3   | CHPLVPO | CHP Under-voltage  | N/A         | N/A            | Motor is re-started when voltage<br>recovers |

| 0201h | 4   | VGLLVPO | VGL Under-voltage  | N/A         | N/A            | Motor is re-started when voltage recovers    |

| 0201h | 5   | FSPO    | FET Short Circuit  | FSPEN       | FSPLT          | After 50 ms (typ.) the motor will re-start   |

Table 3. ERROR AND WARNING DIAGNOSTIC REGISTER (Note 4)

| ADDR  | Bit                                    | Error   | Description                       | Enabled Set               | Latched<br>Set | Self-Recovery Timing                                         |

|-------|----------------------------------------|---------|-----------------------------------|---------------------------|----------------|--------------------------------------------------------------|

| 0201h | 6                                      | THPO    | External<br>Over-temperature      | THPEN                     | N/A            | Motor is re-started when temperature re-<br>covers           |

| 0201h | 7                                      | CPO     | Locked Rotor                      | CPEN                      | CPLT           | Wait 8 t <sub>CPTM</sub> periods (see " <u>Motor Lock</u> ") |

| 0202h | 0                                      | THWPO   | Chip Junction Warning             | THWEN                     | N/A            | Only warning                                                 |

| 0202h | 1                                      | THSPO   | Chip Junction<br>Over-temperature | N/A                       | N/A            | Motor is re-started when temperature recovers                |

| 0202h | 2                                      | WDTPO   | Watchdog Timeout                  | WDTEN                     | N/A            | Motor is re-started when WDT is reset                        |

| 0202h | 3                                      | CLDO    | Current Limit Warning             | CLDOEN                    | N/A            | Only warning                                                 |

| 0202h | 4                                      | OOPO    | Motor Open Detect                 | OOPOEN                    | N/A            | Same as Motor Lock protect                                   |

| 0202h | 5                                      | RCSMPO  | Register Checksum<br>Error        | N/A                       | N/A            | Write MRRST = 55h or MRODL = 00h or<br>MRODL = FFh           |

| 0202h | 6                                      | VCLVPO  | VCC under-voltage                 | VCLVPEN                   | N/A            | Motor is re-started when voltage recovers                    |

| 0202h | 7                                      | PWMPO   | PWM Input Fault                   | FLSEL<br>ZPSEL<br>PPDOSEL | N/A            | Motor is re-started when PWM input recovers                  |

| 0203h | 0                                      | VDHOVPO | VDH Over Voltage                  | VDHOVPEN                  | N/A            | Motor is re-started when voltage recovers                    |

| 0203h | 1                                      | STUPO   | Startup Operation                 | N/A                       | N/A            | Only warning                                                 |

| 0203h | 2                                      | SPCO    | Loss of speed lock                | N/A                       | N/A            | Only warning                                                 |

| 0203h | 3 FGERPO FG error protection<br>output |         | FG error protection<br>output     | FGERACCEN<br>FGERDECEN    | N/A            | Wait t <sub>RCVTM</sub> periods                              |

| 0203h | 4                                      | REGAZ   | Register data all 0<br>output     | N/A                       | N/A            | Only warning                                                 |

| 0203h | 5                                      | OTPAZ   | OTP data all 0 output             | N/A                       | N/A            | Only warning                                                 |

| Table 3. ERROR AND WARNING DIAGNOSTIC REGISTER (Note 4) (continued) |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

4. See register MRCONF 7 to 12 for error and warning activation, masking and latching options.

# **Detection of Loss of Commutation Synchronization**

The following three kinds of approach have been provided to detect the loss of commutation synchronization which is significant for sensorless motor control applications.

- 1. Open load

- 2. Abnormal rotational speed change

- 3. Locked rotor

The following sections describe the actual implementation of LV8961H for these approaches.

# **Open Load Detection**

Block Description

LV8961H can detect that the connector is open due to disconnection for instance. This function is enabled by setting OOPOEN = 1.

When this function is enabled, the current is flowed for certain time in the order of UH–VL, VH–WL, WH–UL after detecting the motor constraint state, and holds whether or not reach to current limitation in each case. When the current is not limited in two or more of these three states, it is judged as open and OOPO = 1 is output as result. For this reason, it

is necessary to select the time set by OPDTM that the current limit is always taken.

It can be checked which U, V, W connector is open by reading the status register. One connector opening of U, V, W can be distinguished, but when two or three openings overlap, it is judged that everything is open so it cannot be distinguished what is not open. Also, if only one of UH–VL, VH–WL, WH–UL doesn't reach to current limitation, it is judged that all phases are connected.

When automatic recovery mode is set, OOPO returns to 0 when the time set in the CPTM register (the constraint protection detection time multiplied by 8) has elapsed. When latch mode is set, OOPO returns to 0 by EN = L input, PWM 0% input, or MRRST command.

Because the open load detection is performed after the constraint protection detection, CPO = 1 is output.

The detection time of the current limit set by OPDTM register indicates the upper limit, and when LV8961H reaches to current limitation, the output is turned OFF immediately.

Figure 17 shows an example where automatic recovery mode is set and phase–V is detected to be open.

Figure 17. Timing Chart of OOPO

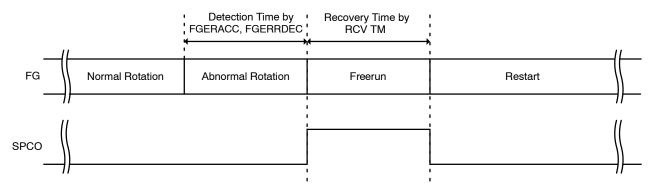

## Abnormal Rotational Speed Change Detection

#### **Block Description**

When FGERACCEN/FGERDECEN = 1, the rotation speed abnormality protection according to the FGERACC/FGERDEC register setting is valid respectively.

When the motor is accelerating, it is compared the number of times set by FGERACC with the number of consecutive times of zero cross detection immediately after the mask is opened, and it is judged to be abnormal if they match.

When the motor is decelerating, it is judged to be abnormal rotating after detection period shown in Table 4 is elapsed without zero crossing detection.

| FGERDEC[2:0] | Detection Setting                                    |

|--------------|------------------------------------------------------|

| 0            | (previous 60 electrical degrees period) $\times1.25$ |

| 1            | (previous 60 electrical degrees period) $\times$ 1.5 |

| 2            | (previous 60 electrical degrees period) $\times1.75$ |

| 3            | (previous 60 electrical degrees period) $\times$ 2   |

| 4            | (previous 60 electrical degrees period) $\times$ 3   |

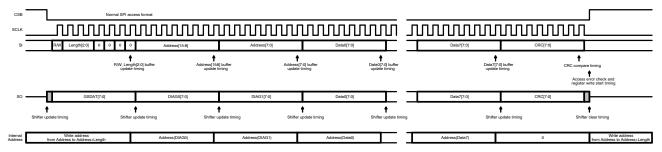

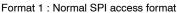

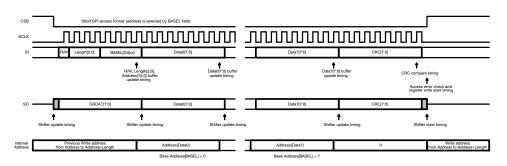

| 5            | (previous 60 electrical degrees period) $\times$ 4   |