#### **SPECIFICATIONS**

# PXIe-5763

#### 16-Bit, 500 MS/s, 4-Channel PXI FlexRIO Digitizer

This document lists the specifications for the PXIe-5763. Specifications are subject to change without notice. For the most recent device specifications, refer to *ni.com/support*.

### Contents

| Definitions                                                     | 1   |

|-----------------------------------------------------------------|-----|

| Conditions                                                      |     |

| Digital I/O                                                     |     |

| Digital I/O Single-Ended Channels                               |     |

|                                                                 |     |

| Digital I/O High-Speed Serial MGT                               |     |

| Reconfigurable FPGA                                             |     |

| Onboard DRAM                                                    | 5   |

| Analog Input                                                    | . 5 |

| General Characteristics                                         |     |

| Typical Specifications                                          | 5   |

| CLK/REF IN                                                      |     |

| General Characteristics                                         | 12  |

| Bus Interface                                                   | 15  |

| Maximum Power Requirements                                      | 15  |

| Physical                                                        | 16  |

| Environment                                                     | 16  |

| Operating Environment                                           | 16  |

| Storage Environment                                             | 16  |

| Shock and Vibration                                             | 16  |

| TCLK Specifications                                             | 17  |

| Intermodule Synchronization Using NI-TClk for Identical Modules | 17  |

### **Definitions**

*Warranted* specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.

*Characteristics* describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.

- Typical specifications describe the performance met by a majority of models.

- *Nominal* specifications describe an attribute that is based on design, conformance testing, or supplemental testing.

- Measured specifications describe the measured performance of a representative model.

Specifications are *Typical* unless otherwise noted.

### **Conditions**

Specifications are valid under the following conditions unless otherwise noted.

- Ambient temperature of 23 °C  $\pm$  5 °C

- Installed in chassis with slot cooling capacity ≥58 W

## Digital I/O

| Connector   | Molex <sup>TM</sup> Nano-Pitch I/O <sup>TM</sup> |

|-------------|--------------------------------------------------|

| 5.0 V Power | ±5%, 50 mA maximum, nominal                      |

Table 1. Digital I/O Signal Characteristics

| Signal        | Туре                  | Direction     |

|---------------|-----------------------|---------------|

| MGT Tx± <30>1 | Xilinx UltraScale GTH | Output        |

| MGT Rx± <30>1 | Xilinx UltraScale GTH | Input         |

| DIO <70>      | Single-ended          | Bidirectional |

| 5.0 V         | DC                    | Output        |

| GND           | Ground                | _             |

## Digital I/O Single-Ended Channels

| Number of channels | 8                                 |

|--------------------|-----------------------------------|

| Signal type        | Single-ended                      |

| Voltage families   | 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V |

| Input impedance    | 100 kΩ, nominal                   |

| Output impedance   | 50 Ω, nominal                     |

Multi-gigabit transceiver (MGT) signals are available on devices with KU040 and KU060 FPGAs only.

| Direction control                         | Per channel                      |

|-------------------------------------------|----------------------------------|

| Minimum required direction change latency | 200 ns                           |

| Maximum output toggle rate                | 60 MHz with 100 μA load, nominal |

Table 2. Digital I/O Single-Ended DC Signal Characteristics<sup>2</sup>

| Voltage Family | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>OL</sub><br>(100μA load) | V <sub>OH</sub><br>(100μA load) | Maximum DC Drive<br>Strength |

|----------------|-----------------|-----------------|---------------------------------|---------------------------------|------------------------------|

| 3.3 V          | 0.8 V           | 2.0 V           | 0.2 V                           | 3.0 V                           | 24 mA                        |

| 2.5 V          | 0.7 V           | 1.6 V           | 0.2 V                           | 2.2 V                           | 18 mA                        |

| 1.8 V          | 0.62 V          | 1.29 V          | 0.2 V                           | 1.5 V                           | 16 mA                        |

| 1.5 V          | 0.51 V          | 1.07 V          | 0.2 V                           | 1.2 V                           | 12 mA                        |

| 1.2 V          | 0.42 V          | 0.87 V          | 0.2 V                           | 0.9 V                           | 6 mA                         |

## Digital I/O High-Speed Serial MGT<sup>3</sup>

Note MGTs are available on devices with KU040 and KU060 FPGAs only.

| Data rate                                        | 500 Mbps to 16.375 Gbps, nominal         |

|--------------------------------------------------|------------------------------------------|

| Number of Tx channels                            | 4                                        |

| Number of Rx channels                            | 4                                        |

| I/O AC coupling capacitor                        | 100 nF                                   |

| MGT TX± Channels                                 |                                          |

| Minimum differential output voltage <sup>4</sup> | 170 mV pk-pk into 100 $\Omega$ , nominal |

| I/O coupling                                     | AC-coupled with 100 nF capacitor         |

| MGT RX± Channels                                 |                                          |

| Differential input voltage range                 |                                          |

| ≤ 6.6 Gb/s                                       | 150 mV pk-pk to 2000 mV pk-pk, nominal   |

| > 6.6 Gb/s                                       | 150 mV pk-pk to 1250 mV pk-pk, nominal   |

<sup>&</sup>lt;sup>2</sup> Voltage levels are guaranteed by design through the digital buffer specifications.

<sup>&</sup>lt;sup>3</sup> For detailed FPGA and High-Speed Serial Link specifications, refer to Xilinx documentation.

<sup>4 800</sup> mV pk-pk when transmitter output swing is set to the maximum setting.

## Reconfigurable FPGA

PXIe-5763 modules are available with multiple FPGA options. The following table lists the FPGA specifications for the PXIe-5763 FPGA options.

Table 3. Reconfigurable FPGA Options

|                                      | KU035                                                      | KU040   | KU060   |

|--------------------------------------|------------------------------------------------------------|---------|---------|

| LUTs                                 | 203,128                                                    | 242,200 | 331,680 |

| DSP48 slices<br>(25 × 18 multiplier) | 1,700                                                      | 1,920   | 2,760   |

| Embedded Block RAM                   | 19.0 Mb                                                    | 21.1 Mb | 38.0 Mb |

| Default timebase                     | 80 MHz                                                     |         |         |

| Timebase reference sources           | PXI Express 100 MHz (PXIe_CLK100)                          |         | CLK100) |

| Data transfers                       | DMA, interrupts, programmed I/O multi-gigabit transceivers |         | 1 0     |

| Number of DMA channels               | 60                                                         |         |         |

**Note** The Reconfigurable FPGA Options table depicts the total number of FPGA resources available on the part. The number of resources available to the user is slightly lower, as some FPGA resources are consumed by board-interfacing IP for PCI Express, device configuration, and various board I/O. For more information, contact NI support.

**Note** For FPGA designs using the majority of KU040 or KU060 FPGA resources while running at clock rates over 150 MHz, the module may require more power than is available. If the module attempts to draw more than allowed per its specification, the module protects itself and reverts to a default FPGA personality. Refer to the getting started guide for your module or contact NI support for more information.

### **Onboard DRAM**

Note DRAM is available on devices with KU040 and KU060 FPGAs only.

| Memory size                   | 4 GB (2 banks of 2 GB)      |

|-------------------------------|-----------------------------|

| DRAM clock rate               | 1064 MHz                    |

| Physical bus width            | 32 bit                      |

| LabVIEW FPGA DRAM clock rate  | 267 MHz                     |

| LabVIEW FPGA DRAM bus width   | 256 bit per bank            |

| Maximum theoretical data rate | 17 GB/s (8.5 GB/s per bank) |

## **Analog Input**

**Notice** The maximum input signal levels are valid only when the module is powered on. To avoid permanent damage to the PXIe-5763, do not apply a signal to the device when the module is powered down.

### **General Characteristics**

| Number of channels                | 4, single-ended, simultaneously sampled |

|-----------------------------------|-----------------------------------------|

| Connector type                    | SMA                                     |

| Input impedance                   | 50 Ω                                    |

| Input coupling                    | AC or DC <sup>5</sup>                   |

| Sample Rate                       |                                         |

| Internal Sample Clock             | 500 MHz                                 |

| External Sample Clock             | $500~\mathrm{MHz^6}$                    |

| Analog-to-digital converter (ADC) | ADS54J69, 16-bit resolution             |

|                                   |                                         |

## Typical Specifications

| Full-scale input range (normal oper | rating conditions)                    |

|-------------------------------------|---------------------------------------|

| AC-coupled                          | $2.03~V_{pp}~(10.15~dBm)$ at $10~MHz$ |

| DC-coupled                          | 1.97 V <sub>pp</sub> (9.87 dBm)       |

<sup>&</sup>lt;sup>5</sup> Only one analog input path type is populated.

<sup>&</sup>lt;sup>6</sup> You must provide a 1 GHz clock at the CLK/REF IN front panel connector to enable this rate.

#### Gain accuracy

| AC-coupled                     | ±0.1 dB at 10 MHz          |

|--------------------------------|----------------------------|

| DC-coupled                     | ±1% at DC                  |

| DC Offset                      |                            |

| AC-coupled                     | ±41 μV                     |

| DC-coupled                     | ±225 μV                    |

| Bandwidth (-3 dB) <sup>7</sup> |                            |

| AC-coupled                     | 0.07 MHz to 225 MHz        |

| DC-coupled                     | DC to 225 MHz <sup>9</sup> |

|                                |                            |

Table 4. Single-Tone Spectral Performance

|                           | AC-Coupled      |           | DC-Coupled      |           |

|---------------------------|-----------------|-----------|-----------------|-----------|

|                           | Input Frequency |           | Input Frequency |           |

|                           | 10.1 MHz        | 123.1 MHz | 10.1 MHz        | 123.1 MHz |

| SNR <sup>9</sup> (dBFS)   | 73.7            | 71.8      | 71.7            | 70.6      |

| SINAD <sup>9</sup> (dBFS) | 73.5            | 71.7      | 70.7            | 70.5      |

| SFDR (dBc)                | -85.6           | -87.7     | -77.2           | -86.1     |

| ENOB <sup>10</sup> (bits) | 11.9            | 11.6      | 11.5            | 11.4      |

#### Table 5. Noise Spectral Density

| Module     | nV/rt (Hz) | dBm/Hz | dBFS/Hz |

|------------|------------|--------|---------|

| AC-coupled | 9.5        | -147.4 | -157.5  |

| DC-coupled | 11.8       | -145.6 | -155.4  |

Note Noise spectral density is verified using a 50  $\Omega$  terminator connected to the input.

<sup>&</sup>lt;sup>7</sup> Normalized to 10 MHz.

<sup>&</sup>lt;sup>8</sup> Upper -3 dB bandwidth limited by ADC decimation filter.

<sup>9</sup> Measured with a -1 dBFS signal and corrected to full-scale. 1 kHz resolution bandwidth.

<sup>&</sup>lt;sup>10</sup> Calculated from SINAD and corrected to full scale.

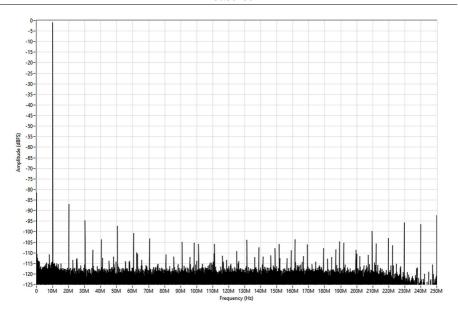

Figure 1. AC-Coupled Single Tone Spectrum (10.1 MHz, -1 dBFS, 1 kHz RBW), Measured

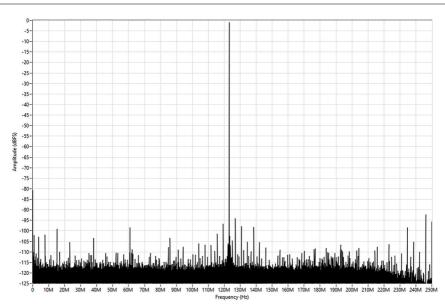

Figure 2. AC-Coupled Single Tone Spectrum (123.1 MHz, -1 dBFS, 1 kHz RBW), Measured

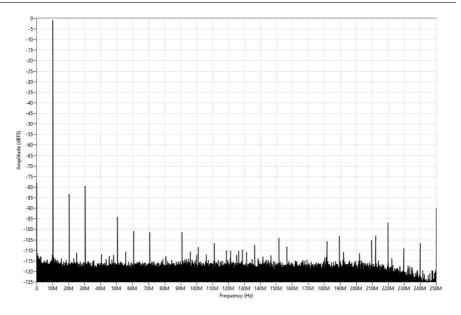

Figure 3. DC-Coupled Single Tone Spectrum (10.1 MHz, -1 dBFS, 1 kHz RBW), Measured

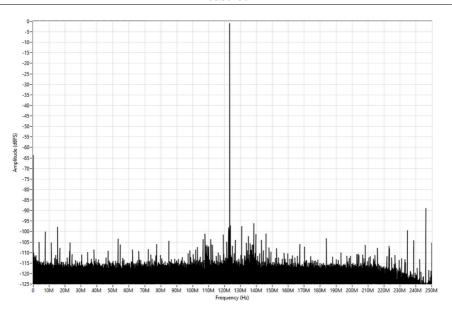

Figure 4. DC-Coupled Single Tone Spectrum (123.1 MHz, -1 dBFS, 1 kHz RBW), Measured

| Channel-to-channel crosstalk AC-coupled, characteristic |                            |  |

|---------------------------------------------------------|----------------------------|--|

| 10 MHz                                                  | -87 dB                     |  |

| 100 MHz                                                 | -89 dB                     |  |

| 225 MHz                                                 | -85 dB                     |  |

| Channel-to-channel crosstalk                            | DC-coupled, characteristic |  |

| 1 MHz                                                   | -94 dB                     |  |

| 100 MHz                                                 | -83 dB                     |  |

| 225 MHz                                                 | -78 dB                     |  |

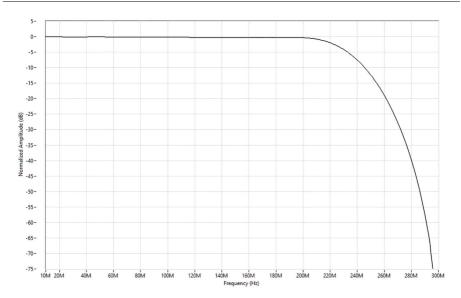

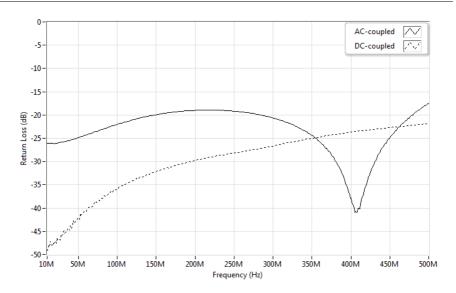

Figure 5. AC-Coupled Frequency Response, Measured

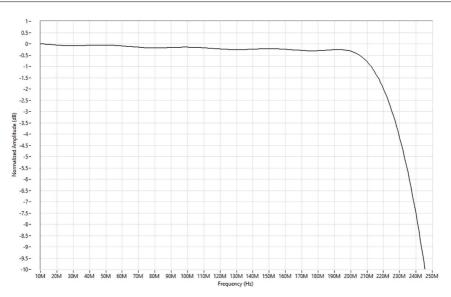

Figure 6. AC-Coupled Frequency Response Zoomed In, Measured

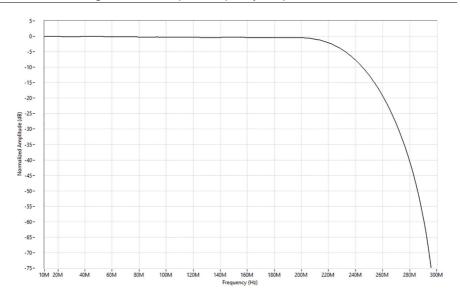

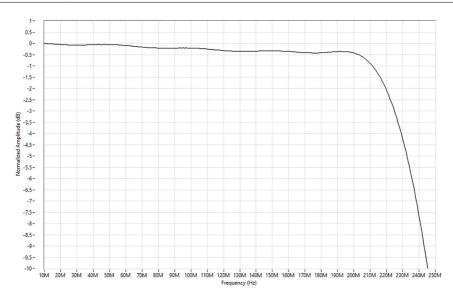

Figure 8. DC-Coupled Frequency Response Zoomed In, Measured

## **CLK/REF IN**

### **General Characteristics**

| Connector type                       | SMA                                                |

|--------------------------------------|----------------------------------------------------|

| Input impedance                      | 50 Ω                                               |

| Input coupling                       | AC                                                 |

| Reference input voltage range        | $0.3~\mathrm{V_{pp}}$ to $4~\mathrm{V_{pp}}$       |

| Sample Clock input voltage range     | $0.3~\mathrm{V_{pp}}$ to $4~\mathrm{V_{pp}}$       |

| Absolute maximum voltage             | $\pm 12 \text{ V DC}, 4 \text{ V}_{pp} \text{ AC}$ |

| Duty cycle                           | 45% to 55%                                         |

| Onboard reference timebase stability | ±0.5 ppm                                           |

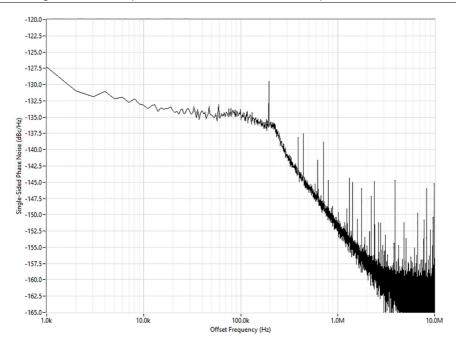

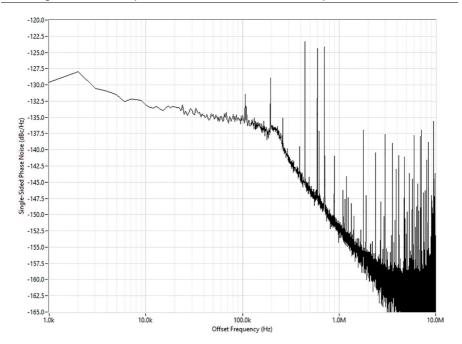

| Sample Clock jitter <sup>11</sup>    |                                                    |

| AC-coupled                           | 135 fs RMS                                         |

| DC-coupled                           | 142 fs RMS                                         |

<sup>11</sup> Integrated from 1 kHz to 10 MHz. Includes the effects of the converter aperture uncertainty and the clock circuitry jitter. Excludes trigger jitter.

Table 6. Clock Configuration Options

| Clock Configuration                       | External<br>Clock Type | External<br>Clock<br>Frequency | Description                                                                                                                                 |

|-------------------------------------------|------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Reference<br>Clock <sup>12</sup> | _                      | _                              | The internal Sample Clock locks to an onboard voltage-controlled temperature compensated crystal oscillator (VCTCXO).                       |

| Internal PXI_CLK10                        | _                      | 10 MHz                         | The internal Sample Clock locks to<br>the PXI 10 MHz Reference Clock,<br>which is provided through the<br>backplane.                        |

| External Reference<br>Clock (CLK/REF IN)  | Reference<br>Clock     | 10 MHz <sup>13</sup>           | The internal Sample Clock locks to<br>an external Reference Clock,<br>which is provided through the<br>CLK/REF IN front panel<br>connector. |

| External Sample<br>Clock (CLK/REF IN)     | Sample Clock           | 1 GHz <sup>14</sup>            | An external Sample Clock can be provided through the CLK/REF IN front panel connector.                                                      |

Default clock configuration.

The PLL Reference Clock must be accurate to ±25 ppm.

The ADC sample rate is 500 MS/s with a 1 GHz clock.

Figure 10. AC-Coupled Phase Noise with 182.6 MHz Input Tone, Measured

Figure 11. DC-Coupled Phase Noise with 182.6 MHz Input Tone, Measured

### **Bus Interface**

PCI Express Gen-3 x8 Form factor

## Maximum Power Requirements

**Note** Power requirements are dependent on the contents of the LabVIEW FPGA VI used in your application.

| +3.3 V              | 3 A  |

|---------------------|------|

| +12 V               | 4 A  |

| Maximum total power | 58 W |

## **Physical**

| Dimensions (not including connectors) | 2.0 cm × 13.0 cm × 21.6 cm<br>(0.8 in. × 5.1 in. × 8.5 in.) |

|---------------------------------------|-------------------------------------------------------------|

| Weight                                | 500 g (17.6 oz)                                             |

### **Environment**

| Maximum altitude | 2,000 m (800 mbar) (at 25 °C ambient temperature) |

|------------------|---------------------------------------------------|

| Pollution Degree | 2                                                 |

Indoor use only.

### **Operating Environment**

| Ambient temperature range | 0 °C to 55 °C <sup>15</sup> |

|---------------------------|-----------------------------|

| Relative humidity range   | 10% to 90%, noncondensing   |

## Storage Environment

| Ambient temperature range | -40 °C to 71 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2. Meets MIL-PRF-28800F Class 4 limits.) |

|---------------------------|-------------------------------------------------------------------------------------------------------------------|

| Relative humidity range   | 5% to 95%, noncondensing (Tested in accordance with IEC 60068-2-56.)                                              |

### Shock and Vibration

| Operating shock | 30 g peak, half-sine, 11 ms pulse (Tested in accordance with IEC 60068-2-27. Meets MIL-PRF-28800F Class 2 limits.) |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

|                 |                                                                                                                    |

<sup>15</sup> The PXIe-5763 requires a chassis with slot cooling capacity ≥58 W. Not all chassis with slot cooling capacity ≥58 W can achieve this ambient temperature range. Refer to the PXI Chassis Manual for specifications to determine the ambient temperature ranges your chassis can achieve.

#### Random vibration

| Operating    | 5 Hz to 500 Hz, 0.3 $g_{rms}$ (Tested in accordance with IEC 60068-2-64.)                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Nonoperating | 5 Hz to 500 Hz, 2.4 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64. Test profile exceeds the requirements of MIL-PRF-28800F, Class 3.) |

## **TCLK Specifications**

You can use the NI TClk synchronization method and the NI-TClk driver to align the Sample Clocks on any number of supported devices, in one or more chassis. For more information about TClk synchronization, refer to the NI-TClk Synchronization Help within the FlexRIO Help. For other configurations, including multichassis systems, contact NI Technical Support at ni.com/support.

### Intermodule Synchronization Using NI-TClk for Identical Modules

Synchronization specifications are valid under the following conditions:

- All modules are installed in one PXI Express chassis.

- The NI-TClk driver is used to align the Sample Clocks of each module.

- All parameters are set to identical values for each module.

- Modules are synchronized without using an external Sample Clock.

Note Although you can use NI-TClk to synchronize non-identical modules, these specifications apply only to synchronizing identical modules.

| Skew <sup>16</sup>            |                  |  |

|-------------------------------|------------------|--|

| AC-coupled                    | 130 ps, measured |  |

| DC-coupled                    | 140 ps, measured |  |

| Skew after manual adjustment  | ≤10 ps, measured |  |

| Sample Clock delay/adjustment | 1.5 ps           |  |

<sup>16</sup> Caused by clock and analog delay differences. No manual adjustment performed. Tested with a PXIe-1085 chassis with a 24 GB backplane with a maximum slot to slot skew of 100 ps. Measured at 23 °C.

Information is subject to change without notice. Refer to the NI Trademarks and Logo Guidelines at ni.com/trademarks for information on NI trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering NI products/technology, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your media, or the National Instruments Patent Notice at ni.com/patents. You can find information about end-user license agreements (EULAs) and third-party legal notices in the readme file for your NI product. Refer to the Export Compliance Information at ni.com/legal/export-compliance for the NI global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data. NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS. U.S. Government Customers: The data contained in this manual was developed at private expense and is subject to the applicable limited rights and restricted data rights as set forth in FAR 52.227-14, DFAR 252.227-7014, and DFAR 252.227-7015. © 2018—2020 National Instruments. All rights reserved.

376459B-01 January 27, 2020