## **MPQ8847A**

6A, 2.7V to 6V, High-Efficiency, Synchronous Step-Down Converter with I<sup>2</sup>C Interface, AEC-Q100 Qualified

#### **DESCRIPTION**

The MPQ8847A is a highly integrated, high-frequency, synchronous step-down converter with an I<sup>2</sup>C control interface. The MPQ8847A can support up to 6A of load current across an input voltage ( $V_{IN}$ ) supply range from 2.7V to 6V, with excellent load and line regulation.

Constant-frequency hysteretic mode provides an extremely fast transient response without loop compensation to achieve high efficiency under light-load conditions.

The output voltage ( $V_{OUT}$ ) can be controlled onthe-fly through a 3.4Mbps I<sup>2</sup>C serial interface. The voltage range can be adjusted from 0.6V to 1.235V in 5mV steps. The  $V_{OUT}$  slew rate, switching frequency ( $f_{SW}$ ), and power-save mode can be configured via the I<sup>2</sup>C interface.

Full protection features include internal soft start, over-current protection (OCP), and thermal shutdown.

The MPQ8847A requires a minimal number of readily available, standard external components, and is available in a compact QFN-14 (2.5mmx3mm) package.

#### **FEATURES**

#### • Flexible with I<sup>2</sup>C Interface:

- I<sup>2</sup>C-Configurable Output Voltage (V<sub>OUT</sub>)

Range from 0.6V to 1.235V in 5mV

Steps

- Adjustable Switching Frequency (f<sub>SW</sub>) from 0.85MHz to 2.2MHz

- I<sup>2</sup>C-Compatible Interface up to 3.4Mbps

- Power-Save Mode Selectable via I<sup>2</sup>C

### Designed for Heavy Loads:

- Up to 6A Load Current

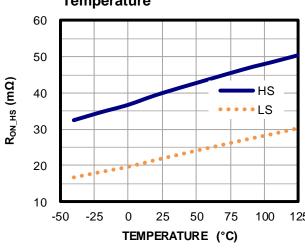

- o Internal 40m $\Omega$  High-Side and 22m $\Omega$  Low-Side Power MOSFETs

#### Additional Features:

- 2.7V to 6V Input Voltage (V<sub>IN</sub>) Range

- o Internal 165µs Soft Start

- Power Good (PG) Indicator

- Current Overload and Thermal Shutdown Protection

- Available in a QFN-14 (2.5mmx3mm)

Package

- Available in AEC-Q100 Grade 1

#### **APPLICATIONS**

- Automotive Infotainment Systems

- Automotive Telematics Systems

- Advanced Driver Assistance Systems (ADASs)

- Automotive Applications

- Processor Core Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

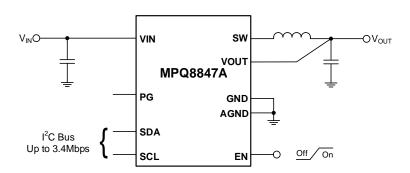

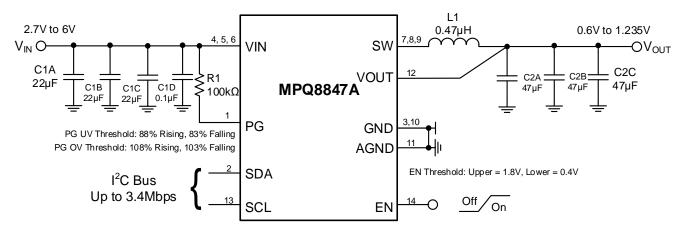

## **TYPICAL APPLICATION**

### **ORDERING INFORMATION**

| Part Number*     | Package            | Top Marking | MSL Rating** |

|------------------|--------------------|-------------|--------------|

| MPQ8847AGQB-AEC1 | QFN-14 (2.5mmx3mm) | See Below   | 1            |

\*For Tape & Reel, add suffix -Z (e.g. MPQ8847AGQB -AEC1-Z).

\*\* Moisture Sensitivity Level Rating

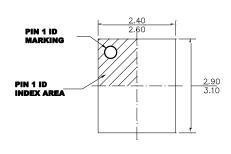

## **TOP MARKING**

BGA

YWW

LLL

BGA: Product code of MPQ8847AGQB -AEC1

Y: Year code WW: Week code LLL: Lot number

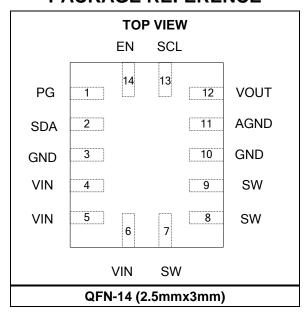

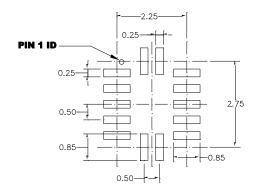

### **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin#    | Name | Description                                                                                                                                                                                                                                                                                                                |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PG   | <b>Power good output.</b> The output of this pin is an open drain that goes low if the output voltage (V <sub>OUT</sub> ) exceeds 108% of nominal voltage or drops below 83% of the nominal voltage. Connect PG to a ≤6V voltage source with a resistor (e.g. $100k\Omega$ ). The PG pin can be floated if it is not used. |

| 2       | SDA  | I <sup>2</sup> C serial data. The SDA pin can be floated if it is not used.                                                                                                                                                                                                                                                |

| 3, 10   | GND  | <b>Power ground.</b> The GND pin should be electrically connected to the system's power ground plane with the shortest and lowest impedance connection possible.                                                                                                                                                           |

| 4, 5, 6 | VIN  | <b>Input supply voltage.</b> In addition to placing a large bulk input capacitor at VIN for a stable power source, connect a bypass capacitor from VIN to GND to reduce noise. The bypass capacitor should be placed as close to the chip as possible.                                                                     |

| 7, 8, 9 | SW   | <b>Switch node.</b> SW is the output from the high-side switch. SW should be connected to one side of the external power inductor.                                                                                                                                                                                         |

| 11      | AGND | Analog ground. AGND is the ground for the internal logic and signal control blocks.                                                                                                                                                                                                                                        |

| 12      | VOUT | <b>Output voltage sense.</b> Connect the VOUT pin directly to the MPQ8847A's output. Note that the device's output voltage cannot be set by using an external resistor divider and connecting VOUT to the tap of divider.                                                                                                  |

| 13      | SCL  | I <sup>2</sup> C serial clock. The SCL pin can be floated if it is not used.                                                                                                                                                                                                                                               |

| 14      | EN   | On and off control. Pull EN below 0.4V to shut the chip down. Pull EN above 1.8V to enable the chip. Floating EN shuts the chip down, since an internal $1M\Omega$ resistor is connected from EN to ground.                                                                                                                |

## **ABSOLUTE MAXIMUM RATINGS (1)** Supply voltage (V<sub>IN</sub>) .....--0.3V to 7V $V_{SW}$ ......-0.3V (-5V for <10ns) to .....+6.5V (+8V for <10ns or +10V for <3ns) All other pins.....-0.3V to +6.5V Continuous power dissipation ( $T_A = 25^{\circ}C$ ) (2) (7) Storage temperature.....-65°C to +150°C Electrostatic Discharge (ESD) Ratings Human body mode (HBM) ...... Class 2 (3) Charged device mode (CDM) ...... Class C2b (4) **Recommended Operating Conditions** Supply voltage (V<sub>IN</sub>) ...... 2.7V to 6V Output voltage (V<sub>OUT</sub>)............... 0.6V to 1.235V Operating junction temp (T<sub>J</sub>)..... .....-40°C to +125°C (5)

| Thermal Resistance  | $oldsymbol{	heta}$ JA | $\boldsymbol{\theta}$ JC |

|---------------------|-----------------------|--------------------------|

| QFN-14 (2.5mmx3mm)  |                       |                          |

| JESD51-7 (6)        | . 60                  | 13 °C/W                  |

| EVQ8847A-QB-00A (7) | . 33                  | 3 °C/W                   |

#### Notes:

- Absolute maximum ratings are rated under room temperature unless otherwise noted.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- Operating junction temperatures above 125°C may be supported; contact MPS for details.

- 6) Measured on JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

- Measured on EVQ8847-QB-00A, 4-layer PCB, 2oz copper thickness, 6.35cmx6.35cm.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 5V$ ,  $T_{J} = -40$ °C to +125°C, typical values refer to  $T_{J} = 25$ °C, unless otherwise noted.

| Parameter                       | Symbol               | Condition                                                                                  | Min   | Тур   | Max   | Units            |

|---------------------------------|----------------------|--------------------------------------------------------------------------------------------|-------|-------|-------|------------------|

| Input voltage range             | V <sub>IN</sub>      |                                                                                            | 2.7   |       | 6     | V                |

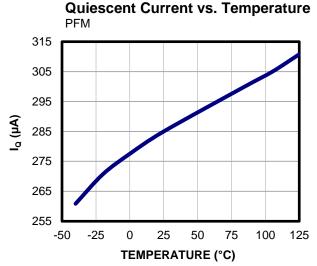

| Quiescent current               | ΙQ                   | EN = 1.8V, no switching, PFM mode                                                          |       | 285   |       | μA               |

| Shutdown current                | Is                   | EN = GND, T <sub>J</sub> = 25°C                                                            |       |       | 1     | μA               |

| Internal reference voltage      | \/                   | T <sub>J</sub> = 25°C                                                                      | 0.585 | 0.600 | 0.615 | V                |

| Internal reference voltage      | V <sub>REF</sub>     | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                       | 0.579 | 0.600 | 0.621 | V                |

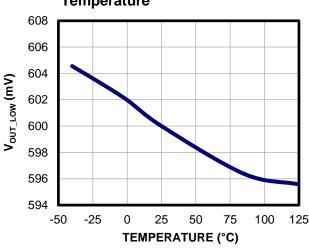

| Lowest output voltage           | $V_{LOW}$            | T <sub>J</sub> = 25°C                                                                      | 0.585 | 0.600 | 0.615 | V                |

| Lowest output voltage           | V LOW                | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                       | 0.579 | 0.600 | 0.621 | V                |

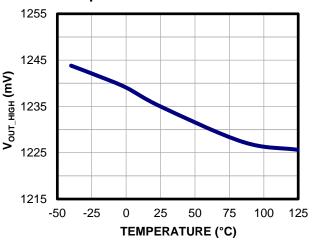

| Highoot output voltage          | VHIGH                | T <sub>J</sub> = 25°C                                                                      | 1.205 | 1.235 | 1.265 | V                |

| Highest output voltage          | VHIGH                | -40°C < T <sub>J</sub> < +125°C                                                            | 1.192 | 1.235 | 1.278 | V                |

| Output voltage step             | VSTEP                |                                                                                            |       | 5     |       | mV               |

| High-side switch on resistance  | R <sub>HS_ON</sub>   |                                                                                            |       | 40    | 80    | mΩ               |

| Low-side switch on resistance   | R <sub>LS_ON</sub>   |                                                                                            |       | 22    | 45    | mΩ               |

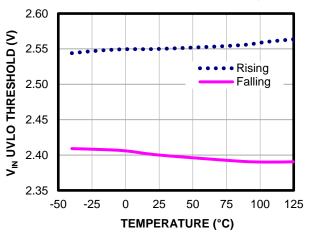

| UVLO rising threshold           | Vuvlor               |                                                                                            |       | 2.55  | 2.7   | V                |

| UVLO hysteretic                 | Vuvlohy              |                                                                                            |       | 150   |       | mV               |

| Switching frequency             | fsw                  |                                                                                            | 0.85  |       | 2.2   | MHz              |

| Frequency variation             |                      |                                                                                            |       |       | 25%   | f <sub>SW</sub>  |

| Minimum on time <sup>(8)</sup>  | t <sub>MINON</sub>   |                                                                                            |       | 60    |       | ns               |

| High-side switch leakage        | I <sub>SW_H</sub>    | V <sub>EN</sub> = 0V, V <sub>IN</sub> = 5V,<br>V <sub>SW</sub> = 0V, T <sub>J</sub> = 25°C |       |       | 1     | μA               |

| Low-side switch leakage         | I <sub>SW_L</sub>    | V <sub>EN</sub> = 0V, V <sub>IN</sub> = 5V,<br>V <sub>SW</sub> = 5V, T <sub>J</sub> = 25°C |       |       | 10    | μA               |

| EN input current                | I <sub>EN</sub>      |                                                                                            |       | 4     |       | μA               |

| EN logic low voltage            | V <sub>ENH</sub>     |                                                                                            |       |       | 0.4   | V                |

| EN logic high voltage           | VENL                 |                                                                                            | 1.8   |       |       | V                |

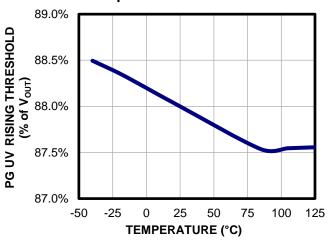

| Power good UV rising threshold  | PG <sub>VTH-НІ</sub> | Good                                                                                       |       | 88%   |       | Vouт             |

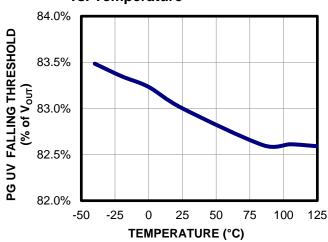

| Power good UV falling threshold | PG <sub>VTH-LO</sub> | Fault                                                                                      |       | 83%   |       | Vouт             |

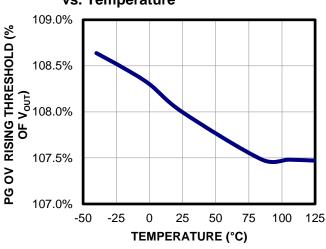

| Power good OV rising threshold  | PG <sub>VTH-НІ</sub> | Fault                                                                                      |       | 108%  |       | Vouт             |

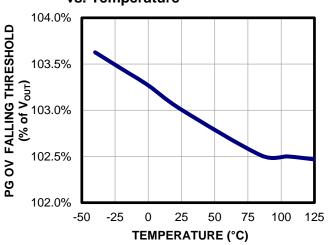

| Power good OV falling threshold | PG <sub>VTH-LO</sub> | Good                                                                                       |       | 103%  |       | V <sub>OUT</sub> |

| Power good pull-down voltage    | $V_{PGL}$            | Isink = 1mA                                                                                |       |       | 0.4   | V                |

| Power good deglitch time        | t <sub>PGD</sub>     |                                                                                            |       | 50    |       | μs               |

| Power good leakage              | I <sub>PGD</sub>     |                                                                                            |       |       | 1     | μΑ               |

|                                 |                      |                                                                                            |       |       |       |                  |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_{J} = -40$ °C to +125°C, typical values refer to  $T_{J} = 25$ °C, unless otherwise noted.

| Parameter                                    | Symbol              | Condition                              | Min | Тур  | Max | Units |

|----------------------------------------------|---------------------|----------------------------------------|-----|------|-----|-------|

| High-side switch peak current limit (source) | I <sub>PEAK</sub>   |                                        | 9   | 12.7 |     | Α     |

| Low-side switch valley current limit (8)     | I <sub>VALLEY</sub> |                                        |     | 7.5  |     | А     |

| Low-side switch current                      |                     | PFM mode                               |     | 0    |     | Α     |

| limit (sink)                                 |                     | PWM mode (8)                           |     | -5   |     | Α     |

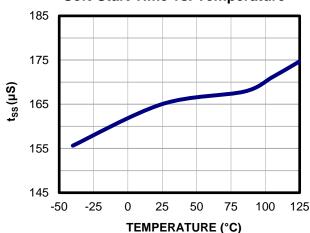

| Soft-start time                              | t <sub>SS-ON</sub>  | V <sub>OUT</sub> rises from 10% to 90% |     | 165  |     | μs    |

| Discharge resistor                           |                     |                                        |     | 500  |     | Ω     |

| Thermal shutdown (8)                         |                     |                                        |     | 170  |     | °C    |

| DAC resolution (8)                           |                     |                                        |     | 7    |     | bits  |

#### Note:

8) Not tested in production. Guaranteed by design and characterization.

## I/O LEVEL CHARACTERISTICS

$V_{IN} = 5V$ ,  $T_{J} = -40$ °C to +125°C, typical values refer to  $T_{J} = 25$ °C, unless otherwise noted.

| <b>D</b>                                                                       |                  |                                                                                             | HS-N                      | /lode                    | LS-N                      | lode                  |       |  |

|--------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------|---------------------------|--------------------------|---------------------------|-----------------------|-------|--|

| Parameter                                                                      | Symbol           | Condition                                                                                   | Min                       | Max                      | Min                       | Max                   | Units |  |

| Low-level input voltage                                                        | VIL              |                                                                                             | -0.5                      | 0.3 x<br>V <sub>CC</sub> | -0.5                      | 0.3 x<br>Vcc          | V     |  |

| High-level input voltage                                                       | V <sub>IH</sub>  |                                                                                             | 0.7 x<br>Vcc              | Vcc + 0.5                | 0.7 x<br>Vcc              | V <sub>CC</sub> + 0.5 | V     |  |

| Hysteresis of Schmitt                                                          | V <sub>HYS</sub> | Vcc > 2V                                                                                    | 0.05 x<br>V <sub>CC</sub> |                          | 0.05 x<br>V <sub>CC</sub> |                       | V     |  |

| trigger inputs                                                                 | VHY5             | Vcc < 2V                                                                                    | 0.1 x<br>Vcc              |                          | 0.1 x<br>Vcc              |                       |       |  |

| Low-level output voltage                                                       |                  | Vcc > 2V                                                                                    | 0                         | 0.4                      | 0                         | 0.4                   |       |  |

| (open drain) at 3mA sink current                                               | Vol              | V <sub>CC</sub> < 2V                                                                        | 0                         | 0.2 x<br>Vcc             | 0                         | 0.2 x<br>Vcc          | V     |  |

| Low-level output current                                                       | l <sub>OL</sub>  |                                                                                             |                           | 3                        |                           | 3                     | mA    |  |

| Transfer gate on resistance for currents between SDA and SCAH, or SCL and SCLH | R <sub>ONL</sub> | $V_{OL}$ level, $I_{OL} = 3mA$                                                              |                           | 50                       |                           | 50                    | Ω     |  |

| Transfer gate on resistance between SDA and SCAH, or SCL and SCLH              | Ronh             | Both signals (SDA and SDAH, or SCL and SCLH) at Vcc level                                   | 50                        |                          | 50                        |                       | kΩ    |  |

| Pull-up current of the SCLH current source                                     | Ics              | SCLH output levels between 0.3 x Vcc and 0.7 x Vcc                                          | 2                         | 6                        | 2                         | 6                     | mA    |  |

| Rising time of the SCLH                                                        | trcl             | Output rising time (current source enabled) with an external pull-up current source of 3mA  |                           |                          |                           |                       |       |  |

| or SCL signal                                                                  |                  | Capacitive load from 10pF to 100pF                                                          | 10                        | 40                       |                           |                       | ns    |  |

|                                                                                |                  | Capacitive load of 400pF                                                                    | 20                        | 80                       |                           |                       | ns    |  |

| Falling time of the SCLH                                                       | t <sub>FCL</sub> | Output falling time (current source enabled) with an external pull-up current source of 3mA |                           |                          |                           |                       |       |  |

| or SCL signal                                                                  | 02               | Capacitive load from 10pF to 100pF                                                          | 10                        | 40                       |                           |                       | ns    |  |

|                                                                                |                  | Capacitive load of 400pF                                                                    | 20                        | 80                       | 20                        | 250                   | ns    |  |

| Rising time of the SDAH signal                                                 | t <sub>RDA</sub> | Capacitive load from 10pF to 100pF                                                          | 10                        | 80                       |                           |                       | ns    |  |

|                                                                                |                  | Capacitive load of 400pF                                                                    | 20                        | 160                      | 20                        | 250                   | ns    |  |

| Falling time of the SDAH signal                                                | <b>t</b> FDA     | Capacitive load from 10pF to 100pF                                                          | 10                        | 80                       |                           |                       | ns    |  |

| oignai                                                                         |                  | Capacitive load of 400pF                                                                    | 20                        | 160                      | 20                        | 250                   | ns    |  |

## I<sup>2</sup>C PORT SIGNAL CHARACTERISTICS

VIN = 5V,  $T_J$ = -40°C to +125°C. Typical values refer to  $T_J$ = +25°C, unless otherwise noted.

| Danamatan                                                                                | Council of          | Com distant                                              | <b>C</b> <sub>B</sub> = ' | 100pF                    | C <sub>B</sub> = 400p     | 11!4       |          |

|------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------|---------------------------|--------------------------|---------------------------|------------|----------|

| Parameter                                                                                | Symbol              | Condition                                                | Min                       | Max                      | Min                       | Max        | Units    |

| Pulse width of spikes that must be suppressed by the input filter                        | tsp                 |                                                          | 0                         | 10                       | 0                         | 50         | ns       |

| Input current for each I/O pin                                                           | l <sub>l</sub>      | Input voltage between 0.1 x Vcc and 0.9 x Vcc            |                           | 10                       | -10                       | +10        | μA       |

| Capacitance for each I/O pin                                                             | Cī                  |                                                          |                           | 10                       | -                         | 10         | pF       |

| SCLH and SCL clock frequency                                                             | fschl               |                                                          | 0                         | 3.4                      | 0                         | 0.4        | MHz      |

| Set-up time for a repeated start condition                                               | <b>t</b> su_sta     |                                                          | 160                       |                          | 600                       |            | ns       |

| Hold time for a repeated start condition                                                 | <b>t</b> HD_STA     |                                                          | 160                       |                          | 600                       |            | ns       |

| Low period of the SCL clock                                                              | tLOW                |                                                          | 160                       |                          | 1300                      |            | ns       |

| High period of the SCL clock                                                             | tніgн               |                                                          | 60                        |                          | 600                       |            | ns       |

| Data set-up time                                                                         | t <sub>SU_DAT</sub> |                                                          | 10                        |                          | 100                       |            | ns       |

| Data hold time                                                                           | thd_dat             |                                                          | 0                         | 70                       | 0                         |            | ns       |

| Rising time of SCLH signal                                                               | t <sub>RCL</sub>    |                                                          | 10                        | 40                       | 20 x 0.1 x C <sub>B</sub> | 300        | ns       |

| Rising time of SCLH signal after a repeated start condition and after an acknowledge bit | t <sub>FCL1</sub>   |                                                          | 10                        | 80                       | 20 x 0.1 x C <sub>B</sub> | 300        | ns       |

| Falling time of SCLH signal                                                              | t <sub>FCL</sub>    |                                                          | 10                        | 40                       | 20 x 0.1 x C <sub>B</sub> | 300        | ns       |

| Rising time of SDAH signal                                                               | t <sub>RDA</sub>    |                                                          | 10                        | 80                       | 20 x 0.1 x Св             | 300        | ns       |

| Falling time of SDAH signal                                                              | t <sub>FDA</sub>    |                                                          | 10                        | 80                       | 20 x 0.1 x C <sub>B</sub> | 300        | ns       |

| Set-up time for a stop condition                                                         | ts∪_s⊤o             |                                                          | 160                       |                          | 600                       |            | ns       |

| Bus free time between a stop and start condition                                         | t <sub>BUF</sub>    |                                                          | 160                       |                          | 1300                      |            | ns       |

| Data valid time                                                                          | tvd_dat             |                                                          |                           | 16                       |                           | 90         | ns       |

| Data valid acknowledge time                                                              | t <sub>VD_ACK</sub> |                                                          |                           | 160                      |                           | 900        | ns       |

| Capacitive load for each bus line                                                        | Св                  | SDAH and SCLH line<br>SDAH+SDA line and<br>SCLH+SCL line |                           | 100<br>400               |                           | 400<br>400 | pF<br>pF |

| Noise margin at the low level (9)                                                        | V <sub>NL</sub>     | For each connected device                                |                           | 0.1 x<br>Vcc             | 0.1 x Vcc                 |            | V        |

| Noise margin at the high level (9)                                                       | $V_{NH}$            | For each connected device                                |                           | 0.2 x<br>V <sub>CC</sub> | 0.2 x V <sub>CC</sub>     |            | V        |

#### Note:

9)  $V_{CC}$  is the I<sup>2</sup>C bus voltage, which is between 1.5V and 3.3V.

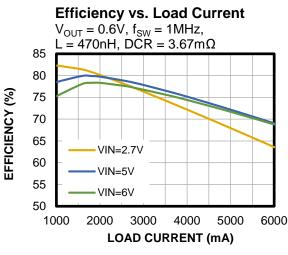

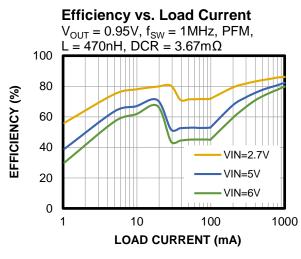

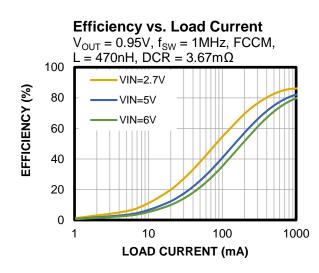

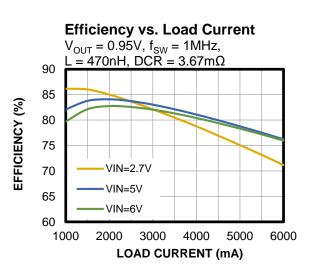

### TYPICAL CHARACTERISTICS

VIN = 5V,  $T_J = -40$ °C to +125°C, unless otherwise noted.

**VIN UVLO Threshold vs. Temperature**

Lowest Output Voltage vs. Temperature

Highest Output Voltage vs. Temperature

High-Side Switch On Resistance vs. Temperature

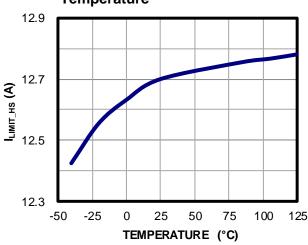

High-Side Current Limit vs. Temperature

## TYPICAL CHARACTERISTICS (continued)

$V_{IN} = 5V$ ,  $T_J = -40$ °C to +125°C, unless otherwise noted.

# PG Under-Voltage Rising Threshold vs. Temperature

# PG Under-Voltage Falling Threshold vs. Temperature

# PG Over-Voltage Rising Threshold vs. Temperature

PG Over-Voltage Falling Threshold vs. Temperature

#### Soft-Start Time vs. Temperature

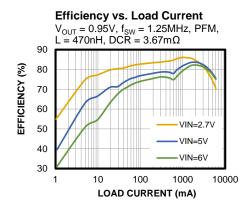

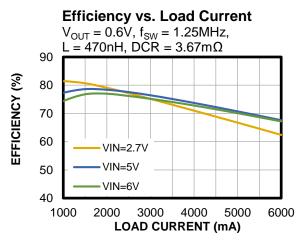

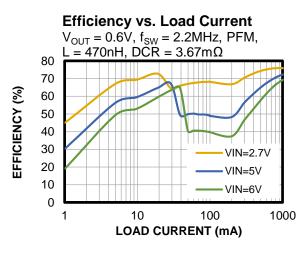

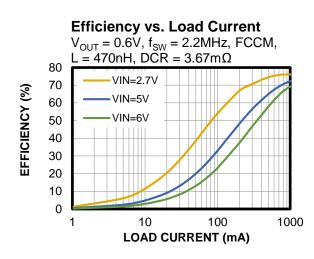

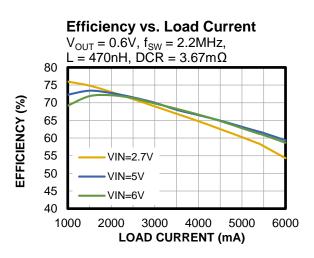

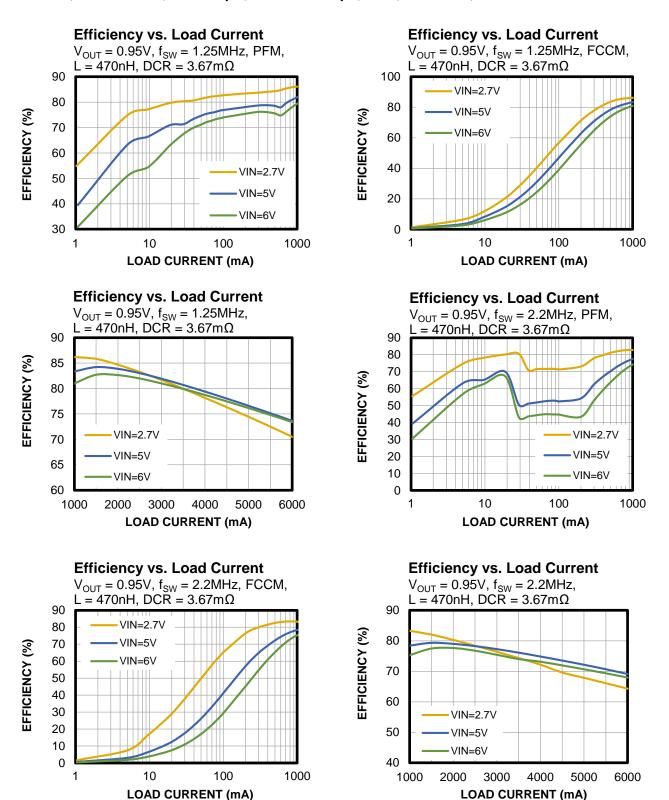

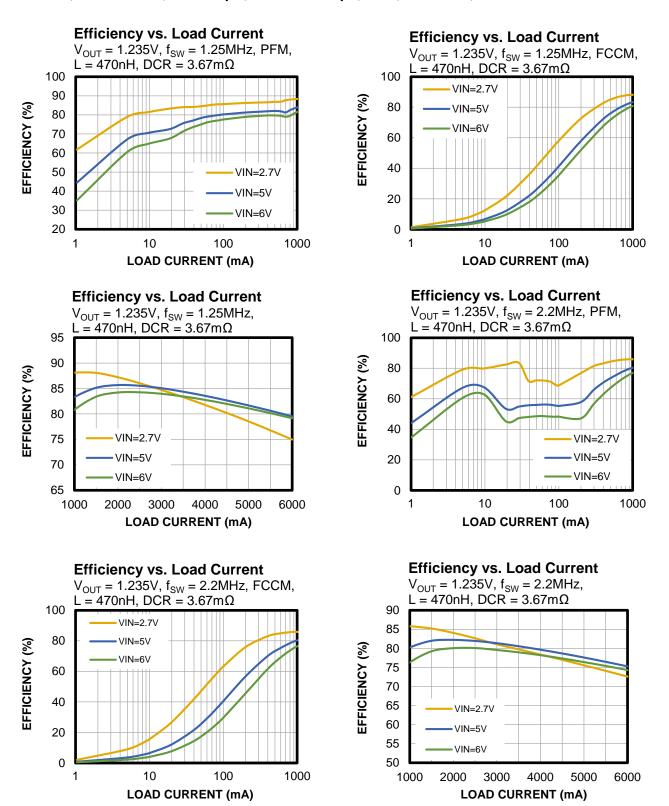

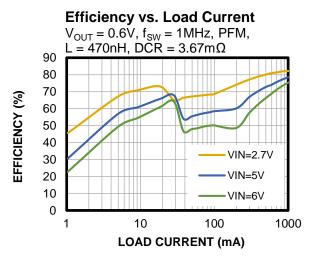

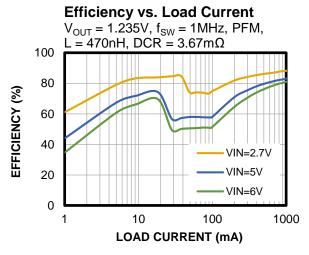

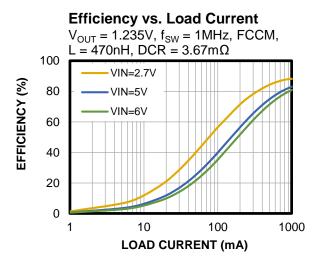

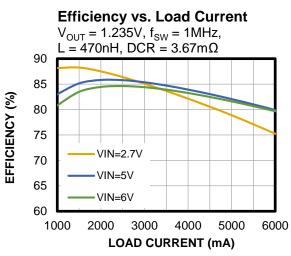

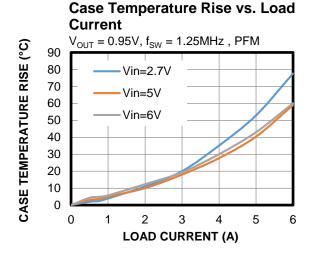

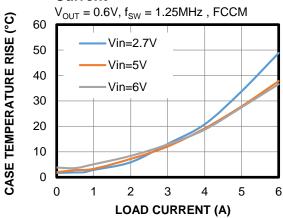

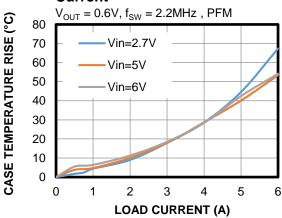

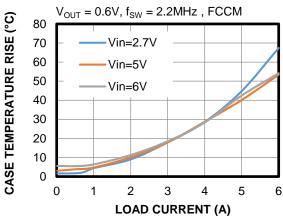

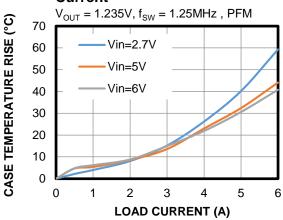

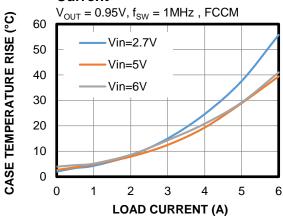

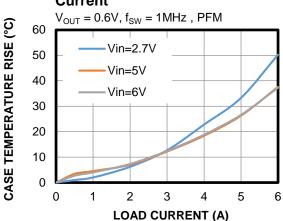

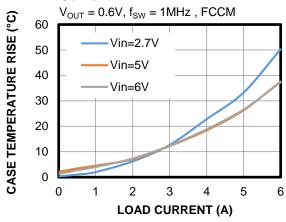

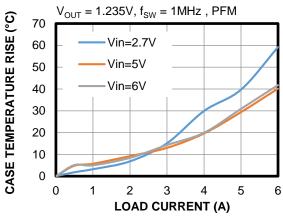

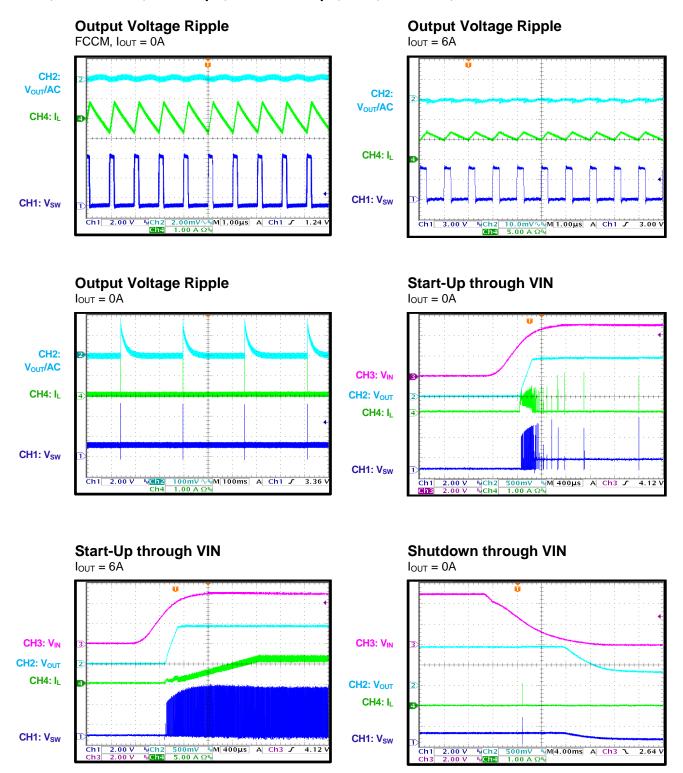

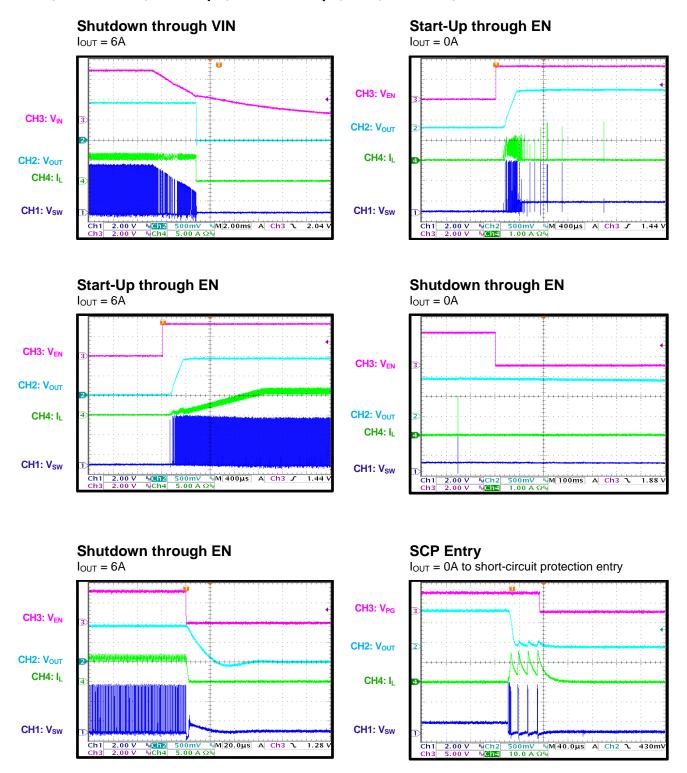

### TYPICAL PERFORMANCE CHARACTERISTICS

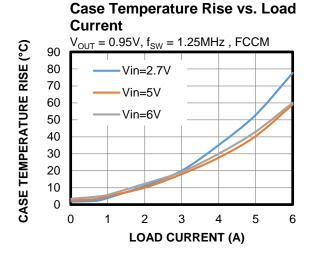

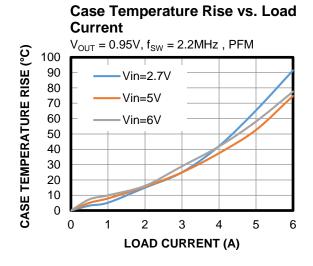

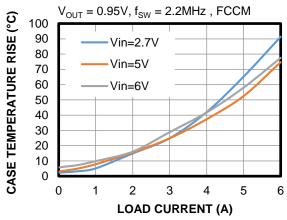

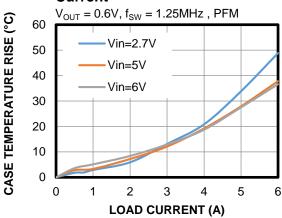

$V_{IN} = 5V$ ,  $V_{OUT} = 0.95V$ ,  $L = 0.47\mu H$ ,  $C_{OUT} = 3 \times 47\mu F$ , PFM,  $T_A = 25^{\circ}C$ , unless otherwise noted.

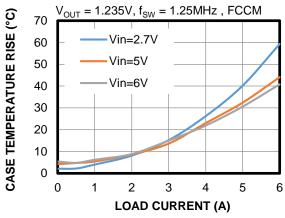

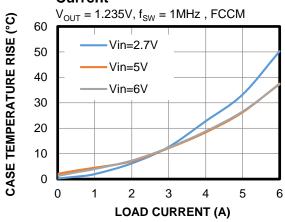

## Case Temperature Rise vs. Load Current

# Case Temperature Rise vs. Load Current

## Case Temperature Rise vs. Load Current

## Case Temperature Rise vs. Load Current

## Case Temperature Rise vs. Load Current

## Case Temperature Rise vs. Load Current

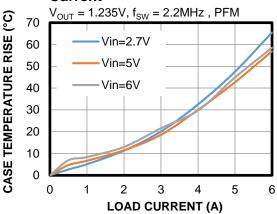

$V_{IN} = 5V$ ,  $V_{OUT} = 0.95V$ ,  $L = 0.47\mu H$ ,  $C_{OUT} = 3 \times 47\mu F$ , PFM,  $T_A = 25^{\circ}C$ , unless otherwise noted.

## Case Temperature Rise vs. Load Current

## **Case Temperature Rise vs. Load Current**

## Case Temperature Rise vs. Load Current

## Case Temperature Rise vs. Load Current

# Case Temperature Rise vs. Load Current

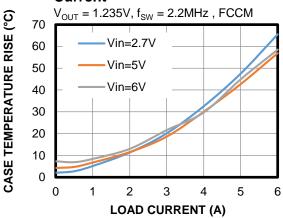

## Case Temperature Rise vs. Load Current

$V_{IN} = 5V$ ,  $V_{OUT} = 0.95V$ ,  $L = 0.47\mu H$ ,  $C_{OUT} = 3 \times 47\mu F$ , PFM,  $T_A = 25^{\circ}C$ , unless otherwise noted.

# Case Temperature Rise vs. Load Current

## Case Temperature Rise vs. Load Current

# Case Temperature Rise vs. Load Current

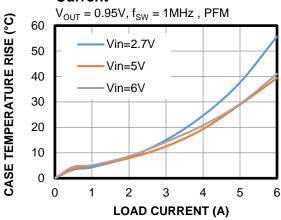

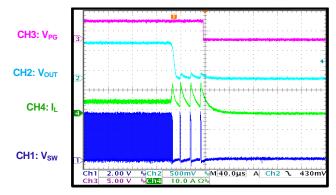

$V_{\text{IN}} = 5V,\, V_{\text{OUT}} = 0.95V,\, L = 0.47\mu\text{H},\, C_{\text{OUT}} = 3~x~47\mu\text{F},\, \text{PFM},\, T_{\text{A}} = 25^{\circ}\text{C},\, \text{unless otherwise noted}.$

## **SCP Entry**

I<sub>OUT</sub> = 6A to short-circuit protection entry

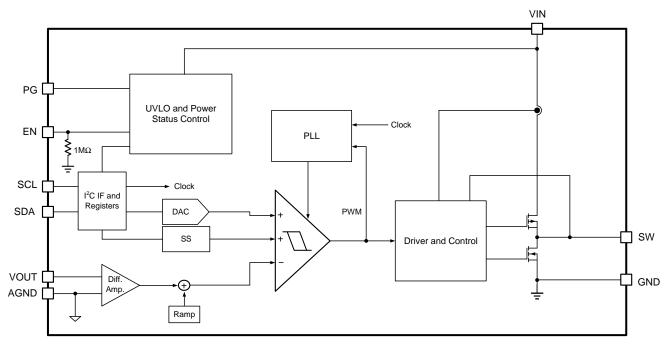

## **FUNCTIONAL BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

### **OPERATION**

The MPQ8847A is a low-voltage, 6A, synchronous step-down converter with an I<sup>2</sup>C interface. The MPQ8847A applies MPS's patented constant-frequency hysteretic control to utilize fast transient response of the hysteretic control and keep the switching frequency (f<sub>SW</sub>) constant. No compensation is required, which simplifies the design procedure.

The MPQ8847A integrates an I<sup>2</sup>C-compatible interface that allows transfers up to 3.4Mbps. This communication interface can be used for dynamic voltage scaling with voltage steps down to 5mV, and an output voltage (V<sub>OUT</sub>) ranging between 0.6V and 1.235V. The voltage transition slew rate can also be configured.

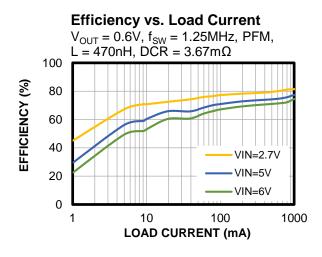

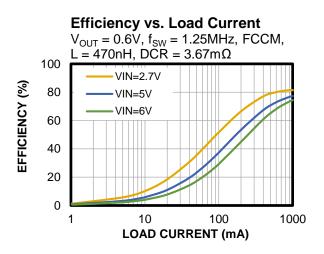

### **Light-Load Operation**

Under light-load conditions, the MPQ8847A has selectable forced continuous conduction mode (FCCM) and automatic pulse-frequency modulation (PFM) mode via the I<sup>2</sup>C. In FCCM, MPQ8847A switching operates with a fixed frequency, regardless of the output load current. In PFM, the MPQ8847A uses a proprietary control scheme to save power and improve efficiency. The MPQ8847A turns off the low-side MOSFET (LS-FET) when the inductor current (I<sub>L</sub>) begins reversing. The MPQ8847A then works in discontinuous conduction mode (DCM).

#### Enable (EN)

When the input voltage ( $V_{\text{IN}}$ ) exceeds the undervoltage lockout (UVLO) threshold (typically 2.55V), the MPQ8847A can be enabled by pulling EN above 1.8V. Pull EN below 0.4V to disable the MPQ8847A. The IC can also be disabled by floating EN. There is an internal 1M $\Omega$  resistor connected from EN to ground.

#### Soft Start (SS)

The MPQ8847A has built-in soft start (SS) that ramps up  $V_{\text{OUT}}$  at a controlled slew rate to prevent inrush current and  $V_{\text{OUT}}$  overshoot at start-up. The soft-start time ( $t_{\text{SS}}$ ) is about 165 $\mu$ s.

#### **Power Good (PG) Indictor**

The MPQ8847A has an open-drain output for power good (PG) indication. Connect this pin to VIN or another voltage source through a resistor (e.g.  $100k\Omega$ ). When  $V_{OUT}$  is within 88% to 108%

of the regulation voltage, PG is pulled high by the external resistor.

#### **Current Limit**

Generally, the MPQ8847A has a 12.7A current limit for the high-side MOSFET (HS-FET). When the HS-FET reaches the current limit, the MPQ8847A extends the minimum off time until the current drops to 7.5A. Then the HS-FET turns on for the next switching cycle. This prevents  $I_{\rm L}$  from becoming exceedingly high and damaging the components.

If the peak current limit is continuously reached several times (typically 3 to 5 times), the MPQ8847A shuts down. A new start-up cycle is required to turn on the MPQ8847A again.

#### **Thermal Protection**

The MPQ8847A employs thermal shutdown by monitoring the IC's internal junction temperature. The MPQ8847A shuts down if the junction temperature exceeds the thermal shutdown threshold (typically 170°C). After thermal shutdown, a new start-up cycle is required to turn on the MPQ8847A again.

#### Start-Up and Shutdown

If both  $V_{\text{IN}}$  and EN exceed their appropriate thresholds, the chip starts. The reference block starts first, generating a stable reference voltage and currents, then the internal regulator is enabled. The regulator provides a stable supply for the remaining circuitries. When the internal supply rail is up, the internal circuits begin working. When the soft-start block is enabled,  $V_{\text{OUT}}$  starts to ramp up slowly and smoothly to its set target within 165µs.

The following events shut down the chip: EN going low,  $V_{\text{IN}}$  falling below its UVLO threshold, thermal shutdown, and writing the I<sup>2</sup>C register REG01, bit D[7] to 0. In the shutdown procedure, the signaling path is blocked first to avoid any fault triggering.

### I<sup>2</sup>C INTERFACE

The MPQ8847A can communicate with the core and the I<sup>2</sup>C for smart design. MPS provides a GUI and evaluation kit to configure the MPQ8847A during development. To make configurations in application, contact an MPS FAE.

### I<sup>2</sup>C Address

The MPQ8847A has an internal I<sup>2</sup>C slave address, which is 0x60 (see Table 1). Contact an MPS FAE if a different address is required.

When the master sends the address as an 8-bit value, the 7-bit address should be followed by a 0 to indicate a write, or a 1 to indicate a read. For example, 0xC0 is a write operation, while 0xC1 is a read operation.

Table 1: I<sup>2</sup>C Slave Address

| Hex              | Α7 | A6 | A5 | A4 | А3  | A2 | A1 | A0  |

|------------------|----|----|----|----|-----|----|----|-----|

| W 0xC0<br>R 0xC1 | 1  | 1  | 0  | 0  | 0   | 0  | 0  | R/W |

| Address          |    |    |    | 0: | x60 |    |    |     |

#### I<sup>2</sup>C Enable

The MPQ8847A's EN pin can force the converter to start up or shut down. The EN command (REG01 VSEL, bit D[7]) in the  $I^2$ C can also control the converter. If D[7] = 0, the converter is off. If D[7] = 1, the converter is on. Both the external EN and internal  $I^2$ C EN can control the converter. The converter works only when both EN signals are high.

### **Output Voltage Selection**

The output voltage ( $V_{\text{OUT}}$ ) can be configured via the I<sup>2</sup>C.  $V_{\text{OUT}}$  cannot be changed with a traditional resistor divider because the internal circuit of the VOUT pin effects the voltage feedback loop.

The default  $V_{\text{OUT}}$  is 0.95V, but this value can be set between 0.6V and 1.235V, with 5mV steps, via the  $I^2$ C. To change  $V_{\text{OUT}}$ , set the GO bit (REG03 SYSCNTLREG2, bit [D5]) to 1. This allows  $V_{\text{OUT}}$  to be set to a value besides the default. Then set the OUTPUT\_REFENCE bits (REG01 VSEL, bits D[6:0]). Table 3 on page 28 shows the possible values for  $V_{\text{OUT}}$ .

#### **Switching Frequency**

The default switching frequency (f<sub>SW</sub>) is 1.25MHz, but this value can be changed based on the

application. By setting the SWITCHING\_FREQUENCY bits (REG02 SYSCNTLREG1, bits D[7:5]),  $f_{\text{SW}}$  can be configured to be 0.85MHz, 1.11MHz, 1.25MHz, 1.67MHz, 2MH,z or 2.2MHz.

#### **Power Good (PG) Configuration**

The MPQ8847A can be set to use the PG\_LOHI function. This function can be set by the PG\_LOHI bit (REG02 SYSCNTLREG1, bit D[2]). The default value is 1, where PG senses both a positive and negative excursion of  $V_{\text{OUT}}$  from the reference. If this bit is set to 0, PG only senses a negative voltage excursion of  $V_{\text{OUT}}$  from the reference.

#### Input Over-Voltage Protection (OVP)

The MPQ8847A has an option to enable  $V_{\text{IN}}$  over-voltage protection (OVP). This function can be set by the VIN\_OVP bit (REG02 SYSCNTLREG1, bit D[1]). The default value is 0, which enables  $V_{\text{IN}}$  OVP. When  $V_{\text{IN}}$  exceeds 6.3V, the converter is disabled. After  $V_{\text{IN}}$  falls to 6.2V, the converter restarts. If VIN\_OVP is set to 1,  $V_{\text{IN}}$  OVP is disabled. The converter continues operating, even if  $V_{\text{IN}}$  exceeds its safe range.

#### Forced Continuous Conduction Mode (FCCM)

The MPQ8847A has automatic pulse-frequency modulation (PFM) mode and forced continuous conduction mode (FCCM). This function can be written in the MODE bit (REG02 SYSCNTLREG1, bit D[0]). The default value is 0, where automatic PFM mode is selected. FCCM is recommended for applications with a small output voltage ripple and a full load range. Set this bit to 1 to disable PFM mode.

#### **Output Voltage Discharge**

The MPQ8847A has a  $V_{\text{OUT}}$  discharge function. Writing the OUT-DIS bit (REG03 SYSCNTLREG2, bit D[4]) can change the output discharge mode. The default value is 0, which means  $V_{\text{OUT}}$  is discharged by its load when EN is low. Set this bit to 1 to enable  $V_{\text{OUT}}$  to be discharged by the internal pull-down resistance.

#### **Output Voltage Transition Slew Rate**

When  $V_{\text{OUT}}$  switches from low to high or from high to low, the, there may be different transition slew rates. There are two possible values to select through the SLEW RATE bits

(REG02SYSCNTLREG1, bits D[4:3]). The slew rate should be set based on the application. The internal reference follows the set slew rate, but the  $V_{\text{OUT}}$  slew rate does not always follow the internal reference. Considering the output capacitor and inductor, the actual  $V_{\text{OUT}}$  slew rate should be a little slower.

#### **Fault Indicator and Diagnostics**

The MPQ8847A provides diagnostics for different fault conditions. For example, the PG pin is pulled high at normal operation, and any fault or warning pulls PG low to indicate a fault status (see Table 2).

The MPQ8847A also has dedicated register bits that serve as fault flags and device status indicators for system diagnostics.

**Table 2: Operation Status**

| Condition                                    | PG  | Regulation | Latch-Off | Status Bit |

|----------------------------------------------|-----|------------|-----------|------------|

| V <sub>IN</sub> over-voltage                 | Low | Off        | No        | OVP        |

| V <sub>IN</sub> under-voltage                | Low | Off        | -         | UVLO       |

| Thermal shutdown                             | Low | Off        | Yes       | -          |

| Short circuit protection                     | Low | Off        | Yes       | ILIM       |

| Output under-voltage                         | Low | Off        | Yes       | VOUV       |

| Output over-voltage (>108% of target output) | Low | On         | No        | VOOV       |

## **REGISTERS MAP AND DESCRIPTION**

### **REGISTER MAP**

| Add     | Name        | R/W | D[7]   | D[6]                                             | D[5] | D[4]             | D[3] | D[2]          | D[1]     | D[0]        |

|---------|-------------|-----|--------|--------------------------------------------------|------|------------------|------|---------------|----------|-------------|

| 00      | STATUS      | R   | ILIM   | UVLO                                             | OVP  | VOOV             | VOUV | PGOOD         | RESERVED | EN_<br>STAT |

| 01      | VSEL        | R/W | EN     | EN OUTPUT_REFERENCE                              |      |                  |      |               |          |             |

| 02      | SYSCNTLREG1 | R/W | SWITCH | HING_FREQUENCY TRANSIENT_ RESPONSE PGLOHI VINOVP |      |                  |      | MODE          |          |             |

| 03 (10) | SYSCNTLREG2 | R/W | RESE   | ERVED                                            | GO   | OUT-DIS RESERVED |      | SLEW_<br>RATE | RESERVED | RESERVED    |

| 04      | ID1         | R   |        | VENDOR_ID DIE_ID                                 |      |                  |      |               |          |             |

| 05      | ID2         | R   |        | RESE                                             | RVED |                  |      | DIE           | _REV     |             |

#### Note:

#### **DEFAULT REGISTER VALUES**

| Add | Name        | R/W | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|-----|-------------|-----|------|------|------|------|------|------|------|------|

| 00  | STATUS      | R   | NA   |

| 01  | VSEL        | R/W | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0    |

| 02  | SYSCNTLREG1 | R/W | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0    |

| 03  | SYSCNTLREG2 | R/W | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

| 04  | ID1         | R   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

| 05  | ID2         | R   | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    |

#### **REGISTER DESCRIPTION**

#### **REG00: Status**

| Bits | Bit Name | Description                                                                                                 |

|------|----------|-------------------------------------------------------------------------------------------------------------|

| D[7] | ILIM     | When this bit is high, the IC has reached its current limit.                                                |

| D[6] | UVLO     | When this bit is high, V <sub>IN</sub> is below the under-voltage lockout (UVLO) threshold.                 |

| D[5] | OVP      | When this bit is high, V <sub>IN</sub> exceeds the over-voltage protection (OVP) threshold.                 |

| D[4] | VOOV     | When this bit is high, Vout exceeds 108% of the regulation voltage.                                         |

| D[3] | VOUV     | When this bit is high, V <sub>OUT</sub> is below 88% of the regulation voltage.                             |

| D[2] | PGOOD    | When this bit is high, V <sub>OUT</sub> is in regulation; otherwise, V <sub>OUT</sub> is out of regulation. |

| D[1] | RESERVED | Reserved.                                                                                                   |

| D[0] | EN_STAT  | When this bit is high, the Smart_MPS is enabled; when the bit is low, the Smart_MPS is disabled.            |

#### **REG01: VSEL**

| Bits   | Bit Name             | Description                                                                                             |

|--------|----------------------|---------------------------------------------------------------------------------------------------------|

| D[7]   | EN                   | I <sup>2</sup> C-controlled enable.                                                                     |

|        |                      | 0: The converter is off 1: The EN bit takes control, and the part turns on when the EN pin is also high |

| D[6:0] | OUTPUT_<br>REFERENCE | Sets the output voltage between 0.6V and 1.235V (see Table 2 on page 28).                               |

<sup>10)</sup> The burst write cannot be on REG03.

**Table 3: Output Voltage Chart**

| D[6:0]   | V <sub>OUT</sub> | D[6:0]   | $\mathbf{V}_{OUT}$ | D[6:0]   | V <sub>out</sub> | D[6:0]   | V <sub>OUT</sub> |

|----------|------------------|----------|--------------------|----------|------------------|----------|------------------|

| 000 0000 | 0.600            | 010 0000 | 0.760              | 100 0000 | 0.920            | 110 0000 | 1.080            |

| 000 0001 | 0.605            | 010 0001 | 0.765              | 100 0001 | 0.925            | 110 0001 | 1.085            |

| 000 0010 | 0.610            | 010 0010 | 0.770              | 100 0010 | 0.930            | 110 0010 | 1.090            |

| 000 0011 | 0.615            | 010 0011 | 0.775              | 100 0011 | 0.935            | 110 0011 | 1.095            |

| 000 0100 | 0.620            | 010 0100 | 0.780              | 100 0100 | 0.940            | 110 0100 | 1.100            |

| 000 0101 | 0.625            | 010 0101 | 0.785              | 100 0101 | 0.945            | 110 0101 | 1.105            |

| 000 0110 | 0.630            | 010 0110 | 0.790              | 100 0110 | 0.950            | 110 0110 | 1.110            |

| 000 0111 | 0.635            | 010 0111 | 0.795              | 100 0111 | 0.955            | 110 0111 | 1.115            |

| 000 1000 | 0.640            | 010 1000 | 0.800              | 100 1000 | 0.960            | 110 1000 | 1.120            |

| 000 1001 | 0.645            | 010 1001 | 0.805              | 100 1001 | 0.965            | 110 1001 | 1.125            |

| 000 1010 | 0.650            | 010 1010 | 0.810              | 100 1010 | 0.970            | 110 1010 | 1.130            |

| 000 1011 | 0.655            | 010 1011 | 0.815              | 100 1011 | 0.975            | 110 1011 | 1.135            |

| 000 1100 | 0.660            | 010 1100 | 0.820              | 100 1100 | 0.980            | 110 1100 | 1.140            |

| 000 1101 | 0.665            | 010 1101 | 0.825              | 100 1101 | 0.985            | 110 1101 | 1.145            |

| 000 1110 | 0.670            | 010 1110 | 0.830              | 100 1110 | 0.990            | 110 1110 | 1.150            |

| 000 1111 | 0.675            | 010 1111 | 0.835              | 100 1111 | 0.995            | 110 1111 | 1.155            |

| 001 0000 | 0.680            | 011 0000 | 0.840              | 101 0000 | 1.000            | 111 0000 | 1.160            |

| 001 0001 | 0.685            | 011 0001 | 0.845              | 101 0001 | 1.005            | 111 0001 | 1.165            |

| 001 0010 | 0.690            | 011 0010 | 0.850              | 101 0010 | 1.010            | 111 0010 | 1.170            |

| 001 0011 | 0.695            | 011 0011 | 0.855              | 101 0011 | 1.015            | 111 0011 | 1.175            |

| 001 0100 | 0.700            | 011 0100 | 0.860              | 101 0100 | 1.020            | 111 0100 | 1.180            |

| 001 0101 | 0.705            | 011 0101 | 0.865              | 101 0101 | 1.025            | 111 0101 | 1.185            |

| 001 0110 | 0.710            | 011 0110 | 0.870              | 101 0110 | 1.030            | 111 0110 | 1.190            |

| 001 0111 | 0.715            | 011 0111 | 0.875              | 101 0111 | 1.035            | 111 0111 | 1.195            |

| 001 1000 | 0.720            | 011 1000 | 0.880              | 101 1000 | 1.040            | 111 1000 | 1.200            |

| 001 1001 | 0.725            | 011 1001 | 0.885              | 101 1001 | 1.045            | 111 1001 | 1.205            |

| 001 1010 | 0.730            | 011 1010 | 0.890              | 101 1010 | 1.050            | 111 1010 | 1.210            |

| 001 1011 | 0.735            | 011 1011 | 0.895              | 101 1011 | 1.055            | 111 1011 | 1.215            |

| 001 1100 | 0.740            | 011 1100 | 0.900              | 101 1100 | 1.060            | 111 1100 | 1.220            |

| 001 1101 | 0.745            | 011 1101 | 0.905              | 101 1101 | 1.065            | 111 1101 | 1.225            |

| 001 1110 | 0.750            | 011 1110 | 0.910              | 101 1110 | 1.070            | 111 1110 | 1.230            |

| 001 1111 | 0.755            | 011 1111 | 0.915              | 101 1111 | 1.075            | 111 1111 | 1.235            |

#### **REG02: SYSCNTLREG1**

| Bits   | Bit Name                | Description                                                                                                                                                                           |

|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                         | Sets the switching frequency (fsw).                                                                                                                                                   |

| D[7:5] | SWITCHING_<br>FREQUENCY | 000: 2.2MHz 001: 2MHz 010: 1.67MHz 011: Not used 100: 1.25MHz (default) 101: 1.11MHz 110: 0.85MHz 111: Not used                                                                       |

| D[4:3] | TRANSIENT_<br>RESPONSE  | Sets the transient response speed                                                                                                                                                     |

|        |                         | 00: Ultra-fast response speed 01: Fast response speed (default) 10: Normal response speed 11: Slow response speed                                                                     |

| D[2]   | PG_LOHI                 | 0: PG only senses a negative voltage excursion of V <sub>OUT</sub> from the reference 1: PG senses the positive and negative voltage excursion of V <sub>OUT</sub> from the reference |

| D[1]   | VIN_OVP                 | 0: Enables V <sub>IN</sub> over-voltage protection (OVP) (default). The converter turns off when V <sub>IN</sub> reaches V <sub>IN_MAX</sub> 1: Disables V <sub>IN</sub> OVP          |

| D[0]   | MODE                    | 0: Enables PFM mode 1: Disables PFM mode                                                                                                                                              |

#### **REG03: SYSCNTLREG2**

| Bits   | Bit Name             | Description                                                                                                                                                                                           |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:6] | RESERVED             | Reserved.                                                                                                                                                                                             |

| D[5]   | GO                   | Write to this bit to start a V <sub>OUT</sub> transition, regardless of its initial value.                                                                                                            |

| D[4]   | OUTPUT_<br>DISCHARGE | 0: Disables V <sub>OUT</sub> discharge. V <sub>OUT</sub> must be discharged by the load<br>1: Enables V <sub>OUT</sub> discharge. V <sub>OUT</sub> is discharged by the internal pull-down resistance |

| D[3]   | RESERVED             | Reserved.                                                                                                                                                                                             |

| D[2]   | SLEW_RATE            | 0: The slew rate is 32mV/μs<br>1: The slew rate is 8mV/μs                                                                                                                                             |

| D[1:0] | RESERVED             | Reserved.                                                                                                                                                                                             |

### REG04: ID1

| Bi  | ts Bit Name    | Description            |

|-----|----------------|------------------------|

| D[7 | 7:4] VENDOR_ID | Returns the vendor ID. |

| D[3 | 3:0] DIE_ID    | Returns the IC type.   |

### REG05: ID2

| Bits   | Bit Name | Description               |

|--------|----------|---------------------------|

| D[7:4] | RESERVED | Reserved.                 |

| D[3:0] | DIE_REV  | Returns the die revision. |

### **APPLICATION INFORMATION**

#### Selecting the Inductor

An inductor must supply a constant current to the output load while being driven by the switching input voltage. A larger-value inductor results in less ripple current and a lower output voltage ripple. However, larger-value inductors are physically larger, have a higher series resistance, and a lower saturation current.

A good rule to determine the inductance is to allow the inductor's peak-to-peak ripple current to be approximately 30% of the maximum switch current limit. Ensure that the peak inductor current is below the maximum switch current limit. The inductance value can be calculated with Equation (1):

$$L1 = \frac{V_{OUT}}{f_{SW} \times \Delta I_{L}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(1)

Where  $V_{OUT}$  is the output voltage,  $V_{IN}$  is the input voltage,  $f_{SW}$  is the switching frequency, and  $\Delta I_L$  is the peak-to-peak inductor ripple current.

Choose an inductor that does not saturate under the maximum inductor peak current. The peak inductor current can be estimated with Equation (2):

$$I_{LP} = I_{LOAD} + \frac{V_{OUT}}{2 \times f_{SW} \times L1} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(2)

Where I<sub>LOAD</sub> is the load current.

#### Selecting the Input Capacitor

The step-down converter's input current is discontinuous, and a capacitor is required to supply the AC current to the converter while maintaining the DC input voltage. Use low-ESR capacitors for the best performance. Ceramic capacitors are recommended, but tantalum or low-ESR electrolytic capacitors are sufficient.

For simplification, choose an input capacitor with a RMS current rating greater than half of the maximum load current. The input capacitor ( $C_{IN}$ ) can be electrolytic, tantalum, or ceramic.

When using electrolytic or tantalum capacitors, a small, high-quality ceramic capacitor (i.e. 0.1µF) should be placed as close to the IC as possible. When using ceramic capacitors, ensure that they have enough capacitance to provide sufficient charge in order to prevent an excessive input voltage ripple The input voltage ripple caused by capacitance can be calculated with Equation (3):

$$\Delta V_{IN} = \frac{I_{LOAD}}{f_{SW} \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(3)

#### **Selecting the Output Capacitor**

An output capacitor ( $C_{\text{OUT}}$ ) is required to maintain the DC output voltage. Ceramic, tantalum, or low-ESR electrolytic capacitors are recommended. Low-ESR capacitors keep the output voltage ripple low. The output voltage ripple can be estimated with Equation (4):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{SW}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times f_{\text{SW}} \times C_{\text{OUT}}}\right) \tag{4}$$

Where L is the inductor value, and  $R_{\text{ESR}}$  is the equivalent series resistance (ESR) value of  $C_{\text{OUT}}$

When using ceramic capacitors, the capacitance dominates the impedance at the switching frequency and causes the majority of the output voltage ripple. For simplification, the output voltage ripple can be calculated with Equation (5):

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f_{SW}^2 \times L \times C_{OUT}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \quad (5)$$

When using tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be estimated with Equation (6):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{SM}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times R_{\text{ESR}} \quad (6)$$

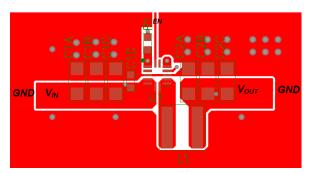

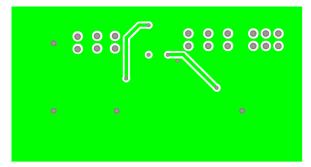

### PCB Layout Guidelines (11)

Efficient PCB layout is critical for stable operation. For the best results, refer to Figure 2 and follow the guidelines below:

- 1. Keep the switching current path short.

- Minimize the loop area formed by the input capacitor, high-side MOSFET, and low-side MOSFET.

- Place the input capacitor as close to VIN as possible.

- 4. Ensure that all feedback connections are short and direct.

- 5. Make the trace between VOUT and the output capacitor as short as possible.

- 6. Route SW away from sensitive analog areas, such as the output.

- 7. Connect IN, SW, and GND to large copper areas to cool the chip, and improve thermal performance and long-term reliability.

**Top Layer**

**Inner Layer 1**

**Inner Layer 2**

Bottom Layer

Figure 2: Recommended PCB Layout

#### Note:

11) The recommended PCB layout is based on Figure 3 on page 32

## TYPICAL APPLICATION CIRCUIT

Figure 3: Typical Application Circuit ( $f_{SW} = 1.25MHz$ ,  $V_{OUT} = 0.95V$ )

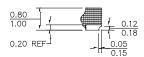

## **PACKAGE INFORMATION**

## QFN-14 (2.5mmx3mm) **Wettable Flank**

0.50

PIN 1 ID

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

**SECTION A-A**

**RECOMMENDED LAND PATTERN**

#### **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS. 2) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

- 3) JEDEC REFERENCE IS MO-220. 4) DRAWING IS NOT TO SCALE.

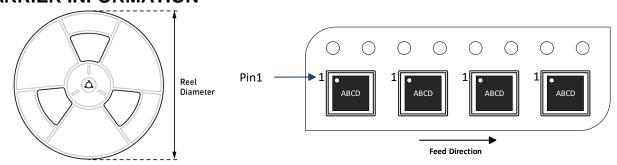

## **CARRIER INFORMATION**

| Part Number            | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Quantity/<br>Tray | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|------------------------|------------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|

| MPQ8847AGQB-<br>AEC1-Z | QFN14<br>(2.5mmx3mm)   | 5000              | N/A               | N/A               | 13in             | 12mm                     | 8mm                      |

## **REVISION HISTORY**

| Revision # | Revision<br>Date | Description     | Pages Updated |

|------------|------------------|-----------------|---------------|

| 1.0        | 11/18/2021       | Initial Release | =             |

**Notice:** The information in this document is subject to change without notice. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.