## **DATASHEET**

# **Description**

The 552-02S is a low skew, single-input to eight- output clock buffer. The device offers a dual input with pin select for switching between two clock sources. It has best in class Additive Phase Jitter of sub 50fsec

IDT makes many non-PLL and PLL based low skew output devices as well as Zero Delay Buffers to synchronize clocks. Contact us for all of your clocking needs.

## **Features**

- Low RMS Additive Phase Jitter: 50fs

- Low output skew: 50ps

- Operating Voltages of 1.8V to 3.3V

- Packaged in 16-pin TSSOP and 16-pin VFQFN, Pb-free

- Input clock multiplexer simplifies clock selection

- Output Enable pin tri-states outputs

- Input/Output clock frequency up to 200 MHz

- Low power CMOS technology

- 3.3V tolerant inputs

- Extended temperature (-40°C to +105°C)

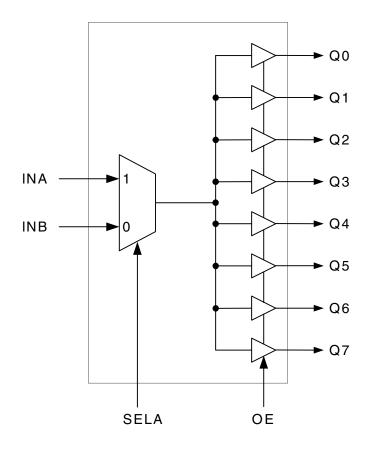

## **Block Diagram**

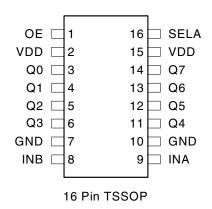

## **Pin Assignments**

# **Input Source Select**

| SELA | Input |

|------|-------|

| 0    | INB   |

| 1    | INA   |

# **Pin Descriptions**

| Pin    | Pin  | Pin    | Pin Description                                                        |

|--------|------|--------|------------------------------------------------------------------------|

| Number | Name | Type   |                                                                        |

| 1      | OE   | Input  | Output Enable. Tri-states outputs when low. Internal pull-up resistor. |

| 2      | VDD  | Power  | Connect to +1.8V, +2.5V or +3.3V. Must be the same as pin 15.          |

| 3      | Q0   | Output | Clock Output 0.                                                        |

| 4      | Q1   | Output | Clock Output 1.                                                        |

| 5      | Q2   | Output | Clock Output 2.                                                        |

| 6      | Q3   | Output | Clock Output 3.                                                        |

| 7      | GND  | Power  | Connect to ground.                                                     |

| 8      | INB  | Input  | Clock Input B. 3.3V tolerant.                                          |

| 9      | INA  | Input  | Clock Input A. 3.3V tolerant.                                          |

| 10     | GND  | Power  | Connect to ground.                                                     |

| 11     | Q4   | Output | Clock Output 4.                                                        |

| 12     | Q5   | Output | Clock Output 5.                                                        |

| 13     | Q6   | Output | Clock Output 6.                                                        |

| 14     | Q7   | Output | Clock Output 7.                                                        |

| 15     | VDD  | Power  | Connect to +1.8V, +2.5V or +3.3V. Must be the same as pin 2.           |

| 16     | SELA | Input  | Selects either INA or INB. Internal pull-up resistor.                  |

# **External Components**

A minimum number of external components are required for proper operation. Decoupling capacitors of 0.01  $\mu$ F should be connected between VDD on pin 2 and GND on pin 7, and between VDD on pin 15 and GND on pin 10, as close to the device as possible. A 33  $\Omega$  series terminating resistor should be used on each clock output if the trace is longer than 1 inch.

To achieve the low output skews that the 552-02S is capable of, careful attention must be paid to board layout. Essentially, all 8 outputs must have identical terminations, identical loads, and identical trace geometries. If they do not, the output skew will be degraded. For example, using a  $30\Omega$  series termination on one output (with  $33\Omega$  on the others) will cause at least 15ps of skew.

# **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 552-02S. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                    | Rating           |

|-----------------------------------------|------------------|

| Supply Voltage, VDD                     | 3.465V           |

| All Inputs and Outputs                  | -0.5 V to 3.465V |

| Ambient Operating Temperature, Extended | -40 to +105°C    |

| Storage Temperature                     | -65 to +150 °C   |

| Junction Temperature                    | 175 °C           |

| Soldering Temperature                   | 260 °C           |

# **Recommended Operation Conditions**

| Parameter                                         | Min.  | Тур. | Max.   | Units |

|---------------------------------------------------|-------|------|--------|-------|

| Ambient Operating Temperature, Extended           | -40   | -    | +105   | °C    |

| Power Supply Voltage (measured in respect to GND) | +1.71 |      | +3.465 | V     |

## **DC Electrical Characteristics**

VDD=1.8 V ±5%, Ambient temperature -40°C to +105°C, unless stated otherwise

| Parameter                    | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|------------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage            | VDD             |                          | 1.71    |      | 1.89    | V     |

| Input High Voltage, INA, INB | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | 1.89    | V     |

| Input Low Voltage, INA, INB  | V <sub>IL</sub> | Note 1                   |         |      | 0.3xVDD | V     |

| Input High Voltage, OE, SELA | V <sub>IH</sub> |                          | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, OE, SELA  | V <sub>IL</sub> |                          |         |      | 0.3xVDD | V     |

| Output High Voltage          | V <sub>OH</sub> | I <sub>OH</sub> = -10 mA | 1.3     |      |         | V     |

| Output Low Voltage           | V <sub>OL</sub> | I <sub>OL</sub> = 10 mA  |         |      | 0.35    | V     |

| Operating Supply Current     | IDD             | No load, 135 MHz         |         | 32   |         | mA    |

## **VDD=2.5 V ±5%**, Ambient temperature -40°C to +105°C, unless stated otherwise

| Parameter                    | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|------------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage            | VDD             |                          | 2.375   |      | 2.625   | V     |

| Input High Voltage, INA, INB | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | 2.625   | V     |

| Input Low Voltage, INA, INB  | $V_{IL}$        | Note 1                   |         |      | 0.3xVDD | V     |

| Input High Voltage, OE, SELA | V <sub>IH</sub> |                          | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, OE, SELA  | $V_{IL}$        |                          |         |      | 0.3xVDD | V     |

| Output High Voltage          | V <sub>OH</sub> | I <sub>OH</sub> = -16 mA | 1.8     |      |         | V     |

| Output Low Voltage           | V <sub>OL</sub> | I <sub>OL</sub> = 16 mA  |         |      | 0.5     | V     |

| Operating Supply Current     | IDD             | No load, 135 MHz         |         | 43   |         | mA    |

## VDD=3.3 V ±5%, Ambient temperature -40°C to +105°C, unless stated otherwise

| Parameter                    | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|------------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage            | VDD             |                          | 3.135   |      | 3.465   | V     |

| Input High Voltage, INA, INB | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | 3.465   | V     |

| Input Low Voltage, INA, INB  | V <sub>IL</sub> | Note 1                   |         |      | 0.3xVDD | V     |

| Input High Voltage, OE, SELA | V <sub>IH</sub> |                          | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, OE, SELA  | V <sub>IL</sub> |                          |         |      | 0.3xVDD | V     |

| Output High Voltage          | V <sub>OH</sub> | I <sub>OH</sub> = -25 mA | 2.2     |      |         | V     |

| Output Low Voltage           | V <sub>OL</sub> | I <sub>OH</sub> = 25 mA  |         |      | 0.7     | V     |

| Operating Supply Current     | IDD             | No load, 135 MHz         |         | 55   |         | mA    |

## **AC Electrical Characteristics**

**VDD = 1.8V ±5%**, Ambient Temperature -40°C to +105°C, unless stated otherwise

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.36 to 1.44 V, C <sub>L</sub> =5 pF                   |      | 1    | 1.5  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 1.44 to 0.36 V, C <sub>L</sub> =5 pF                   |      | 1    | 1.5  | ns    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

| Propagation Delay                 | Note 1                | 135MHz                                                 | 2    | 2.5  | 3    | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12KHz-20MHz                 |      | 50   | 65   | ps    |

| Output to output skew             | Note 2                | Rising edges at VDD/2                                  |      | 0    | 65   | ps    |

| Input A to Input B skew           | Note 3                |                                                        |      | 0    | 50   | ps    |

## **VDD = 2.5V ±5%**, Ambient Temperature -40°C to +105°C, unless stated otherwise

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.5 to 2.0 V, C <sub>L</sub> =5 pF                     |      | 0.6  | 1.0  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 2.0 to 0.5 V, C <sub>L</sub> =5 pF                     |      | 0.6  | 1.0  | ns    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

| Propagation Delay                 | Note 1                | 135MHz                                                 | 2    | 2.7  | 3.5  | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12KHz-20MHz                 |      | 50   | 65   | ps    |

| Output to output skew             | Note 2                | Rising edges at VDD/2                                  |      | 0    | 65   | ps    |

| Input A to Input B skew           | Note 3                |                                                        |      | 0    | 50   | ps    |

## **VDD = 3.3V ±5%**, Ambient Temperature -40°C to +105°C, unless stated otherwise

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.66 to 2.64 V, C <sub>L</sub> =5 pF                   |      | 0.6  | 1.0  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 2.64 to 0.66 V, C <sub>L</sub> =5 pF                   |      | 0.6  | 1.0  | ns    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

| Propagation Delay                 | Note 1                | 135MHz                                                 | 2    | 2.5  | 3    | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12KHz-20MHz                 |      | 50   | 65   | ps    |

| Output to output skew             | Note 2                | Rising edges at VDD/2                                  |      | 0    | 65   | ps    |

| Input A to Input B skew           | Note 3                |                                                        |      | 0    | 50   | ps    |

#### Notes:

- With rail-to-rail input clock.

- 2. Between any two outputs with equal loading.

3. Propagation delay matching through the part.

4. Duty cycle on outputs will match incoming clock duty cycle. Consult IDT for tight duty cycle clock generators.

01

SHEET 1 OF 2

PSC-4478

С

DO NOT SCALE DRAWING

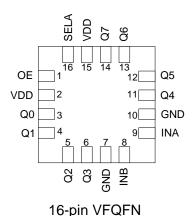

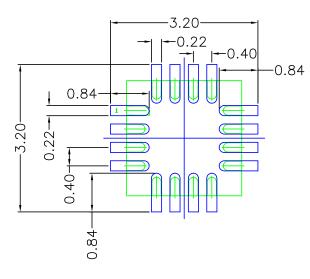

**Package**

Outline

and

Dimensions, cont. (16-pin VFQFN)

|     | REVISIONS        |          |          |

|-----|------------------|----------|----------|

| REV | DESCRIPTION      | DATE     | APPROVED |

| 00  | INITIAL RELEASE  | 04/03/14 | JH       |

| 01  | ADD PIN1 CHAMFER | 12/11/14 | JH       |

RECOMMENDED LAND PATTERN DIMENSION

### NOTES:

RENESAS

- DIMENSIONS ARE IN MM. ANGLES IN DEGREES.

P DOWN VIEW AS VIEWED ON PCB.

MPONENT OUTLINE IS SHOWN FOR REFERENCE IN GREEN.

ID PATTERN IN BLUE. NSMD PATTERN ASSUMED.

- 5. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

| TOLERANCES UNLESS SPECIFIED DECIMAL ANGULAR X± ±1° |          |       |                              | 6024 Silver  |          | y Road |

|----------------------------------------------------|----------|-------|------------------------------|--------------|----------|--------|

|                                                    |          |       | San Jose CA PHONE: (408)     |              |          | 0      |

| XX±<br>XXX±                                        |          | ww    | /w.IDT.com                   | FAX: (408) 2 | 284-8591 |        |

| APPROVALS                                          | DATE     | TITLE | TITLE CMG 16 PACKAGE OUTLINE |              |          |        |

| DRAWN JH                                           | 04/03/14 |       | 2.5 x 2.5 mm BODY            |              |          |        |

| CHECKED                                            |          |       | 0.40 mm PIT(                 | CH VFQFN     |          |        |

|                                                    |          | SIZE  | DRAWING No.                  |              |          | REV    |

|                                                    |          | С     | PSC-4478                     |              |          | 01     |

|                                                    |          | DO NO | OT SCALE DRAWING             | ·            | SHEET 2  | OF 2   |

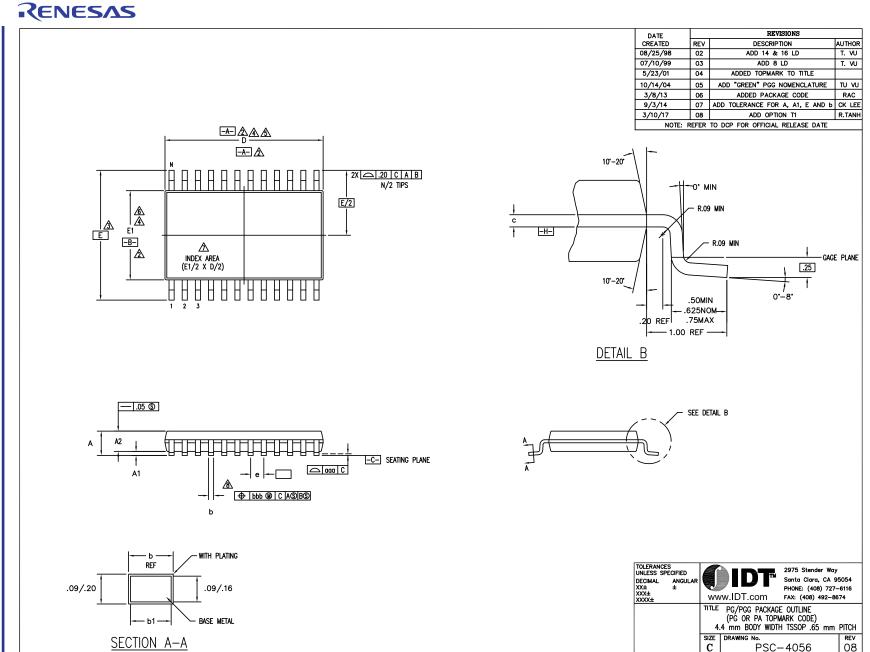

**Package**

Outline and Dimensions (16-pin TSSOP)

⋬

SHEET 1 OF 3

DO NOT SCALE DRAWING

| DATE     |       | REVISIONS                        |        |

|----------|-------|----------------------------------|--------|

| CREATED  | REV   | DESCRIPTION                      | AUTHOR |

| 08/25/98 | 02    | ADD 14 & 16 LD                   | T. VU  |

| 07/10/99 | 03    | ADD 8 LD                         | T. VU  |

| 5/23/01  | 04    | ADDED TOPMARK TO TITLE           |        |

| 10/14/04 | 05    | ADD "GREEN" PGG NOMENCLATURE     | TU VU  |

| 3/8/13   | 06    | ADDED PACKAGE CODE               | RAC    |

| 9/3/14   | 07    | ADD TOLERANCE FOR A, A1, E AND b | CK LEE |

| 3/10/17  | 08    | ADD OPTION T1                    | R.TANH |

| NOTE:    | REFER | TO DCP FOR OFFICIAL RELEASE DATE |        |

ackage

Outline

and

**Dimensions**

(16-pin

TSSOP), cont.

|                  |      | PG/P     | GG8  |     |      | PG/P     | GG14 |     | PG/PGG16 PG/PGG20 PG/PGG24 |          |      |     | PG/P | GG28     |      |     |      |          |      |      |      |          |      |     |

|------------------|------|----------|------|-----|------|----------|------|-----|----------------------------|----------|------|-----|------|----------|------|-----|------|----------|------|------|------|----------|------|-----|

| S<br>Y<br>M<br>R | JEDE | C VARIAT | ION  | i z | JEDE | C VARIAT | ION  | , p | JEDE                       | C VARIAT | ION  | i z | JEDE | C VARIAT | ION  | ים  | JEDE | C VARIAT | ION  | - To | JEDE | C VARIAT | ION  | Ē   |

| ľ                | MIN  | NOM      | MAX  | Ė   | MIN  | NOM      | MAX  | Ė   | MIN                        | NOM      | MAX  | Ė   | MIN  | NOM      | MAX  | Ė   | MIN  | NOM      | MAX  | Ė    | MIN  | NOM      | MAX  | 1 É |

| Α                | .85  | 1.10     | 1.20 |     | .85  | 1.10     | 1.20 |     | .85                        | 1.10     | 1.20 |     | .85  | 1.10     | 1.20 |     | .85  | 1.10     | 1.20 |      | .85  | 1.10     | 1.20 |     |

| A1               | .05  | .10      | .15  |     | .05  | .10      | .15  |     | .05                        | .10      | .15  |     | .05  | .10      | .15  |     | .05  | .10      | .15  |      | .05  | .10      | .15  |     |

| A2               | .80  | 1.00     | 1.05 |     | .80  | 1.00     | 1.05 |     | .80                        | 1.00     | 1.05 |     | .80  | 1.00     | 1.05 |     | .80  | 1.00     | 1.05 |      | .80  | 1.00     | 1.05 |     |

| D                | 2.90 | 3.00     | 3.10 | 4,5 | 4.90 | 5.00     | 5.10 | 4,5 | 4.90                       | 5.00     | 5.10 | 4,5 | 6.40 | 6.50     | 6.60 | 4,5 | 7.70 | 7.80     | 7.90 | 4,5  | 9.60 | 9.70     | 9.80 | 4,5 |

| Ε                | 6.20 | 6.40     | 6.60 | 3   | 6.20 | 6.40     | 6.60 | 3   | 6.20                       | 6.40     | 6.60 | 3   | 6.20 | 6.40     | 6.60 | 3   | 6.20 | 6.40     | 6.60 | 3    | 6.20 | 6.40     | 6.60 | 3   |

| E1               | 4.30 | 4.40     | 4.50 | 4,6 | 4.30 | 4.40     | 4.50 | 4,6 | 4.30                       | 4.40     | 4.50 | 4,6 | 4.30 | 4.40     | 4.50 | 4,6 | 4.30 | 4.40     | 4.50 | 4,6  | 4.30 | 4.40     | 4.50 | 4,6 |

| е                |      | .65 BSC  |      |     |      | .65 BSC  |      |     |                            | .65 BSC  |      |     |      | .65 BSC  |      |     |      | .65 BSC  |      |      |      | .65 BSC  |      |     |

| b                | .19  | .25      | .30  |     | .19  | .25      | .30  |     | .19                        | .25      | .30  |     | .19  | .25      | .30  |     | .19  | .25      | .30  |      | .19  | .25      | .30  |     |

| b1               | .19  | .22      | .25  |     | .19  | .22      | .25  |     | .19                        | .22      | .25  |     | .19  | .22      | .25  |     | .19  | .22      | .25  |      | .19  | .22      | .25  |     |

| aaa              | -    | -        | .10  |     | -    | -        | .10  |     | -                          | -        | .10  |     | _    | -        | .10  |     | -    | -        | .10  |      | -    | -        | .10  |     |

| bbb              | -    | _        | .10  |     | -    | -        | .10  |     | _                          | ı        | .10  |     | _    | ı        | .10  |     | -    | ı        | .10  |      | _    | -        | .10  |     |

| N                |      | 8        |      |     |      | 14       |      |     |                            | 16       |      |     |      | 20       |      |     |      | 24       |      |      |      | 28       |      |     |

#### NOTES:

- 1 ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994

- △ DATUMS —A— AND —B— TO BE DETERMINED AT DATUM PLANE —H—

- ⚠ DIMENSION E TO BE DETERMINED AT SEATING PLANE —C—

- DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE -H-

- DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED .15 mm PER SIDE

- DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED .25 mm PER SIDE

- DETAIL OF PIN 1 IDENTIFIER IS OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED

- LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION IS .08 mm IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .10 AND .25 mm FROM THE LEAD TIP

- 10 ALL DIMENSIONS ARE IN MILLIMETERS

- 11 THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-153, VARIATION AA, AB-1, AB, AC, AD & AE

|                  |      | OPTION T1           |      |             |  |  |  |  |  |  |

|------------------|------|---------------------|------|-------------|--|--|--|--|--|--|

|                  |      | PGG14T1             |      |             |  |  |  |  |  |  |

| S<br>M<br>B<br>L | JEDE | C VARIAT            | ION  | N           |  |  |  |  |  |  |

| M<br>B           |      | AB-1                |      | N<br>T<br>E |  |  |  |  |  |  |

| 2                | MIN  | NOM                 | MAX  | Ė           |  |  |  |  |  |  |

| Α                | .90  | 1.10                | 1.20 |             |  |  |  |  |  |  |

| A1               | .05  | .10                 | .15  |             |  |  |  |  |  |  |

| A2               | .80  | 1.00                | 1.05 |             |  |  |  |  |  |  |

| D                | 4.90 | 5.00                | 5.10 | 4,5         |  |  |  |  |  |  |

| Ε                | 6.20 | 6.40                | 6.60 | 3           |  |  |  |  |  |  |

| E1               | 4.30 | 4.40                | 4.50 | 4,6         |  |  |  |  |  |  |

| е                |      | .65 BSC             |      |             |  |  |  |  |  |  |

| Ь                | .19  | .25                 | .30  |             |  |  |  |  |  |  |

| b1               | .19  | .22                 | .25  |             |  |  |  |  |  |  |

| С                | .09  | -                   | .20  |             |  |  |  |  |  |  |

| aaa              | -    | -                   | .10  |             |  |  |  |  |  |  |

| bbb              | -    |                     |      |             |  |  |  |  |  |  |

| N                |      | -   -   .10  <br>14 |      |             |  |  |  |  |  |  |

| TOLERANCES UNLESS SPECIFIED DECIMAL ANGULAR XX± ± XXXX± XXXX± | <b>S</b> ≤  | W.IDT.com                                           | Santa Cla<br>PHONE: ( | ender Way<br>ara, CA 95<br>(408) 727–<br>8) 492–86 | 6116      |

|---------------------------------------------------------------|-------------|-----------------------------------------------------|-----------------------|----------------------------------------------------|-----------|

|                                                               | TITLE<br>4. | PG/PGG PACKAGE<br>(PG OR PA TOPM<br>4 mm BODY WIDTH | iark cod              | E)                                                 | PITCH     |

|                                                               | SIZE        | DRAWING No.<br>PSC-                                 | -4056                 | 6                                                  | REV<br>08 |

|                                                               | DO NO       | T SCALE DRAWING                                     |                       | SHEET 2                                            | OF 3      |

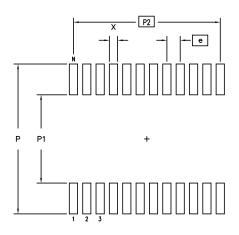

Package Outline and Dimensions (16-pin TSSOP), cont.

| DATE     |       | REVISIONS                        |       |

|----------|-------|----------------------------------|-------|

| CREATED  | REV   | DESCRIPTION                      | AUTHO |

| 08/25/98 | 02    | ADD 14 & 16 LD                   | T. VL |

| 07/10/99 | 03    | ADD 8 LD                         | T. VI |

| 5/23/01  | 04    | ADDED TOPMARK TO TITLE           |       |

| 10/14/04 | 05    | ADD "GREEN" PGG NOMENCLATURE     | TU V  |

| 3/8/13   | 06    | ADDED PACKAGE CODE               | RAC   |

| 9/3/14   | 07    | ADD TOLERANCE FOR A, A1, E AND b | CK LE |

| 3/10/17  | 08    | ADD OPTION T1                    | R.TAN |

| NOTE: F  | REFER | TO DCP FOR OFFICIAL RELEASE DATE |       |

## LAND PATTERN DIMENSIONS

|    | MIN   | MAX  |

|----|-------|------|-------|------|-------|------|-------|------|-------|------|-------|------|

| Р  | 7.20  | 7.40 | 7.20  | 7.40 | 7.20  | 7.40 | 7.20  | 7.40 | 7.20  | 7.40 | 7.20  | 7.40 |

| P1 | 4.20  | 4.40 | 4.20  | 4.40 | 4.20  | 4.40 | 4.20  | 4.40 | 4.20  | 4.40 | 4.20  | 4.40 |

| P2 | 1.95  | BSC  | 3.90  | BSC  | 4.55  | BSC  | 5.85  | BSC  | 7.15  | BSC  | 8.45  | BSC  |

| Х  | .30   | .50  | .30   | .50  | .30   | .50  | .30   | .50  | .30   | .50  | .30   | .50  |

| е  | .65 [ | BSC  | .65 E | BSC  | .65 E | BSC  | .65 f | BSC  | .65 [ | BSC  | .65 E | BSC  |

| N  |       | 3    | 1     | 14   |       | 16   |       | 0    | 24    |      | 2     | 8    |

|                     | RANCES   |              |       |                                   | 2975 Ste | ender Way                             |       |

|---------------------|----------|--------------|-------|-----------------------------------|----------|---------------------------------------|-------|

| DECI<br>XX±<br>XXX: | MAL<br>E | ANGULAR<br>± | W     | w.IDT.com                         | PHONE: ( | ara, CA 9:<br>(408) 727-<br>8) 492-86 | 6116  |

| AAA                 | 146      |              |       | (PG OR PA TOPM<br>4 mm BODY WIDTH | iark cod | E)                                    | PITCH |

|                     |          |              | SIZE  | DRAWING No.                       |          |                                       | REV   |

|                     |          |              | C     | PSC-                              | -4056    | 3                                     | 80    |

|                     |          |              | DO NO | OT SCALE DRAWING                  | •        | SHEET 3                               | OF 3  |

APRIL 18, 2017

## **Ordering Information**

| Part / Order Number | Marking | Shipping Packaging | Package      | Temperature     |

|---------------------|---------|--------------------|--------------|-----------------|

| 552-02SPGGI         |         | Tubes              | 16-pin TSSOP | -40°C to +105°C |

| 552-02SPGGI8        | TBD     | Tape and Reel      | 16-pin TSSOP | -40°C to +105°C |

| 552-02SCMGI         | 100     | Tubes              | 16-pin VFQFN | -40°C to +105°C |

| 552-02SCMGI8        |         | Tape and Reel      | 16-pin VFQFN | -40°C to +105°C |

<sup>&</sup>quot;G" after the two-letter package code denotes Pb-Free configuration, RoHS compliant.

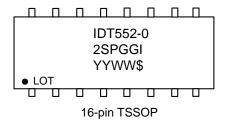

# **Marking Diagrams**

16-pin QFN

#### Notes:

- 1. "\*\*" is the lot sequence.

- 2. "YYWW" or "Y" is the last digit(s) of the year and week that the part was assembled.

- 3. "\$" denotes the mark code.

- 4. "LOT" denotes lot number.

- 5. "G" after the two-letter package code denotes RoHS compliant package.

- 6. "I" denotes extended temperature range device.

- 7. Bottom marking: country of origin (TSSOP only).

# **Revision History**

| Rev. | Date     | Originator | Description of Change                                                                                 |

|------|----------|------------|-------------------------------------------------------------------------------------------------------|

| В    | 04/18/17 | C.P.       | Replaced package outline drawings with latest CMG16 and PGG16 versions.     Updated legal disclaimer. |

| Α    | 07/11/16 | H.G.       | Release to final.                                                                                     |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/