FEDL22120-01

Issue date: Mar 1, 2023

# **ML22120**

Speech Synthesis LSI with pitch control function for Automotive

#### Overview

ML22120 is a speech synthesis LSI with a serial flash memory interface for sound data and compatible with the sound data playback function (Sound Generator).

It has a Clock Synchronous Serial Interface and I<sup>2</sup>C interface (slave).

The pitch and volume can be changed dynamically by controlling the setting register.

It adopts a 16-bit D/A converter and low-pass filter which realize high-quality sound.

It has the 5Band equalizer as a sound quality effect processing.

The functions necessary for sound output are integrated into a single chip, so that sound functions can be realized simply by adding this LSI and an external speaker amplifier.

In this data sheet, the sound data playback function is referred to as Sound Generator.

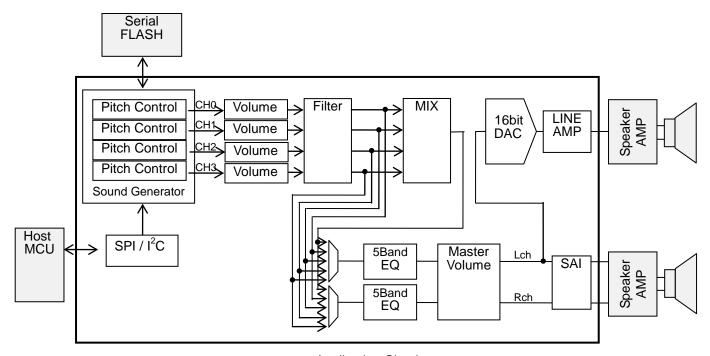

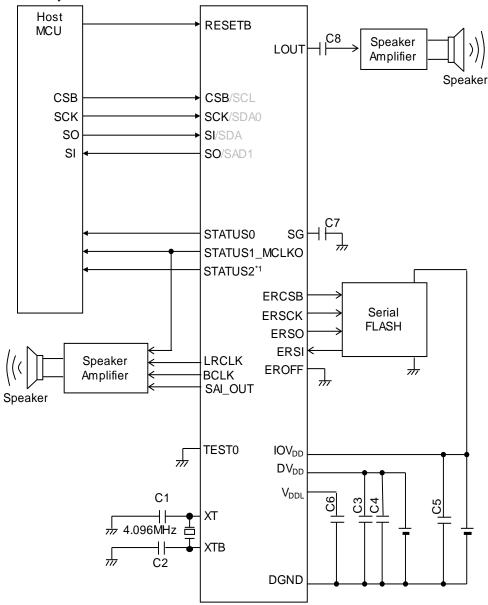

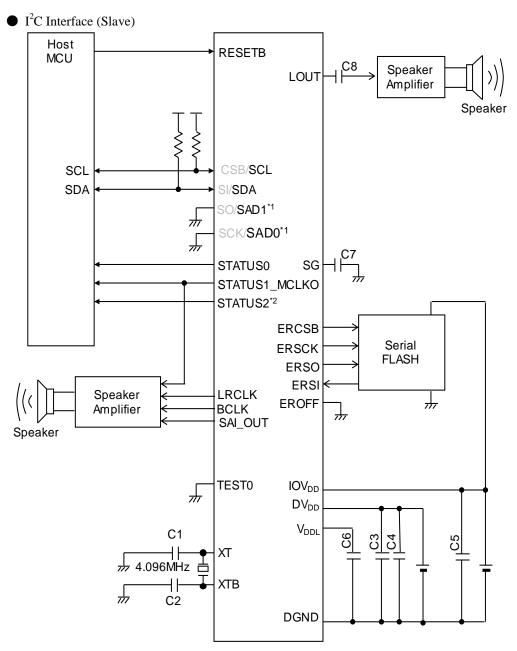

**Application Circuit**

ML22120

#### **■** Feature

Sound Generator

Speech synthesis algorithm: 16bit Straight PCM

Maximum number of phrases: 64 Phrases

Flash memory capacity: Maximum 128Mbits

| Sampling frequency (kHz)            | 48.0 | 24.0 | 12.0 | 32.0 | 16.0 | 8.0  |

|-------------------------------------|------|------|------|------|------|------|

| Maximum sound production time (sec) | 174  | 349  | 698  | 262  | 524  | 1048 |

• Sampling frequency: 48.0kHz/24.0kHz/12.0kHz, 32.0kHz/16.0kHz/8.0kHz

• Playback function

Repeat function

Mixing-function: 4-channels

Volume adjustment function:

Volume setting for each channel -76.7dB to +25.5dB/0.1dB step (including MUTE) Master volume setting for Lch/Rch -76.7dB to +25.5dB/0.1dB step (including MUTE)

With fade function

Pitch adjustment function: 4-channels

CH0/CH1:0.0625 times to 4 times (0.00390625 times step) CH2/CH3:0.0625 times to 1 times (0.00390625 times step)

With fade function

• Serial audio interface (master)

PCM format: 16bit Straight PCM

Sampling frequency at transfer(gfs): 48.0/32.0kHz (not depend on the sampling frequency of the Sound

Generator)

Data length: 16bit

MCLK frequency: 128/256/512gfs selectable

BCLK frequency: 32gfs to 64gfs

LRCLK transfer mode/ frame synchronous transfer mode selectable

LRCLK forward/reverse selectable 1-bit delay ON/OFF selectable MSB first/LSB first selectable

• 5Band equalizer Band center frequency, Band width, and Gain can be set.

Low-pass filter16-bit D/A converter

• Line amplifier output:  $10k\Omega$  driving

• MCU interface: Clock Synchronous Serial Interface/I<sup>2</sup>C Interface (Slave)

• Master clock frequency: 4.096MHz, 4.000MHz

• Power-supply voltage: 2.7V to 3.6V

• Power-supply voltage for a serial flash memory interface: 2.7V to 3.6V

• Operating temperature range:  $-40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}(+125^{\circ}\text{C}^{*_1})$  \*1 Key interlocking application

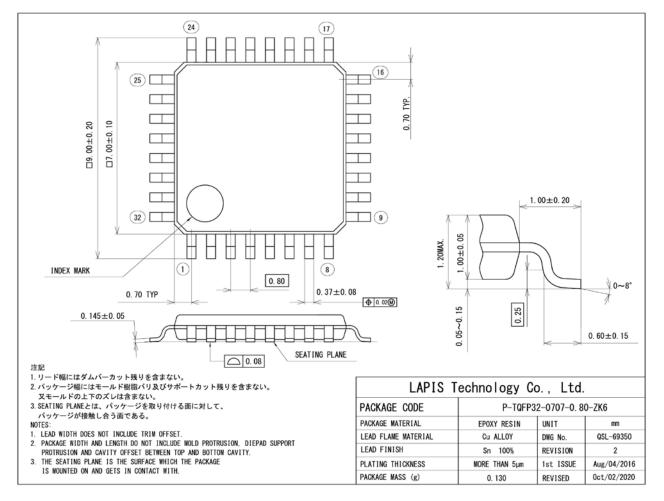

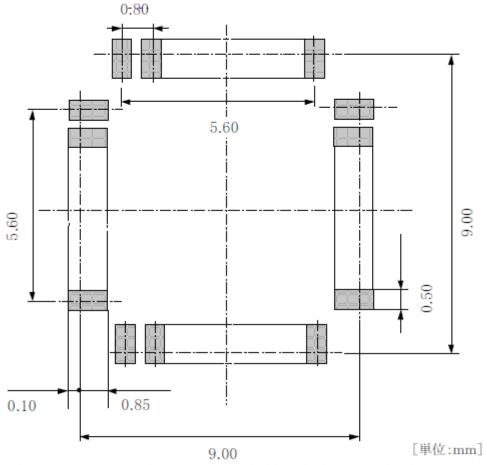

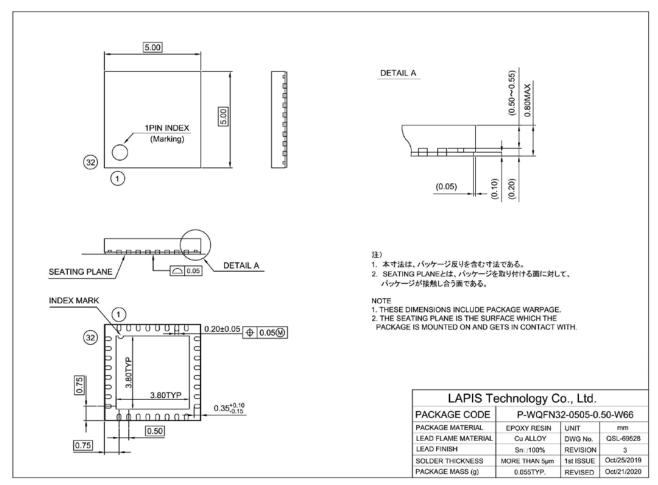

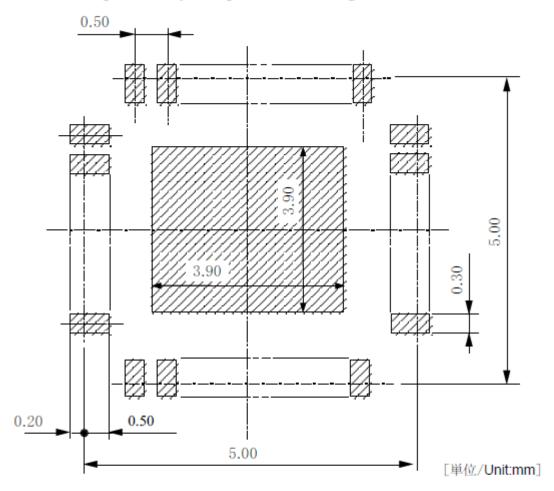

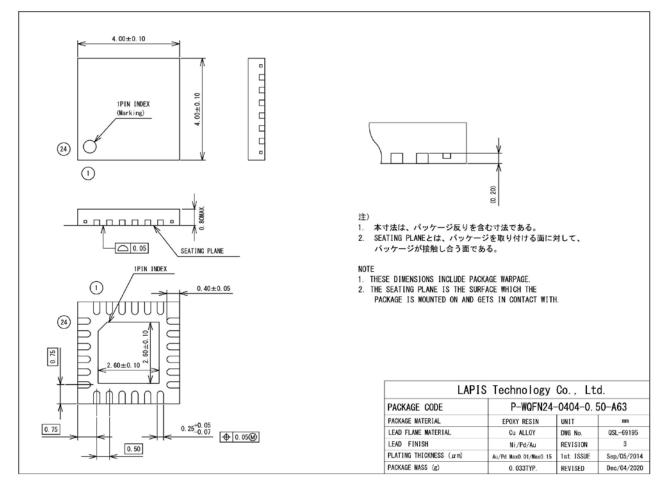

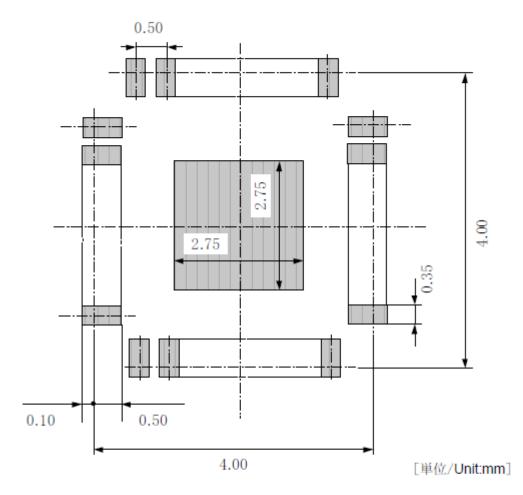

• Package: 32-pin TQFP (7mm x 7mm, 0.8mm pitch)

32-pin WQFN (5mm x 5mm, 0.5mm pitch) 24-pin WQFN (4mm x 4mm, 0.5mm pitch)

• Ordered Part Name: ML22120TB (32-pin TQFP)

ML22120GD (32-pin WQFN) Under Development

ML22120GP (24-pin WQFN)

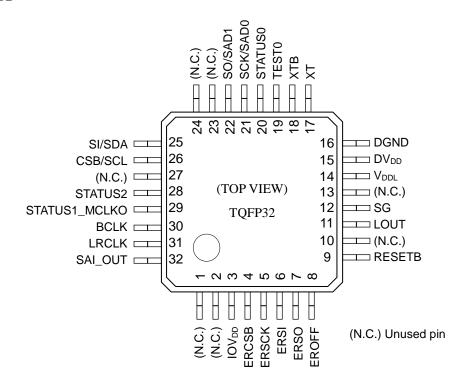

- Pin Configuration (TOP VIEW)

- ML22120TB

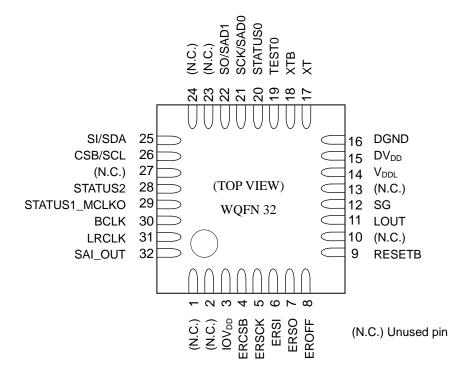

### ML22120GD

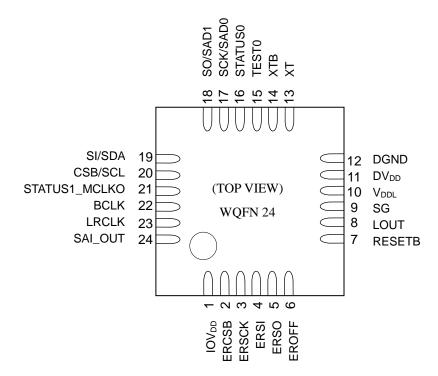

ML22120GP

ML22120

# ■ Pin Description

|                                            | in        |                   |     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Initial  |

|--------------------------------------------|-----------|-------------------|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 32<br>pin                                  | 24<br>pin | Symbol            | I/O | Attribute | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           | value *1 |

| 3                                          | 1         | IOV <sub>DD</sub> | Р   | -         | Serial flash memory interface power supply pin. Connect a bypass capacitor between this pin and the DGND pin.                                                                                                                                                                                                                                                                                                                                         | _        |

| 4                                          | 2         | ERCSB             | 0   | Negative  | Serial flash memory interface chip select output pin. Output the "H" level during non-access and the "L" level during access. Setting the EROFF pin to "L" enables output.                                                                                                                                                                                                                                                                            | Н        |

| 5                                          | 3         | ERSCK             | 0   | -         | Serial flash memory interface serial clock output pin. Setting the EROFF pin to "L" enables output.                                                                                                                                                                                                                                                                                                                                                   | L        |

| 6                                          | 4         | ERSI              | I   | -         | Serial flash memory interface serial data input pin. Setting the EROFF pin to "L" enables input. A pull-down resistor is internally connected.                                                                                                                                                                                                                                                                                                        | L        |

| 7                                          | 5         | ERSO              | 0   | -         | Serial flash memory interface serial data output pin. Setting the EROFF pin to "L" enables output.                                                                                                                                                                                                                                                                                                                                                    | L        |

| 8                                          | 6         | EROFF             | ı   | Positive  | Pin to disable the serial flash memory interface.  When this bit is set to "L", the serial flash memory interface pin is enabled. A pull-down resistor is internally connected.  Set this pin to "L" during playback operation using serial flash memory.  When this pin set to "H", the serial flash memory interface is in a condition of high-impedance.  Set to "H" when rewriting by connecting the FLASH writer to ERCSB / ERSCK / ERSI / ERSO. | L        |

| 9                                          | 7         | RESETB            | I   | Negative  | Reset-input pin. The LSI is initialized by the "L" level input. After a reset is input, all the circuits stop operating and enter the standby state. At power-on, input an "L" level to this pin. After the power supply voltage stabilizes, set this pin to an "H" level.                                                                                                                                                                            | _        |

| 11                                         | 8         | LOUT              | 0   | -         | Used exclusively for line amplifier output.                                                                                                                                                                                                                                                                                                                                                                                                           | L        |

| 12                                         | 9         | SG                | 0   | -         | Reference voltage output pin for line amplifier. Connect a capacitor between this pin and DGND pin.                                                                                                                                                                                                                                                                                                                                                   | L        |

| 14                                         | 10        | $V_{DDL}$         | 0   | -         | 1.5V regulator output pin. Used as internal power supply. Connect a capacitor between this pin and DGND pin as close as possible.                                                                                                                                                                                                                                                                                                                     | L        |

| 15                                         | 11        | $D_{VDD}$         | Р   | -         | Digital power supply pin.  Connect a bypass capacitor between this pin and the DGND pin.                                                                                                                                                                                                                                                                                                                                                              | _        |

| 16                                         | 12        | DGND              | G   |           | Digital ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                   | _        |

| 1,<br>2,<br>10,<br>13,<br>23,<br>24,<br>27 | ı         | N.C.              | -   | -         | Unused pin.<br>Leave open.                                                                                                                                                                                                                                                                                                                                                                                                                            | Hi-Z     |

<sup>\*1</sup> Initial value at reset input and standby. The pin whose IO is "I" indicates a fixed level from outside.

# ML22120

| Р         | in        |                   |     |           |                                                                                                                                                                                                                                                                                                                                                      | <br>Initial |

|-----------|-----------|-------------------|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 32<br>pin | 24<br>pin | Symbol            | I/O | Attribute | Description                                                                                                                                                                                                                                                                                                                                          | value *1    |

| 17        | 13        | XT                | ı   | Negative  | Crystal or ceramic resonator connection pin. A feedback resistor of about $1M\Omega$ is built in between the XT pin and the XTB pin. To use an external clock, input from this pin. Delete the capacitor when a crystal or ceramic resonator is connected. When using a resonator, connect it as close as possible. Leave it open when not in use.   | L           |

| 18        | 14        | XTB               | 0   | Positive  | Crystal or ceramic resonator connection pin.  When an external clock is used, leave it open and capacitor is not required when a crystal or ceramic resonator is connected.  When using a resonator, connect it as close as possible.  Leave it open when not in use.                                                                                | Н           |

| 19        | 15        | TEST0             | I   | Positive  | Input pin for testing. A pull-down resistor is internally connected. Fix to the DGND.                                                                                                                                                                                                                                                                | L           |

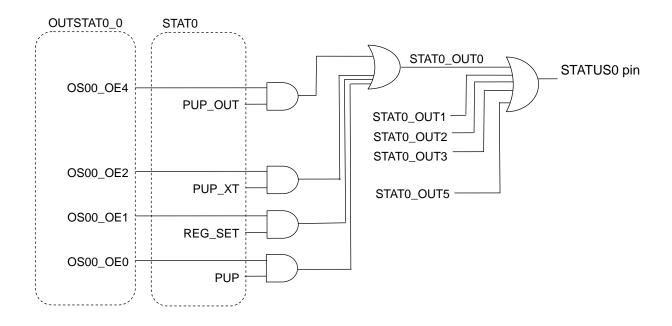

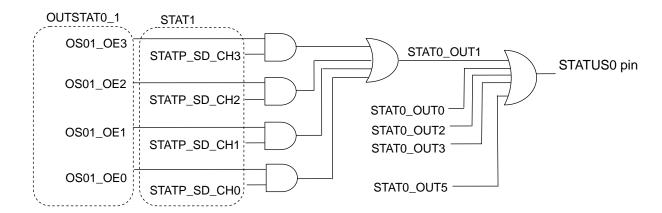

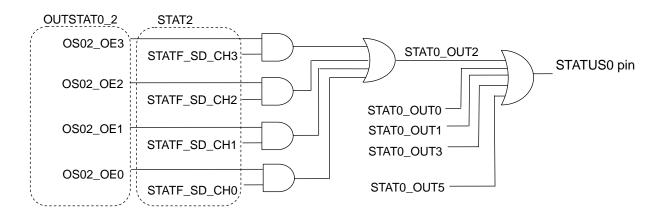

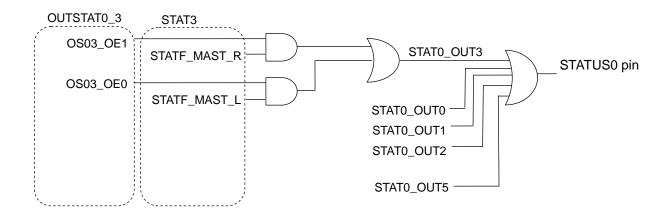

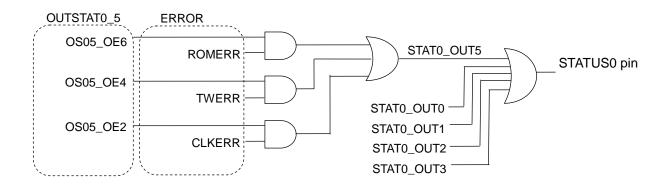

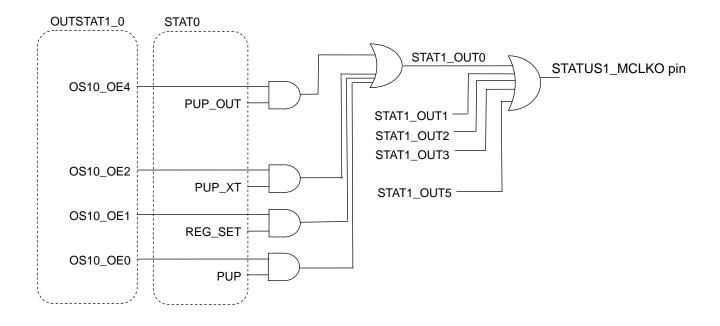

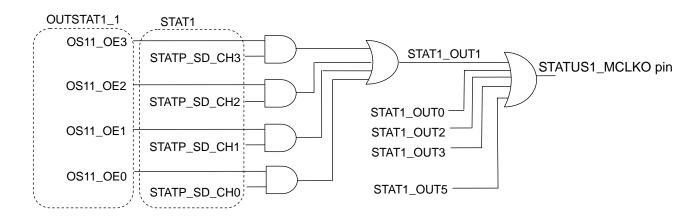

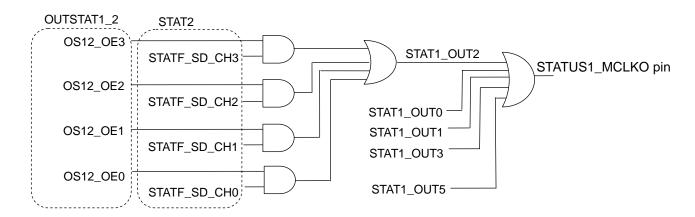

| 20        | 16        | STATUS0           | 0   | -         | Status output pin 0. Set the OUTSTATO_0 to 5 registers to select the output of various statuses, playback status of each channel, and internal error status.                                                                                                                                                                                         | L           |

|           |           |                   | 1   | -         | SCK: Synchronous serial interface clock input pin.                                                                                                                                                                                                                                                                                                   | L           |

| 21        | 17        | SCK/SAD0          | ı   | -         | SAD0: $I^2C$ slave address select pin. Set the slave address by fixing it to $DV_{DD}$ or DGND.                                                                                                                                                                                                                                                      | _           |

| 22        | 18        | SO/SAD1           | 0   | -         | SO: Synchronous serial interface data output pin. When the status is read, the data is output in synchronization with SCK. when the status is not read, this pin enters a high-impedance state.                                                                                                                                                      | Hi-Z        |

|           |           |                   | ı   | -         | SAD1: $I^2C$ slave address select pin. Set the slave address by fixing it to $DV_{DD}$ or DGND.                                                                                                                                                                                                                                                      | _           |

|           |           |                   | ı   | -         | SI: Synchronous serial interface data input pin. Data is fetched in synchronization with SCK.                                                                                                                                                                                                                                                        | L           |

| 25        | 19        | SI/SDA            | Ю   | -         | SDA: I <sup>2</sup> C slave serial data input/output pin. An input / output pin used for setting the write mode / read mode, writing the slave address, and writing / reading data. When using an I <sup>2</sup> C, be sure to insert a pull-up resistor between DV <sub>DD</sub> pin. Output: Nch MOS OPEN DRAIN output Input: High-impedance input | Hi-Z        |

|           |           | 007/00/           | ı   | Negative  | CSB: Synchronous serial interface chip select pin. The SCK and SI inputs are accepted only when this pin is at the "L" level.                                                                                                                                                                                                                        | Н           |

| 26        | 20        | CSB/SCL           | I   | -         | SCL: I <sup>2</sup> C slave serial clock pin.<br>When using an I <sup>2</sup> C, be sure to insert a pull-up resistor between DV <sub>DD</sub> pin.                                                                                                                                                                                                  | Hi-Z        |

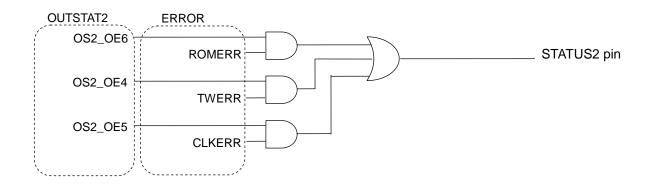

| 28        | -         | STATUS2           | 0   | -         | Status output pin 2. Set the OUTSTAT2 register to select internal error status.                                                                                                                                                                                                                                                                      | L           |

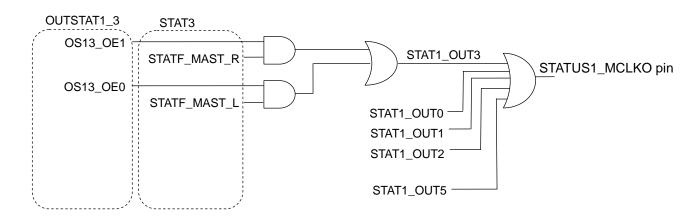

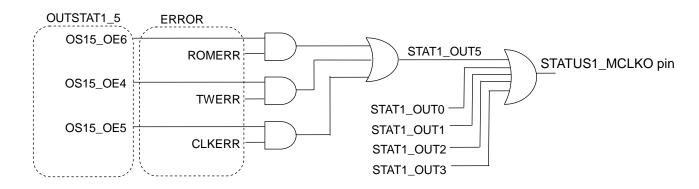

| 29        | 21        | STATUS1_<br>MCLKO | 0   | -         | Status output pin 1 or SAI master clock output pin.  When the MCLKSEL bit of the IFSEL register is set to "0", set the OUTSTAT1_0 to 5 registers to select the output of various statuses, playback status of each channel, and internal error status.  When the MCLKSEL bit of the IFSEL register is set to "1", SAI master clock is output.        | L           |

| 30        | 22        | BCLK              | 0   | -         | SAI bit clock output pin.                                                                                                                                                                                                                                                                                                                            | L           |

| 31        | 23        | LRCLK             | 0   | -         | SAI word clock output pin.                                                                                                                                                                                                                                                                                                                           | L           |

| 32        | 24        | SAI_OUT           | 0   | -         | SAI bit data output pin. Output data at the falling edge of BCLK.                                                                                                                                                                                                                                                                                    | L           |

<sup>32 24</sup> SAI\_OUT O - SAI bit data output pin. Output data at the falling edge of BCLK.

\*1 Initial value at reset input and standby. The pin whose IO is "I" indicates a fixed level from outside.

ML22120

# ■ Termination of Unused Pins

This section explains how to terminate unused pins.

| Symbol   | Recommended pin termination |

|----------|-----------------------------|

| EROFF    | Connect to the DGND.        |

| TEST0    | Connect to the DGND.        |

| XT       |                             |

| XTB      |                             |

| LOUT     |                             |

| STATUS0  |                             |

| STATUS1_ |                             |

| MCLKO    | Leave open.                 |

| STATUS2  |                             |

| BCLK     |                             |

| LRCLK    |                             |

| SAI_OUT  |                             |

| N.C.     |                             |

# ■ I/O Equivalent Circuit

| Classifi cation | Circuit | Overview                                                                                                                                                                                                                                     |

|-----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A               |         | Attribute: Input Power: DV <sub>DD</sub> Function: CMOS inputs with pull-down Applicable pin: TEST0  Attribute: Input Power: IOV <sub>DD</sub> Function: CMOS inputs with pull-down Applicable pin: EROFF, ERSI                              |

| В               |         | Attribute: Input Power: DV <sub>DD</sub> Function: CMOS inputs Applicable pin: SCK/SAD0, RESETB                                                                                                                                              |

| С               |         | Attribute: Output Power: DV <sub>DD</sub> Function: CMOS outputs Applicable pin: STATUS0, STATUS1_MCLKO, STATUS2, LRCLK, BCLK, SAI_OUT  Attribute: Output Power: IOV <sub>DD</sub> Function: CMOS outputs Applicable pin: ERCSB, ERSCK, ERSO |

| D               |         | Attribute: Input/output Power: DV <sub>DD</sub> Function: CMOS inputs / outputs Applicable pins: SO/SAD1                                                                                                                                     |

| Classifi cation | Circuit        | Overview                                                                                                                        |

|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------|

| E               |                | Attribute: input/output Power: DV <sub>DD</sub> Function: CMOS inputs / Nch Open Drain outputs Applicable pins: CSB/SCL, SI/SDA |

| F               | XTB  XTB  XTB  | Attribute: Oscillator circuit Power: DV <sub>DD</sub> Function: 4.096M, 4.000M oscillation Applicable pins: XT, XTB             |

| G               | analog入力<br>SG | Attribute: Analog Power: DV <sub>DD</sub> Function: Sound output Applicable pin: LOUT                                           |

| Н               |                | Attribute: Analog Power: DV <sub>DD</sub> Function: Line amplifier reference voltage output Applicable pins: SG                 |

ML22120

## ■ Electrical characteristics

# Absolute maximum rating

|                              |                                       |                                                  | DGND=0V                        | , Ta=25°C |

|------------------------------|---------------------------------------|--------------------------------------------------|--------------------------------|-----------|

| Parameter                    | Symbol                                | Condition                                        | Rating                         | Unit      |

| Power supply voltage 1       | DV <sub>DD</sub><br>IOV <sub>DD</sub> | _                                                | -0.3 to +4.6                   | V         |

| Input voltage 1              | $V_{IN1}$                             | _                                                | -0.3 to DV <sub>DD</sub> +0.3  | V         |

| Input voltage 2              | $V_{IN2}$                             | _                                                | -0.3 to IOV <sub>DD</sub> +0.3 | V         |

| Allowable loss               | P <sub>D</sub>                        | When the LSI is mounted on JEDEC 2-layer board.  | 1000                           | mW        |

| Output short-circuit current | los                                   | Applies to pins other than $V_{\text{DDL}}$ pin. | 10                             | mA        |

|                              |                                       | Applies to the V <sub>DDL</sub> pin.             | 50                             | mA        |

| Storage temperature          | T <sub>STG</sub>                      | _                                                | -55 to +150                    | °C        |

# • Recommended operating conditions

|                                                                   |                                       |           |                                    |       |      | DGND=0V |

|-------------------------------------------------------------------|---------------------------------------|-----------|------------------------------------|-------|------|---------|

| Parameter                                                         | Symbol                                | Condition |                                    | Range |      |         |

| DV <sub>DD</sub> ,<br>IOV <sub>DD</sub> ,<br>Power-supply voltage | DV <sub>DD</sub><br>IOV <sub>DD</sub> | _         | 2.7 to 3.6                         |       |      | V       |

| Operating temperature                                             | Тор                                   | _         | -40 to +105 ( +125 <sup>*1</sup> ) |       | °C   |         |

|                                                                   |                                       |           | Min.                               | Тур.  | Max. |         |

| Master clock frequency                                            | fosc                                  | _         | Тур                                | 4.096 | Тур  | MHz     |

|                                                                   |                                       |           | -5%                                | 4.000 | +5%  |         |

<sup>\*1</sup> Key interlocking application

ML22120

## DC characteristics

|                        |                   | =IOV <sub>DD</sub> =2.7 to 3.6V, DGN | D=0V, Ta=-40 to +125°0 | C, Load capac          | itance of out      | out pin =15pF         | (max.) |

|------------------------|-------------------|--------------------------------------|------------------------|------------------------|--------------------|-----------------------|--------|

| Parameter              | Symbol            | Condition                            | Applicable pin         | Min.                   | Typ. <sup>*1</sup> | Max.                  | Unit   |

|                        |                   |                                      | CSB/SCL                |                        |                    |                       |        |

|                        |                   |                                      | SCK/SAD0               |                        |                    |                       |        |

|                        |                   |                                      | SI/SDA                 |                        |                    |                       |        |

| "H" input voltage 1    | $V_{IH1}$         | _                                    | (SO)/SAD1              | 0.8×DV <sub>DD</sub>   | _                  | $DV_DD$               | V      |

|                        |                   |                                      | XT                     |                        |                    |                       |        |

|                        |                   |                                      | RESETB                 |                        |                    |                       |        |

|                        |                   |                                      | TEST0                  |                        |                    |                       |        |

| "H" input voltage 2    | \/                |                                      | EROFF                  | 0.8×IOV <sub>DD</sub>  |                    | IOV <sub>DD</sub>     | V      |

| H IIIput voitage 2     | $V_{IH2}$         | _                                    | ERSI                   | U.OXIOVDD              | _                  | IOVDD                 | V      |

|                        |                   |                                      | CSB/SCL                |                        |                    |                       |        |

|                        |                   |                                      | SCK/SAD0               |                        |                    |                       |        |

|                        |                   |                                      | SI/SDA                 |                        |                    |                       |        |

| "L" input voltage 1    | $V_{IL1}$         | _                                    | (SO)/SAD1              | 0                      | _                  | 0.2×DV <sub>DD</sub>  | V      |

|                        |                   |                                      | XT                     |                        |                    |                       |        |

|                        |                   |                                      | RESETB                 |                        |                    |                       |        |

|                        |                   |                                      | TEST0                  |                        |                    |                       |        |

| III II imput valtaga O | \/                |                                      | EROFF                  | 0                      |                    | 0.0.10\/              | \/     |

| "L" input voltage 2    | $V_{IL2}$         | _                                    | ERSI                   | 0                      | _                  | 0.2×IOV <sub>DD</sub> | V      |

| "H" output voltage 1   | V <sub>OH1</sub>  | I <sub>OH</sub> = -50μA              | XTB                    | DV <sub>DD</sub> -0.4  | _                  | _                     | V      |

|                        |                   |                                      | LRCLK                  |                        |                    |                       |        |

|                        |                   |                                      | BCLK                   |                        |                    |                       |        |

|                        |                   |                                      | SAI_OUT                |                        |                    |                       |        |

| "H" output voltage 2   | $V_{OH2}$         | $I_{OH} = -1mA$                      | SO/(SAD1)              | DV <sub>DD</sub> -0.4  | _                  | _                     | V      |

| 3.1                    | 0.12              | 0                                    | STATUS0                |                        |                    |                       |        |

|                        |                   |                                      | STATUS1_MCLKO          |                        |                    |                       |        |

|                        |                   |                                      | STATUS2                |                        |                    |                       |        |

| -                      |                   |                                      | ERCSB                  |                        |                    |                       |        |

| "H" output voltage 3   | V <sub>OH3</sub>  | $I_{OH} = -1mA$                      | ERSCK                  | IOV <sub>DD</sub> -0.4 | _                  | _                     | V      |

| 3.1                    | 01.0              | <b></b>                              | ERSO                   |                        |                    |                       |        |

| "L" output voltage 1   | V <sub>OL1</sub>  | I <sub>OL</sub> = 50μA               | XTB                    | _                      | _                  | 0.4                   | V      |

|                        |                   | <u> </u>                             | LRCLK                  |                        |                    |                       |        |

|                        |                   |                                      | BCLK                   |                        |                    |                       |        |

|                        |                   |                                      | SAI_OUT                |                        |                    |                       |        |

| "L" output voltage 2   | V <sub>OL2</sub>  | $I_{OL} = 2mA$                       | SO/(SAD1)              | _                      | _                  | 0.4                   | V      |

| 3.1                    | 022               | 02                                   | STATUS0                |                        |                    |                       |        |

|                        |                   |                                      | STATUS1_MCLKO          |                        |                    |                       |        |

|                        |                   |                                      | STATUS2                |                        |                    |                       |        |

|                        |                   |                                      | ERCSB                  |                        |                    |                       |        |

| "L" output voltage 3   | V <sub>OL3</sub>  | $I_{OL} = 2mA$                       | ERSCK                  | _                      | _                  | 0.4                   | V      |

| 1 0                    | 020               | 02                                   | ERSO                   |                        |                    |                       |        |

|                        |                   |                                      | (SI)/SDA               |                        |                    |                       |        |

| "L" output voltage 4   | $V_{OL4}$         | $I_{OL} = 3mA$                       | (CSB)/SCL              | _                      | _                  | 0.4                   | V      |

| Output leakage         | 1.                | VOH=DV <sub>DD</sub>                 | -                      |                        |                    |                       |        |

| current 1              | I <sub>OOH1</sub> | (in high-impedance state)            | (SI)/SDA               |                        | _                  | 10                    | μΑ     |

|                        |                   | VOL=DGND                             | (CSB)/SCL              |                        |                    |                       | _      |

|                        | I <sub>OOL1</sub> | (in high-impedance state)            | SO/(SAD1)              | -10                    | _                  | -                     | μΑ     |

| Output leakage         |                   | VOH=IOV <sub>DD</sub>                |                        |                        |                    |                       |        |

| current 2              | I <sub>OOH2</sub> | (in high-impedance state)            | ERCSB                  | -                      | _                  | 10                    | μA     |

|                        |                   | VOL=DGND                             | ERSCK                  |                        |                    |                       |        |

|                        | I <sub>OOL2</sub> | (in high-impedance state)            | ERSO                   | -10                    | _                  | _                     | μΑ     |

| -                      | L                 | (iii nigh impedance state)           |                        |                        |                    | L                     | Ь      |

ML22120

| Parameter                                 | Symbol           | =IOV <sub>DD</sub> =2.7 to 3.6V, DGN Condition                                                                  | Applicable pin                             | Min. | Typ.*1          | Max.                                          | Unit  |

|-------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|-----------------|-----------------------------------------------|-------|

|                                           | <del>'</del> .   |                                                                                                                 | '''                                        | 1    |                 |                                               |       |

| "H" input current 1                       | I <sub>IH1</sub> | $V_{IH} = DV_{DD}$                                                                                              | XT<br>CSB/SCL                              | 0.8  | 5.0             | 20                                            | μΑ    |

|                                           |                  |                                                                                                                 | SCK/SAD0                                   |      |                 |                                               |       |

| "H" input current 2                       | I <sub>IH2</sub> | $V_{IH} = DV_{DD}$                                                                                              | SI/SDA                                     | _    | _               | 10                                            | uА    |

|                                           | -1112            | *    1 = *    0                                                                                                 | (SO)/SAD1                                  |      |                 |                                               | P., . |

|                                           |                  |                                                                                                                 | RESETB                                     |      |                 |                                               |       |

| "H" input current 3                       | I <sub>IH3</sub> | $V_{IH} = DV_{DD}$                                                                                              | TEST0                                      | 20   | 300             | 700                                           | μA    |

| "H" input current 4                       | I <sub>IH4</sub> | $V_{IH} = IOV_{DD}$                                                                                             | EROFF                                      | 20   | 300             | 700                                           | μΑ    |

| "H" input current 5                       | I <sub>IH5</sub> | $V_{IH} = IOV_{DD}$                                                                                             | ERSI                                       | 2    | 40              | 300                                           | μΑ    |

| "L" input current 1                       | I <sub>IL1</sub> | $V_{IL} = DGND$                                                                                                 | XT                                         | -20  | -5.0            | -0.8                                          | μΑ    |

| "L" input current 2                       | I <sub>IL2</sub> | $V_{IL} = DGND$                                                                                                 | CSB/SCL<br>SCK/SAD0<br>SI/SDA<br>(SO)/SAD1 | -10  | _               | _                                             | μA    |

|                                           |                  |                                                                                                                 | RESETB<br>EROFF<br>TEST0                   |      |                 | 20 μA  10 μA  700 μA  700 μA  300 μA  -0.8 μA |       |

| During playback<br>Current<br>consumption | I <sub>DDO</sub> | f <sub>OSC</sub> =4.096MHz<br>fs=48kHz, f=1kHz,<br>(4ch simultaneous)<br>operating the line<br>amplifier output | _                                          | _    | 6 <sup>*2</sup> | 15 <sup>*2</sup>                              | mA    |

| Standby                                   |                  | Ta=-40 to +55°C                                                                                                 | _                                          | _    | 1*2             | 10.0 <sup>*2</sup>                            | μA    |

| Current consumption*3                     | I <sub>DDS</sub> | Ta=-40 to +125°C                                                                                                | _                                          | _    | 1 <sup>*2</sup> | 30.0 <sup>*2</sup>                            | μA    |

<sup>\*1</sup> Typ. : DV<sub>DD</sub>=IOV<sub>DD</sub>=3.0V,DGND=0 V,Ta=25°C

<sup>\*2</sup> Total values of the  $\text{DV}_{\text{DD}}$  pin and  $\text{IOV}_{\text{DD}}$  pin

<sup>\*3</sup> RESETB pin is at the "L" level.

## Analog Part Characteristics

| Parameter                             | Symbol           | Condition                                  | Min.                         | Тур.                | Max.                         | Unit |

|---------------------------------------|------------------|--------------------------------------------|------------------------------|---------------------|------------------------------|------|

| RC4MHz                                | Frc              | _                                          | 3.68                         | 4.096               | 4.51                         | MHz  |

| Line amplifier output resistance      | R <sub>LA1</sub> | When 1/2DV <sub>DD</sub> ± 1 mA is applied | _                            | _                   | 300                          | Ω    |

| Line amplifier output-load-resistance | R <sub>LA2</sub> | For DGND                                   | 10                           |                     |                              | kΩ   |

| Line amplifier Out put Voltage Range  | V <sub>AO</sub>  | No output load                             | DV <sub>DD</sub> /6          | _                   | DV <sub>DD</sub> ×5/6        | V    |

| SG pin output voltage                 | V <sub>SG</sub>  | _                                          | 0.95x<br>DV <sub>DD</sub> /2 | DV <sub>DD</sub> /2 | 1.05x<br>DV <sub>DD</sub> /2 | V    |

| SG pin output resistance              | R <sub>SG</sub>  |                                            | 57                           | 96                  | 135                          | kΩ   |

## AC characteristic

| Parameter                                                      | Symbol            | Condition                                                  | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------|-------------------|------------------------------------------------------------|------|------|------|------|

| Master clock duty cycle                                        | f <sub>duty</sub> | _                                                          | 40   | 50   | 60   | %    |

| RESETB input pulse width                                       | t <sub>RST</sub>  | _                                                          | 10   | _    | -    | μs   |

| Reset noise rejection pulse width                              | t <sub>NRST</sub> | RESETB pin                                                 | _    | _    | 0.1  | μs   |

| Initialization time after reset release                        | t <sub>PRC</sub>  | _                                                          | _    |      | 5    | ms   |

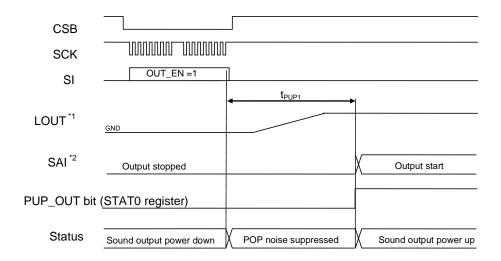

| Line amplifier power up time (with Pop Noise Suppression)      | t <sub>PUP1</sub> | 4.096MHz external clock input<br>POP="H"<br>OUT_EN="L"→"H" | _    | 73   | 77   | ms   |

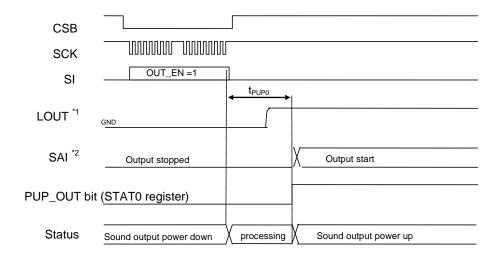

| Line amplifier power up time (without Pop Noise Suppression)   | t <sub>PUP0</sub> | 4.096MHz external clock input<br>POP="L"<br>OUT_EN="L"→"H" | _    | 33   | 37   | ms   |

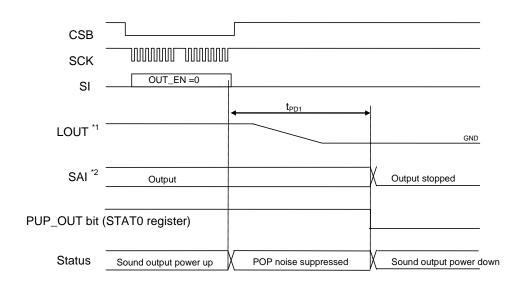

| Line amplifier power down time (with Pop Noise Suppression)    | t <sub>PD1</sub>  | 4.096MHz external clock input<br>POP="H"<br>OUT_EN="H"→"L" | _    | 144  | 148  | ms   |

| Line amplifier power down time (without Pop Noise Suppression) | t <sub>PD0</sub>  | 4.096MHz external clock input<br>POP="L"<br>OUT_EN="H"→"L" | _    | 104  | 108  | ms   |

| Playback start time                                            | t <sub>PSTA</sub> | $f_{OSC} = 4.096MHz$                                       | _    | _    | 400  | μs   |

| Fade start time                                                | t <sub>FAD</sub>  | $f_{OSC} = 4.096MHz$                                       | _    | _    | 400  | μs   |

| Playback stop time                                             | t <sub>PSTP</sub> | $f_{OSC} = 4.096MHz$                                       | _    | _    | 5    | ms   |

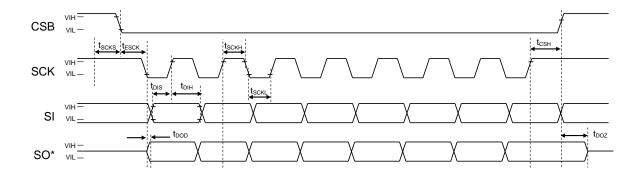

## • AC Characteristics (Clock Synchronous Serial Interface)

DV<sub>DD</sub>=IOV<sub>DD</sub>=2.7 to 3.6V, DGND=0V, Ta=-40 to +125°C, Load capacitance of output pin =15pF(max.)

| Parameter                                   | Symbol            | Condition | Min. | Тур. | Max. | Unit |

|---------------------------------------------|-------------------|-----------|------|------|------|------|

| SCK setup time from CSB falling edge        | tscks             | _         | 100  | _    | _    | ns   |

| SCK input enable time from CSB falling edge | t <sub>ESCK</sub> | _         | 100  | _    | _    | ns   |

| SCK hold time from CSB rising edge          | t <sub>CSH</sub>  | _         | 100  | _    | _    | ns   |

| Data floating time from CSB rising edge     | t <sub>DOZ</sub>  | RL=3KΩ    | _    | _    | 100  | ns   |

| Data setup time from SCK                    | t <sub>DIS</sub>  | _         | 50   | _    | _    | ns   |

| Data hold time from SCK                     | t <sub>DIH</sub>  | _         | 50   | _    | _    | ns   |

| Data output delay time from SCK             | t <sub>DOD</sub>  | _         | _    | _    | 90   | ns   |

| SCK "H" level pulse width                   | t <sub>SCKH</sub> | _         | 100  | _    | _    | ns   |

| SCK "L" level pulse width                   | t <sub>SCKL</sub> | _         | 100  | _    | _    | ns   |

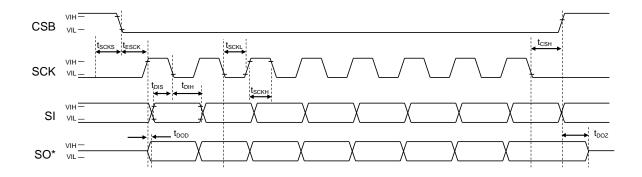

<sup>&</sup>lt;When rewriting the flash memory using the clock synchronous serial interface>

|                                             |                   |           | , <b>_</b> |      |      |      |

|---------------------------------------------|-------------------|-----------|------------|------|------|------|

| Parameter                                   | Symbol            | Condition | Min.       | Тур. | Max. | Unit |

| SCK setup time from CSB falling edge        | tscks             | _         | 125        |      | _    | ns   |

| SCK input enable time from CSB falling edge | tesck             | _         | 125        | _    | _    | ns   |

| SCK hold time from CSB rising edge          | t <sub>CSH</sub>  | _         | 125        | _    | _    | ns   |

| Data floating time from CSB rising edge     | t <sub>DOZ</sub>  | RL=3KΩ    | _          |      | 125  | ns   |

| Data setup time from SCK                    | t <sub>DIS</sub>  | _         | 50         | _    | _    | ns   |

| Data hold time from SCK                     | t <sub>DIH</sub>  | _         | 50         | _    | _    | ns   |

| Data output delay time from SCK             | t <sub>DOD</sub>  |           | _          | _    | 110  | ns   |

| SCK "H" level pulse width                   | tsckh             |           | 125        | _    | _    | ns   |

| SCK "L" level pulse width                   | t <sub>SCKL</sub> | _         | 125        | _    | _    | ns   |

ML22120

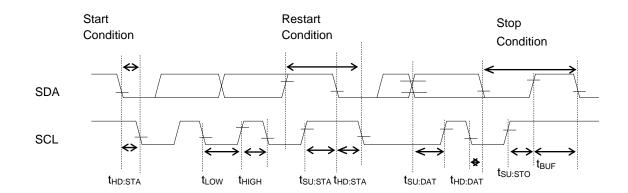

# • AC Characteristics (I<sup>2</sup>C Interface)

| Parameter                               | Symbol              | Min | Max. | Unit |

|-----------------------------------------|---------------------|-----|------|------|

| SCL clock frequency                     | t <sub>SCL</sub>    | 0   | 400  | kHz  |

| SCL hold time (start/restart condition) | t <sub>HD;STA</sub> | 0.6 | _    | μs   |

| SCL clock "L" level time                | t <sub>LOW</sub>    | 1.3 | _    | μs   |

| SCL clock "H" level time                | tніgн               | 0.6 | _    | μs   |

| SCL setup time (restart condition)      | t <sub>su;sta</sub> | 0.6 | _    | μs   |

| SDA hold time                           | t <sub>HD;DAT</sub> | 0   | _    | μs   |

| SDA setup time                          | t <sub>SU;DAT</sub> | 0.1 | _    | μs   |

| SDA setup time (stop condition)         | t <sub>su;sто</sub> | 0.6 | _    | μs   |

| Bus free time                           | t <sub>BUF</sub>    | 1.3 | _    | μs   |

| Capacitive load on each bus line        | Cb                  | _   | 400  | pF   |

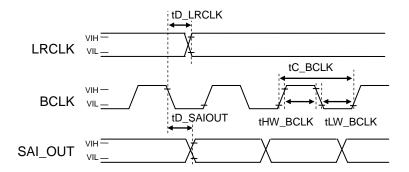

# • AC Characteristics (SAI Interface (Master))

| Parameter             | Symbol    | Condition | Min.  | Тур. | Max.  | Unit |

|-----------------------|-----------|-----------|-------|------|-------|------|

| SAI_BCLK period       | tC_BCLK   | _         | 32gfs | _    | 64gfs | Hz   |

| SAI_BCLK "H" period   | tHW_BCLK  |           | 146   | _    | _     | ns   |

| SAI_BCLK "L" period   | tLW_BCLK  | _         | 146   | _    | _     | ns   |

| SAI_LRCLK delay time  | tD_LRCLK  |           | _     | _    | 20    | ns   |

| SAI_SAIOUT delay time | tD_SAIOUT | _         | _     | _    | 20    | ns   |

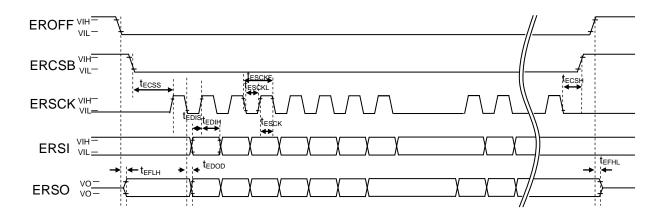

## • AC Characteristics (Flash Memory Interface)

$DV_{DD}$ = $IOV_{DD}$ =2.7 to 3.6V, DGND=0V, Ta=-40 to +125°C, Load capacitance of output pin =15pF(max.)

|                                                     | ,                  |           | ,     |        | tpat piio | p: (a,) |

|-----------------------------------------------------|--------------------|-----------|-------|--------|-----------|---------|

| Parameter                                           | Symbol             | Condition | Min.  | Тур.   | Max.      | Unit    |

| ERSCK enable time from ERCSB falling edge           | t <sub>ECSS</sub>  | _         | 50    | _      | _         | ns      |

| ERSCK hold time from ERCSB rising edge              | t <sub>ECSH</sub>  | _         | 50    | _      | _         | ns      |

| Data setup time from ERSCK rising edge              | t <sub>EDIS</sub>  | _         | 10    | _      | _         | ns      |

| Data hold time from ERSCK rising edge               | t <sub>EDIH</sub>  | _         | 10    | _      | _         | ns      |

| Data delay time from ERSCK falling edge             | t <sub>EDOD</sub>  | _         | _     | _      | 5         | ns      |

| ERSCK frequency                                     | tesckf             | _         | 1.228 | 16.384 | 17.20     | MHz     |

| ERSCK "H" level pulse width                         | t <sub>ESCKH</sub> | _         | 26    | _      | _         | ns      |

| ERSCK "L" level pulse width                         | t <sub>ESCKL</sub> | _         | 26    | _      | _         | ns      |

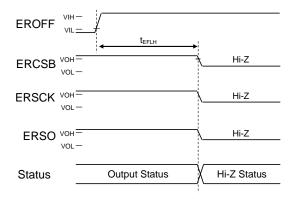

| ERCSB/ERSCK/ERSO delay time from EROFF rising edge  | t <sub>EFLH</sub>  | _         | _     | _      | 1         | ms      |

| ERCSB/ERSCK/ERSO delay time from EROFF falling edge | t <sub>EFHL</sub>  | _         | _     | _      | 1         | ms      |

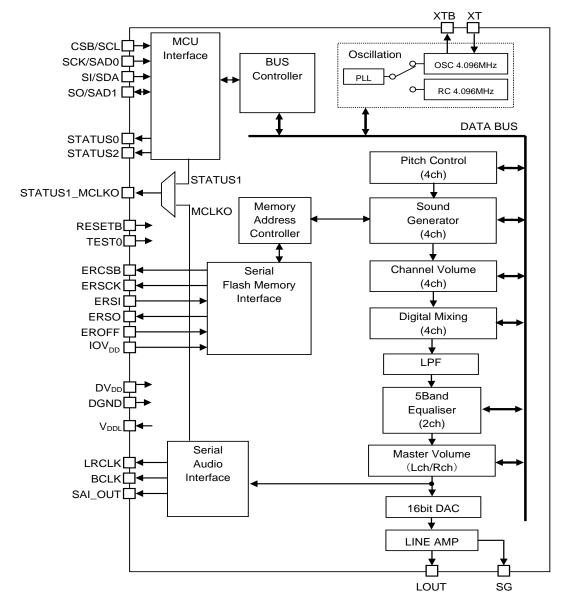

## ■ Block diagram

The block diagram is shown below.

### ■ Function description

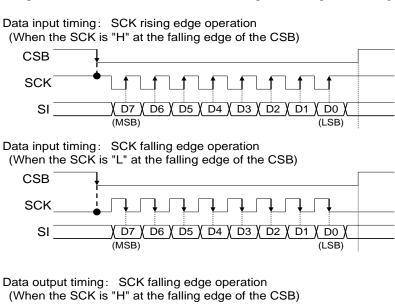

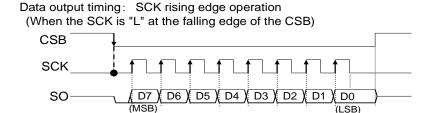

#### Clock Synchronous Serial Interface

Various registers are written and read by the CSB, SCK, SI, SO pins.

For data inputting, after "L" level is input to the CSB pin, data is input to the SI pin in MSB first in synchronization with the input clock signal of the SCK pin. The SI pin data is loaded into the LSI in synchronization with the SCK pin clock, and the input data is determined by the SCK pin clock of the eighth pulse.

Write access and read access to the register can be selected according to the MSB data when each register address is set.

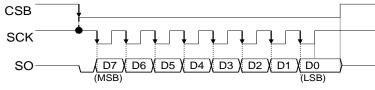

When the MSB of the address data is set to the "L" level, write access is performed, and the SI pin data is taken into the LSI as write data in synchronization with the SCK pin clock. If the MSB of the address data is set to "H" level, read access is performed and the data is output from the SO pin in synchronization with the SCK pin clock.

The address is automatically incremented while the CSB is at the "L" level, and data can be written and read continuously. The selection of the rising or falling edge of the SCK pin clock depends on the state of the SCK pin at the falling edge of the CSB pin.

When the SCK pin is "H" at the falling edge of the CSB pin, the SI pin data is loaded into the LSI on the rising edge of the SCK pin clock, and the status signal is output from the SO pin on the falling edge of the SCK pin clock.

When the SCK pin is "L" at the falling edge of the CSB pin, the SI pin data is loaded into the LSI on the falling edge of the SCK pin clock, and the status signal is output from the SO pin on the rising edge of the SCK pin clock.

The serial interface can be returned to the initial state by setting the CSB pin to "H" level.

When the CSB pin is "H" level or when read data isn't output, the SO pin is in a high impedance state.

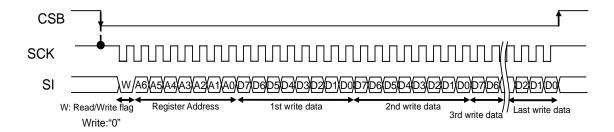

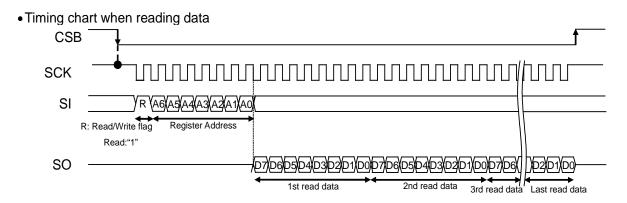

- One-time input mode

- Timing chart when writing data

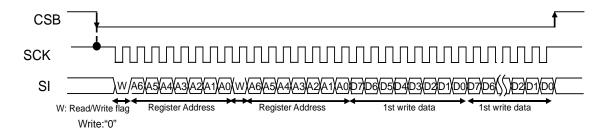

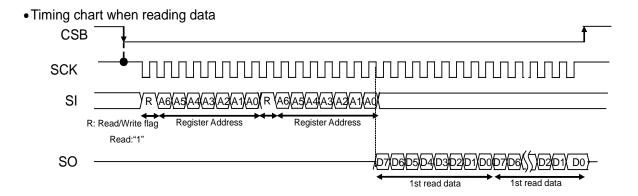

- Two-times input mode

- Timing chart when writing data

In the two-times input mode, if two-times input error is detected when reading a register, read data "1" is output.

### • I<sup>2</sup>C Interface (Slave)

This serial interface conforms to the I<sup>2</sup>C bus specifications. It supports Fast modes and can transmit and receive data at 400kbit/s. The SCL and SDA pins are used to write various register and to read the status. The slave addresses are set by the SAD 0 to 1 pins.

When I<sup>2</sup>C is used, be sure to connect a pull-up resistor between SCL and SDA pins and DV<sub>DD</sub> pin.

In the communication flow between the master and this device (slave) on the I<sup>2</sup>C bus, after the start condition is set, the slave address (upper 3 bits of the slave address are set by the SAD0 to 1 pins) is entered in the first 7 bits, the data direction is determined in the 8th bit (when the 8th bit is "0", data is written from the master, and data is read from the master when "1") and communication is performed in byte units thereafter. At this time, acknowledgment is required for each byte.

The reception operation supports auto-increment transfer and random access transfer, and the transmission operation supports auto-increment operation. Use the I<sup>2</sup>C access mode selection(I<sup>2</sup>CSEL) register to set auto-increment transfer and random access transfer. The flow of write operation and read operation is shown below.

## ◆ One-time input mode

Write operation (auto-increment transfer) SA[6:0] W RA[7:0] WD[7:0] WD[7:0] WD[7:0] Р Write operation (random access transfer) SA[6:0] RA[7:0] WD[7:0] W RA[7:0] WD[7:0] • Read operation (auto-increment transfer) SA[6:0] W Sr SA[6:0] Α RA[7:0] RD1[7:0] RD2[7:0] **Dummy Write** Current address read S: Start condition SA[6:0]: Slave address Read/Write flag Write="0" W: A: Acknowledge RA[7:0]: Register address in this LSI WD[7:0]: Write data Stop condition Sr: Restart condition R: Read/Write flag Read="1" RD1,2[7:0]: Read data Not-Acknowledge ~A: P: Stop condition From master to slave From slave to master

ML22120

## ◆ Two-times input mode

Write operation (random access transfer)

S SA[6:0] W A RA[7:0] A RA[7:0] A WD1[7:0] A WD1[7:0] P

\* Read operation (auto-increment transfer)

S SA[6:0] W A RA[7:0] A RA[7:0] A Sr SA[6:0] R A RD1[7:0] A RD1[7:0] ~A P

Dummy Write

Current address read

S: Start condition SA[6:0]: Slave address

W: Read/Write flag Write="0"

A: Acknowledge

RA[7:0]: Register address in this LSI

WD[7:0]: Write data P: Stop condition

Sr: Restart condition

R: Read/Write flag Read="1"

RD1[7:0]: Read data

~A: Not-Acknowledge

P: Stop condition

From master to slave

From slave to master

The slave address can be set as follows using the SAD1 to SAD0 pin.

| Highest | SAD1 | SAD0 | Lower 4 bits | Slave address |

|---------|------|------|--------------|---------------|

| 1       | 0    | 0    | 0101         | 100_0101      |

| 1       | 0    | 1    | 0101         | 101_0101      |

| 1       | 1    | 0    | 0101         | 110_0101      |

| 1       | 1    | 1    | 0101         | 111_0101      |

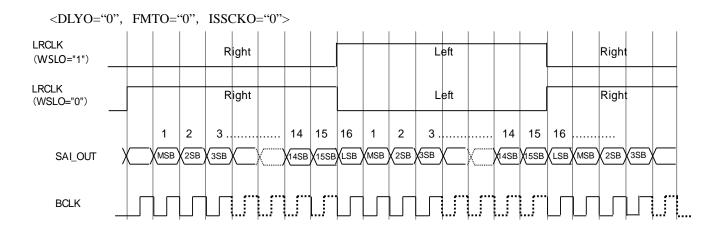

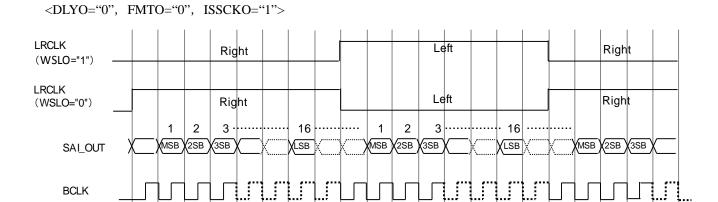

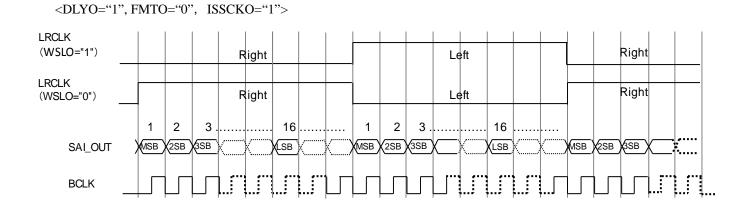

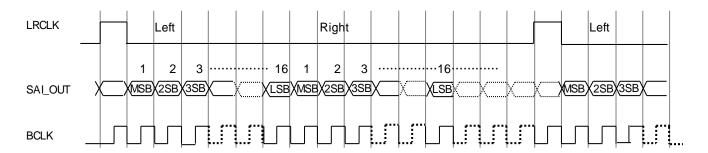

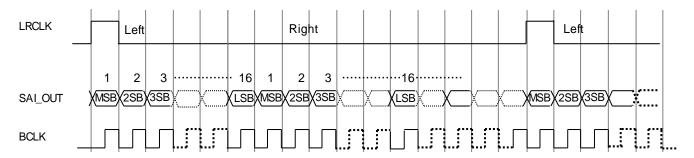

### SAI (Serial Audio Interface)

Various serial data formats are supported by a combination of register settings. A WSLO, DLYO and FMTO are used to represent the supported formats. For WSLO, DLYO and FMTO, refer to the "SAITCON register" in the "Registers" chapter.

<DLYO="0", FMTO="1", ISSCKO="1">

In frame synchronous transfer mode, Rch data follows immediately after Lch data.

<DLYO="1", FMTO="1", ISSCKO="1">

In frame synchronous transfer mode, Rch data follows immediately after Lch data.

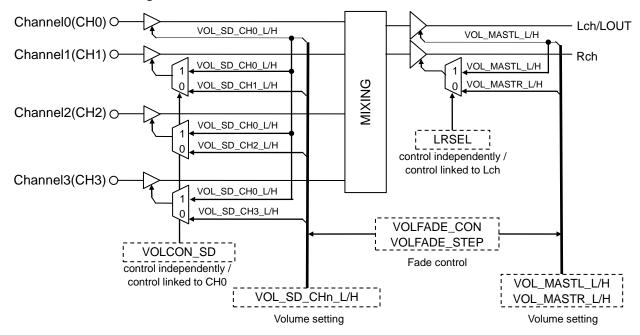

### Volume settings

For the SoundGenerator volume, set volume control independently / volume control linked to CH0 (initial value: volume control independently) of each channel by the VOLCON\_SD register. Set the volume of each channel by the VOL\_SD\_CHn\_L/H(n = 0 to 3) registers.

For the volume after mixing, set volume control independently / volume control linked to Lch (initial value: volume control independently) by the LRSEL register. The volume after mixing can be set by the VOL\_MASTL\_L/H register and VOL\_MASTR\_L/H register.

The combination of volume control for each channel is as follows.

—: Apply VOL\_SD\_CHn\_L / H (volume control independently)

∠: Apply VOL\_SD\_CH0\_L / H (volume control linked to CH0)

| VOLCON_SD register             |     | Volume control |     |

|--------------------------------|-----|----------------|-----|

| VOLEN_SD_<br>CHn bit(n=1 to 3) | СНЗ | CH2            | CH1 |

| 000(Initial value)             | _   |                |     |

| 001                            | _   |                | レ   |

| 010                            | _   | レ              | _   |

| 011                            | _   | レ              | レ   |

| 100                            | レ   |                |     |

| 101                            | レ   |                | レ   |

| 110                            | レ   | レ              | _   |

| 111                            | レ   | V              | レ   |

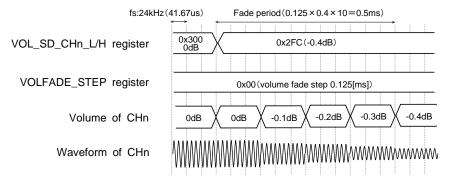

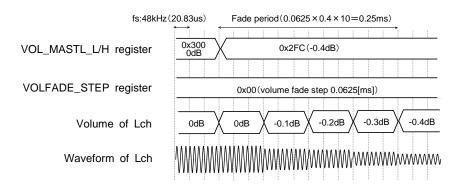

Furthermore, by enabling fade when changing the volume in the VOLFADE\_CON register, the volume transition time can be adjusted in the fade step set in the VOLFADE\_STEP register. The volume changes every 0.1 dB.

Volume fade is effective when changing the volume of each channel using the VOL\_SD\_CHn\_L/H(n = 0 to 3) registers, or when changing the VOL\_MASTL\_L/H register and VOL\_MASTR\_L/H register.

When changing the volume of each channel in the VOL\_SD\_CHn\_L/H(n = 0 to 3) registers>

• When playing sound code data of fs = 24kHz

The volume transitions according to the sampling frequency (fs). If sound code data of different fs is being played at the same time, the volume transition time will be different. For the volume transition time, refer "VOLFADE\_STEP register" in the "Registers" chapter.

< When changing the volume by the VOL\_MASTL\_L/H register and VOL\_MASTR\_L/H register >

• GFS bit = 0 (OUTMODE register).

The volume transitions at 48kHz or 32kHz depending on the GFS bit of the OUTMODE register. For the volume transition time, refer "VOLFADE\_STEP register" in the "Registers" chapter.

ML22<u>120</u>

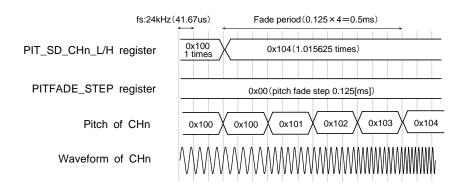

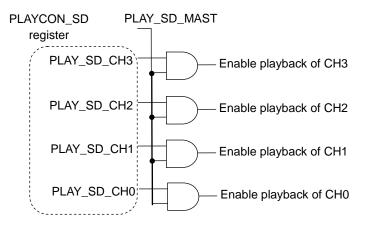

## Pitch settings

SoundGenerator can play while changing the pitch (playback speed).

The pitch magnification of CH 0 to 1 can be set from 0.0625 times to 3.9960938 times in 0.00390625 times steps. The pitch magnification of CH 2 to 3 can be set from 0.0625 times to 1 time in 0.00390625 times steps. For the pitch of the SoundGenerator, set pitch control independently / pitch control linked to CH0 (initial value:pitch control independently) by the PITCHCON\_SD register.

The combinations of pitch for each channel are as follows.

—: Apply PIT\_SD\_CH1\_L / H (pitch control independently)

∠: Apply PIT\_SD\_CH0\_L / H (pitch control linked to CH0)

| PITCHCON_SD register | Pitch control |

|----------------------|---------------|

| PITCHEN_SD_CH1 bit   | CH1           |

| 0                    | _             |

| 1                    | レ             |

Furthermore, by enabling fade when changing the pitch in the PITFADE\_CON register, the pitch can be adjusted step by step in the pitch step set in the PITFADE\_STEP register.

Memory allocation and creating sound data

The sound code data stored in the serial flash memory consists of sound (i.e., phrase) control area, test area, and sound area. The sound control area manages the sound data in the Memory. It contains data for controlling sound data for 64 phrases. The sound area contains actual waveform data.

The Sound data is created using a dedicated tool (Speech LSI Utility).

### Configuration of Serial Flash Memory Data (128Mbits)

| 0x00000  |                    |

|----------|--------------------|

|          | Test area          |

| 0x0007F  |                    |

| 0x00080  |                    |

|          | Sound control area |

| 0x0207F  |                    |

| 0x02080  |                    |

|          |                    |

|          |                    |

|          | Sound area         |

|          |                    |

|          |                    |

|          |                    |

|          |                    |

|          |                    |

|          |                    |

|          |                    |

|          |                    |

| 0xFFFFFF |                    |

Playback time and memory capacity

The playback time depends on memory capacity and sampling frequency. The relationship is shown below.

$$Playback \ Time = \frac{1.024 \times (Memory \ Capacity \ (kbit)-65)}{Sampling \ frequency \ (kHz) \times bit \ length} \tag{sec}$$

When sound data with a sampling frequency of 48 kHz is registered in the 4Mbit serial flash memory, the playback time will be approximately 5.37 seconds.

Playback Time =

$$\frac{1.024 \times (4096 \text{(kbit)- 65})}{48 \text{ (kHz)} \times 16 \text{ (bit)}} \ \ \ \ \ \ \ \ \ \ \ 5.37 \text{(sec)}$$

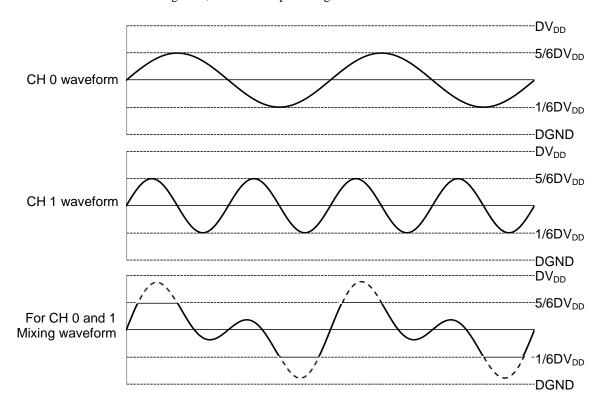

## Waveform clamp precautions for mixing

When mixing, the clamp may be generated as shown in the figure below due to the calculation of the synthesis. If the clamp is known to be generated in advance, adjust the volume of each channel with the volume control register. For details on volume control registers, refer the chapter "Registers".

If the result of mixing CH 0 and 1 exceeds from the  $1/6{\rm DV_{DD}}$  to  $5/6{\rm DV_{DD}}$  level (as indicated by the broken line), the sound quality may be reduced by clamping.

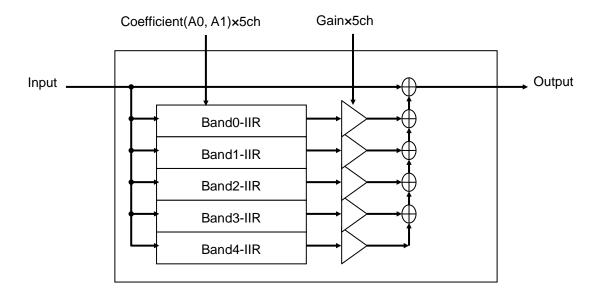

### 5Band equalizer

The 5Band equalizer consists of a second-order IIR type Band Pass Filter. It is equipped with Lch (EQL) and Rch (EQR). The center frequency and band width of each band can be set arbitrarily. ON / OFF can be set by setting the EQLCON register and EQRCON register. The settings are as follows.

A0 =  $(1-\tan\pi fb / fs) / (1 + \tan\pi fb / fs)$ A1 =  $(-2\cos 2\pi f0 / fs) / (1 + \tan\pi fb / fs)$

f0: Center frequency of the band [Hz]

fb: -3dB bandwidth [Hz] fs: sampling frequency [Hz]

For the actual register value, multiply the result of the above formula by  $2^{14}$  and use the integer value rounded to the nearest whole number.

For details on Coefficient (A0, A1) and Gain, refer "Equalizer related registers" in the "Registers" chapter.

The equalizer can be adjusted using the dedicated tool (Speech LSI Utility). Set the value generated by the Speech LSI Utility in the "Equalizer related registers".

#### Error detection function

It has a built-in error detection function, and the presence or absence of error detection can be read from the ERROR register. The presence or absence of error detection can be output to the STATUS0 pin (set by the OUTSTAT0\_0 to 5 registers), the STATUS1\_MCLKO pin (set by the OUTSTAT1\_0 to 5 registers), and the STATUS2 pin (set by the OUTSTAT2 register). For details on the ERROR register, OUTSTAT0\_0 to 5 registers, OUTSTAT1\_0 to 5 registers, OUTSTAT1\_0 to 5 registers, refer the chapter "Registers".

The error detection is shown below.

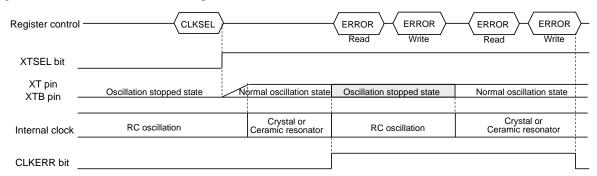

◆ Detects the stop of clock input from a crystal resonator or ceramic resonator.

When oscillation stop is detected with the XTSEL bit of the CLKSEL register set to "1", the CLKERR bit becomes "1". At the same time, the clock backup function starts and automatically switches to the RC oscillation circuit (4.096MHz). The CLKERR bit can be read from the ERROR register. The CLKERR bit can be cleared by writing to the ERROR register. However, if the oscillation stop continues, the CLKERR bit continues to be "1".

For details on the ERROR register and CLKSEL register, refer the chapter "Registers".

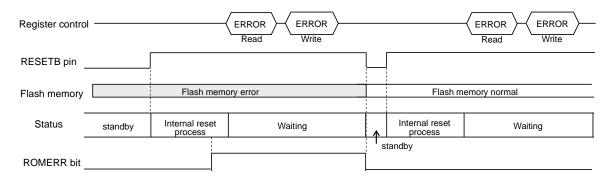

#### Flash memory error detection

When the RESETB pin is set to the "L"  $\rightarrow$  "H" level, the flash memory is read during the internal reset process. If an error is detected in the read data of the flash memory, the ROMERR bit becomes "1". In this case, initialize this LSI by resetting with the RESETB pin.

The ROMERR bit can be read from the ERROR register. The ROMERR bit is not cleared even if writing to the ERROR register.

For details on the ERROR register, refer the chapter "Registers".

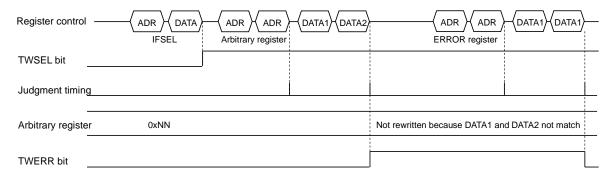

### ◆ Two-times input error detection

In order to prevent malfunction due to noise of the serial interface pin, it is equipped with a function to input address and data twice each. Setting the TWSEL bit of the IFSEL register to "1" shifts to the two-times input mode.

In the two-times input mode, the address and data is input two-times in succession, and it is valid only when the input data matches. If a mismatch occurs during the second data input after the first data input, the TWERR bit is set to "1", and the address or data entered is ignored.

The TWERR bit can be read from the ERROR register. The TWERR bit can be cleared by writing to the ERROR register.

For details on the ERROR register and IFSEL register, refer the chapter "Registers".

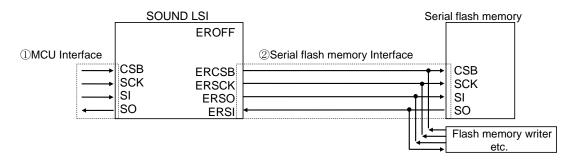

Serial flash memory rewrite function

The serial flash memory can be rewritten in the following two ways.

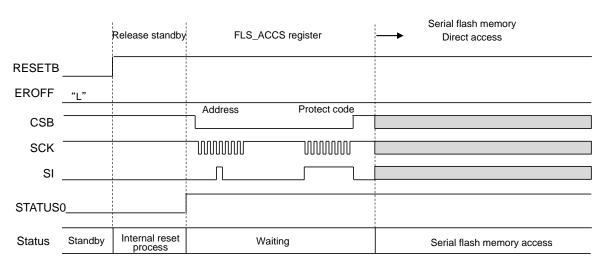

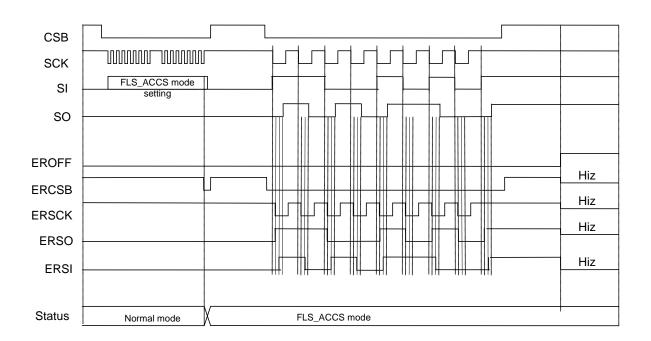

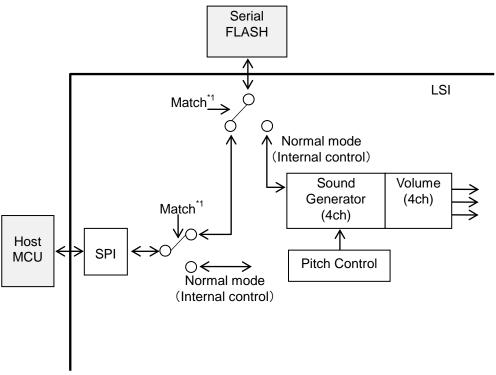

① Rewrite using the clock synchronous serial interface of the MCU interface

By using the CSB, SCK, SI and SO pins, which are clock synchronous serial interfaces of the MCU interface

the serial flash memory can be rewritten. When the protect code written in the FLS\_ACCS register matches the information

stored in the flash memory, direct access to the serial flash memory is enabled from the CSB, SCK, SI and SO pins.

For details on the FLS\_ACCS register, refer the chapter "Registers".

② Rewrite using serial flash memory interface without this LSI

The serial flash memory can be rewritten using the ERCSB, ERSCK, ERSI and ERSO pins that is the serial flash memory interface.

When the EROFF pin set to "H", the serial flash memory can be rewritten using the ERCSB, ERSCK, ERSI and ERSO pins without this LSI. (ERCSB, ERSCK and ERSO pins are in a condition of high-impedance.)

- Timing chart

- Common

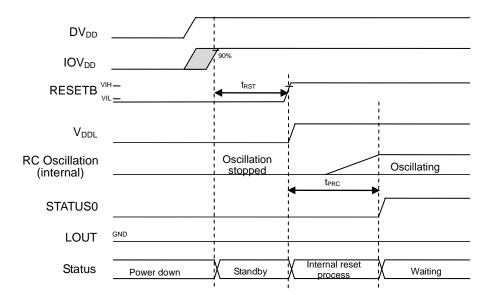

- ◆ Power-on timing

When turning on the power, enter "L" in the RESETB pin.

While the RESETB pin is at L level, it is in standby mode.

Start up in the order of  $DV_{DD}$  and  $IOV_{DD}$ . The  $DV_{DD}$  and  $IOV_{DD}$  can also start up at the same time.

After the reset is released (RESETB is at  $L \rightarrow H$  level), it goes through internal reset processing and becomes waiting status (oscillating).

Access the register after t<sub>PRC</sub> has elapsed or after the STATUS0 pin has become "H".

Be sure to enter "L" at the RESETB pin when the DV<sub>DD</sub> is below the (recommended) operating voltage range.

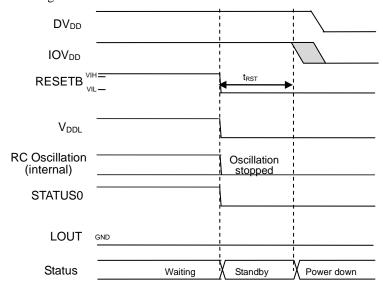

#### Power-off timing

When turning off the power, enter "L" in the RESETB pin.

Shut down in the order of  $IOV_{DD}$  and  $DV_{DD}$ . The  $DV_{DD}$  and  $IOV_{DD}$  can also shut down at the same time.

Be sure to enter "L" at the RESETB pin when the  $DV_{DD}$  is below the (recommended) operating voltage range.

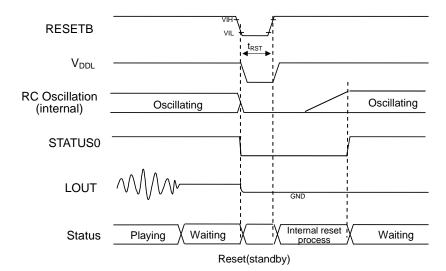

## ◆ Reset input timing

◆ SAI interface timing (master)

MCLKO is synchronized with BCLK.

◆ Serial flash memory interface timing

- Clock synchronous serial

- ◆ Clock Synchronous Serial Interface Timing (SCK Initial Value = "H" Level)

◆ Clock Synchronous Serial Interface Timing (SCK Initial Value = "L" Level)

<sup>\*</sup> Outputs "H" or "L" to the SO pin only when reading.

At the time of writing, the SO pin is in a high impedance state.

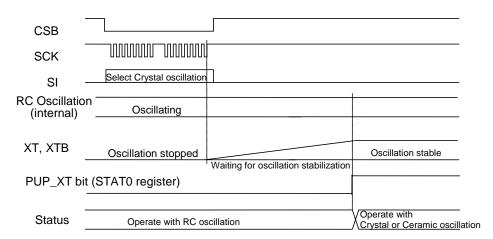

◆ Crystal oscillation switching timing

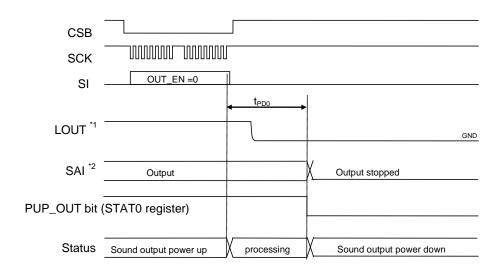

◆ Sound output power-up timing (pop noise countermeasure bit POP ="1")

- \*1 If playback from the LINE amplifier is not selected in OUT\_MD [1: 0] of the OUTMODE register, it is fixed to GND.

- \*2 If playback from the SAI pin is not selected in OUT\_MD [1: 0] of the OUTMODE register, not output to the SAI pin (BCLK / LRCLK / SAI\_OUT / STATUS1\_MCLKO).

- ◆ Sound output power-up timing (pop noise countermeasure bit POP = "0")

<sup>\*1</sup> If playback from the LINE amplifier is not selected in OUT\_MD [1: 0] of the OUTMODE register, it is fixed to GND.

<sup>\*2</sup> If playback from the SAI pin is not selected in OUT\_MD [1: 0] of the OUTMODE register, not output to the SAI pin (BCLK / LRCLK / SAI\_OUT / STATUS1\_MCLKO).

◆ Sound output power-down timing (pop noise countermeasure bit POP ="1")

- \*1 If playback from the LINE amplifier is not selected in OUT\_MD [1: 0] of the OUTMODE register, it is fixed to GND.

- \*2 If playback from the SAI pin is not selected in OUT\_MD [1: 0] of the OUTMODE register, not output to the SAI pin (BCLK / LRCLK / SAI\_OUT / STATUS1\_MCLKO).

- ◆ Sound output power-down timing (pop noise countermeasure bit POP = "0")

<sup>\*1</sup> If playback from the LINE amplifier is not selected in OUT\_MD [1: 0] of the OUTMODE register, it is fixed to GND.

<sup>\*2</sup> If playback from the SAI pin is not selected in OUT\_MD [1: 0] of the OUTMODE register, not output to the SAI pin (BCLK / LRCLK / SAI\_OUT / STATUS1\_MCLKO).

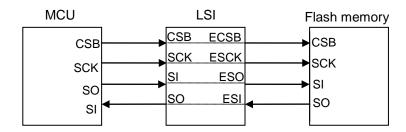

### Flash memory access flow

When FLS\_ACCS mode is set, the pins are directly connected inside the LSI as shown below. When the EROFF pin is set to H level, the ERCSB, ERSCK, ERSO and ERSI pins are in the HiZ(high-impedance) state.

| Symbol | I/O | Symbol to be | I/O           |         |

|--------|-----|--------------|---------------|---------|

|        |     | connected    | EROFF=L       | EROFF=H |

| CSB    | ı   | ERCSB        | 0             | HiZ     |

| SCK    | ı   | ERSCK        | 0             | HiZ     |

| SI     | ı   | ERSO         | 0             | HiZ     |

| SO     | 0   | ERSI         | I (Pull Down) | HiZ     |

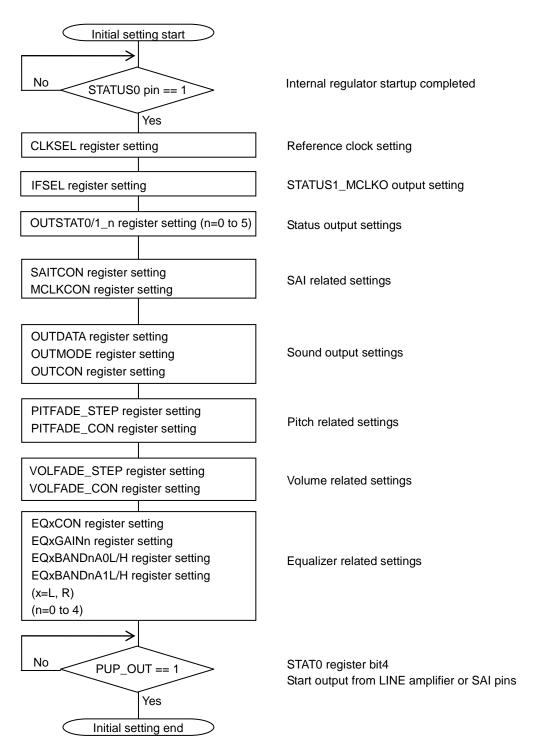

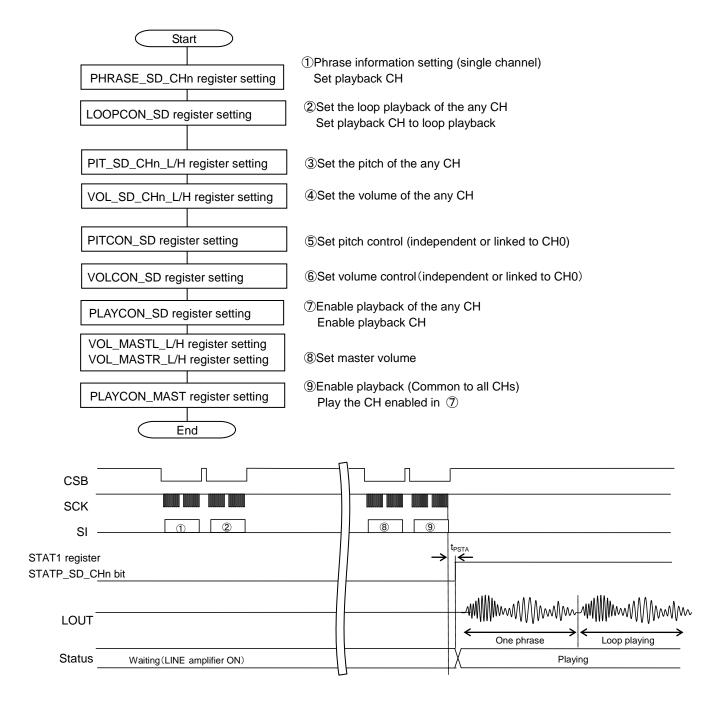

### SoundGenerator initial setting flow

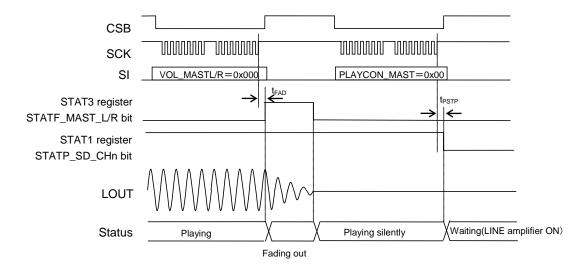

◆ SoundGenerator playback flow (Single channel / with loop)

- SoundGenerator can select once playback or loop playback depending on the presence or absence of loop setting. To end loop playback, release the loop setting and wait for the phrase to end before ending playback. If want to end the playback immediately, disable the any CH.

- If phrases with different sampling frequencies are started playing on different channels at the same time, there may be a gap between the channels during a loop depending on the sound code data length.

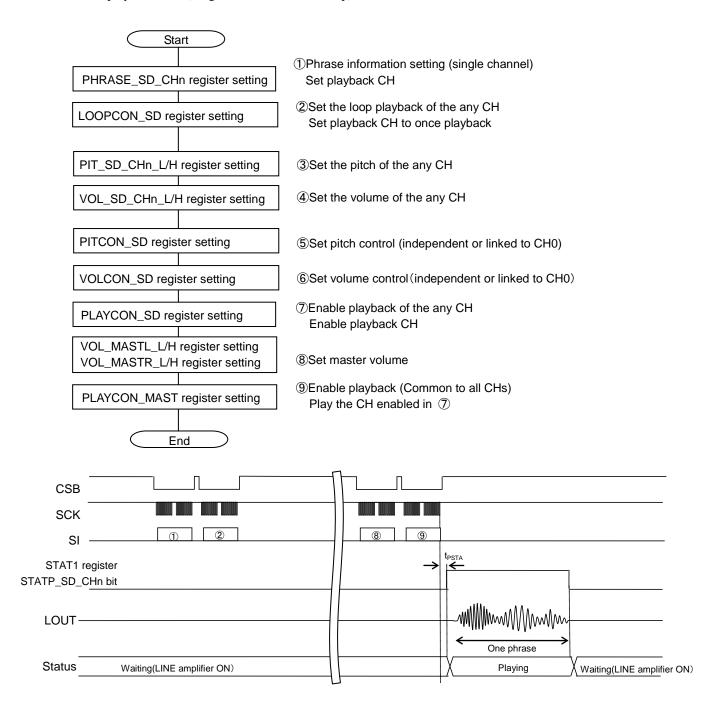

◆ SoundGenerator playback flow (Single channel / without loop)

SoundGenerator can select once playback or loop playback depending on the presence or absence of loop setting. When playing once, the playback ends at the same time as the phrase ends.

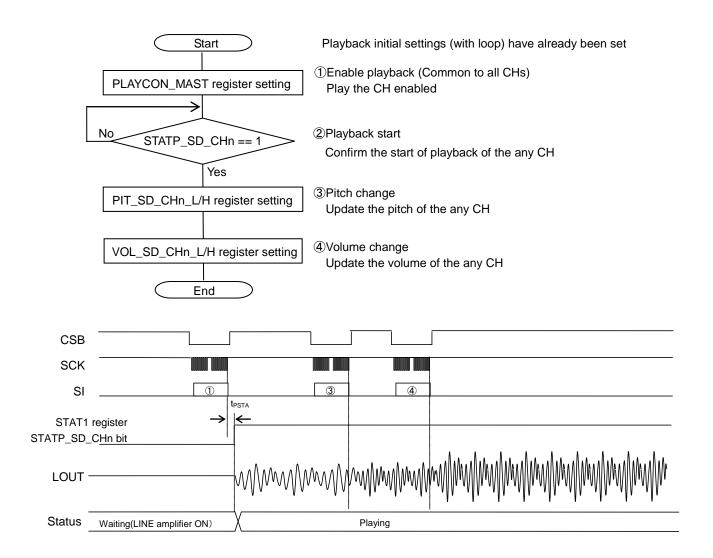

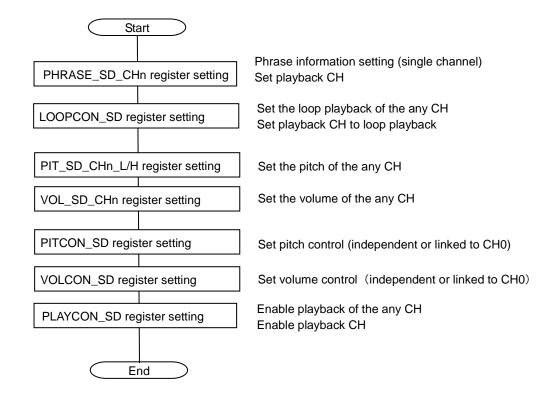

◆ SoundGenerator pitch / volume change flow during playback

The pitch and volume can be changed during playback.

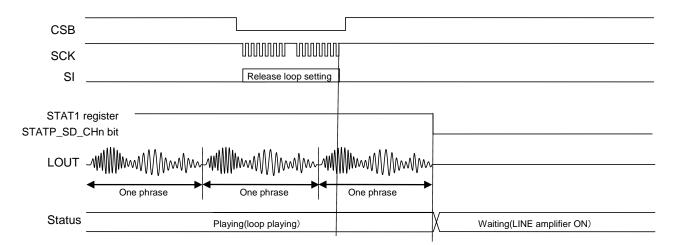

◆ SoundGenerator loop playback release timing

Loop playback is stopped at the end of the phrase.

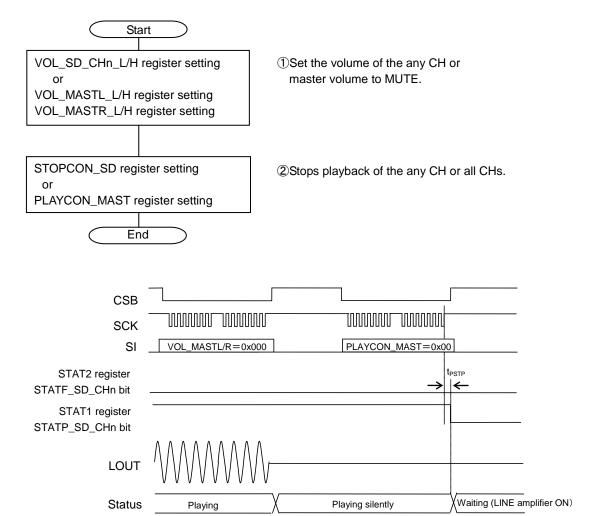

Playback end timing (without fade)

- To stop the playback of multiple channels, set the volume (VOL\_SD\_CHn) of the any CH to MUTE. To stop playback of all channels, set the master volume (VOL\_MASTL L/H, VOL\_MASTR L/H) to MUTE.

- To stop playback when playing a single channel, set the master volume (VOL\_MASTL\_L/H, VOL\_MASTR\_L/H) to MUTE.

- To restart playback after stopping playback in the PLAYCON\_MAST register, refer to the SoundGenerator playback flow.

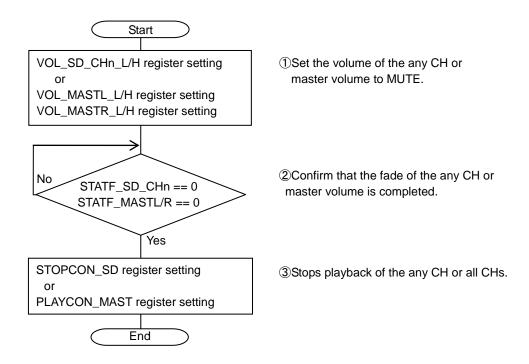

### ◆ Playback end timing (with fade)

- To stop the playback of multiple channels, set the volume (VOL\_SD\_CHn) of the any CH to MUTE. To stop playback of all channels, set the master volume (VOL\_MASTL\_L/H, VOL\_MASTR\_ L/H) to MUTE.

- To stop playback when playing a single channel, set the master volume (VOL\_MASTL\_L/H, VOL\_MASTR\_L/H) to MUTE.

- To restart playback after stopping playback in the PLAYCON\_MAST register, refer to the SoundGenerator playback flow.

- SoundGenerator CH additional playback flow

- When playing a CH that is not playing while playing any CH (When playing the stopped CH after stopping the playback of only some CHs with the STOPCON\_SD register while playing multiple CHs.)

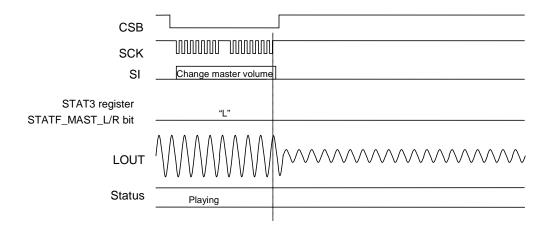

♦ Volume change timing (all CHs) (without fade)

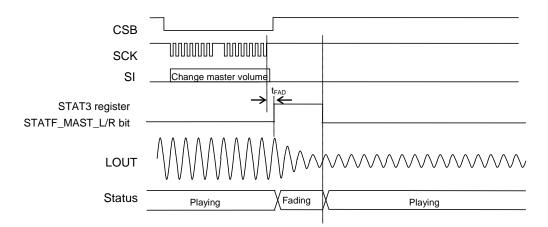

◆ Volume change timing (all CHs) (with fade)

\*1 For the volume transition time, refer " VOLFADE\_STEP register" in the registers.

- I<sup>2</sup>C Interface (Slave)

- ◆ I<sup>2</sup>C Interface Timing

### ■ Registers

### Register bank list

Registers are arranged in banks for each function.

Banks are switched using the BANKSEL register, which is a register common to all banks.

| BANKSEL register [3:0] | Select registers section          |

|------------------------|-----------------------------------|

| 0x0                    | SoundGenerator0 related registers |

| 0x1                    | SoundGenerator1 related registers |

| 0x2                    | EqualizerLch related registers    |

| 0x3                    | EqualizerRch related registers    |

| 0x4-0xF                | Setting prohibited                |

Check the following pages for the registers of each bank.

Writing to banks and addresses not listed is prohibited. Write the initial value to the unused bit of each register.

### Registers list

◆ All banks common registers list (BANKSEL[3:0]= 0x0, 0x1, 0x2, 0x3)

The address space from 0x00 to 0x3F is common to all banks and can be accessed from any bank.

Writing to addresses not listed is prohibited. Write the initial value to the unused bit of each register.

| Address   | Register name       | Functions                                          | R/W |

|-----------|---------------------|----------------------------------------------------|-----|

| 0x00      | BANKSEL             | Access bank selection                              | R/W |

| 0x01      | CLKSEL              | Reference clock selection                          | R/W |

| 0x02      | I <sup>2</sup> CSEL | I <sup>2</sup> C access mode selection             | R/W |