## dsPIC33CDVL64MC106 FAMILY

## 16-Bit Digital Signal Controllers with High-Resolution PWM, Op Amps, Advanced Analog, MOSFET Driver and LIN Transceiver

#### **Operating Conditions**

- 3.0V to 3.6V: -40°C to +125°C, DC to 100 MIPS

- 3.0V to 3.6V: -40°C to +150°C, DC to 70 MIPS

## High-Performance 16-Bit DSP RISC CPU

- 16-Bit Wide Data Path

- · Code Efficient (C and Assembly) Architecture

- 40-Bit Wide Accumulators

- Single-Cycle (MAC/MPY) with Dual Data Fetch

- Single-Cycle, Mixed-Sign Multiply:

- 32-bit multiply support

- · Fast Six-Cycle Divide

- Zero Overhead Looping

## **High-Resolution PWM**

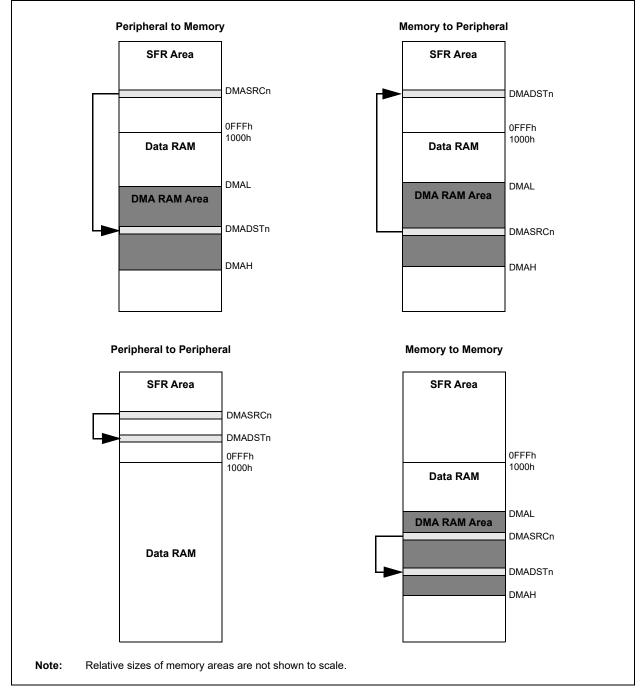

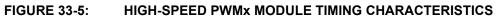

- · Four PWM Pairs

- Up to 2 ns PWM Resolution

- · Dead Time for Rising and Falling Edges

- Dead-Time Compensation

- Clock Chopping for High-Frequency Operation

- PWM Support for:

- DC/DC, AC/DC, inverters, PFC, lighting

- BLDC, PMSM, ACIM, SRM motors

- · Fault and Current Limit Inputs

- Flexible Trigger Configuration for ADC Triggering

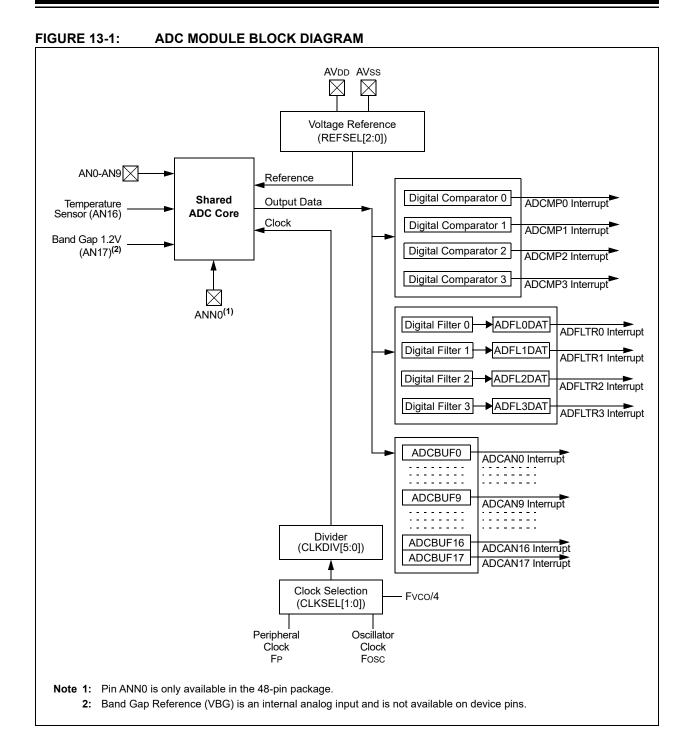

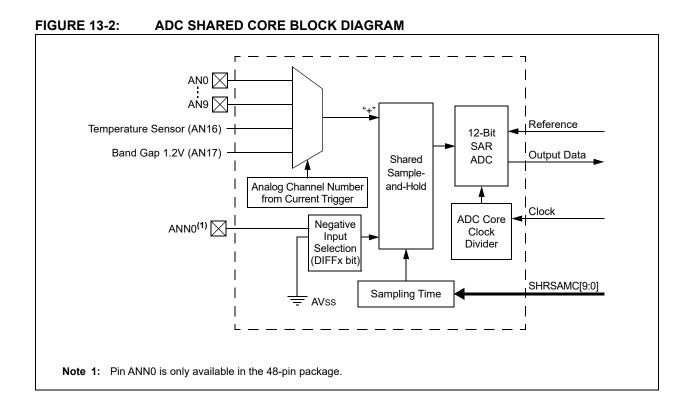

#### High-Speed Analog-to-Digital Converter

- Up to 15 A/D inputs

- 12-Bit Resolution

- One Shared SAR ADC Core

- Up to 3.5 Msps Conversion Rate per Core

- · Dedicated Result Buffer for Each Analog Channel

- · Flexible and Independent ADC Trigger Sources

- · Four Digital Comparators

- Four Oversampling Filters

#### **Microcontroller Features**

- · High-Current I/O Sink/Source

- Edge or Level Change Notification Interrupt on I/O

Pins

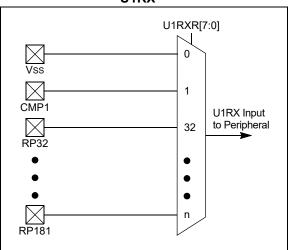

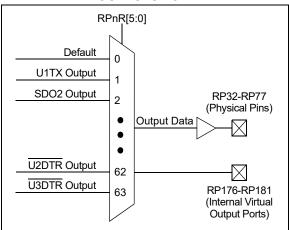

- · Peripheral Pin Select (PPS) Remappable Pins

- Up to 64 Kbytes Flash Memory:

- 10,000 erase/write cycle endurance

- 20 years minimum data retention

- Self-programmable under software control

- Programmable code protection

- Error Code Correction (ECC)

- Flash OTP by ICSP™ Write Inhibit

- Eight Kbytes SRAM Memory:

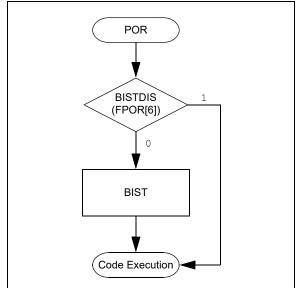

SRAM Memory Built-In Self-Test (MBIST)

- Multiple Interrupt Vectors with Individually Programmable Priority

- Four Sets of Interrupt Context Saving Registers which Include Accumulator and STATUS for Fast Reserved Interrupt Handling

- · Four External Interrupt Pins

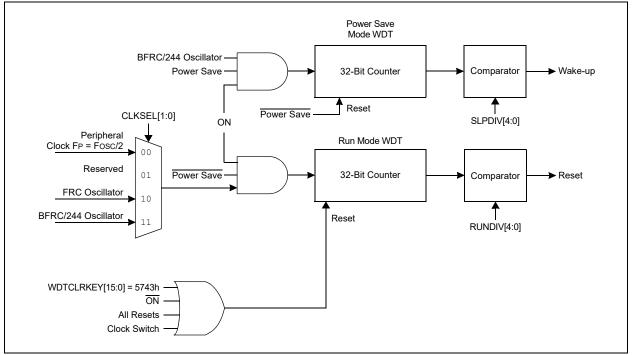

- Watchdog Timer (WDT)

- Windowed Deadman Timer (DMT)

- Fail-Safe Clock Monitor (FSCM) with Dedicated Oscillator

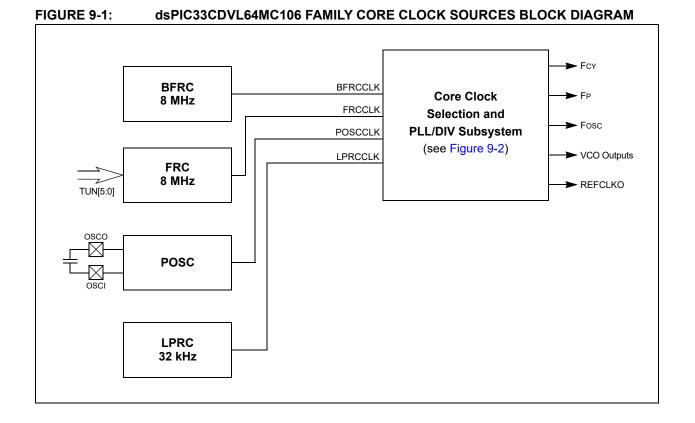

- Selectable Oscillator Options Including:

- High-precision, 8 MHz internal Fast RC (FRC) Oscillator

- Primary high-speed, crystal/resonator oscillator or external clock

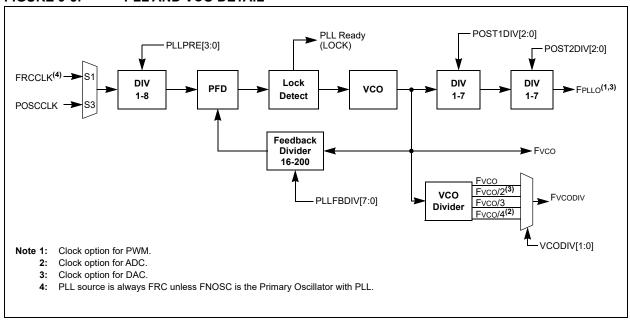

- Primary PLL, which can be clocked from FRC or crystal oscillator

- Low-Power Management modes (Sleep and Idle)

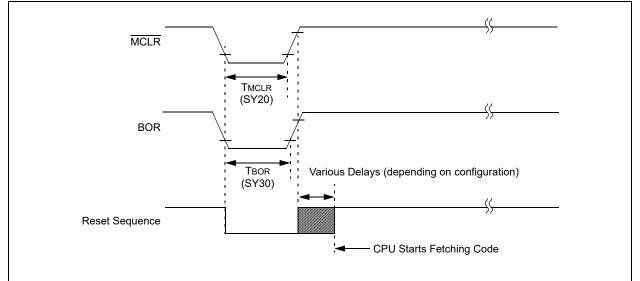

- · Power-on Reset and Brown-out Reset

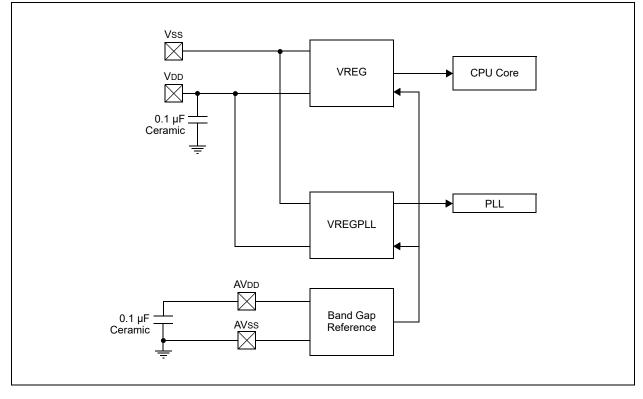

- · On-Board Capacitorless Regulator

- 384 Bytes of One-Time-Programmable (OTP) Memory

## **Peripheral Features**

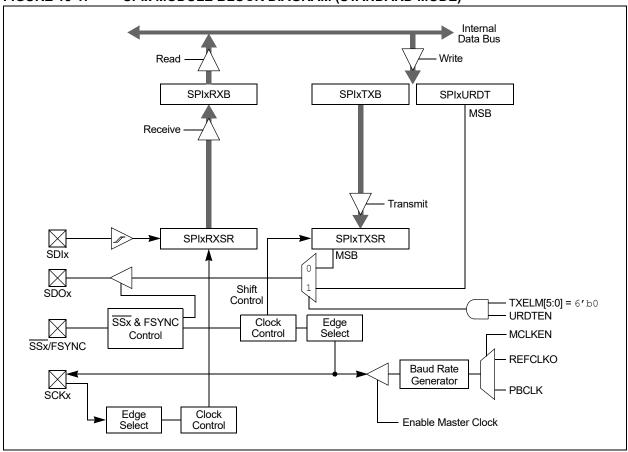

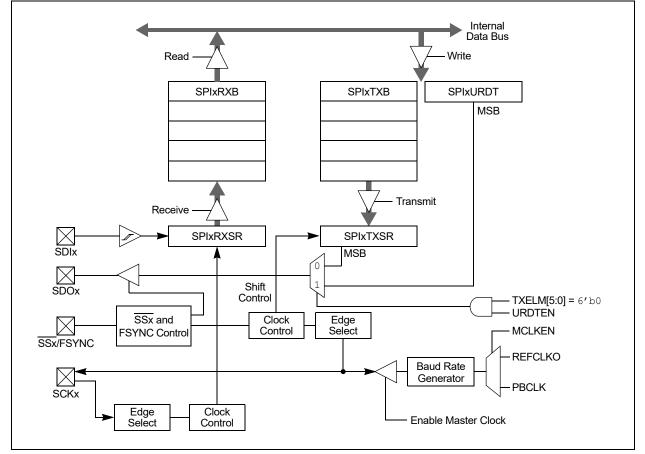

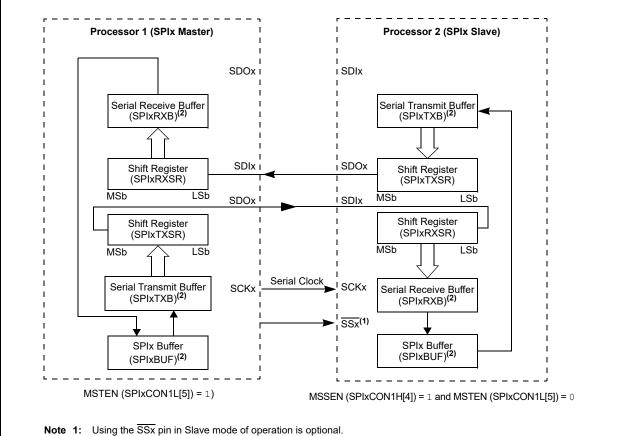

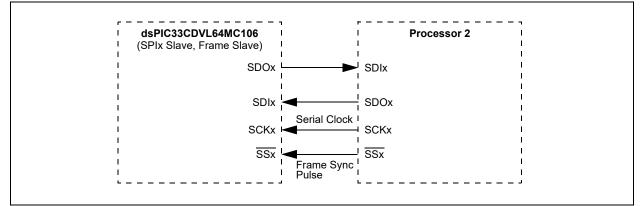

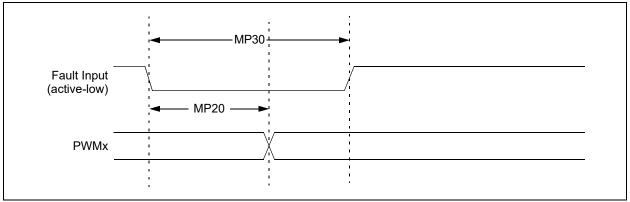

- Two Four-Wire SPI modules (up to 50 Mbps):

- 16-byte FIFO

- Variable width

- I2S mode

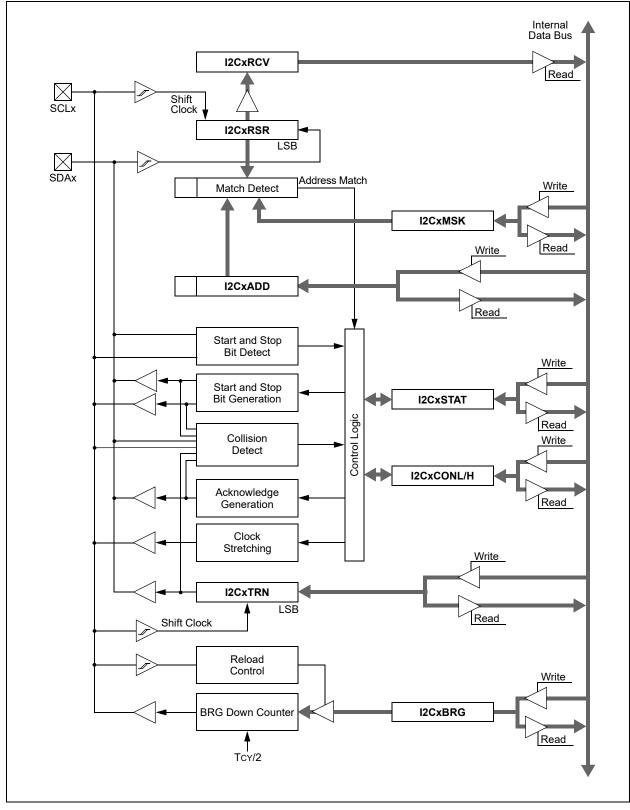

- One I2C Host and Client w/Address Masking and IPMI Support

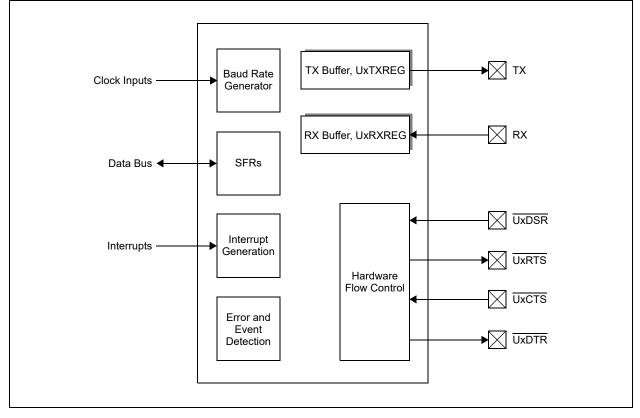

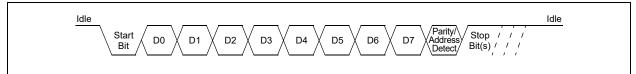

- Three Protocol UARTs with Automated Handling Support for:

- LIN 2.2

- DMX

- Smart card (ISO 7816)

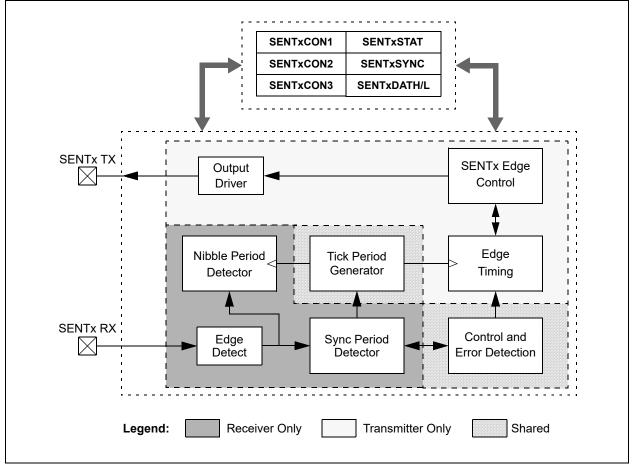

- One SENT module

- Timers/Counters:

- One dedicated 16-bit timer/counter

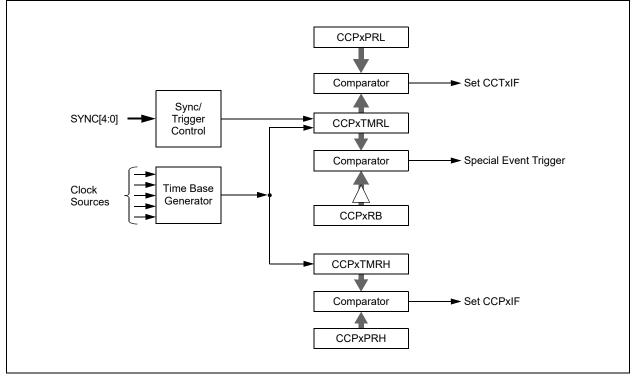

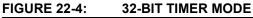

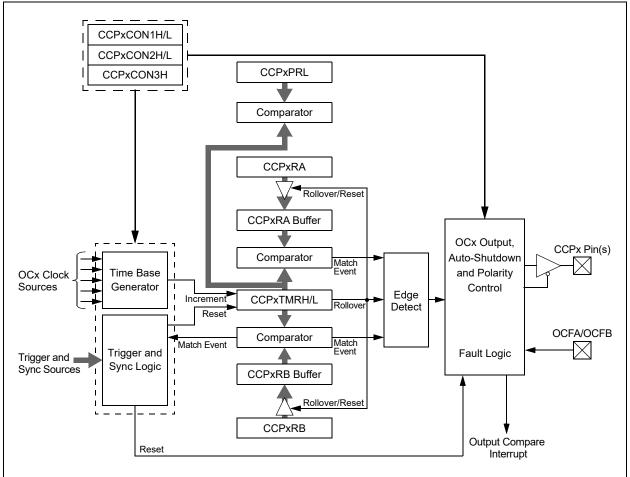

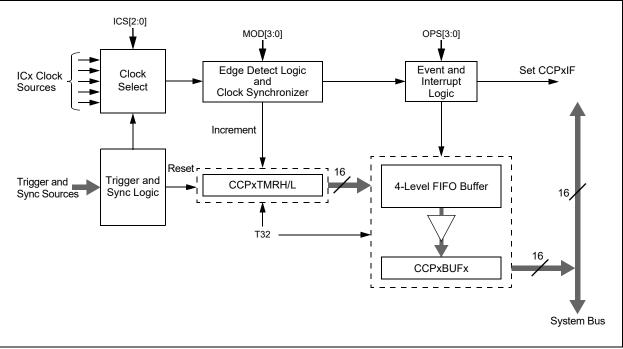

- Four Single Output Capture/Compare/PWM/ Timer (SCCP) modules:

- Flexible configuration as PWM, input capture, output compare or timers

- Two 16-bit timers or one 32-bit timer in each module

- PWM resolution down to 2.5 ns

- Single PWM output

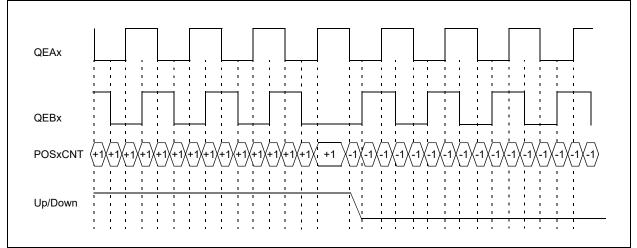

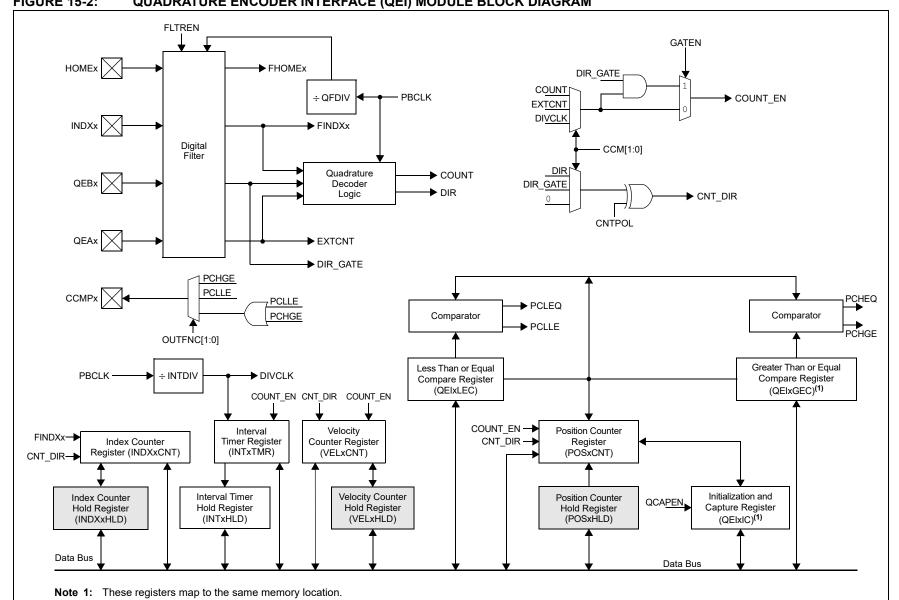

- One Quadrature Encoder Interface (QEI):

- Four inputs: Phase A, Phase B, Home, Index

- One 32-bit timer/counter (in QEI module,

- available if encoder is not used)

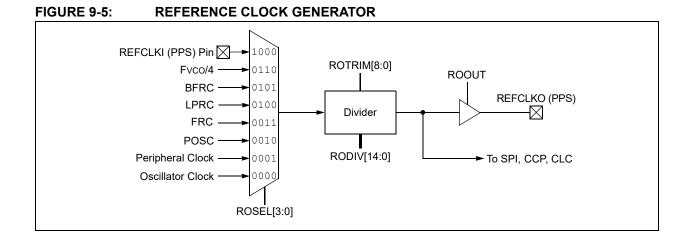

- Reference Clock Output (REFCLKO)

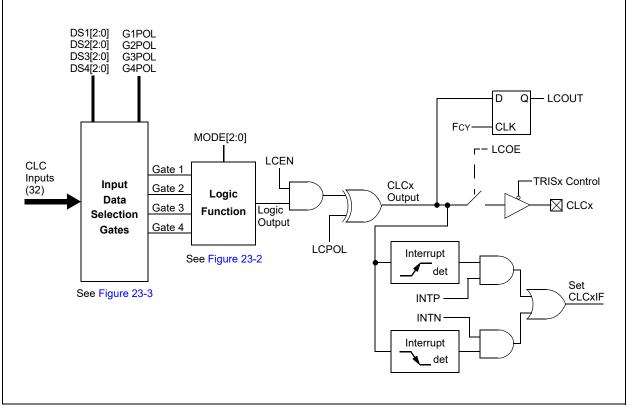

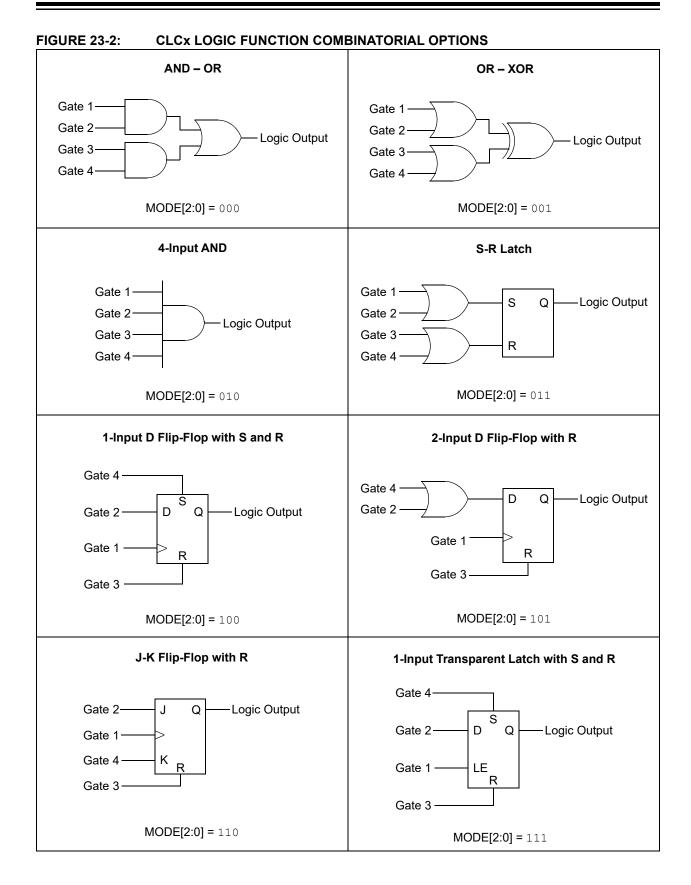

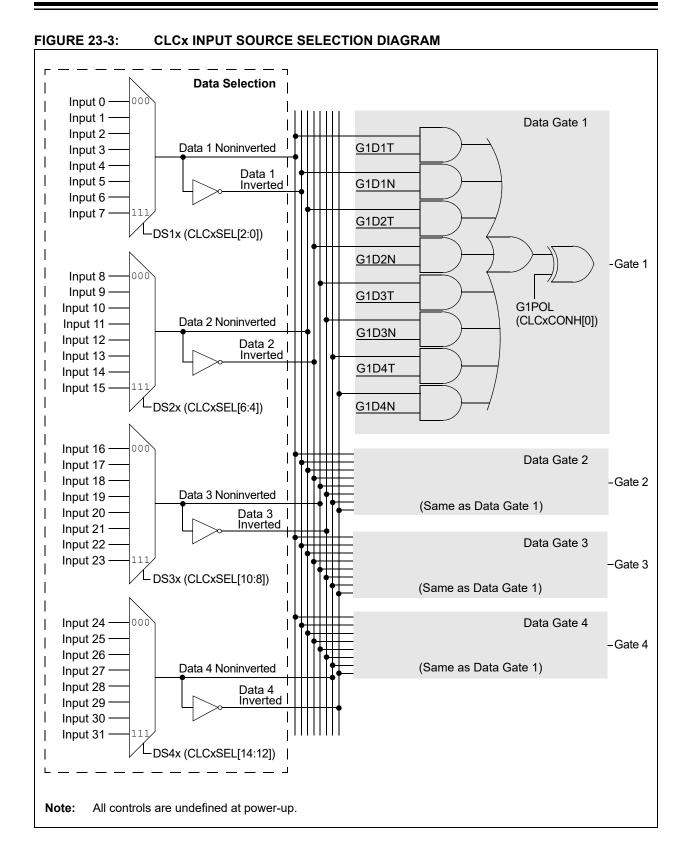

- Four Configurable Logic Cells (CLC) with Internal Connections to Select Peripherals and PPS

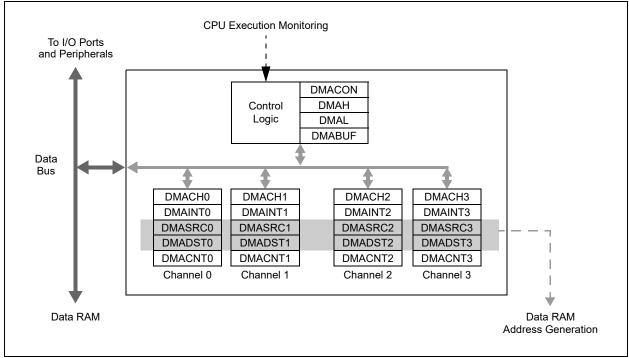

- Four-Channel Hardware DMA

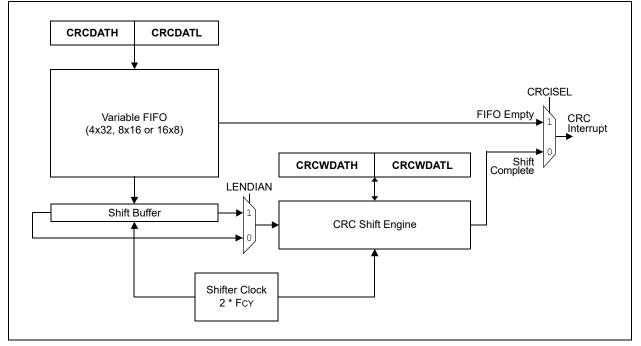

- 32-Bit CRC Calculation module

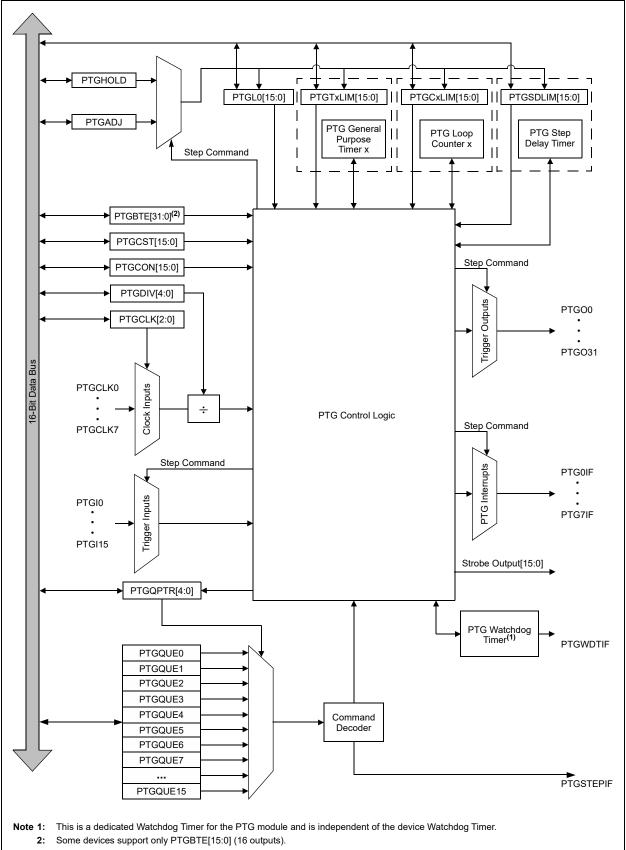

- Peripheral Trigger Generator (PTG):

- 16 possible trigger sources to other peripheral modules

- CPU-independent state machine-based instruction sequencer

- Two 16-bit general purpose timers

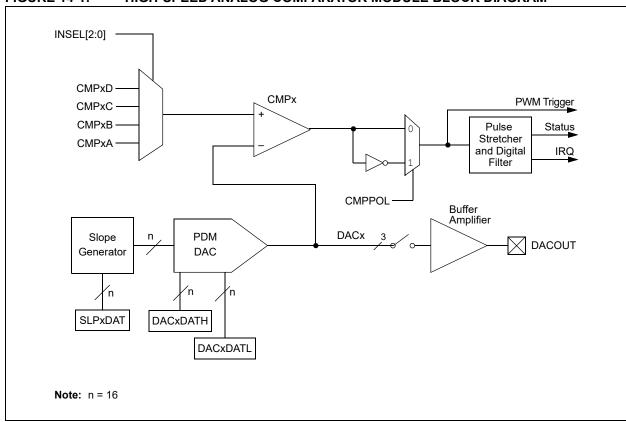

## **Analog Features**

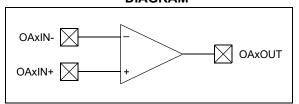

- One Fast Analog Comparator with Input Multiplexing

- Three Operational Amplifiers

- One 12-Bit PDM DAC with Slope Compensation

- One Output DAC Buffer

## **Debug Features**

- Three Programming and Debugging Interfaces:

- Two-wire ICSP™ interface with non-intrusive access and real-time data exchange with application

- · Three Complex, Five Simple Breakpoints

- IEEE Standard 1149.2 Compatible (JTAG) Boundary Scan

## **Safety Features**

- Backup Fast RC Oscillator (BFRC)

- Brown-out Reset (BOR)

- Capless Internal Voltage Regulator

- Clock Monitor System with Backup Oscillator

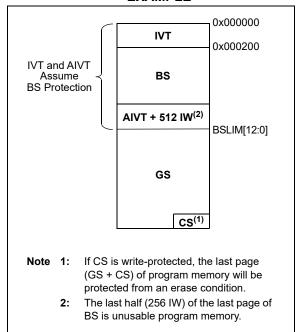

- CodeGuard<sup>™</sup> Security

- Cyclic Redundancy Check (CRC)

- Dual Watchdog Timer (WDT)

- Fail-Safe Clock Monitoring (FSCM)

- Flash Error Correcting Code (ECC)

- Flash OTP by ICSP™ Write Inhibit

- RAM Memory Built-In Self-Test (MBIST)

- Two-Speed Start-up

- · Virtual Pins for Redundancy and Monitoring

- Windowed Deadman Timer (DMT)

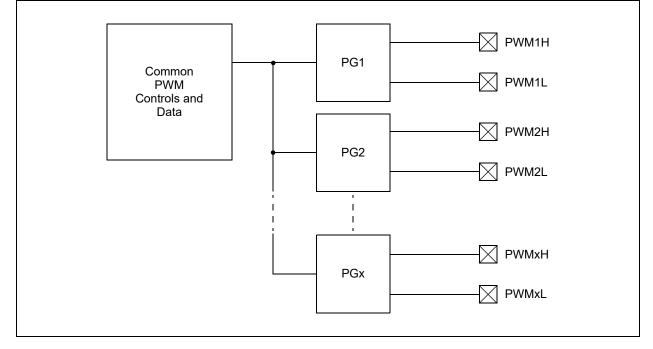

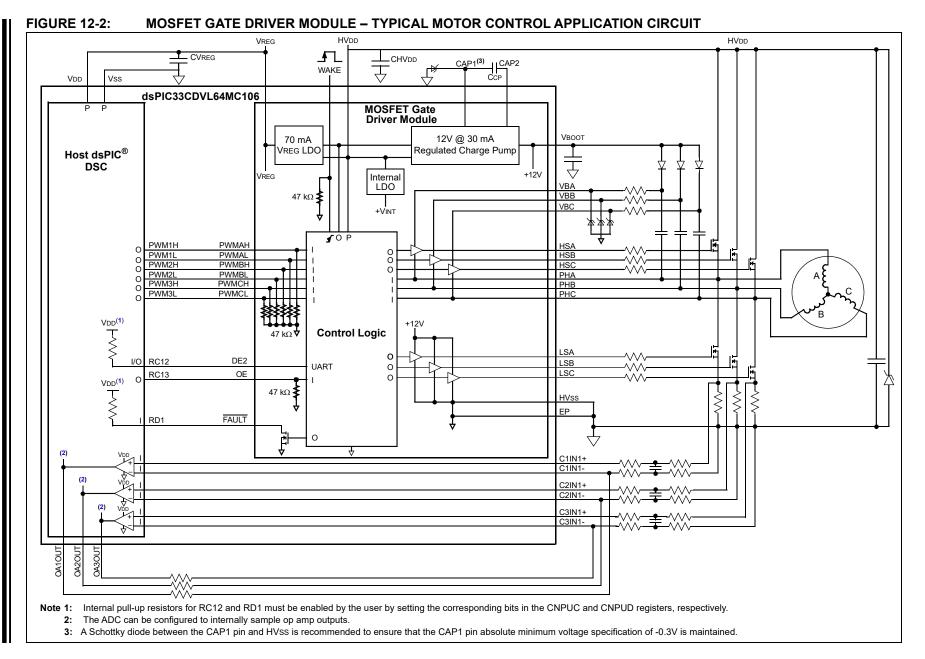

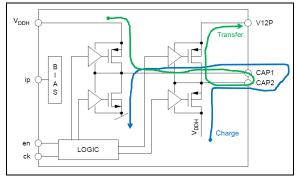

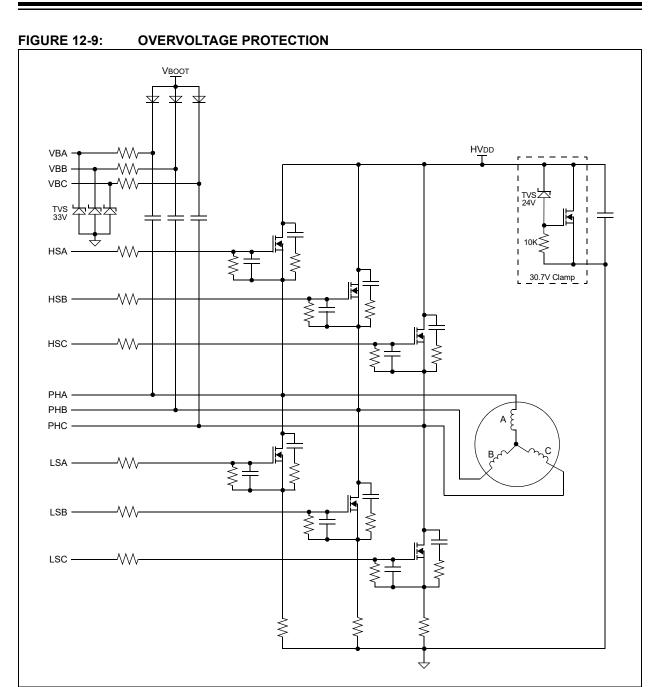

# MOSFET Gate Driver Module (Based on MCP8021 Device)

- Three Half-Bridge Drivers Configured to Drive External High-Side NMOS and Low-Side NMOS MOSFETs:

- Peak output current: 0.5A @ 12V

- Shoot-through protection

- Overcurrent and short-circuit protection

- Fixed Output Linear Regulator:

- 3.3V @ 70 mA

- True Current Foldback

- Protection Features:

- Gate Drive Undervoltage Lockout: 4.5V

- Supply Voltage Undervoltage Shutdown: 4.5V

- Supply Voltage Undervoltage Lockout (UVLO): 6.25V

- Overvoltage Lockout (OVLO): 32V

- Transient (100 ms) Voltage Tolerance: 40V

- Power Module Thermal Shutdown

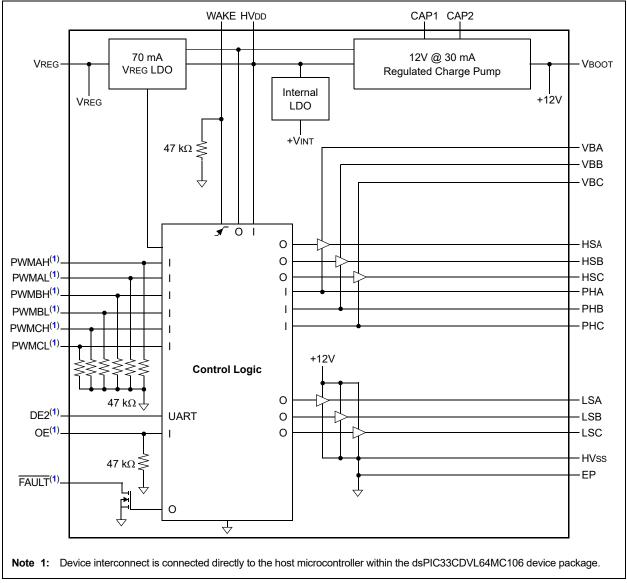

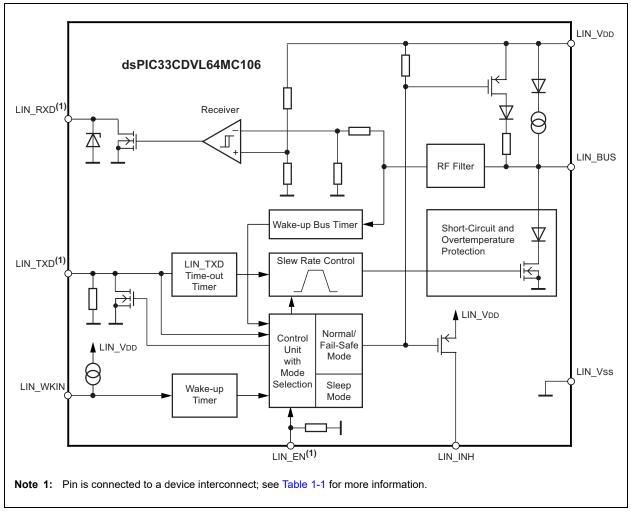

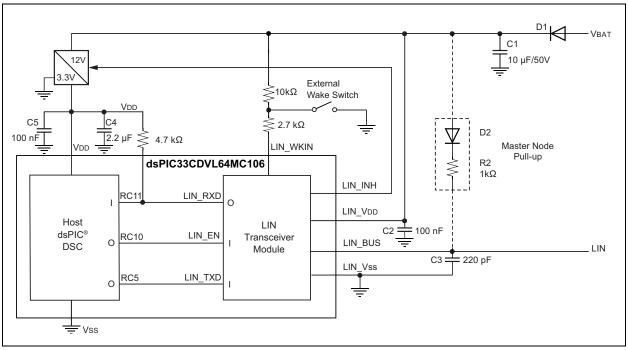

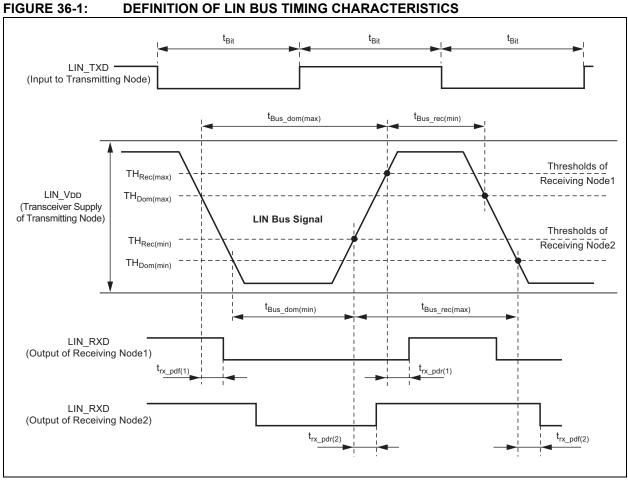

## LIN Transceiver Module (Based on ATA663211 Device) (dsPIC33CDVL64MC106 Only)

- LIN\_BUS Voltage Up to 40V

- LIN\_VDD Voltage = 5V to 28V

- Very Low Supply Current:

- Sleep mode: typically 9 µA

- Fail-Safe mode: typically 80 µA

- Normal mode: typically 250 µA

- Fully Compatible with 3.3V and 5V Devices

- LIN Physical Layer According to LIN 2.0, 2.1, 2.2, 2.2A and SAEJ2602-2

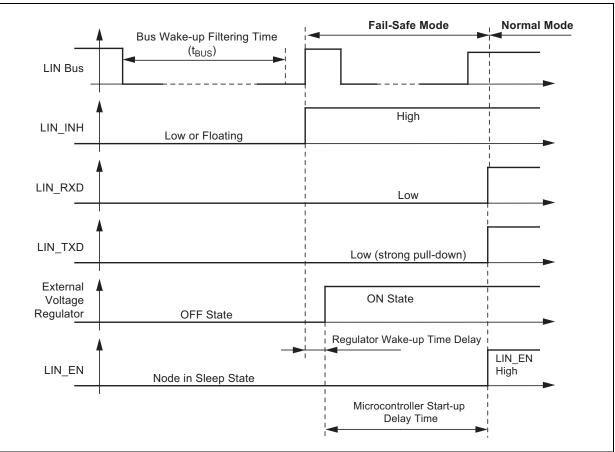

- Wake-up Capability via LIN\_BUS Activity (100 µs dominant)

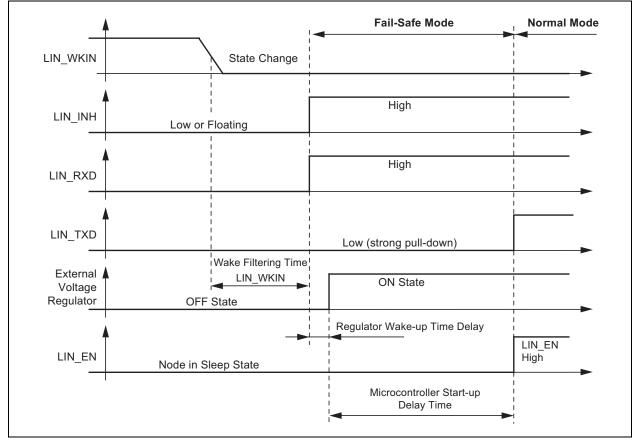

- External Wake-up via LIN\_WKIN Pin (100 µs low level)

### **Functional Safety Collaterals**

- Class B Safety Library IEC 60730

- For ASIL B and Beyond Applications ISO 26262

- FMEDA Computation Spreadsheet (evaluation of Random Hardware Failures Metric)

- Functional Safety Manual

- Functional Safety Diagnostics Suite

#### Qualification

- AEC-Q100 REV G (Grade 1: -40°C to +125°C)

- AEC-Q100 REV G (Grade 0: -40°C to +150°C)

## dsPIC33CDVL64MC106

The dsPIC33CDVL64MC106 family device features are listed in Table 1.

#### TABLE 1: dsPIC33CDVL64MC106 DEVICE FEATURES

| Device             | Pins | Flash (Kbytes) | SRAM (Kbytes) | DMA # of Ch | GPIO/PPS | LIN Transceiver | <b>MOSFET Gate Driver</b> | 16-Bit Timer | SCCP | UART | IdS | I <sup>2</sup> C | SENT | MC PWM | PWM Res (nS) | QEI | 12-Bit ADC Module | ADC Channels | Op Amp | Analog Comp<br>w/12-Bit DAC | PTG | CLC | REFO | CRC | WDT/DMT |

|--------------------|------|----------------|---------------|-------------|----------|-----------------|---------------------------|--------------|------|------|-----|------------------|------|--------|--------------|-----|-------------------|--------------|--------|-----------------------------|-----|-----|------|-----|---------|

| dsPIC33CDVL64MC106 | 64   | 64             | 8             | 4           | 27/22    | 1               | 1                         | 1            | 4    | 3    | 2   | 1                | 1    | 4x2    | 2            | 1   | 1                 | 15           | 3      | 1                           | 1   | 4   | 1    | 1   | 1/1     |

| dsPIC33CDV64MC106  | 64   | 64             | 8             | 4           | 30/25    | 0               | 1                         | 1            | 4    | 3    | 2   | 1                | 1    | 4x2    | 2            | 1   | 1                 | 15           | 3      | 1                           | 1   | 4   | 1    | 1   | 1/1     |

## dsPIC33CDVL64MC106 FAMILY

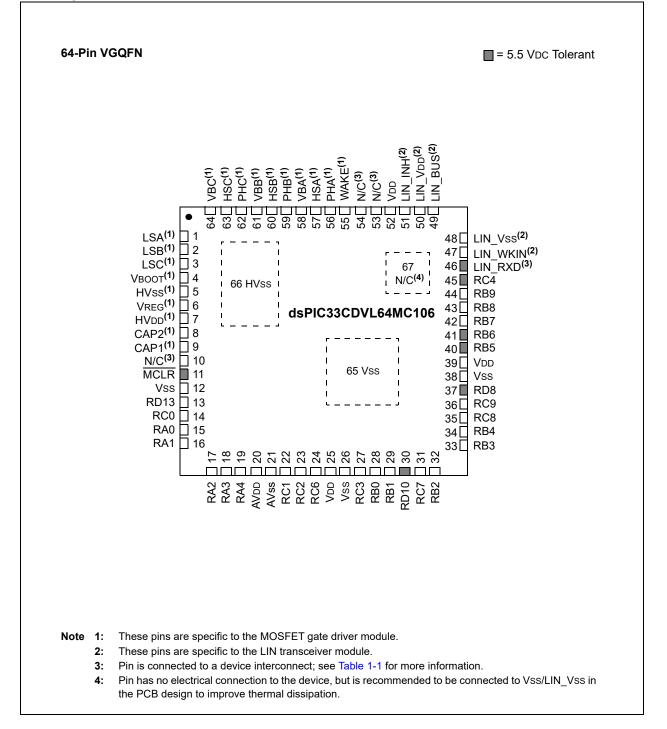

#### **Pin Diagrams**

| Pin | Function                                            | Pin | Function                           |

|-----|-----------------------------------------------------|-----|------------------------------------|

| 1   | LSA                                                 | 35  | RP56/ASDA1/SCK2/RC8                |

| 2   | LSB                                                 | 36  | RP57/ASCL1/SDI2/RC9                |

| 3   | LSC                                                 | 37  | RP72/PCI19/SDO2/RD8                |

| 4   | VBOOT                                               | 38  | Vss                                |

| 5   | HVss                                                | 39  | VDD                                |

| 6   | VREG                                                | 40  | PGD3/ <b>RP37</b> /RB5             |

| 7   | HVdd                                                | 41  | PGC3/ <b>RP38</b> /RB6             |

| 8   | CAP2                                                | 42  | AN2/ <b>RP39</b> /RB7              |

| 9   | CAP1                                                | 43  | PGD1/AN10/RP40/SCL1/RB8            |

| 10  | N/C <sup>(1)</sup>                                  | 44  | PGC1/AN11/ <b>RP41</b> /SDA1/RB9   |

| 11  | MCLR                                                | 45  | <b>RP52</b> /RC4                   |

| 12  | Vss                                                 | 46  | LIN_RXD <sup>(1)</sup>             |

| 13  | ANN0/ <b>RP77</b> /RD13                             | 47  | LIN_WKIN                           |

| 14  | AN12/ <b>RP48</b> /RC0                              | 48  | LIN_Vss                            |

| 15  | OA1OUT/AN0/CMP1A/IBIAS0/RA0                         | 49  | LIN_BUS                            |

| 16  | OA1IN-/RA1                                          | 50  | LIN_VDD                            |

| 17  | OA1IN+/AN9/RA2                                      | 51  | LIN_INH                            |

| 18  | DACOUT/AN3/CMP1C/RA3                                | 52  | VDD                                |

| 19  | OA3OUT/AN4/IBIAS3/RA4                               | 53  | N/C <sup>(1)</sup>                 |

| 20  | AVDD                                                | 54  | N/C <sup>(1)</sup>                 |

| 21  | AVss                                                | 55  | WAKE                               |

| 22  | OA3IN-/AN13/CMP1B/ISRC0/RP49/RC1                    | 56  | РНА                                |

| 23  | OA3IN+/AN14/ISRC1/ <b>RP50</b> /RC2                 | 57  | HSA                                |

| 24  | IBIAS1/ <b>RP54</b> /RC6                            | 58  | VBA                                |

| 25  | VDD                                                 | 59  | РНВ                                |

| 26  | Vss                                                 | 60  | HSB                                |

| 27  | AN15/IBIAS2/RP51/RC3                                | 61  | VBB                                |

| 28  | OSCI/CLKI/AN5/RP32/RB0                              | 62  | PHC                                |

| 29  | OSCO/CLKO/AN6/ <b>RP33</b> /RB1                     | 63  | HSC                                |

| 30  | ISRC3/RP74/RD10                                     | 64  | VBC                                |

| 31  | ISRC2/RP55/RC7                                      | 65  | Vss <sup>(2)</sup>                 |

| 32  | OA2OUT/AN1/AN7/CMP1D/RP34/INT0/RB2                  | 66  | HVss <sup>(2)</sup>                |

| 33  | PGD2/OA2IN-/AN8/ <b>RP35</b> /RB3                   | 67  | N/C <sup>(3)</sup>                 |

| 34  | PGC2/OA2IN+/ <b>RP36</b> /RB4                       |     |                                    |

|     | <b>d: RPn</b> represents remappable pins for the Pr |     | I Dive O a La at (DDO) from atilan |

### TABLE 2: dsPIC33CDVL64MC106 COMPLETE PIN FUNCTIONS

Legend: RPn represents remappable pins for the Peripheral Pin Select (PPS) function.

**Note 1:** Pin is connected to a device interconnect; see Table 1-1 for more information.

2: Pin is connected to a device exposed pad.

**3:** Pin has no electrical connection to the device, but is recommended to be connected to Vss in the PCB design to improve thermal dissipation.

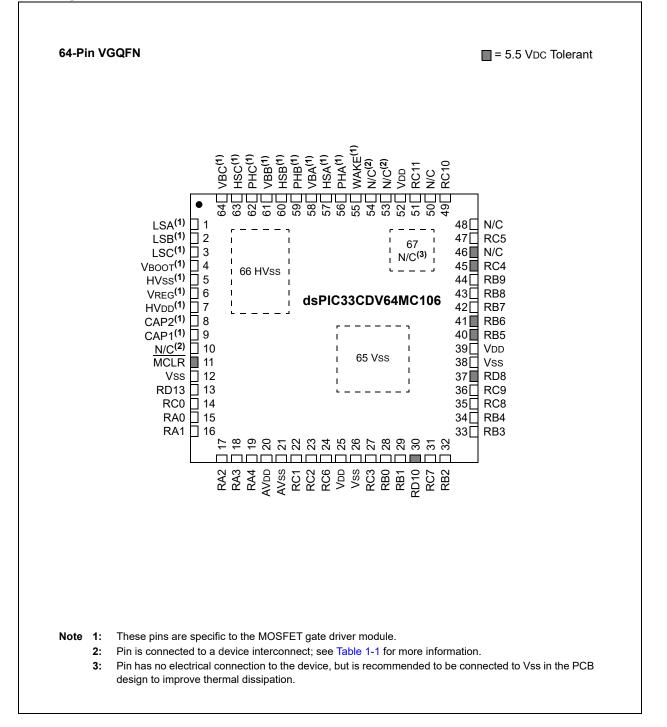

#### **Pin Diagrams (Continued)**

| Pin | Function                           | Pin | Function                         |

|-----|------------------------------------|-----|----------------------------------|

| 1   | LSA                                | 35  | RP56/ASDA1/SCK2/RC8              |

| 2   | LSB                                | 36  | RP57/ASCL1/SDI2/RC9              |

| 3   | LSC                                | 37  | RP72/PCI19/SDO2/RD8              |

| 4   | VBOOT                              | 38  | Vss                              |

| 5   | HVss                               | 39  | VDD                              |

| 6   | VREG                               | 40  | PGD3/ <b>RP37</b> /RB5           |

| 7   | HVdd                               | 41  | PGC3/ <b>RP38</b> /RB6           |

| 8   | CAP2                               | 42  | AN2/ <b>RP39</b> /RB7            |

| 9   | CAP1                               | 43  | PGD1/AN10/ <b>RP40</b> /SCL1/RB8 |

| 10  | N/C <sup>(1)</sup>                 | 44  | PGC1/AN11/ <b>RP41</b> /SDA1/RB9 |

| 11  | MCLR                               | 45  | <b>RP52</b> /RC4                 |

| 12  | Vss                                | 46  | N/C                              |

| 13  | ANN0/ <b>RP77</b> /RD13            | 47  | <b>RP53</b> /RC5                 |

| 14  | AN12/ <b>RP48</b> /RC0             | 48  | N/C                              |

| 15  | OA1OUT/AN0/CMP1A/IBIAS0/RA0        | 49  | <b>RP58</b> /RC10                |

| 16  | OA1IN-/RA1                         | 50  | N/C                              |

| 17  | OA1IN+/AN9/RA2                     | 51  | RP59/RC11                        |

| 18  | DACOUT/AN3/CMP1C/RA3               | 52  | VDD                              |

| 19  | OA3OUT/AN4/IBIAS3/RA4              | 53  | N/C <sup>(1)</sup>               |

| 20  | AVDD                               | 54  | N/C <sup>(1)</sup>               |

| 21  | AVss                               | 55  | WAKE                             |

| 22  | OA3IN-/AN13/CMP1B/ISRC0/RP49/RC1   | 56  | РНА                              |

| 23  | OA3IN+/AN14/ISRC1/RP50/RC2         | 57  | HSA                              |

| 24  | IBIAS1/ <b>RP54</b> /RC6           | 58  | VBA                              |

| 25  | Vdd                                | 59  | РНВ                              |

| 26  | Vss                                | 60  | HSB                              |

| 27  | AN15/IBIAS2/ <b>RP51</b> /RC3      | 61  | VBB                              |

| 28  | OSCI/CLKI/AN5/ <b>RP32</b> /RB0    | 62  | РНС                              |

| 29  | OSCO/CLKO/AN6/ <b>RP33</b> /RB1    | 63  | HSC                              |

| 30  | ISRC3/ <b>RP74</b> /RD10           | 64  | VBC                              |

| 31  | ISRC2/ <b>RP55</b> /RC7            | 65  | Vss <sup>(2)</sup>               |

| 32  | OA2OUT/AN1/AN7/CMP1D/RP34/INT0/RB2 | 66  | HVss <sup>(2)</sup>              |

| 33  | PGD2/OA2IN-/AN8/ <b>RP35</b> /RB3  | 67  | N/C <sup>(3)</sup>               |

| 34  | PGC2/OA2IN+/RP36/RB4               |     |                                  |

### TABLE 3: dsPIC33CDV64MC106 COMPLETE PIN FUNCTIONS

Legend: RPn represents remappable pins for the Peripheral Pin Select (PPS) function.

**Note 1:** Pin is connected to a device interconnect; see Table 1-1 for more information.

2: Pin is connected to a device exposed pad.

**3:** Pin has no electrical connection to the device, but is recommended to be connected to Vss in the PCB design to improve thermal dissipation.

## **Table of Contents**

| 1.0   | Device Overview                                                       |     |

|-------|-----------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers |     |

| 3.0   | CPU                                                                   |     |

| 4.0   | Memory Organization                                                   |     |

| 5.0   | Flash Program Memory                                                  |     |

| 6.0   | Resets                                                                |     |

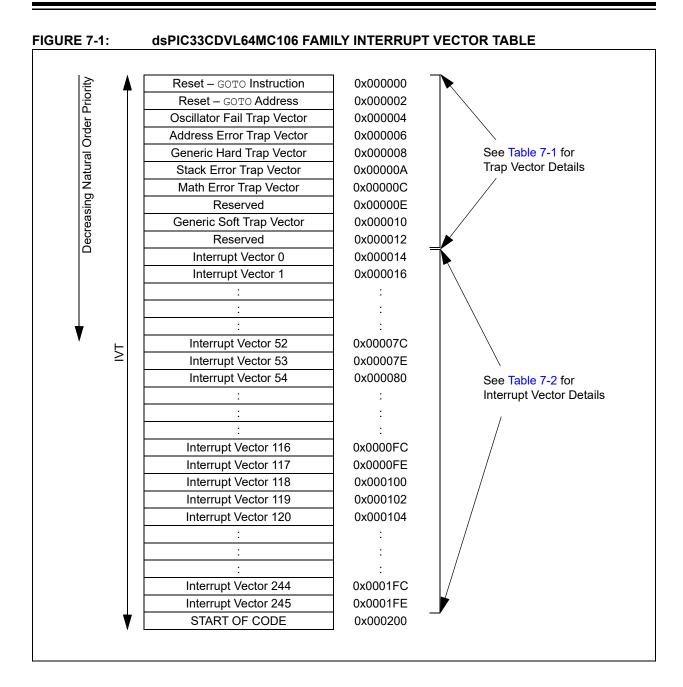

| 7.0   | Interrupt Controller                                                  |     |

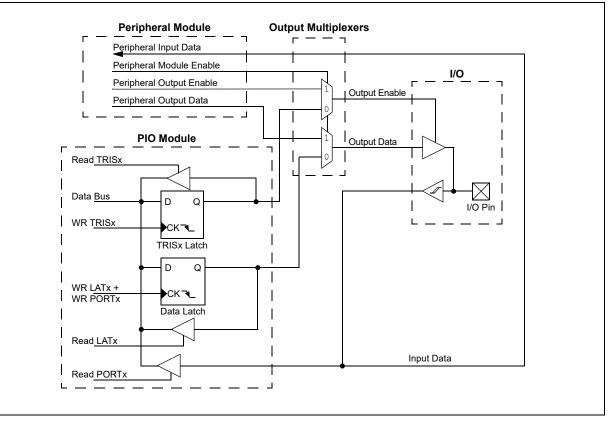

| 8.0   | I/O Ports                                                             |     |

| 9.0   | Oscillator with High-Frequency PLL                                    |     |

| 10.0  | Direct Memory Access (DMA) Controller                                 |     |

| 11.0  |                                                                       |     |

| 12.0  | • •                                                                   |     |

| 13.0  |                                                                       |     |

| 14.0  | High-Speed Analog Comparator with Slope Compensation DAC              |     |

|       | Quadrature Encoder Interface (QEI)                                    |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                    |     |

| 17.0  | LIN Transceiver Module                                                |     |

|       | Serial Peripheral Interface (SPI)                                     |     |

| 19.0  |                                                                       |     |

| 20.0  |                                                                       |     |

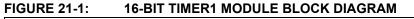

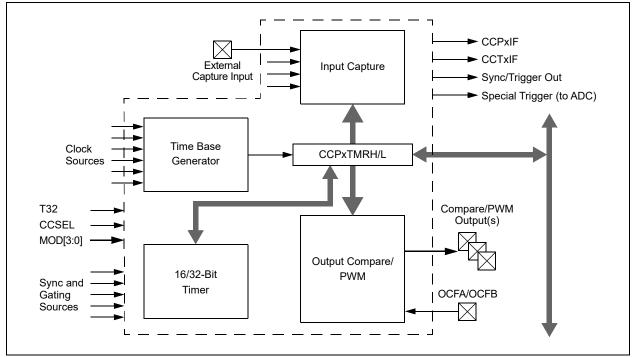

| 21.0  | Timer1                                                                |     |

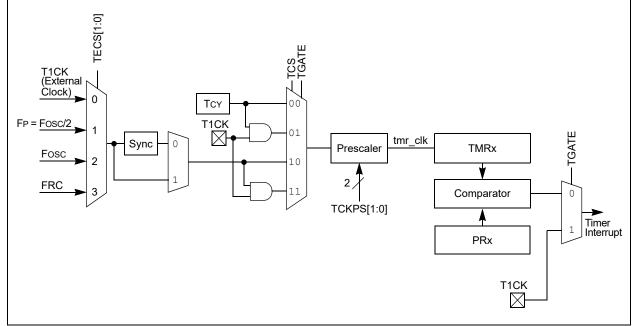

| 22.0  | Capture/Compare/PWM/Timer Modules (SCCP)                              |     |

|       | Configurable Logic Cell (CLC)                                         |     |

| 24.0  | Peripheral Trigger Generator (PTG)                                    |     |

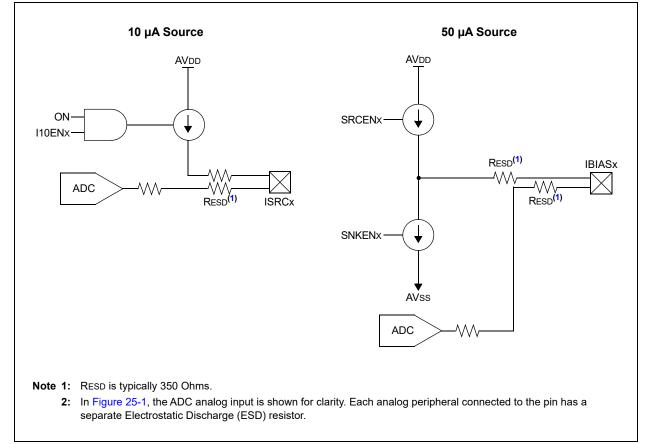

| 25.0  | Current Bias Generator (CBG)                                          | 419 |

| 26.0  | Operational Amplifier                                                 |     |

| 27.0  | Deadman Timer (DMT)                                                   |     |

| 28.0  |                                                                       |     |

| 29.0  | Power-Saving Features                                                 |     |

| 30.0  | Special Features                                                      |     |

| 31.0  | Instruction Set Summary                                               | 479 |

| 32.0  |                                                                       |     |

| 33.0  | Electrical Characteristics                                            | 491 |

| 34.0  | High-Temperature Electrical Characteristics                           |     |

| 35.0  | MOSFET Gate Driver Electrical Characteristics                         |     |

| 36.0  | LIN Transceiver Electrical Characteristics                            |     |

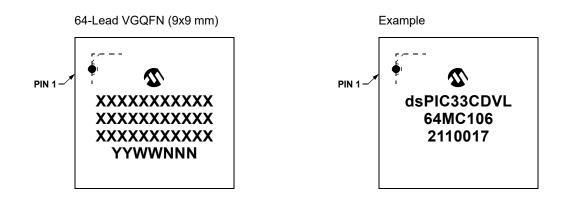

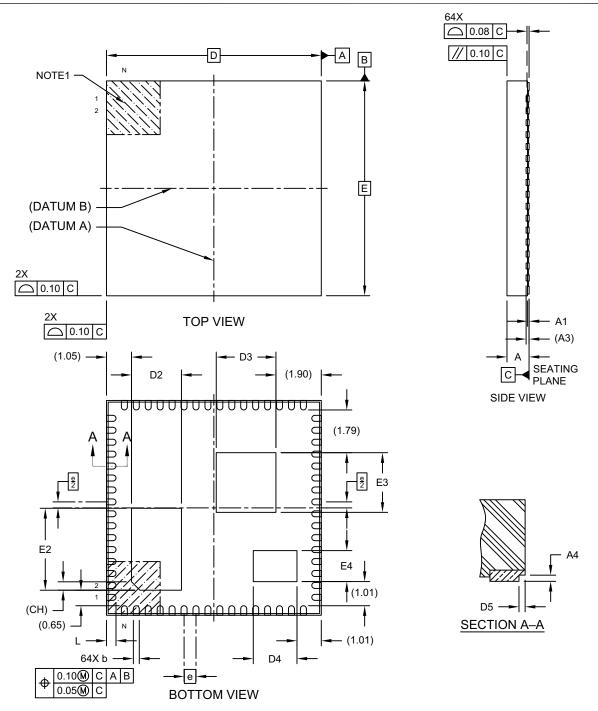

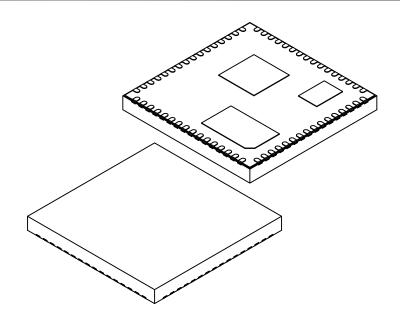

| 37.0  | Packaging Information                                                 |     |

| Appe  | endix A: Revision History                                             |     |

| Index | X                                                                     |     |

| The I | Microchip Website                                                     | 555 |

| Custo | omer Change Notification Service                                      | 555 |

| Cust  | omer Support                                                          | 555 |

| Prod  | luct Identification System                                            |     |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the documents listed below, browse to the documentation section of the dsPIC33CDVL64MC106 product page of the Microchip website (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (www.microchip.com/DS70573)

- "Enhanced CPU" (www.microchip.com/DS70005158)

- "Data Memory" (www.microchip.com/DS70595)

- "dsPIC33/PIC24 Program Memory" (www.microchip.com/DS70000613)

- "Flash Programming" (www.microchip.com/70000609)

- "Reset" (www.microchip.com/DS70602)

- "Interrupts" (www.microchip.com/DS70000600)

- "I/O Ports with Edge Detect" (www.microchip.com/DS70005322)

- "Oscillator Module with High-Speed PLL" (www.microchip.com/DS70005255)

- "Direct Memory Access Controller (DMA)" (www.microchip.com/DS30009742)

- "High-Resolution PWM with Fine Edge Placement" (www.microchip.com/DS70005320)

- "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (www.microchip.com/DS70005213)

- "High-Speed Analog Comparator Module" (www.microchip.com/DS70005280)

- "Quadrature Encoder Interface (QEI)" (www.microchip.com/DS70000601)

- "Multiprotocol Universal Asynchronous Receiver Transmitter (UART) Module" (www.microchip.com/DS70005288)

- "Serial Peripheral Interface (SPI) with Audio Codec Support" (www.microchip.com/DS70005136)

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (www.microchip.com/DS70000195)

- "Single-Edge Nibble Transmission (SENT) Module" (www.microchip.com/DS70005145)

- "Timer1 Module" (www.microchip.com/DS70005279)

- "Capture/Compare/PWM/Timer (MCCP and SCCP)" (www.microchip.com/DS30003035)

- "Configurable Logic Cell (CLC)" (www.microchip.com/DS70005298)

- "Peripheral Trigger Generator (PTG)" (www.microchip.com/DS70000669)

- "Current Bias Generator (CBG)" (www.microchip.com/DS70005253)

- "Deadman Timer (DMT)" (www.microchip.com/DS70005155)

- "32-Bit Programmable Cyclic Redundancy Check (CRC)" (www.microchip.com/DS30009729)

- "Dual Watchdog Timer" (www.microchip.com/DS70005250)

- "Watchdog Timer and Power-Saving Modes" (www.microchip.com/DS70615)

- "Programming and Diagnostics" (www.microchip.com/DS70608)

- "CodeGuard™ Intermediate Security" (www.microchip.com/DS70005182)

- "Flash Programming" (www.microchip.com/DS70000609)

## **Terminology Cross Reference**

Table 4 provides updated terminology for depreciated naming conventions. Register and bit names remain unchanged, however, descriptions and usage guidance may have been updated

| TABLE 4: | TERMINOLOGY CROSS |

|----------|-------------------|

|          | REFERENCES        |

| Use Case         | Depreciated<br>Term | New Term  |

|------------------|---------------------|-----------|

| CPU              | Master              | Initiator |

| DMA              | Master              | Initiator |

| l <sup>2</sup> C | Master              | Host      |

|                  | Slave               | Client    |

| SPI              | Master              | Host      |

|                  | Slave               | Client    |

| UART, LIN Mode   | Master              | Commander |

|                  | Slave               | Responder |

| PWM              | Master              | Host      |

|                  | Slave               | Client    |

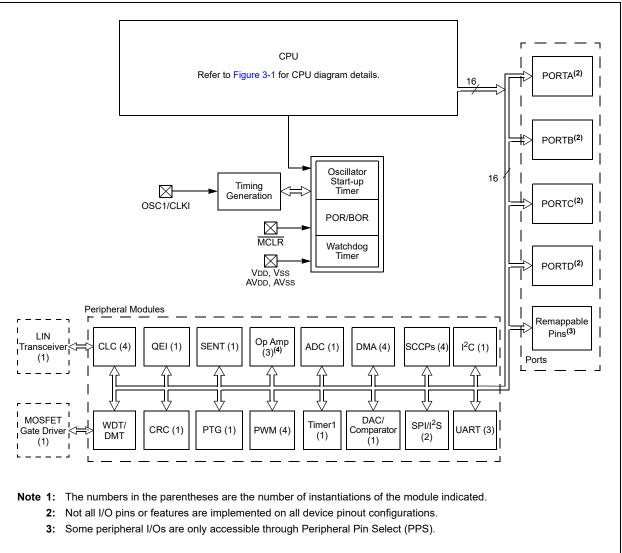

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33CDVL64MC106 devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33CDVL64MC106 Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

The dsPIC33CDVL64MC106 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-2 shows a general block diagram of the core and peripheral modules of the dsPIC33CDVL64MC106 family. Table 1-2 lists the functions of the various pins shown in the pinout diagrams.

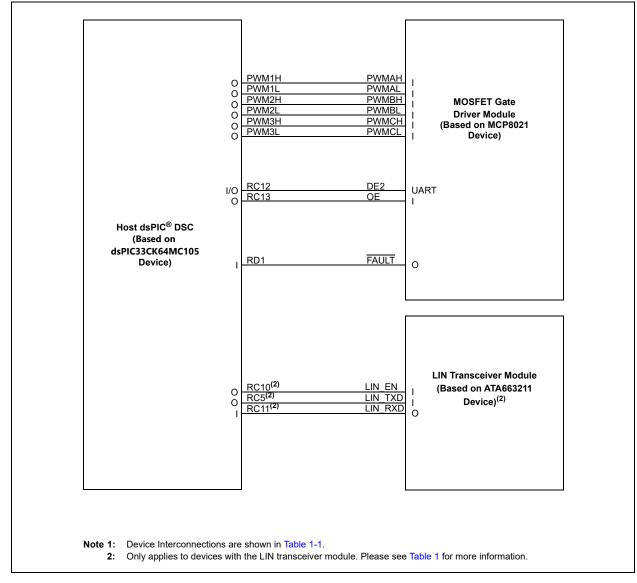

#### FIGURE 1-1: dsPIC33CDVL64MC106 FAMILY INTERNAL CONNECTIONS BLOCK DIAGRAM

| Host dsPIC <sup>®</sup> DSC Connection | MOSFET Gate Driver Connection             | External Pin |

|----------------------------------------|-------------------------------------------|--------------|

| RB14/PWM1H                             | PWMAH                                     | 10           |

| RB15/PWM1L                             | PWMAL                                     | No           |

| RB12/PWM2H                             | PWMBH                                     | 54           |

| RB13/PWM2L                             | PWMBL                                     | No           |

| RB10/PWM3H                             | PWMCH                                     | 53           |

| RB11/PWM3L                             | PWMCL                                     | No           |

| RD1                                    | FAULT                                     | No           |

| RC12/RP60                              | DE2                                       | No           |

| RC13                                   | OE                                        | No           |

| Host dsPIC DSC Connection              | LIN Transceiver Connection <sup>(2)</sup> | External Pin |

| RC10                                   | LIN_EN                                    | No           |

| RC5/RP53                               | LIN_TXD                                   | No           |

| RC11/RP59                              | LIN_RXD                                   | 46           |

## TABLE 1-1: dsPIC33CDVL64MC106 FAMILY INTERCONNECTIONS<sup>(1)</sup>

**Note 1:** Interconnect is also bonded to an external device pin.

2: Only applies to devices with LIN transceiver module.

| Pin Name <sup>(1)</sup>          | Pin<br>Type | Buffer<br>Type | PPS      | Description                                                                                             |

|----------------------------------|-------------|----------------|----------|---------------------------------------------------------------------------------------------------------|

| dsPIC <sup>®</sup> DSC Functions |             |                |          | I                                                                                                       |

| AN0-AN15                         |             | Analog         | No       | Analog input channels.                                                                                  |

| ANN0                             | 1           | Analog         | No       | Analog negative input.                                                                                  |

| CLKI                             | I           | ST             | No       | External Clock (EC) source input. Always associated with OSCI pin function.                             |

| CLKO                             | 0           | —              | No       | In Configuration bits, it can be set to output the CPU clock. Always associated with OSCO pin function. |

| OSCI                             | I           | CMOS           | No       | Oscillator crystal input. Connects to crystal or resonator in Crystal Oscillator mode.                  |

| OSCO                             | I/O         | _              | No       | Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode.              |

| REFCLKI                          | I           | ST             | Yes      | Reference clock input.                                                                                  |

| REFCLKO                          | 0           | —              | Yes      | Reference clock output.                                                                                 |

| INT0                             | I           | ST             | No       | External Interrupt 0.                                                                                   |

| INT1                             | I           | ST             | Yes      | External Interrupt 1.                                                                                   |

| INT2<br>INT3                     |             | ST<br>ST       | Yes      | External Interrupt 2.                                                                                   |

|                                  |             |                | Yes      | External Interrupt 3.                                                                                   |

| IOCA[4:0]<br>IOCB[15:0]          |             | ST<br>ST       | No<br>No | Interrupt-on-Change input for PORTA.<br>Interrupt-on-Change input for PORTB.                            |

| IOCC[13:0]                       |             | ST             | No       | Interrupt-on-Change input for PORTE.                                                                    |

| IOCD1, IOCD8, IOCD10<br>IOCD13   |             | ST             | No       | Interrupt-on-Change input for PORTD.                                                                    |

| QEIAx                            | I           | ST             | Yes      | QEIx Input A.                                                                                           |

| QEIBx                            | I           | ST             | Yes      | QEIx Input B.                                                                                           |

| QEINDXx                          | I           | ST             | Yes      | QEIx Index input.                                                                                       |

| QEIHOMx                          |             | ST             | Yes      | QEIx Home input.                                                                                        |

| QEICMPx                          | 0           | —              | Yes      | QEIx comparator output.                                                                                 |

| RP32-RP61, RP65, RP72,<br>RP77   | I/O         | ST             | Yes      | Remappable I/O ports.                                                                                   |

| RA0-RA4                          | I/O         | ST             | No       | PORTA is a bidirectional I/O port.                                                                      |

| RB0-RB15                         | I/O         | ST             | No       | PORTB is a bidirectional I/O port.                                                                      |

| RC0-RC13                         | I/O         | ST             | No       | PORTC is a bidirectional I/O port.                                                                      |

| RD1, RD8, RD10, RD13             | I/O         | ST             | No       | PORTD is a bidirectional I/O port.                                                                      |

| T1CK                             | I           | ST             | Yes      | Timer1 external clock input.                                                                            |

| U1CTS                            | I           | ST             | Yes      | UART1 Clear-to-Send.                                                                                    |

| U1RTS                            | Ó           | —              | Yes      | UART1 Request-to-Send.                                                                                  |

| U1RX                             | I           | ST             | Yes      | UART1 receive.                                                                                          |

| U1TX                             | 0           | —              | Yes      | UART1 transmit.                                                                                         |

| U1DSR                            | I           | ST             | Yes      | UART1 Data-Set-Ready.                                                                                   |

| U1DTR                            | 0           |                | Yes      | UART1 Data-Terminal-Ready.                                                                              |

## TABLE 1-2: PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4L and PWM4H pins are available on PPS.

3: Pin is connected to a device interconnect; see Table 1-1 for more information.

**4:** A Schottky diode between the CAP1 pin and HVss is recommended to ensure that the CAP1 pin absolute minimum voltage specification of -0.3V is maintained.

O = Output

I = Input

| TABLE 1-2: PINOUT          |             | JURIP          |          |                                                           |

|----------------------------|-------------|----------------|----------|-----------------------------------------------------------|

| Pin Name <sup>(1)</sup>    | Pin<br>Type | Buffer<br>Type | PPS      | Description                                               |

| U2CTS                      | I           | ST             | Yes      | UART2 Clear-to-Send.                                      |

| U2RTS                      | 0           |                | Yes      | UART2 Request-to-Send.                                    |

| U2RX                       | I           | ST             | Yes      | UART2 receive.                                            |

| U2TX                       | 0           |                | Yes      | UART2 transmit.                                           |

| U2DSR                      | I           | ST             | Yes      | UART2 Data-Set-Ready.                                     |

| U2DTR                      | 0           | —              | Yes      | UART2 Data-Terminal-Ready.                                |

| U3CTS                      | I           | ST             | Yes      | UART3 Clear-to-Send.                                      |

| U3RTS                      | 0           |                | Yes      | UART3 Request-to-Send.                                    |

| U3RX                       | I           | ST             | Yes      | UART3 receive.                                            |

| U3TX                       | 0           |                | Yes      | UART3 transmit.                                           |

| U3DSR                      | 1           | ST             | Yes      | UART3 Data-Set-Ready.                                     |

| U3DTR                      | 0           | —              | Yes      | UART3 Data-Terminal-Ready.                                |

| SENT1                      | I           | ST             | Yes      | SENT1 input.                                              |

| SENT1OUT                   | 0           | —              | Yes      | SENT1 output.                                             |

| PTGTRG24                   | 0           |                | Yes      | PTG Trigger Output 24.                                    |

| PTGTRG25                   | 0           | —              | Yes      | PTG Trigger Output 25.                                    |

| TCKI1-TCKI4                | I           | ST             | Yes      | SCCP timer inputs.                                        |

| ICM1-ICM4                  | 1           | ST             | Yes      | SCCP capture inputs.                                      |

| OCFA-OCFB                  | 1           | ST             | Yes      | SCCP Fault inputs.                                        |

| OCM1x-OCM4x                | 0           | —              | Yes      | SCCP compare outputs.                                     |

| SCK1                       | I/O         | ST             | Yes      | Synchronous serial clock input/output for SPI1.           |

| SDI1                       | I           | ST             | Yes      | SPI1 data in.                                             |

| SDO1                       | 0           | —              | Yes      | SPI1 data out.                                            |

| SS1                        | I/O         | ST             | Yes      | SPI1 Slave synchronization or frame pulse I/O.            |

| SCK2                       | I/O         | ST             | Yes      | Synchronous serial clock input/output for SPI2.           |

| SDI2                       | 1           | ST             | Yes      | SPI2 data in.                                             |

| SDO2                       | 0           |                | Yes      | SPI2 data out.                                            |

| SS2                        | I/O         | ST             | Yes      | SPI2 Slave synchronization or frame pulse I/O.            |

| SCL1                       | I/O         | ST             | No       | Synchronous serial clock input/output for I2C1.           |

| SDA1                       | I/O         | ST             | No       | Synchronous serial data input/output for I2C1.            |

| ASCL1                      | I/O         | ST             | No       | Alternate synchronous serial clock input/output for I2C1. |

| ASDA1                      | I/O         | ST             | No       | Alternate synchronous serial data input/output for I2C1.  |

| PCI8-PCI18                 | I           | ST             | Yes      | PWM Inputs 8 through 18.                                  |

| PCI19                      | I           | ST             | No       | PWM Input 19.                                             |

| PWMEA-PWMED                | 0           | —              | Yes      | PWM Event Outputs A through D.                            |

| PWM1L-PWM4L <sup>(2)</sup> | 0           | —              | No       | PWM Low Outputs 1 through 4.                              |

| PWM1H-PWM4H <sup>(2)</sup> | 0           | —              | No       | PWM High Outputs 1 through 4.                             |

| CLCINA-CLCIND              | Ι           | ST             | Yes      | CLC Inputs A through D.                                   |

| CLCxOUT                    | 0           | —              | Yes      | CLCx output.                                              |

| CMP1A                      | I           | Analog         | No       | Comparator Channel 1A.                                    |

| CMP1B                      | I           | Analog         | No       | Comparator Channel 1B.                                    |

| CMP1C                      | I           | Analog         | No       | Comparator Channel 1C.                                    |

| CMP1D                      | I           | Analog         | No       | Comparator Channel 1D.                                    |

| Legend: CMOS = CMOS        | compat      | ible input     | t or out | put Analog = Analog input P = Power                       |

| ST = Schmitt Tri           |             |                |          |                                                           |

#### TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

P = Power

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

PPS = Peripheral Pin Select

O = Output

I = Input

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4L and PWM4H pins are available on PPS.

**3:** Pin is connected to a device interconnect; see Table 1-1 for more information.

**4:** A Schottky diode between the CAP1 pin and HVss is recommended to ensure that the CAP1 pin absolute minimum voltage specification of -0.3V is maintained.

| Pin Nan       | ne <sup>(1)</sup> | Pin<br>Type | Buffer<br>Type | PPS                 | Description                                                                   |

|---------------|-------------------|-------------|----------------|---------------------|-------------------------------------------------------------------------------|

| DACOUT        | ACOUT O —         |             | No             | DAC output voltage. |                                                                               |

| IBIAS0-IBIAS3 |                   | 0           | Analog         | No                  | 50 µA Constant-Current Outputs 0 through 3.                                   |

| ISRC0-ISRC3   |                   | 0           | Analog         | No                  | 10 µA Constant-Current Outputs 0 through 3.                                   |

| OA1IN+        |                   | I           |                | No                  | Op Amp 1+ input.                                                              |

| OA1IN-        |                   | I           |                | No                  | Op Amp 1- input.                                                              |

| OA1OUT        |                   | 0           |                | No                  | Op Amp 1 output.                                                              |

| OA2IN+        |                   | 1           |                | No                  | Op Amp 2+ input.                                                              |

| OA2IN-        |                   | I           |                | No                  | Op Amp 2- input.                                                              |

| OA2OUT        |                   | 0           |                | No                  | Op Amp 2 output.                                                              |

| OA3IN+        |                   | I           |                | No                  | Op Amp 3+ input.                                                              |

| OA3IN-        |                   | I           |                | No                  | Op Amp 3- input.                                                              |

| OA3OUT        |                   | 0           | —              | No                  | Op Amp 3 output.                                                              |

| ADTRG31       |                   | I           | ST             | No                  | External ADC trigger source.                                                  |

| PGD1          |                   | I/O         | ST             | No                  | Data I/O pin for Programming/Debugging Communication Channel 1.               |

| PGC1          |                   | I           | ST             | No                  | Clock input pin for Programming/Debugging Communication<br>Channel 1.         |

| PGD2          |                   | I/O         | ST             | No                  | Data I/O pin for Programming/Debugging Communication Channel 2.               |

| PGC2          |                   | I           | ST             | No                  | Clock input pin for Programming/Debugging Communication<br>Channel 2.         |

| PGD3          |                   | I/O         | ST             | No                  | Data I/O pin for Programming/Debugging Communication Channel 3.               |

| PGC3          |                   | I           | ST             | No                  | Clock input pin for Programming/Debugging Communication Channel 3.            |

| MCLR          |                   | I/P         | ST             | No                  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |

| AVdd          |                   | Р           | Р              | No                  | Positive supply for analog modules. This pin must be connected at all times.  |

| AVss          |                   | Р           | Р              | No                  | Ground reference for analog modules. This pin must be connected at all times. |

| Vdd           |                   | Р           | Р              | No                  | Positive supply for peripheral logic and I/O pins.                            |

| Vss           |                   | Р           | Р              | No                  | Ground reference for logic and I/O pins.                                      |

## TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

P = Power

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

PPS = Peripheral Pin Select

O = Output

I = Input

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

**2:** PWM4L and PWM4H pins are available on PPS.

**3:** Pin is connected to a device interconnect; see Table 1-1 for more information.

**4:** A Schottky diode between the CAP1 pin and HVss is recommended to ensure that the CAP1 pin absolute minimum voltage specification of -0.3V is maintained.

| Pin Name <sup>(1)</sup>   | Pin     | Buffer     | PPS      | Description                                                                                             |

|---------------------------|---------|------------|----------|---------------------------------------------------------------------------------------------------------|

|                           | Туре    | Туре       | FFJ      | Description                                                                                             |

| MOSFET Gate Driver Mod    | ule Fun | octions    |          |                                                                                                         |

| WAKE                      | I       |            |          | HV digital edge input, device wake-up from Sleep with internal                                          |

|                           | 1/0     |            |          | pull-down resistor                                                                                      |

| PHA                       | 1/0     |            |          | Phase A high-side MOSFET Driver reference, back-EMF sense input                                         |

| HSA                       | 0       |            |          | Phase A high-side N-channel MOSFET Driver, active-high                                                  |

| VBA                       | P       |            |          | Phase A high-side MOSFET Driver bias                                                                    |

| PHB                       | I/O     |            |          | Phase B high-side MOSFET Driver reference, back-EMF sense input                                         |

| HSB                       | 0       |            |          | Phase B high-side N-channel MOSFET Driver, active-high                                                  |

| VBB                       | Р       |            |          | Phase B high-side MOSFET Driver bias                                                                    |

| PHC                       | I/O     |            |          | Phase C high-side MOSFET Driver reference, back-EMF sense input                                         |

| HSC                       | 0       |            |          | Phase C high-side N-channel MOSFET Driver, active-high                                                  |

| VBC                       | Р       |            |          | Phase C high-side MOSFET driver bias.                                                                   |

| LSA                       | 0       |            |          | Phase A low-side N-channel MOSFET Driver, active-high.                                                  |

| LSB                       | 0       |            |          | Phase B low-side N-channel MOSFET Driver, active-high.                                                  |

| LSC                       | 0       |            |          | Phase C low-side N-channel MOSFET Driver, active-high                                                   |

| VBOOT                     | Р       |            |          | External bootstrap circuit supply voltage output                                                        |

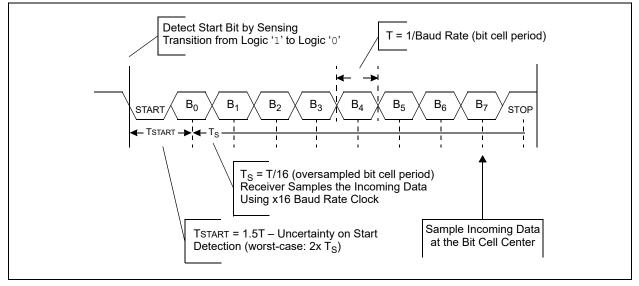

| CAP1 <sup>(4)</sup>       | Р       |            |          | Charge Pump Flying Capacitor Input 1                                                                    |

| CAP2                      | Р       |            |          | Charge Pump Flying Capacitor Input 2                                                                    |

| HVDD                      | Р       |            |          | Input supply                                                                                            |

| VREG                      | Р       |            |          | Linear Regulator Output: 3.3V                                                                           |

| HVss                      | Р       |            |          | MOSFET Driver Ground Reference                                                                          |

| PWMAH <sup>(3)</sup>      | I       |            |          | Phase A high-side control, internal 47 k $\Omega$ pull-down                                             |

| PWMAL <sup>(3)</sup>      | I       |            |          | Phase A low-side control, internal 47 kΩ pull-down                                                      |

| PWMBH <sup>(3)</sup>      | 1       |            |          | Phase B high-side control, internal 47 k $\Omega$ pull-down                                             |

| PWMBL <sup>(3)</sup>      | 1       |            |          | Phase B low-side control, internal 47 kΩ pull-down                                                      |

| PWMCH <sup>(3)</sup>      | 1       |            |          | Phase C high-side control, internal 47 k $\Omega$ pull-down                                             |

| PWMCL <sup>(3)</sup>      |         |            |          | Phase C low-side control, internal 47 k $\Omega$ pull-down                                              |

| FAULT <sup>(3)</sup>      | Ó       |            |          | Digital output, active-low Fault, open-drain                                                            |

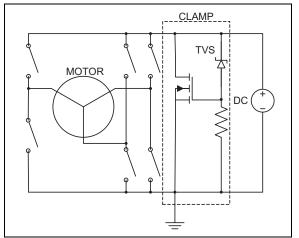

| DE2 <sup>(3)</sup>        | UART    |            |          | Digital communications port, open-drain                                                                 |

| $OE^{(3)}$                | 0/ 4 (1 |            |          | Digital input, output enable, Fault clearing, internal 47 k $\Omega$ pull-down                          |

| LIN Transceiver Module Fi | unction | s (dsPl(   | C33CD    |                                                                                                         |

| LIN INH                   | 1       |            |          | LIN Transceiver Inhibit, active high                                                                    |

| LIN BUS                   | 1/O     |            |          | LIN Communications Bus                                                                                  |

| LIN WKin                  | 1/0     |            |          | LIN Wake Input                                                                                          |

| LIN_RXD <sup>(3)</sup>    |         |            |          | LIN Received Data output to host dsPIC <sup>®</sup> DSC                                                 |

| LIN_VDD <sup>(3)</sup>    | P       |            |          | LIN Transceiver Input Supply                                                                            |

| LIN_VSS <sup>(3)</sup>    |         |            |          | LIN Transceiver Input Supply                                                                            |

| LIN_EN <sup>(3)</sup>     |         |            |          | Digital input, enable signal                                                                            |

| LIN_TXD <sup>(3)</sup>    |         |            |          |                                                                                                         |

| LIN_RXD <sup>(3)</sup>    |         |            |          | Transmit data input from microcontroller                                                                |

|                           | 0       |            |          | Receive data output to microcontroller,<br>use 4.7 k $\Omega$ external pull-up and 20 pF load capacitor |

| Legend: CMOS = CMOS       | compati | ible input | t or out |                                                                                                         |

| ST = Schmitt Tric         |         |            |          |                                                                                                         |

| PPS = Periphera           |         |            |          |                                                                                                         |

| •                         |         |            | rkane    | variants. See the "Pin Diagrams" section for pin availability.                                          |

| <b>TABLE 1-2:</b> | PINOUT I/O DESCRIPTIONS (CONTINUED) |

|-------------------|-------------------------------------|

|-------------------|-------------------------------------|

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4L and PWM4H pins are available on PPS.

3: Pin is connected to a device interconnect; see Table 1-1 for more information.

**4:** A Schottky diode between the CAP1 pin and HVss is recommended to ensure that the CAP1 pin absolute minimum voltage specification of -0.3V is maintained.

NOTES:

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33CDVL64MC106 family devices requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins regardless if ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- PGCx/PGDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.4 "ICSP Pins")

- OSCI and OSCO pins when an external oscillator source is used (see Section 2.5 "External Oscillator Pins")

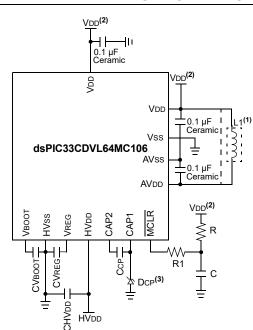

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

- Note 1: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $1\Omega$  and the inductor capacity greater than 10 mA.

- 2: VDD/AVDD pins may be powered by either an external power supply or by the 3.3V VREG output.

- A Schottky diode between the CAP1 pin and HVss is recommended to ensure that the CAP1 pin absolute minimum voltage specification of -0.3V is maintained.

Where:

$$f = \frac{FCNV}{2}$$

(i.e., ADC conversion rate/2)

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

## 2.2.1 BULK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a bulk capacitor for integrated circuits, including DSCs, to supply a local power source. The value of the bulk capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the bulk capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

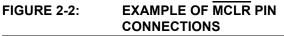

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- · Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components, as shown in Figure 2-2, within one-quarter inch (6 mm) from the MCLR pin.

### 2.4 ICSP Pins

The PGCx and PGDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGCx and PGDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> debugger tool.

For more information on the MPLAB programmer/ debugger connection requirements, refer to the Microchip website.

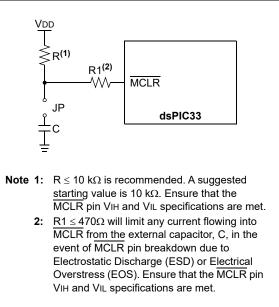

#### 2.5 External Oscillator Pins

When the Primary Oscillator (POSC) circuit is used to connect a crystal oscillator, special care and consideration is required to ensure proper operation. The POSC circuit should be tested across the environmental conditions that the end product is intended to be used. The load capacitors specified in the crystal oscillator data sheet can be used as a starting point, however, the parasitic capacitance from the PCB traces can affect the circuit and the values may need to be altered to ensure proper start-up and operation.

Excessive trace length and other physical interaction can lead to poor signal quality. Poorly tuned oscillator circuits can have reduced amplitude, incorrect frequency (runt pulses), distorted waveforms and long start-up times that may result in unpredictable application behavior, such as instruction misexecution, illegal op code fetch, etc. Ensure that the crystal oscillator circuit is at full amplitude and correct frequency before the system begins to execute code. In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator do not have high frequencies, short rise and fall times and other similar noise. For further information on the Primary Oscillator see Section 9.4 "Internal Fast RC (FRC) Oscillator".

## 2.6 External Oscillator Layout Guidance

Use best practices during PCB layout to ensure robust start-up and operation. The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. If using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the Microchip website (www.microchip.com):

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

- AN1798, "Crystal Selection for Low-Power Secondary Oscillator

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to a certain frequency (see Section 9.0 "Oscillator with High-Frequency PLL") to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a Logic Low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Targeted Applications

- Power Factor Correction (PFC):

- Interleaved PFC

- Critical Conduction PFC

- Bridgeless PFC

- DC/DC Converters:

- Buck, Boost, Forward, Flyback, Push-Pull

- Half/Full-Bridge

- Phase-Shift Full-Bridge

- Resonant Converters

- DC/AC:

- Half/Full-Bridge Inverter

- Resonant Inverter

- Motor Control

- BLDC

- PMSM

- SR

- ACIM

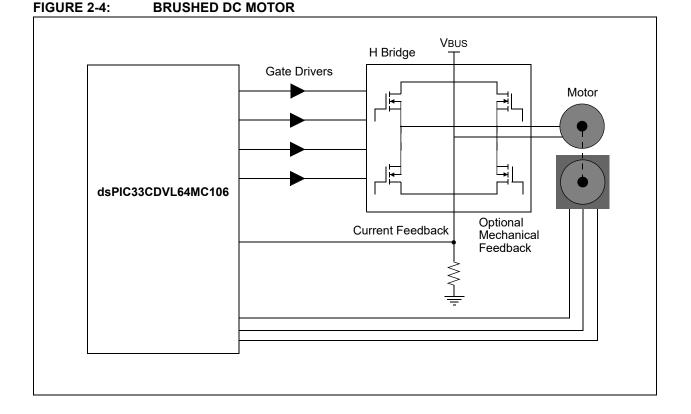

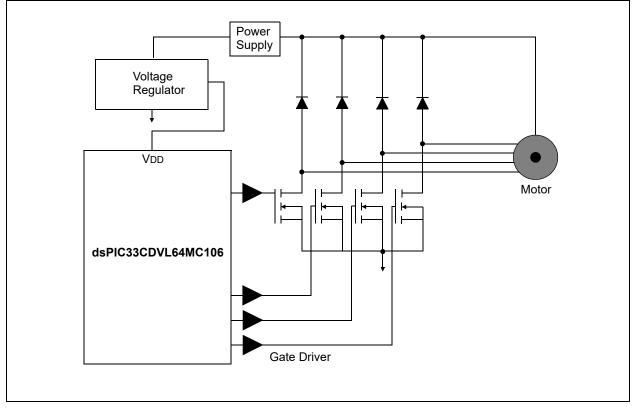

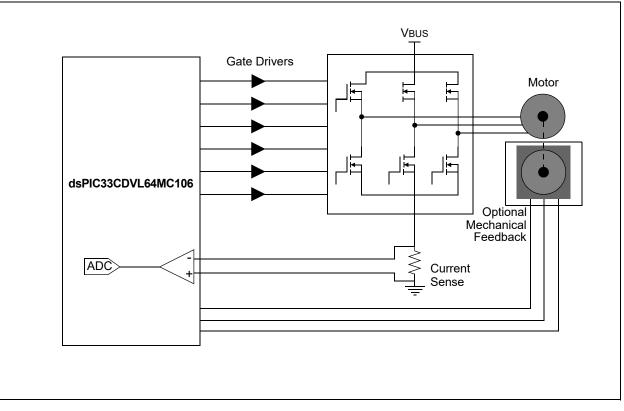

Examples of typical applications are shown in Figure 2-4 through Figure 2-6.

## dsPIC33CDVL64MC106 FAMILY

## FIGURE 2-5: STEPPER MOTOR

#### FIGURE 2-6: BLDC MOTOR

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33CDVL64MC106 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced CPU" (www.microchip.com/ DS70005158) in the "dsPIC33/PIC24 Family Reference Manual".

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

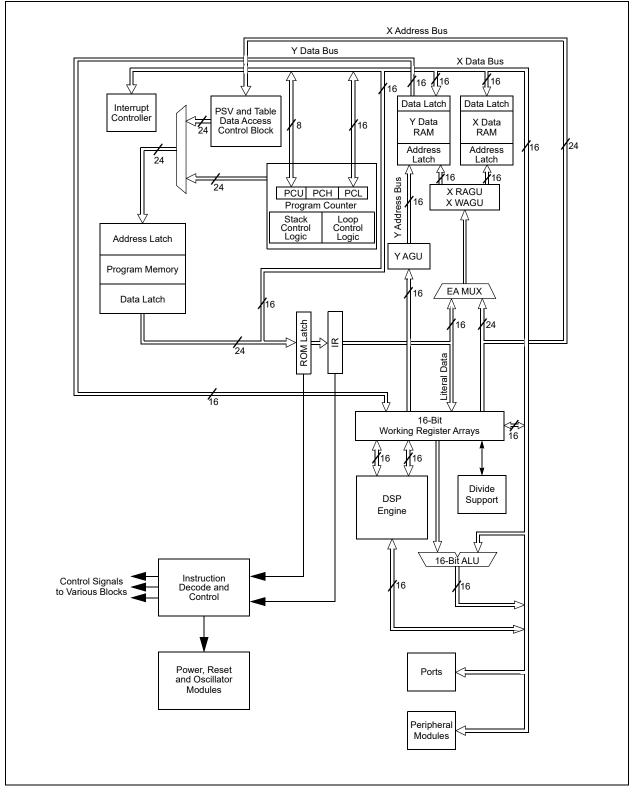

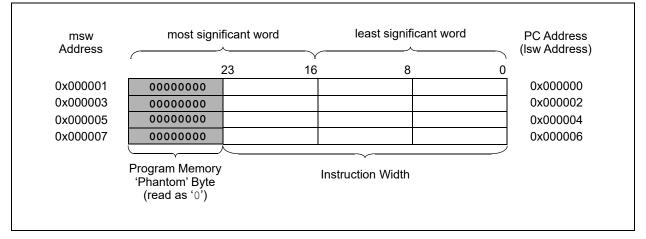

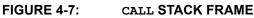

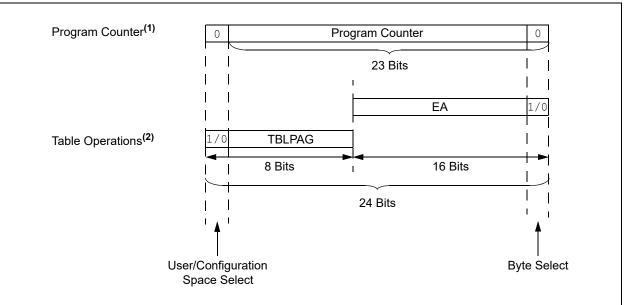

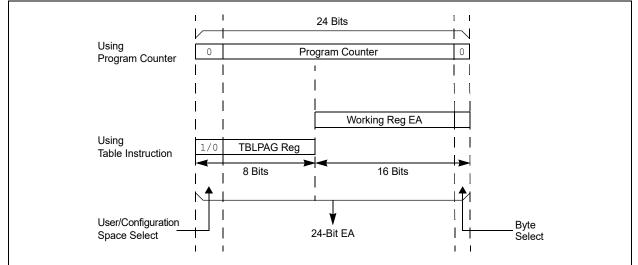

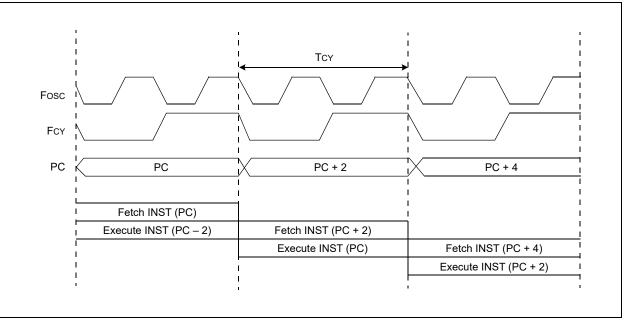

The dsPIC33CDVL64MC106 family CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for Digital Signal Processing (DSP). The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

#### 3.1 Registers

The dsPIC33CDVL64MC106 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The 16th Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

In addition, the dsPIC33CDVL64MC106 devices include four Alternate Working register sets, which consist of W0 through W14. The Alternate Working registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The Alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx[2:0] bits in the FALTREG Configuration register. The Alternate Working registers can also be accessed manually by using the CTXTSWP instruction. The CCTXI[2:0] and MCTXI[2:0] bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

## 3.2 Instruction Set

The instruction set for the dsPIC33CDVL64MC106 family has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

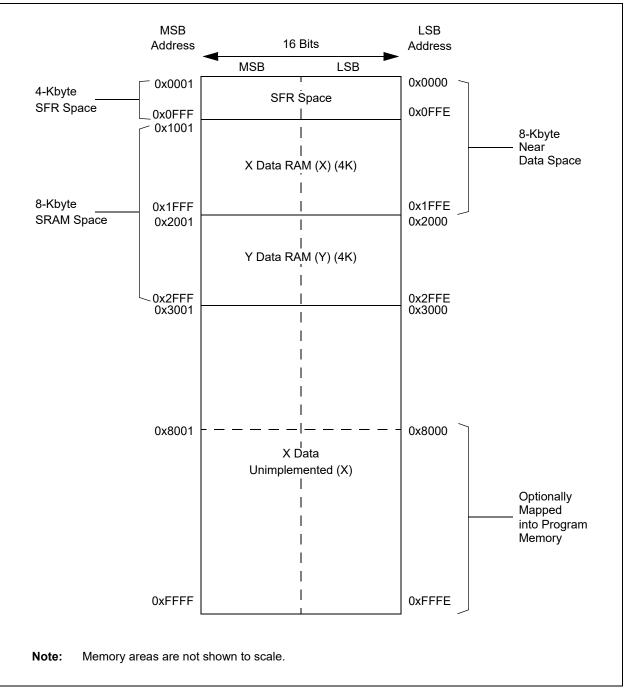

## 3.3 Data Space Addressing

The base Data Space can be addressed as up to 4K words or 8 Kbytes, and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which split the data address space into two parts. The X and Y Data Space boundary is device-specific.

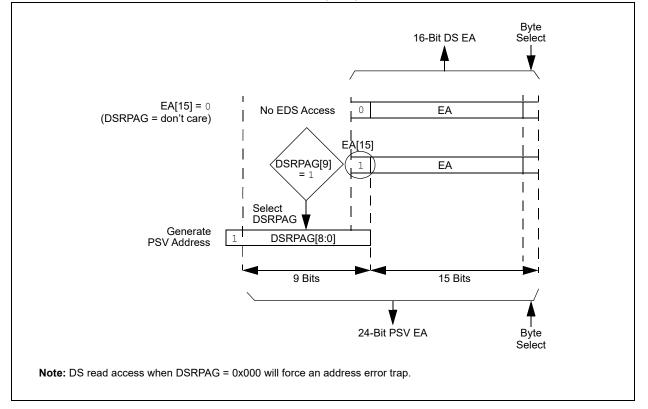

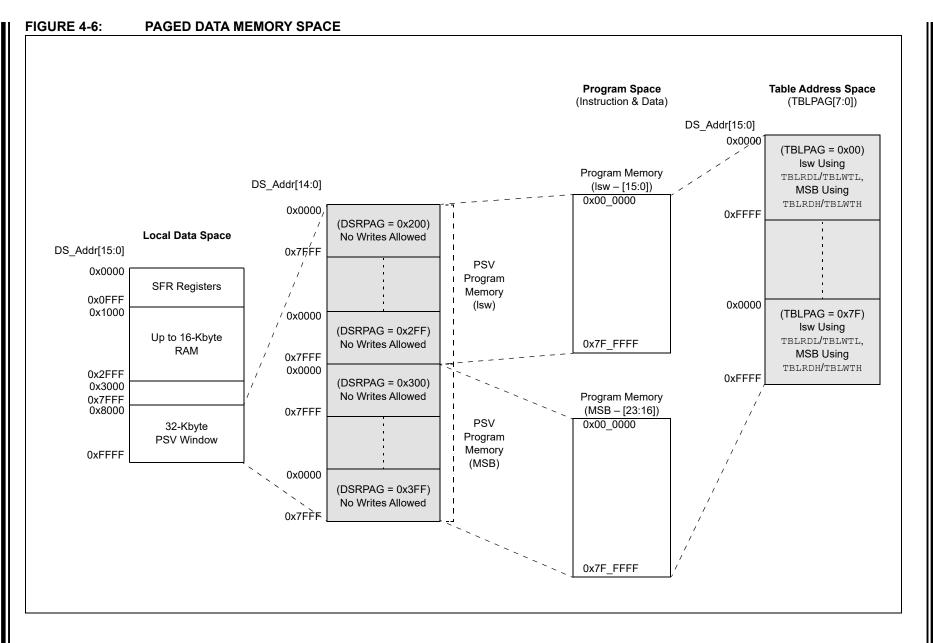

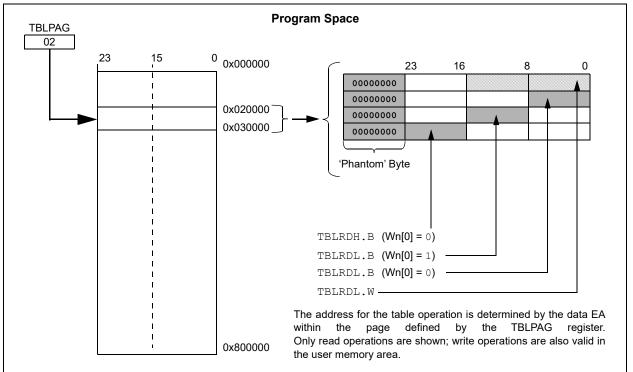

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Refer to "**Data Memory**" (www.microchip.com/DS70595) in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on PSV and table accesses.

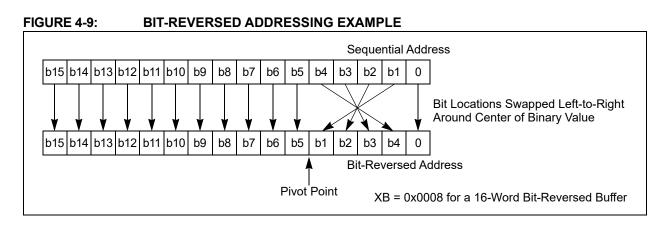

On the dsPIC33CDVL64MC106 devices, overheadfree circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

## dsPIC33CDVL64MC106 FAMILY

## FIGURE 3-1: dsPIC33CDVL64MC106 FAMILY CPU BLOCK DIAGRAM

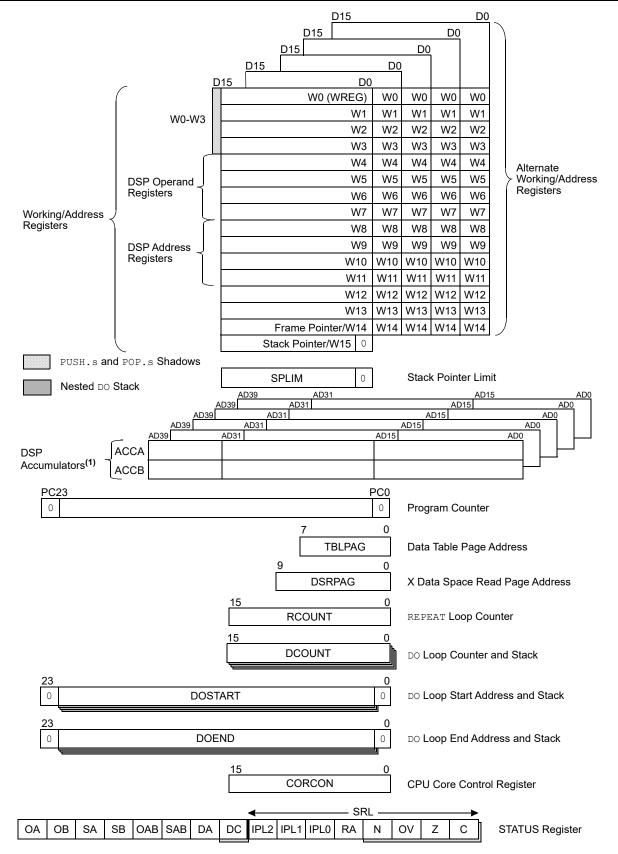

#### 3.4.1 PROGRAMMER'S MODEL

The programmer's model for the dsPIC33CDVL64MC106 devices is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33CDVL64MC106 devices contain control registers for Modulo Addressing, Bit-Reversed Addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Figure 3-2.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

| IADLL J-I. |                                          |

| Register(s) Name                  | Description                                                      |

|-----------------------------------|------------------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>     | Working Register Array                                           |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 1                               |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 2                               |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 3                               |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 4                               |

| ACCA, ACCB                        | 40-Bit DSP Accumulators (Additional Four Alternate Accumulators) |

| PC                                | 23-Bit Program Counter                                           |

| SR                                | ALU and DSP Engine STATUS Register                               |

| SPLIM                             | Stack Pointer Limit Value Register                               |

| TBLPAG                            | Table Memory Page Address Register                               |

| DSRPAG                            | Extended Data Space (EDS) Read Page Register                     |

| RCOUNT                            | REPEAT Loop Counter Register                                     |

| DCOUNT                            | DO Loop Counter Register                                         |

| DOSTARTH, DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)                    |

| DOENDH, DOENDL                    | DO Loop End Address Register (High and Low)                      |

| CORCON                            | Contains DSP Engine, DO Loop Control and Trap Status bits        |

**Note 1:** Memory-mapped W0 through W14 represent the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

## dsPIC33CDVL64MC106 FAMILY

#### 3.4.2 CPU RESOURCES

Many useful resources are provided on the main product page of the Microchip website for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 3.4.2.1 Key Resources

- "Enhanced CPU" (www.microchip.com/ DS70005158) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### 3.4.3 CPU CONTROL REGISTERS

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| bit 14<br>bit 13<br>bit 12<br>bit 11<br>bit 10<br>bit 9<br>bit 8                                                                                                                                        | OR<br>OA: Accumu<br>1 = Accumul<br>0 = Accumul<br>OB: Accumu                                                                                            | R/W-0 <sup>(2)</sup><br>IPL0 <sup>(1)</sup><br>C = Clearable<br>W = Writable<br>'1'= Bit is set<br>lator A Overflow<br>ator A has overfl<br>ator A has not o | bit<br>Status bit              | OAB<br>R/W-0<br>N<br>U = Unimplem<br>'0' = Bit is clea |                        | DA<br>R/W-0<br>Z                                    | DC<br>bit 8<br>R/W-0<br>C<br>bit 0 |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------|------------------------|-----------------------------------------------------|------------------------------------|--|--|--|--|--|