## High-Performance Audio Codec with Integrated HiFi 3z and FastDSP Cores

# **FEATURES**

- ► FastDSP<sup>™</sup> audio processing engine

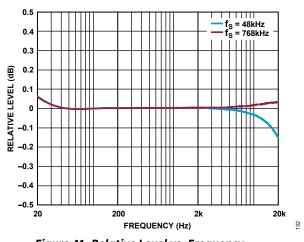

- Low latency at sample rates up to 768kHz

- Supports up to 128 instructions

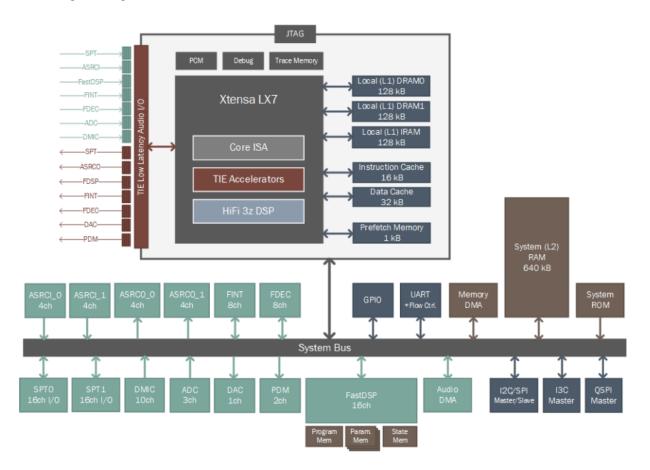

- ► Tensilica<sup>®</sup> HiFi 3z DSP with TIE accelerators

- Quad MAC/cycle and 1024kB total memory

- 2-way SIMD IEEE floating point multiplier

- Supports both 50MHz and 200MHz modes

- ► 5µs group delay (analog input to amp output)

- ► 768kHz sample rate (FastDSP bypass mode)

- Three low power 24-bit ADC record channels

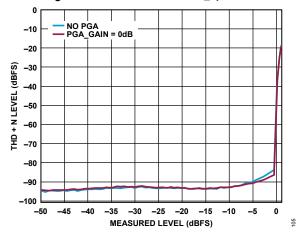

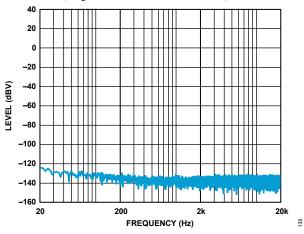

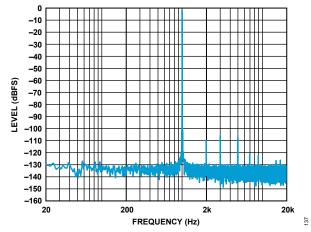

- ▶ 104dB SNR, -91dB THD+N, 0.6mW (PGA on)

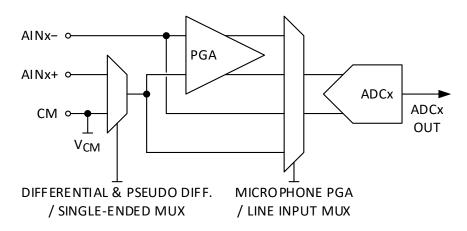

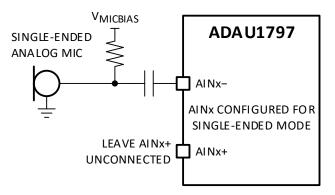

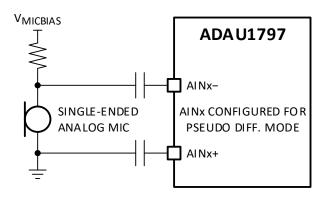

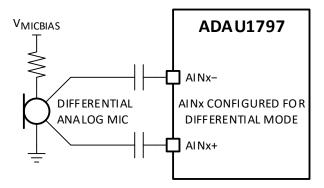

- Flexible differential or single-ended inputs

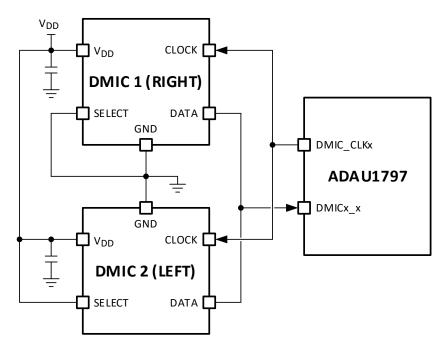

- ► Ten digital microphone (DMIC) input channels

- Two clock outputs (384kHz to 6.144MHz)

- Mono low power 24-bit DAC playback channel

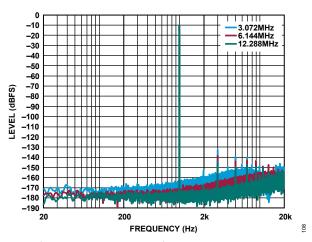

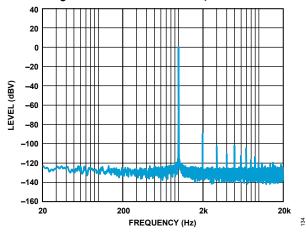

- 113dB SNR, -93dB THD+N, 1.4mW PQ

- ▶ High-efficiency, low-noise, Class-D amplifier

- ▶ Two high-performance PDM output channels

- Supports 3.072MHz or 6.144MHz clock rates

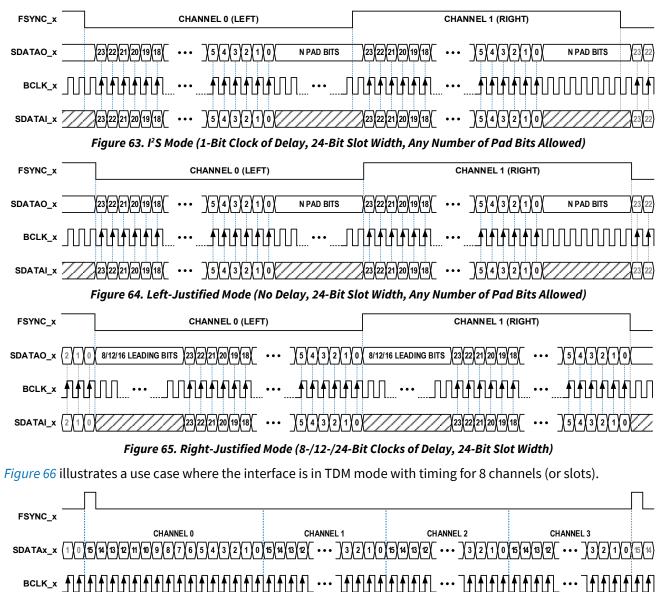

- ▶ Two 32-bit I2S/TDM serial audio data ports

- Sync clock frequencies from 8kHz to 768kHz

- Two full-duplex, 4-channel ASRCs

- Supports low power, single-supply mode (1.8V)

- Integrated LDO or switch-cap regulator

- Digital I/O supports 1.2V or 1.8V logic levels

- Digital Control and Communication interfaces

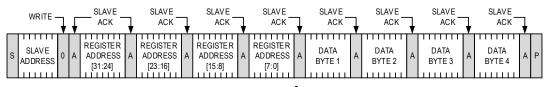

- ► I<sup>2</sup>C/SPI control and I<sup>3</sup>C combined interfaces

- Master QSPI, UART, and JTAG interfaces

- Supports self-boot from QSPI Flash/EEPROM

- Multi-purpose I/O pins for GPIO / IRQ support

# **APPLICATIONS**

- True wireless stereo (TWS) ANC headphones

- Over-ear stereo ANC headphones

- VR and AR headsets and wearable devices

- Hearing assist and PSAP devices

- Soundbar and smart speaker systems

- Gaming devices and tablets

## **GENERAL DESCRIPTION**

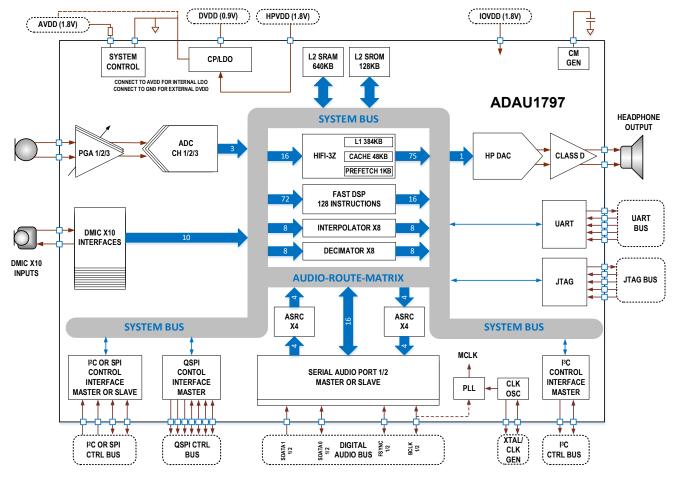

The device is a low power, high-performance audio codec that provides three analog input channels, ten DMIC input channels, two PDM output channels, and one high-efficiency Class-D amplifier output channel.

The device features a low power HiFi 3z audio DSP core and a low-latency FastDSP core. The audio DSP cores paired with high-fidelity audio data converters are ideal for applications like noise cancellation, transparency, personal sound amplification, and voice processing.

When operating in low-power mode, the DSP cores are optimized for small form factor applications such as true wireless stereo (TWS) headphones. In this mode, the device delivers the right level of processing power while still minimizing power consumption to extend play time.

The device has the flexibility to also support applications requiring additional processing capability such as overear headphones, VR and AR headsets, wearables, hearing assist, and PSAP devices. In high-performance mode, the HiFi 3z core is boosted from 50Mhz to 200MHz, and the FastDSP supports double the number of instructions (up from 64 to 128). This increased processing capability can either be used to offload cycles from the host processor or enable a lower-cost host processor without requiring an additional external audio DSP or MCU.

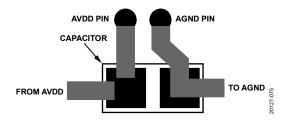

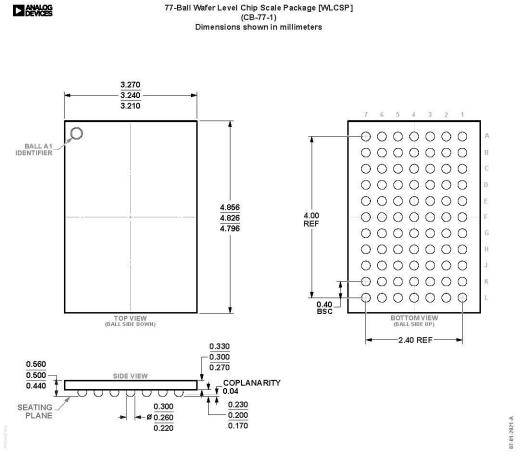

The device supports a -40°C to +85°C temperature range and is available in a space-saving 77-ball WLCSP package (0.4mm pitch, 3.24mm × 4.83mm)

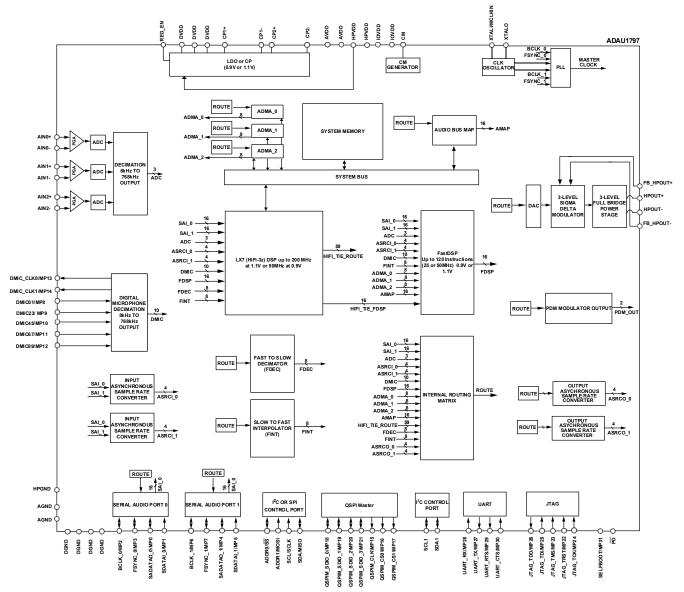

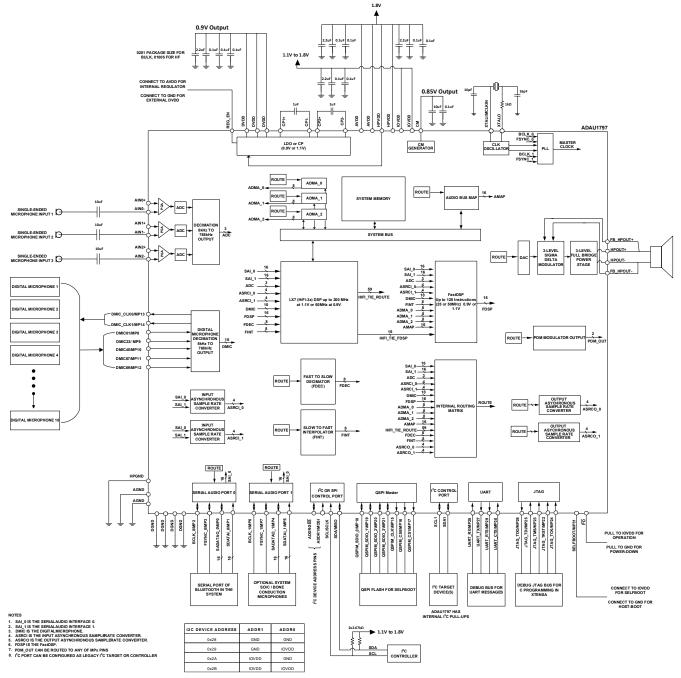

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Top Level Block Diagram

# **REVISION HISTORY**

9/2023-Revision 0: Initial Version

# **SPECIFICATIONS**

#### Table 1. Electrical Characteristics

| PARAMETER             | SYMBOL             | CONDITION                     | S/COMMENTS       | MIN  | ΤΥΡ   | МАХ  | UNITS |

|-----------------------|--------------------|-------------------------------|------------------|------|-------|------|-------|

| POWER SUPPLY VOLTAG   | E RANGE            |                               |                  |      |       |      |       |

| AVDD Voltage          | V <sub>AVDD</sub>  |                               |                  | 1.7  | 1.8   | 1.98 | V     |

| AVDD Undervoltage     |                    |                               |                  |      | 1.55  |      | V     |

| Trip Point            |                    |                               |                  |      | 1.55  |      | v     |

| HPVDD Voltage         | V <sub>HPVDD</sub> |                               |                  | 1.7  | 1.8   | 1.98 | V     |

| HPVDD Undervoltage    |                    |                               |                  |      | 1.55  |      | V     |

| Trip Point            |                    |                               |                  |      | 1.55  |      | v     |

|                       |                    | Integrated supply             | HIFI_SPEED = 0   | 0.85 | 0.9   | 0.99 |       |

| DVDD Voltage          | V <sub>DVDD</sub>  | External supply               | HIFI_SPEED = 0   | 0.85 | 0.9   | 1.21 | V     |

|                       |                    | Integrated or external supply | HIFI_SPEED = 1   | 1.05 | 1.1   | 1.21 |       |

| IOVDD Voltage         | VIOVDD             |                               |                  | 1.1  | 1.8   | 1.98 | V     |

| ANALOG-TO-DIGITAL COI | NVERTERS (A        | DCs)                          |                  |      |       |      | 1     |

| ADC Resolution        |                    |                               |                  |      | 24    |      | Bits  |

| Digital Volume Step   |                    |                               |                  |      | 0.375 |      | dB    |

| Digital Volume Range  |                    |                               |                  | -71  |       | +24  | dB    |

| Digital Volume Ramp   |                    |                               |                  |      | 4.5   |      | dB/ms |

| Rate                  |                    |                               |                  |      | 4.5   |      | ub/ms |

| ANALOG INPUT RESISTAI | NCE (AINPx/A       | INNx R <sub>IN</sub> )        |                  |      |       |      |       |

| Input Disabled        |                    |                               |                  |      | ≥1    |      | MΩ    |

| Direct ADC Input Mode |                    |                               |                  |      | 21    |      | kΩ    |

|                       |                    |                               | -9dB attenuation |      | 33.7  |      |       |

|                       |                    | Differential                  | 0dB gain         |      | 22.5  |      |       |

|                       |                    | input mode                    | 6dB gain         |      | 15    |      |       |

| Programmable Gain     |                    |                               | 28.5dB gain      |      | 1.5   |      | kΩ    |

| Amplifier Input Mode  |                    | Single-ended or               | -9dB attenuation |      | 26.5  |      | 1/22  |

|                       |                    | pseudo-diff.                  | 0dB gain         |      | 15    |      | ļ     |

|                       |                    | input mode                    | 6dB gain         |      | 9.2   |      |       |

|                       |                    |                               | 28.5dB gain      |      | 0.9   |      |       |

| PARAMETER                     | SYMBOL      | CONDITIONS                      | 5/COMMENTS              | MIN     | ΤΥΡ          | МАХ | UNITS            |

|-------------------------------|-------------|---------------------------------|-------------------------|---------|--------------|-----|------------------|

| SINGLE-ENDED OR PSEU          | DO-DIFFEREN | ITIAL LINE INPUT M              | ODE (DIRECT TO AD       | C INPUT | .)           |     |                  |

| Full-Scale Input              |             | Input loval for a Os            |                         |         | 0.64         |     | V <sub>RMS</sub> |

| Voltage                       |             | Input level for a Oc            | IBFS output             |         | 1.8          |     | V <sub>P-P</sub> |

|                               |             | A-weighted filter,              | Normal                  |         |              |     |                  |

| Dynamic Range <sup>(1)</sup>  |             | f <sub>IN</sub> = 1kHz,         | operation mode          |         | 100          |     | dB               |

|                               |             | -60dBFS output                  | (default)               |         |              |     |                  |

|                               |             | A-weighted filter,              | Extreme power-          |         |              |     |                  |

|                               |             | $f_{IN} = 1 kHz$ ,              | saving mode             |         | 96           |     |                  |

|                               |             | -60dBFS output                  | Saving mode             |         |              |     |                  |

| Dynamic Range <sup>(1)</sup>  |             |                                 | Normal                  |         |              |     | dB               |

| - )                           |             | Unweighted                      | operation mode          |         | 97           |     |                  |

|                               |             | filter, f <sub>IN</sub> = 1kHz, | (default)               |         |              |     |                  |

|                               |             | -60dBFS output                  | Extreme power-          |         | 93           |     |                  |

|                               |             |                                 | saving mode             |         |              |     |                  |

| Signal-to-Noise Ratio         |             | Normal                          | A-weighted filter       |         | 100          |     | dB               |

| (SNR) <sup>(2)</sup>          |             | operation mode                  | Unweighted filter       |         | 97           |     |                  |

| THD+N Level <sup>(3)</sup>    |             | f <sub>IN</sub> = 1kHz, -1dBFS  | output, normal          |         | -87          |     | dBFS             |

|                               |             | operation mode                  |                         |         |              |     |                  |

| Interchannel Gain<br>Mismatch |             |                                 |                         |         | 0.04         |     | dB               |

| Offset Error                  |             |                                 |                         |         | ±0.1         |     | mV               |

| Gain Error                    |             |                                 |                         |         | ±0.1<br>±0.2 |     | dB               |

| Interchannel Isolation        |             | C = 10µF                        |                         |         | ±0.2         |     | dB               |

|                               |             | $C_{CM} = 10 \mu F$             | 6 4111                  |         |              |     | uв               |

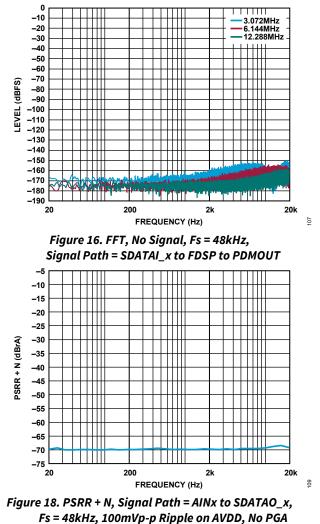

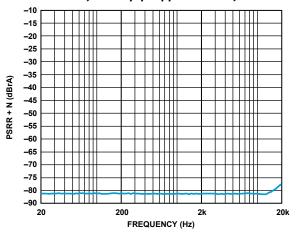

| Power Supply                  |             | $C_{CM} = 10 \mu F$ ,           | $f_{IN} = 1 kHz$        |         | 70           |     | dB               |

| Rejection Ratio (PSRR)        |             | 100mV <sub>P-P</sub> signal     | f <sub>IN</sub> = 10kHz |         | 50           |     |                  |

| DIFFERENTIAL LINE INPU        | T MODE (DIR | ECT TO ADC INPUT                |                         |         |              |     |                  |

| Full-Scale Input              |             | Input level for a Oc            | IBFS output             |         | 1.08         |     | V <sub>RMS</sub> |

| Voltage                       |             | •                               |                         |         | 3.05         |     | V <sub>P-P</sub> |

|                               |             | A                               | Normal                  |         |              |     |                  |

| Dynamic Range <sup>(1)</sup>  |             | A-weighted filter,              | operation mode          |         | 106          |     |                  |

|                               |             | $f_{IN} = 1 kHz$ ,              | (default)               |         |              |     | dB               |

|                               |             | -60dBFS output                  | Extreme power-          |         | 100          |     |                  |

|                               |             |                                 | saving mode             |         |              |     |                  |

$(Supply voltages V_{AVDD} = V_{HPVDD} = V_{IOVDD} = 1.8V \text{ and } V_{DVDD} = 0.9V \text{ (external), Supply bypass } C_{AVDD} = C_{HPVDD} = C_{IOVDD} = 2.2 \mu F + 2 \times 0.1 \mu F \text{ and } C_{DVDD} = 2.2 \mu F + 3 \times 0.1 \mu F, \text{ Master clock} = 24.576 \text{ MHz}, \text{ Serial audio data port sample rate} = 48 \text{ Hz}, \text{ Audio data word width} = 24 \text{ -bits}, \text{ Headphone amplifier load} = 16\Omega + 33 \mu \text{ H}, \text{ default analog power modes}, \text{ AC measurement bandwidth} = 20 \text{ Hz to } 20 \text{ Hz}, \text{ Ambient temperature } (T_A) = -40^{\circ}\text{C to } +85^{\circ}\text{C with typical values at} +25^{\circ}\text{C unless otherwise noted}, \text{ see the } System Block Diagram} \text{ for other external component values.}$

| PARAMETER                     | SYMBOL      | CONDITIONS                                                       | 5/COMMENTS                            | MIN | ΤΥΡ  | МАХ | UNITS            |

|-------------------------------|-------------|------------------------------------------------------------------|---------------------------------------|-----|------|-----|------------------|

|                               |             | Unweighted<br>filter, f <sub>IN</sub> = 1kHz,                    | Normal<br>operation mode<br>(default) |     | 103  |     |                  |

|                               |             | -60dBFS output                                                   | Extreme power-<br>saving mode         |     | 97   |     |                  |

| Signal-to-Noise Ratio         |             | Normal                                                           | A-weighted filter                     |     | 106  |     | dB               |

| (SNR) <sup>(2)</sup>          |             | operation mode                                                   | Unweighted filter                     |     | 103  |     | ЧЪ               |

| THD+N Level <sup>(3)</sup>    |             | f <sub>IN</sub> = 1kHz, -1dBFS<br>operation mode                 | output, normal                        |     | -93  |     | dBFS             |

| CMRR                          |             |                                                                  |                                       |     | 60   |     | dB               |

| Interchannel Gain<br>Mismatch |             |                                                                  |                                       |     | 0.04 |     | dB               |

| Offset Error                  |             |                                                                  |                                       |     | ±0.1 |     | mV               |

| Gain Error                    |             |                                                                  |                                       |     | ±0.2 |     | dB               |

| Interchannel Isolation        |             | $C_{CM} = 10 \mu F$                                              |                                       |     | 100  |     | dB               |

| Power Supply                  |             | $C_{CM} = 10 \mu F$ ,                                            | f <sub>IN</sub> = 1kHz                |     | 70   |     | db               |

| Rejection Ratio (PSRR)        |             | 100mV <sub>P-P</sub> signal                                      | f <sub>IN</sub> = 10kHz               |     | 50   |     | dB               |

| SINGLE-ENDED OR PSEUD         | OO-DIFFEREN | TIAL PGA INPUT M                                                 | ODE (PGA ENABLED                      | )   |      |     | L                |

| Full-Scale Input              |             | Input level for a Oc                                             |                                       |     | 0.54 |     | $V_{\text{RMS}}$ |

| Voltage                       |             | Input level for a oc                                             | ibrs output                           |     | 1.53 |     | V <sub>P-P</sub> |

|                               |             | A-weighted filter,<br>f <sub>IN</sub> = 1kHz,<br>-60dBFS output, | Normal<br>operation mode<br>(default) |     | 99   |     |                  |

| Dynamic Range <sup>(1)</sup>  |             | +6dB PGA gain                                                    | Extreme power-<br>saving mode         |     | 98   |     | dB               |

| Dynamic Kange                 |             | Unweighted<br>filter, $f_{IN} = 1$ kHz,                          | Normal<br>operation mode<br>(default) |     | 96   |     | UD               |

|                               |             | -60dBFS output,<br>+6dB PGA gain                                 | Extreme power-<br>saving mode         |     | 94   |     |                  |

| Signal-to-Noise Ratio         |             | +6dB PGA gain,                                                   | A-weighted filter                     |     | 98   |     |                  |

| (SNR) <sup>(2)</sup>          |             | normal operation mode                                            | Unweighted filter                     |     | 95   |     | dB               |

| THD+N Level <sup>(3)</sup>    |             | f <sub>IN</sub> = 1kHz, -1dBFS<br>gain, normal opera             | •                                     |     | -90  |     | dBFS             |

| PARAMETER                    | SYMBOL      | CONDITIONS                      | 5/COMMENTS                                 | MIN | ΤΥΡ   | МАХ    | UNITS            |

|------------------------------|-------------|---------------------------------|--------------------------------------------|-----|-------|--------|------------------|

| PGA Gain Range               |             |                                 |                                            | -9  |       | +29.25 | dB               |

| PGA Gain Step Size           |             |                                 |                                            |     | 0.75  |        | dB               |

| PGA Gain Variation           |             |                                 |                                            |     | 0.05  |        | dB               |

| with 0dB Setting             |             |                                 |                                            |     | 0.05  |        | uБ               |

| PGA Gain Variation           |             |                                 |                                            |     | 0.15  |        | dB               |

| with +24dB Setting           |             |                                 |                                            |     | 0.15  |        | db               |

| Interchannel Gain            |             |                                 |                                            |     | 0.005 |        | dB               |

| Mismatch                     |             |                                 |                                            |     |       |        | db               |

| Offset Error                 |             |                                 |                                            |     | ±0.1  |        | mV               |

| Gain Error                   |             |                                 |                                            |     | ±0.2  |        | dB               |

| Interchannel Isolation       |             | $C_{CM} = 10 \mu F$             |                                            |     | 100   |        | dB               |

| Power Supply                 |             | C <sub>CM</sub> = 10μF, 100mV   | ′ <sub>P-P</sub> signal, f <sub>IN</sub> = |     | 70    |        | dB               |

| Rejection Ratio (PSRR)       |             | 1kHz                            |                                            |     | 10    |        | uв               |

| IFFERENTIAL PGA INPU         | T MODE (PGA | ENABLED)                        |                                            |     |       |        |                  |

| Full-Scale Input             |             | Input level for a Oc            |                                            |     | 1.08  |        | $V_{\text{RMS}}$ |

| Voltage                      |             |                                 | ibro output                                |     | 3.05  |        | $V_{P-P}$        |

|                              |             | A-weighted filter,              |                                            |     |       |        |                  |

|                              |             | f <sub>IN</sub> = 1kHz,         | Normal                                     |     | 104   |        |                  |

|                              |             | -60dBFS output,                 | operation mode                             |     | 104   |        |                  |

|                              |             | 0dB PGA gain                    |                                            |     |       |        |                  |

|                              |             | A-weight(RMS)ed                 |                                            |     |       |        |                  |

| Dynamic Range <sup>(1)</sup> |             | filter, f <sub>IN</sub> = 1kHz, | Extreme power-                             |     | 100   |        | dB               |

| Dynamic Range                |             | -60dBFS output,                 | saving mode                                |     | 100   |        | иБ               |

|                              |             | 0dB PGA gain                    |                                            |     |       |        |                  |

|                              |             | Unweighted                      | Normal                                     |     | 100   |        |                  |

|                              |             | filter, f <sub>IN</sub> = 1kHz, | operation mode                             |     | 100   |        |                  |

|                              |             | -60dBFS output,                 | Extreme power-                             |     | 97    |        |                  |

|                              |             | 0dB PGA gain                    | saving mode                                |     | 51    |        |                  |

| Signal-to-Noise Ratio        |             | 0dB PGA gain,                   | A-weighted filter                          |     | 103   |        |                  |

| (SNR) <sup>(2)</sup>         |             | normal operation                | Unweighted filter                          |     | 100   |        | dB               |

|                              |             | mode                            | onweighted iller                           |     | 100   |        |                  |

| THD+N Level <sup>(3)</sup>   |             | f <sub>IN</sub> = 1kHz, -1dBFS  | output, 0dB PGA                            |     | -93   |        | dBFS             |

|                              |             | gain normal oper                | ation modo                                 |     | -55   |        | 0013             |

gain, normal operation mode

PGA Gain Range

PGA Gain Step Size

dB dB

+30

-6

0.75

| PARAMETER                    | SYMBOL      | CONDITIO                                               | NS/COMMENTS                                 | MIN | ΤΥΡ   | МАХ | UNITS            |

|------------------------------|-------------|--------------------------------------------------------|---------------------------------------------|-----|-------|-----|------------------|

| PGA Gain Variation           |             |                                                        |                                             |     | 0.05  |     | dD               |

| With 0dB Setting             |             |                                                        |                                             |     | 0.05  |     | dB               |

| PGA Gain Variation           |             |                                                        |                                             |     | 0.15  |     | dB               |

| With +24dB Setting           |             |                                                        |                                             |     | 0.15  |     | uВ               |

| CMRR                         |             | 1kHz input frequ                                       | iency                                       |     | 60    |     | dB               |

| Interchannel Gain            |             |                                                        |                                             |     | 0.005 |     | dB               |

| Mismatch                     |             |                                                        |                                             |     | 0.005 |     | UD               |

| Offset Error                 |             |                                                        |                                             |     | ±0.1  |     | mV               |

| Gain Error                   |             |                                                        |                                             |     | ±0.2  |     | dB               |

| Interchannel Isolation       |             | $C_{CM} = 10 \mu F$                                    |                                             |     | 100   |     | dB               |

| Power Supply                 |             | C <sub>CM</sub> = 10μF, 100n                           | ηV <sub>P-P</sub> signal, f <sub>IN</sub> = | 70  |       |     | ЧD               |

| Rejection Ratio (PSRR)       |             | 1kHz                                                   |                                             | 70  |       | dB  |                  |

| DIGITAL-TO-ANALOG CON        | IVERTER (DA | C)                                                     | •                                           |     |       | I   |                  |

| DAC Resolution               |             |                                                        |                                             |     | 24    |     | Bits             |

| Digital Volume Step          |             |                                                        |                                             |     | 0.375 |     | dB               |

| Digital Volume Range         |             |                                                        |                                             | -71 |       | +24 | dB               |

| Digital Volume Ramp          |             |                                                        |                                             |     | 4.5   |     | dD/ma            |

| Rate                         |             |                                                        |                                             |     | 4.5   |     | dB/ms            |

| DIFFERENTIAL HEADPHO         | NE OUTPUT   |                                                        |                                             |     |       |     |                  |

| Full-Scale Output            |             | 0dBFS input to a                                       | nalog output                                |     | 1.15  |     | V <sub>RMS</sub> |

| Voltage                      |             | channel, 16Ω loa                                       | nd                                          |     | 1.15  |     | V RMS            |

|                              |             | A-weighted filter                                      | r, f <sub>IN</sub> = 1kHz,                  |     | 113   |     |                  |

| Dynamic Dango <sup>(1)</sup> |             | -60dBFS input                                          |                                             |     | 115   |     | dB               |

| Dynamic Range <sup>(1)</sup> |             | Unweighted filte                                       | er, f <sub>IN</sub> = 1kHz,                 |     | 110   |     | uв               |

|                              |             | -60dBFS input                                          |                                             |     | 110   |     |                  |

| Signal-to-Noise Ratio        |             | A-weighted filter                                      | -                                           |     | 113   |     | ٦D               |

| (SNR) <sup>(2)</sup>         |             | Unweighted filte                                       | r                                           |     | 110   |     | dB               |

| Output Noice                 |             | A-weighted filter                                      | , zero code digital                         |     | 2 57  |     |                  |

| Output Noise                 |             | input                                                  |                                             |     | 2.57  |     | $\mu V_{RMS}$    |

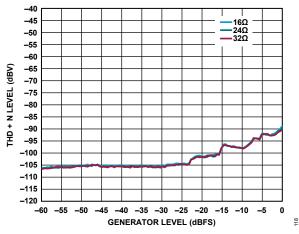

| THD+N Level <sup>(3)</sup>   |             | -2dBFS, 16Ω load                                       | t                                           |     | -90   |     | dBV              |

|                              |             | 32Ω load                                               | $P_{OUT} = 1mW$                             |     | -83   |     |                  |

|                              |             |                                                        | P <sub>OUT</sub> = 30mW                     |     | -90   |     |                  |

| THD+N Ratio                  |             | $24\Omega \text{ load, P}_{\text{OUT}} = 40\text{mW}$  |                                             |     | -90   |     | dB               |

|                              |             | $16\Omega \text{ load, } P_{\text{OUT}} = 60\text{mW}$ |                                             |     | -90   |     |                  |

| PARAMETER                   | SYMBOL | CONDITION                             | S/COMMENTS              | MIN   | ΤΥΡ     | MAX | UNITS |

|-----------------------------|--------|---------------------------------------|-------------------------|-------|---------|-----|-------|

| Headphone Output            |        | HPVDD = 1.8V,<br><0.1% THD+N<br>ratio | 32Ω load                |       | 40      |     |       |

| Power                       |        | HPVDD = 1.8V,                         | 24Ω load                |       | 54      |     | mW    |

|                             |        | <0.1% THD+N<br>ratio                  | 16Ω load                |       | 80      |     |       |

| Gain Error                  |        |                                       |                         |       | ±2.5    |     | %     |

| DC Offset                   |        |                                       |                         |       | ±0.1    |     | mV    |

| Pop-Click Level             |        | A-weighted peak t                     | ransient voltage        |       | 0.5     |     | mV₽   |

| Peak Output Current         |        |                                       |                         |       |         | 350 | mA    |

| Minimum Load<br>Resistance  |        |                                       |                         | 6     |         |     | Ω     |

| Minimum Load<br>Inductance  |        |                                       |                         | 5     |         |     | μH    |

| Maximum Load<br>Capacitance |        | From HPOUTP or<br>HPVDD               | HPOUTN to GND or        |       |         | 470 | pF    |

| Power Efficiency            |        | 55mW into a 16Ω l                     | oad                     |       | 90      |     | %     |

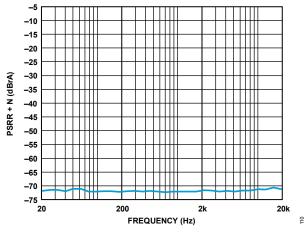

|                             |        |                                       | f <sub>IN</sub> = 1kHz  |       | 89      |     |       |

| PSRR                        |        | 100mV <sub>P-P</sub> signal           | f <sub>IN</sub> = 10kHz |       | 75      |     | dB    |

| COMMON MODE REFERE          | NCE    |                                       |                         |       |         |     |       |

| Output                      |        |                                       |                         |       | 0.85    |     | V     |

| Source Impedance            |        |                                       |                         |       | 5       |     | kΩ    |

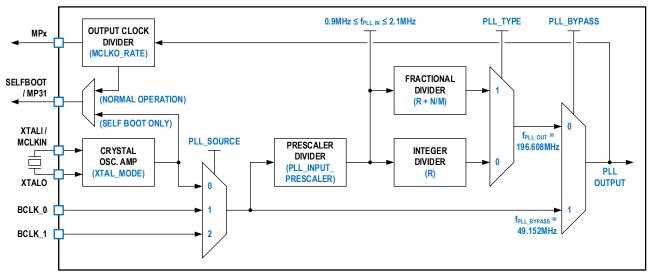

| PHASED-LOCKED LOOP          | PLL)   |                                       |                         |       |         |     |       |

| Input Frequency             |        | After input presca                    | le                      | 0.9   |         | 2.1 | MHz   |

| Output Frequency            |        |                                       |                         | 195.5 | 196.608 | 198 | MHz   |

| Fractional Limits           |        | Fractional mode, f<br>(N/M ratio)     | fraction portion        | 0.1   |         | 0.9 |       |

| Integer Limits              |        | Fractional mode, i                    | integer portion         | 2     |         | 256 |       |

| Input Pre-Divide            |        |                                       |                         | 1     |         | 32  |       |

| Lock Time                   |        | 1.024MHz input                        |                         |       |         | 1   | ms    |

| PLL Bypass XTAL             |        |                                       |                         |       | 10 150  |     | МЦ≁   |

| Frequency                   |        |                                       |                         |       | 49.152  |     | MHz   |

| INTEGRATED LDO REGUI        | ATOR   |                                       |                         |       |         |     |       |

| Line Regulation             |        |                                       |                         |       | 1.1     |     | mV/V  |

| Load Regulation             |        |                                       |                         |       | 0.3     |     | mV/mA |

| PARAMETER                  | SYMBOL          | CONDITIONS/COMMENTS                                                          |                                                                          | MIN                          | ΤΥΡ                          | MAX                         | UNITS |

|----------------------------|-----------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|------------------------------|-----------------------------|-------|

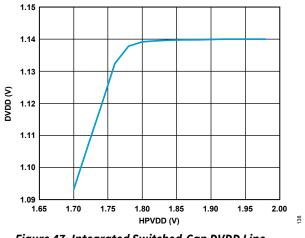

| INTEGRATED SWITCHED        | -CAP REGULA     | TOR                                                                          |                                                                          |                              |                              |                             |       |

| Line Regulation            |                 | V <sub>HPVDD</sub> = 1.8V, see <i>H</i><br>HPVDD range                       | Figure 47 for full                                                       |                              | 5                            |                             | mV/V  |

| Load Regulation            |                 |                                                                              |                                                                          |                              | 0.3                          |                             | mV/mA |

| CRYSTAL AMPLIFIER          |                 |                                                                              |                                                                          | •                            |                              |                             |       |

| Jitter                     |                 |                                                                              |                                                                          |                              | 270                          | 500                         | ps    |

| Frequency Range            |                 |                                                                              |                                                                          | 0.9                          |                              | 50                          | MHz   |

| Load Capacitance           |                 |                                                                              |                                                                          |                              |                              | 20                          | pF    |

| DIGITAL INPUT AND OUT      | PUT             | ·                                                                            |                                                                          |                              |                              |                             |       |

| Input Voltage High         | V <sub>IH</sub> |                                                                              |                                                                          | 0.7 ×<br>V <sub>IOVDD</sub>  |                              |                             | V     |

| Input Voltage Low          | V <sub>IL</sub> |                                                                              |                                                                          |                              |                              | 0.3×<br>V <sub>IOVDD</sub>  | V     |

| Input Leakage High         | I <sub>IH</sub> | V <sub>IOVDD</sub> = 1.8V                                                    | V <sub>IH</sub> = 1.1V                                                   |                              |                              | 10                          | μA    |

| Input Leakage Low          | I <sub>IL</sub> | $V_{IOVDD} = 1.8V$                                                           | V <sub>II</sub> = 0.45V                                                  |                              |                              | 10                          | μA    |

| Output Voltage High        | V <sub>OH</sub> |                                                                              | 12                                                                       | 0.71 ×<br>V <sub>IOVDD</sub> | 0.83 ×<br>V <sub>IOVDD</sub> | -                           | V     |

| Output High Current        |                 | Low output drives                                                            | strength                                                                 |                              | 1                            |                             |       |

| Drive Strength             | I <sub>он</sub> | High output drive                                                            |                                                                          |                              | 3                            |                             | mA    |

| Output Voltage Low         | V <sub>OL</sub> |                                                                              |                                                                          |                              | 0.1×<br>V <sub>IOVDD</sub>   | 0.3 ×<br>V <sub>IOVDD</sub> | V     |

| Output Low Current         |                 | Low output drives                                                            | strength                                                                 |                              | 1                            | -                           |       |

| Drive Strength             | I <sub>OL</sub> | High output drive                                                            | strength                                                                 |                              | 3                            |                             | mA    |

| Input Capacitance          |                 |                                                                              |                                                                          |                              |                              | 5                           | рF    |

| SERIAL AUDIO DATA POP      | RT DIGITAL IN   | TERFACE CURRENT                                                              | 1                                                                        | •                            |                              |                             |       |

|                            |                 | Single serial audic<br>(SPTx), crystal osc<br>(24.576MHz) V <sub>IOVDE</sub> |                                                                          |                              | 0.422                        |                             |       |

| Digital Current<br>(IOVDD) |                 | Single serial<br>audio data port<br>enabled (SPTx),                          | Slave mode, f <sub>S</sub> =<br>48kHz, f <sub>BCLK</sub> =<br>3.072MHz   |                              | 0.475                        |                             | mA    |

|                            |                 | crystal oscillator<br>enabled<br>(24.576MHz),                                | Slave mode, f <sub>s</sub> =<br>192kHz, f <sub>BCLK</sub> =<br>12.288MHz |                              | 0.481                        |                             |       |

| PARAMETER                      | SYMBOL       | CONDITION                                     | S/COMMENTS                                                                | MIN  | ΤΥΡ   | МАХ                        | UNITS |

|--------------------------------|--------------|-----------------------------------------------|---------------------------------------------------------------------------|------|-------|----------------------------|-------|

|                                |              | 25pF line loads,<br>V <sub>IOVDD</sub> = 1.8V | Master mode, f <sub>s</sub> =<br>48kHz, f <sub>BCLK</sub> =<br>3.072MHz   |      | 0.697 |                            |       |

|                                |              |                                               | Master mode, f <sub>s</sub> =<br>192kHz, f <sub>BCLK</sub> =<br>12.288MHz |      | 1.336 |                            |       |

| ADC INPUT TO DAC OUTP          | UT SIGNAL P  | ATH                                           |                                                                           |      |       |                            |       |

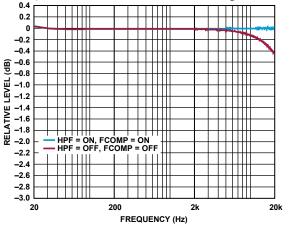

| Pass-Band Ripple               |              | DC to 20kHz Band<br>ADCxx_FCOMP = 1           | width, f <sub>s</sub> = 192kHz,<br>., DAC_FCOMP = 1                       |      |       | ±0.02                      | dB    |

|                                |              | f <sub>s</sub> = 192kHz                       |                                                                           |      | 12.9  |                            |       |

| Group Delay <sup>(4)</sup>     |              | f <sub>s</sub> = 384kHz                       |                                                                           |      | 7.5   |                            | μs    |

|                                |              | f <sub>s</sub> = 768kHz                       |                                                                           |      | 5     |                            |       |

| ASYNCHRONOUS SAMPL             | E RATE CONVI | ERTERS                                        |                                                                           |      |       |                            |       |

|                                |              | f <sub>LRCLK</sub> < 63kHz                    |                                                                           |      |       | 0.475<br>x f <sub>s</sub>  |       |

| Pass-Band Frequency            |              | 63kHz≤f <sub>LRCLK</sub> <11                  | 2kHz                                                                      |      |       | 0.4286<br>x fs             | kHz   |

|                                |              | 112kHz ≤ f <sub>LRCLK</sub>                   |                                                                           |      |       | 0.4286<br>x f <sub>s</sub> |       |

| Audio-Band Ripple              |              | 20Hz to 20kHz bar                             | ndwidth                                                                   | -0.1 |       | +0.1                       | dB    |

| Sample Rate<br>Frequency Range |              | Input and output                              | ASRCs                                                                     | 7    |       | 224                        | kHz   |

|                                |              | ASRCIx_LPM or AS                              | SRCOx_LPM = 0                                                             |      | 130   |                            |       |

| Dynamic Range <sup>(1)</sup>   |              | ASRCIx_LPM or AS                              | SRCOx_LPM = 1                                                             |      | 130   |                            | dB    |

|                                |              | ASRCIx_LPM_II or 1                            | ASRCOx_LPM_II =                                                           |      | 130   |                            | UD    |

|                                |              | ASRCIx_LPM or AS                              | SRCOx_LPM = 0                                                             |      | -130  | -120                       |       |

| THD+N Level <sup>(3, 6)</sup>  |              | ASRCIx_LPM or AS                              | SRCOx_LPM = 1                                                             |      | -120  | -110                       |       |

|                                |              | ASRCIx_LPM_II or 1                            | ASRCOx_LPM_II =                                                           |      | -115  | -90                        | dBFS  |

| Startup Lock-On Time           |              |                                               |                                                                           |      |       | 25                         | ms    |

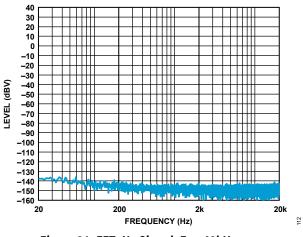

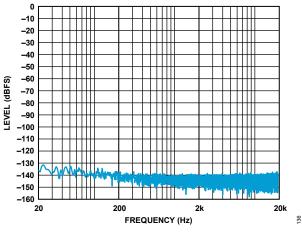

| PULSE DENSITY MODULA           | TION (PDM) C | OUTPUTS                                       |                                                                           |      |       |                            |       |

| Dynamic Range <sup>(1)</sup>   |              | A-weighted filter                             |                                                                           |      | 126   |                            | dB    |

| THD+N Level <sup>(3)</sup>     |              | -6dBFS input leve                             | l                                                                         |      | -125  |                            | dBFS  |

| PARAMETER                                                    | SYMBOL            | CONDITION                                | S/COMMENTS                | MIN    | ТҮР    | MAX  | UNITS |

|--------------------------------------------------------------|-------------------|------------------------------------------|---------------------------|--------|--------|------|-------|

| Crease Datas (5)                                             |                   | $f_s = 384 \text{kHz}, f_{\text{PDM}_C}$ | <sub>LK</sub> = 6.144MHz  |        | 7.5    |      |       |

| Group Delay <sup>(5)</sup>                                   |                   | $f_s = 768 \text{kHz}, f_{\text{PDM}_C}$ | <sub>LK</sub> = 6.144MHz  |        | 4.9    |      | μs    |

| MASTER CLOCK TIMING S                                        | PECIFICATIO       | NS                                       |                           |        |        |      | •     |

| Master Clock Period                                          | t <sub>MP</sub>   | 900kHz to 49.152M<br>frequency           | MHz input clock           | 0.0203 |        | 1.11 | μs    |

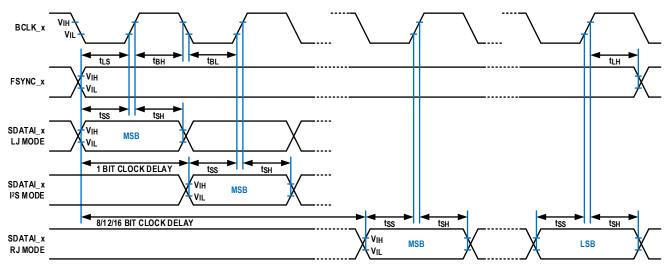

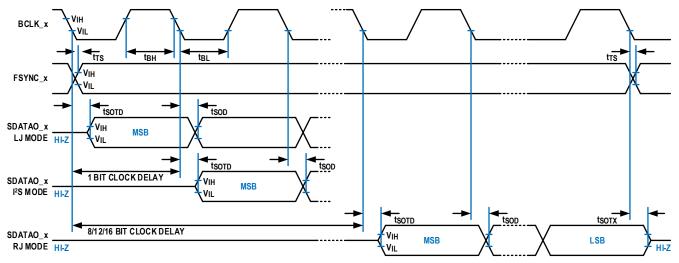

| SERIAL AUDIO DATA POR                                        | T TIMING SPE      | CIFICATIONS                              |                           |        |        |      |       |

| Nominal Bit Clock<br>Frequency                               | f <sub>BCLK</sub> | Maximum valid<br>frequency               | Slave mode                |        | 49.152 |      | MHz   |

| Nominal Bit Clock                                            | £                 | Maximum valid<br>frequency               | Master mode               |        | 24.576 |      | N411- |

| Frequency Range                                              | f <sub>BCLK</sub> | Minimum valid                            | Slave mode                |        | 0.512  |      | MHz   |

|                                                              |                   | frequency                                | Master mode               |        | 2.048  |      |       |

| Bit Clock Low Pulse<br>Width                                 | t <sub>BL</sub>   | Master or slave m                        | ode                       | 18     |        |      | ns    |

| Bit Clock High Pulse<br>Width                                | t <sub>BH</sub>   | Master or slave m                        | ode                       | 18     |        |      | ns    |

| Frame Sync Clock                                             | f                 | Maximum setting                          |                           |        | 768    |      | kHz   |

| Frequency Range                                              | f <sub>sync</sub> | Minimum setting                          |                           |        | 8      |      | КПД   |

| Frame Sync to Bit<br>Clock Active Edge<br>Setup Time         | t <sub>LS</sub>   | Slave mode, setur<br>active edge         | o time to bit clock       | 3      |        |      | ns    |

| Bit Clock Active Edge<br>to Frame Sync Hold<br>Time          | t <sub>LH</sub>   | Slave mode, hold<br>active edge          | time from bit clock       | 5      |        |      | ns    |

| Data Input to Bit Clock<br>Active Edge Setup<br>Time         | t <sub>ss</sub>   | Master or slave m<br>bit clock active ed | ode, setup time to<br>Ige | 3      |        |      | ns    |

| Bit Clock Active Edge<br>to Data Input Hold<br>Time          | t <sub>sH</sub>   | Master or slave m<br>from bit clock act  |                           | 10     |        |      | ns    |

| Bit Clock Inactive Edge<br>to Frame Sync Edge<br>Timing Skew | t <sub>TS</sub>   | Master mode                              |                           |        |        | 6    | ns    |

| Bit Clock Inactive Edge<br>to Data Output Delay              | t <sub>SOD</sub>  | Master or slave<br>mode, delay until     | $V_{IOVDD} \ge 1.62V$     | 0      |        | 16   | ns    |

| PARAMETER                           | SYMBOL            | CONDITIONS                    | COMMENTS             | MIN  | ТҮР   | МАХ | UNITS |

|-------------------------------------|-------------------|-------------------------------|----------------------|------|-------|-----|-------|

|                                     |                   | data output logic             |                      |      |       |     |       |

|                                     |                   | level change                  |                      |      |       |     |       |

|                                     |                   | Master or slave               |                      |      |       |     |       |

|                                     |                   | mode, delay until             | $V_{IOVDD} \ge 1.1V$ | 0    |       | 32  |       |

|                                     |                   | data output level             |                      |      |       |     |       |

|                                     |                   | change                        |                      |      |       |     |       |

| Bit Clock Inactive Edge             | t <sub>sotd</sub> | Master or slave mo            |                      | 0    |       | 16  | ns    |

| to Data Output Active               | 3015              | high-Z data output            |                      |      |       |     |       |

| Bit Clock Inactive Edge             | t <sub>sotx</sub> | Master or slave mo            | •                    | 0    |       | 16  | ns    |

| to Data Output High-Z               |                   | active data output            | is high-Z            |      |       |     |       |

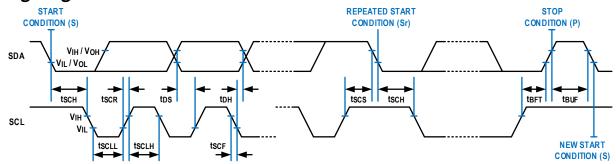

| I <sup>2</sup> C CONTROL PORT TIMIN | IG SPECIFICA      | TIONS                         |                      |      |       |     | [     |

| Serial Clock (SCL)                  | $f_{SCL}$         |                               |                      |      |       | 1   | MHz   |

| Frequency                           | 302               |                               |                      |      |       | _   |       |

| SCL Pulse Width High                | t <sub>SCLH</sub> |                               |                      | 0.26 |       |     | μs    |

| SCL Pulse Width Low                 | $t_{SCLL}$        |                               |                      | 0.5  |       |     | μs    |

| SCL Setup Time for a                |                   | Cotup time from S             | CL rising to CDA     |      |       |     |       |

| Repeated Start                      | t <sub>scs</sub>  | Setup time from Setup falling | CL HSING to SDA      | 0.26 |       |     | μs    |

| Condition                           |                   | laung                         |                      |      |       |     |       |

| SCL Hold Time for a                 | +                 | Hold time from SD             | A falling to SCL     | 0.26 |       |     |       |

| Start Condition                     | t <sub>SCH</sub>  | falling                       |                      | 0.20 |       |     | μs    |

| SCL Setup Time for a                | t                 | Setup time from S             | CL rising to SDA     | 0.5  |       |     | 116   |

| Stop Condition                      | $t_{\sf BFT}$     | rising                        |                      | 0.5  |       |     | μs    |

| Serial Data (SDA)                   | t <sub>DS</sub>   | SDA setup time to             | SCI rising           | 50   |       |     | nc    |

| Setup Time                          | CDS               | SDA setup time to             | SCLIISIIIg           | 50   |       |     | ns    |

| Serial Data (SDA) Hold              | <b>t</b>          | SDA hold time from            | n SCI falling        | 0    |       |     | ns    |

| Time                                | t <sub>DH</sub>   | SDA Hold Line Hol             |                      | 0    |       |     | 115   |

| SCL and SDA Rise                    | t <sub>scr</sub>  | 400pF load                    |                      |      |       | 120 | ns    |

| Time                                | SCR               |                               |                      |      |       | 120 | 115   |

| SCL and SDA Fall Time               | $t_{\sf SCF}$     | 400pF load                    |                      |      |       | 120 | ns    |

| Bus Free Time                       |                   |                               |                      |      |       |     |       |

| Between Stop and                    | t <sub>BUF</sub>  | Master mode                   |                      | 0.5  |       |     | μs    |

| Start Condition                     |                   |                               |                      |      |       |     |       |

| I <sup>3</sup> C CONTROL PORT TIMIN | IG SPECIFICA      | TIONS                         |                      |      |       |     |       |

| Maximum Serial Clock                | f.                | Master or slave mo            | do                   |      | 6.144 |     | MHz   |

| (SCL) Frequency                     | $f_{SCL}$         | Master Of Slave IIIC          |                      |      | 0.144 |     | MUL   |

| PARAMETER                                  | SYMBOL            | CONDITIONS                             | S/COMMENTS                 | MIN | ΤΥΡ   | МАХ  | UNITS |

|--------------------------------------------|-------------------|----------------------------------------|----------------------------|-----|-------|------|-------|

| Maximum Serial Data<br>(SDA) Rate          | $f_{SDA}$         | Master DDR mode                        |                            |     | 6.144 |      | MHz   |

| SCL Pulse Width High                       | t <sub>SCLH</sub> | Slave mode                             |                            | 24  |       |      | ns    |

| SCL Pulse Width Low                        | t <sub>SCLL</sub> | Slave mode                             |                            | 24  |       |      | ns    |

|                                            |                   | Setup time from                        | Setup time from Slave mode |     |       |      |       |

| SDA Input Setup Time                       | $t_{DS}$          | SDA edge to SCL<br>rising edge         | Master mode                | 10  |       |      | ns    |

| SDA Input Hold Time                        | t <sub>DH</sub>   | Slave mode                             |                            | 11  |       |      | ns    |

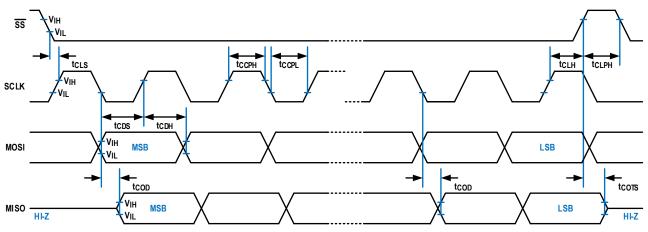

| SERIAL PERIPHERAL INTI                     | ERFACE (SPI)      | PORT TIMING SPEC                       | CIFICATIONS                |     |       |      |       |

| Serial Clock<br>Frequency                  | f <sub>sclk</sub> |                                        |                            |     |       | 10   | MHz   |

| Serial Clock Pulse                         | t <sub>CCPL</sub> | Low pulse                              |                            | 35  |       |      | 20    |

| Width                                      | t <sub>CCPH</sub> | High pulse                             | •                          |     |       |      | ns    |

| Slave Select to Serial<br>Clock Setup Time | t <sub>CLS</sub>  | Setup time to serial clock rising edge |                            | 5   |       |      | ns    |

| Serial Clock to Slave<br>Select Hold Time  | t <sub>CLH</sub>  | Hold time from serial clock rising     |                            | 40  |       |      | ns    |

| Slave Select Pulse<br>Width                | t <sub>clph</sub> | Minimum high pul                       | se                         | 10  |       |      | ns    |

| MOSI to Serial Clock<br>Setup Time         | $t_{CDS}$         | Setup time to seria                    | al clock rising            | 10  |       |      | ns    |

| Serial Clock to MOSI<br>Hold Time          | t <sub>cdh</sub>  | Hold time from se                      | rial clock rising          | 10  |       |      | ns    |

| Serial Clock to MISO<br>Data Delay Time    | t <sub>cod</sub>  | Delay until MISO le                    | evel change                |     |       | 30   | ns    |

| Slave Select to MISO<br>High-Z Delay Time  | t <sub>cots</sub> | Delay until MISO b                     | ecomes high-Z              |     |       | 30   | ns    |

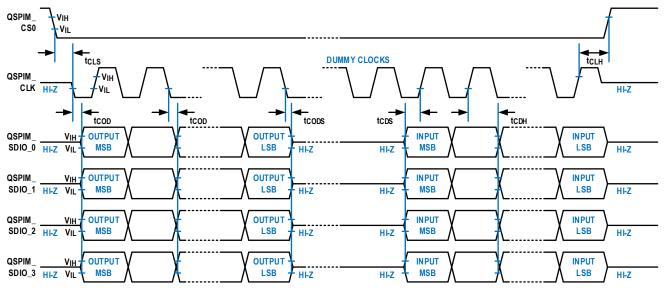

| QUAD-SPI (QSPI) MASTEI                     | R PORT TIMIN      | IG SPECIFICATIONS                      | G SPECIFICATIONS           |     |       |      | 1     |

| QSPI Clock Frequency                       | f <sub>SCLK</sub> | QSPI output clock<br>self-boot         | (QSPI_CLK) during          |     |       | 12.5 | MHz   |

| QSPI Data Input Setup<br>Time              | $t_{\text{CDS}}$  | QSPI data input to setup time          | clock rising edge          | 10  |       |      | ns    |

| QSPI Data Input Hold<br>Time               | t <sub>срн</sub>  | QSPI clock rising t<br>hold time       | o data input edge          | 10  |       |      | ns    |

| PARAMETER                                   | SYMBOL             | CONDITIONS/COMMENTS                                                 | MIN    | ΤΥΡ     | MAX                       | UNITS |

|---------------------------------------------|--------------------|---------------------------------------------------------------------|--------|---------|---------------------------|-------|

| QSPI Data Output<br>Delay Time              | tcod               | QSPI data output delay from clock falling edge                      | 1      |         |                           | ns    |

| QSPI Data Output<br>High-Z Delay Time       | t <sub>cods</sub>  | QSPI data output high-Z delay from chip select rising edge          | 1      |         |                           | ns    |

| UNIVERSAL ASYNCHRON                         | OUS RECEIVE        | R-TRANSMITTER (UART) PORT TIMING                                    | SPECIF | ICATION | IS                        |       |

| UART Baud Rate                              |                    |                                                                     |        |         | 3.125                     | Mbps  |

| ACTIVE-LOW HARDWARE                         | POWER-DOW          | IN INPUT PIN TIMING SPECIFICATIONS                                  |        |         |                           |       |

| Power-Down Input<br>Assert Time             | t <sub>RLPW</sub>  | Minimum time PD input must be asserted low to power down the device | 20     |         |                           | ns    |

| Power-Down Input<br>Hardware Enable<br>Time |                    | REG_EN is pulled high, f <sub>MCLK</sub> =<br>24.576MHz             | 15     |         |                           | ms    |

| GENERAL-PURPOSE INP                         | UT/OUTPUT (        | GPIO) PIN TIMING SPECIFICATIONS                                     |        |         |                           |       |

| GPIO (MPx) Input<br>Latency                 | t <sub>GIL</sub>   | Time delay until MPx logic level is read internally                 |        |         | 1.5 x<br>1/f <sub>S</sub> | μs    |

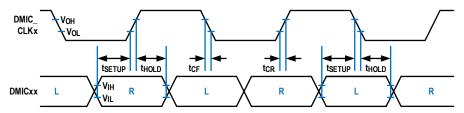

| DIGITAL MICROPHONE IN                       | <b>TERFACE TIN</b> | AING SPECIFICATIONS                                                 |        |         |                           |       |

| DMIC Clock Output<br>Fall Time              | t <sub>CF</sub>    | 2mA output drive strength, 25pF load                                |        |         | 12                        | ns    |

| DMIC Clock Output<br>Rise Time              | t <sub>CR</sub>    | 2mA output drive strength, 25pF load                                |        |         | 14                        | ns    |

| DMIC Data Setup time                        | t <sub>SETUP</sub> | Setup time from DMIC data edge to<br>DMIC clock edge                | 10     |         |                           | ns    |

| DMIC Data Hold Time                         | t <sub>HOLD</sub>  | Hold time from PDM clock edge to<br>DMIC data edge                  | 3      |         |                           | ns    |

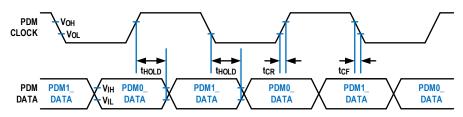

| PULSE DENSITY MODULA                        | TION (PDM)         | DUTPUT TIMING SPECIFICATIONS                                        |        |         |                           |       |

|                                             |                    | PDM_RATE = 0                                                        |        | 12.288  |                           |       |

| PDM Clock Frequency                         | $f_{PDM\_CLK}$     | PDM_RATE = 1                                                        |        | 6.144   |                           | MHz   |

|                                             |                    | PDM_RATE = 2                                                        |        | 3.072   |                           |       |

| PDM Clock Output Fall<br>Time               | t <sub>CF</sub>    | 2mA output drive strength, 25pF load                                |        |         | 12                        | ns    |

| PDM Clock Output<br>Rise Time               | t <sub>CR</sub>    | 2mA output drive strength, 25pF load                                |        |         | 14                        | ns    |

| PDM Data Hold Time                          | t <sub>HOLD</sub>  | Delay time from PDM clock edge to<br>PDM data change                | 35     |         | 46                        | ns    |

- <sup>1</sup> Dynamic range is the ratio of the sum of the inband noise and harmonic power with a -60dBFS input signal level at 1kHz relative to the full-scale power level in decibels. Normal operating mode uses default settings, while extreme power saving mode changes ADCx\_IBIAS to 0x1 and ADC\_LP\_MODE to 1.

- <sup>2</sup> SNR is the ratio of the sum of all inband noise power with no input signal relative to the full-scale power level in decibels.

- <sup>3</sup> THD+N level is the ratio of the sum of the inband harmonic power with the specified input signal level at 1kHz relative to either full-scale code (in dBFS) or a 1V<sub>RMS</sub> reference level (in dBV).

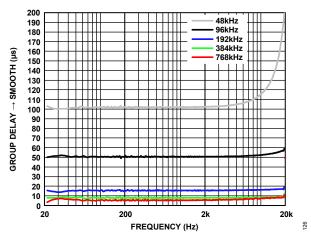

- <sup>4</sup> Group delay specified from analog input to Class-D amplifier output with FastDSP in bypass mode, ADCxx\_FCOMP = 0, and DAC\_FCOMP = 0. Point group delay values taken at  $f_{IN}$  = 1kHz, see the group delay Typical Performance Characteristics for the delay over the entire audio band.

- <sup>5</sup> Group delay specified from input to the PDM output channels to the PDM output pins. Point group delay values taken at  $f_{IN} = 1$ kHz at the specified PDM sample rate.

- <sup>6</sup> ASRC THD+N typical value is specified at  $f_{IN} = 1$ kHz and the maximum value is specified at  $f_{IN} = 20$ kHz

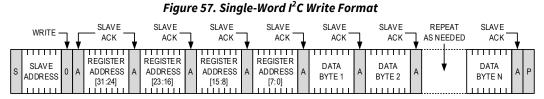

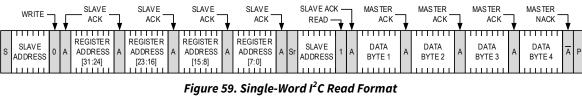

## **Timing Diagrams**

Figure 2. I<sup>2</sup>C Interface Slave Mode Timing Diagram

Figure 3. Serial Audio Data Port Input Timing (Slave Mode, Bit Clock Rising Active Edge)

Figure 4. Serial Audio Data Port Output Timing (Master Mode, Bit Clock Rising Active Edge, Tristate Enabled)

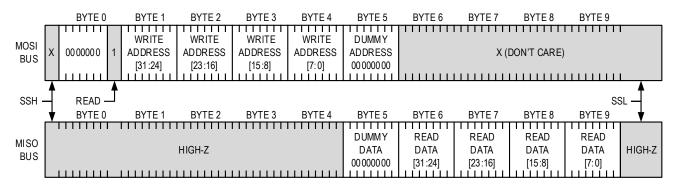

# ADAU1797

#### Figure 5. SPI Port Timing Diagram

Figure 6. QSPI Master Port Timing Diagram (Default Settings with Tristate Idle)

Figure 7. Digital Microphone Timing Diagram

Figure 8. PDM Output Timing Diagram

# **Power Consumption Specifications**

### **Device Power-Down Modes**

Supplies externally connected at  $V_{AVDD} = V_{HPVDD} = V_{IOVDD} = 1.8V$  and  $V_{DVDD} = 0.9V$ , PLL and crystal oscillator disabled.

| DEVICE STATE                                                                   | CONDITIONS                                                    | TYPICAL<br>AVDD<br>CURRENT | TYPICAL<br>HPVDD<br>CURRENT | TYPICAL<br>DVDD<br>CURRENT | TYPICAL<br>IOVDD<br>CURRENT | UNIT |

|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------|------|

| Hardware Power-Down                                                            | PD pin low                                                    | 0.52                       | 0.8                         | 30.2                       | 0.02                        | μA   |

| Software Power-Down                                                            | PD pin high, POWER_EN = 0,<br>no keep-alive modes enabled     | 1.08                       | 1.35                        | 31.17                      | 0.02                        | μΑ   |

| Software Power-Down with<br>Common-Mode Keep Alive Set                         | PD pin high, POWER_EN = 0,<br>CM_KEEP_ALIVE = 1, KEEP_MEM = 0 | 63.92                      | 1.35                        | 32.76                      | 0.02                        | μA   |

| Software Power-Down with Common-Mode,<br>FastDSP/HiFi 3z Memory Keep Alive Set | PD pin high, POWER_EN = 0,<br>CM_KEEP_ALIVE = 1, KEEP_MEM = 1 | 69.93                      | 1.35                        | 32.78                      | 0.02                        | μΑ   |

#### Table 2. Quiescent Power Consumption for Power-Down Mode Configurations

### **Power Management Mode Configurations**

Configuration models a typical active noise canceling (ANC) use case with different analog power mode settings. External supplies are  $V_{AVDD} = V_{HPVDD} = V_{IOVDD} = 1.8V$  and  $V_{DVDD} = 0.9V$ . PLL enabled with  $f_{MCLK} = 24.576$ MHz (crystal amp enabled). 3 ADC inputs with PGAs in single-ended mode with channels 0 and 1 set to  $f_S = 384$ kHz and channel 2 set to  $f_S = 48$ kHz. 2 interpolator and decimator channels. FastDSP core at  $f_S = 384$ kHz, FDSP\_SPEED = 0 (24.576MHz), and 64 instructions. HiFi 3z core disabled. All biquad filters are set to 27-bit precision. DAC to Class-D amp output channel set to  $f_S = 384$ kHz with a 16 $\Omega$  load. Single serial audio data port in slave mode for input and output with 1 input and 2 output ASRC channels. Quiescent current state (zero code or no signal input to all audio channels).

| POWER<br>MODE                        | POWER<br>MANAGEMENT<br>DEVICE SETTINGS                                                                                                                       | l <sub>DVDD</sub><br>(mA) | l <sub>AVDD</sub><br>(mA) | I <sub>HPVDD</sub><br>(mA) | l <sub>IOVDD</sub><br>(mA) | TOTAL<br>POWER<br>(mW) | ADC<br>A-wt DR<br>(dB) | ADC<br>THD+N<br>(dB) <sup>(1)</sup> | Class-D<br>A-wt DR<br>(dB) | Class-D<br>THD+N<br>(dB) <sup>(<u>1</u>)</sup> |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------------------------|------------------------|-------------------------------------|----------------------------|------------------------------------------------|

| Normal<br>Power<br>Mode              | Default Settings                                                                                                                                             | 10.141                    | 1.307                     | 0.747                      | 0.693                      | 14.07                  | 100.0                  | -90.0                               | 110.0                      | -90.9                                          |

| Power-<br>Savings<br>Mode            | ADC_IBIAS: 0x010, ADC_LP_MODE: 1,<br>DAC_IBIAS: 0x01, DAC_PWR_MODE: 0x01,<br>ASRCI_LPM1: 1, ASRCI_LPM2: 0, PGA_IBIAS: 0x10,<br>ASRCO_LPM1: 1, ASRCO_LPM2: 0, | 9.931                     | 1.172                     | 0.735                      | 0.709                      | 13.65                  | 98.0                   | -86.3                               | 112.4                      | -90.6                                          |

| Extreme<br>Power-<br>Savings<br>Mode | ADC_IBIAS: 0x001, ADC_LP_MODE: 1,<br>DAC_IBIAS: 0x01, DAC_PWR_MODE: 0x10,<br>ASRCI_LPM1: 0, ASRCI_LPM2: 1, PGA_IBIAS: 1,<br>ASRCO_LPM1: 0, ASRCO_LPM2: 1     | 9.869                     | 1.083                     | 0.675                      | 0.71                       | 13.324                 | 97.9                   | -85.6                               | 112.4                      | -90.8                                          |

<sup>1</sup> THD+N ratio is measured at  $f_{IN} = 1$ kHz with a -1dBFS output for ADC input channels and at  $f_{IN} = 1$ kHz with 50mW into 16 $\Omega$  for Class-D amplifier.

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = +25$ °C unless otherwise specified.

#### **Table 4. Absolute Maximum Ratings**

| PARAMETER                           | RATING                             |

|-------------------------------------|------------------------------------|

| Power Supply (AVDD, HPVDD IOVDD)    | -0.3V to +1.98V                    |

| Digital Supply (DVDD)               | -0.3V to +1.98V                    |

| Input Current (Except Supply Pins)  | ±20mA                              |

| Analog Input Voltage (Signal Pins)  | -0.3V to V <sub>AVDD</sub> + 0.3V  |

| Digital Input Voltage (Signal Pins) | -0.3V to V <sub>IOVDD</sub> + 0.3V |

| Operating Temperature Range (Case)  | -40°C to +85°C                     |

| Storage Temperature Range           | -65°C to +150°C                    |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **Thermal Resistance**

Thermal performance is directly linked to PCB design and operating environment. Close attention to PCB thermal design is required.  $\theta_{JA}$  and  $\theta_{JC}$  are determined using JESD51-9 on a 4-layer PCB with natural convection cooling.

#### **Table 5. Thermal Resistance**

| PACKAGE TYPE | <b>θ</b> <sub>JA</sub> <sup>(1)</sup> | θ <sub>JC</sub> <sup>(1)</sup> | UNIT |

|--------------|---------------------------------------|--------------------------------|------|

| CB-77-1      | 17                                    | 0.3                            | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with two thermal vias. See JEDEC JESD-51.

### **Electrostatic Discharge (ESD)**

The following ESD information is provided for the handling of ESD-sensitive devices in an ESD-protected area-only Human body model (HBM) per ANSI/ESDA/JEDEC JS-001 Field-induced charged device model (FICDM) and charged device model (CDM) per ANSI/ESDA/JEDEC JS-002. International Electrotechnical Commission (IEC) electromagnetic compatibility: Part 4-2 (IEC) per IEC 61000-4-2. Machine model (MM) per ANSI/ESD STM5.2. MM voltage values are for characterization only.

#### Table 6. ESD Ratings

| ESD MODEL          | WITHSTAND THRESHOLD (V)    | CLASS   |

|--------------------|----------------------------|---------|

| НВМ                | ±7000                      | 3A      |

| CDM                | ±1500                      | C3      |

| IEC <sup>(1)</sup> | ±12000 (contact discharge) | Level 4 |

|                    | >±12000 (air discharge)    | Level 3 |

| ММ                 | ±200                       | М3      |

<sup>1</sup> The IEC withstand threshold applies to the A, B, Y, and Z pins. The IEC withstand thresholds are for 10 positive and 10 negative discharges. The withstand voltage for three positive and three negative discharges is ±15,000 V; IEC Level 4.

### **ESD** Caution

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high-energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

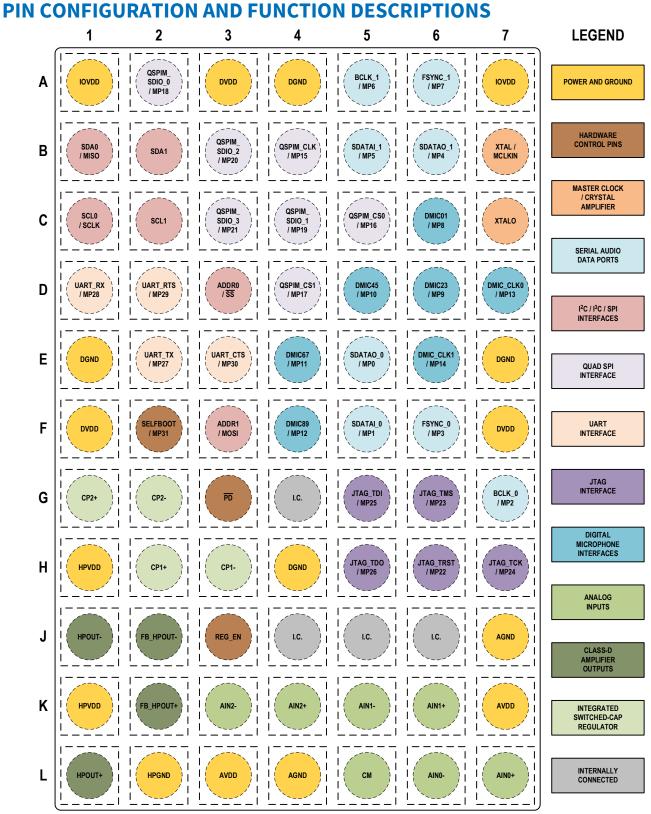

Figure 9. Top View Ball Configuration (View from Top-Side)

### Table 7. Pin Function Descriptions

| PIN | NAME                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      | Туре |