Basic demo board to test the functionality of new family of Silicon on Insulator (SOI) gate drivers

#### **About this document**

#### Scope and purpose

The purpose of this document is to help power electronic engineers evaluate the new family of Silicon on Insulator (SOI) gate drivers from Infineon Technologies. The general purpose board provides the right platform to test the basic functionalities of the gate driver such as PWM input-output performance, check propogation delay, source/sink current capability etc. The board can also be used to do a simple double pulse test when connected to an external load. The high switching frequency performance of SOI gate drivers can also be tested.

#### Intended audience

Power supply design engineers, motor control design engineers

#### **Evaluation Board**

This board will be used during design in, for evaluation and measurement of characteristics, and proof of data sheet specifications.

Note: PCB and auxiliary circuits are NOT optimized for final customer design.

Table 1 2ED2184S06F General Purpose Demo Board Specifications

| Symbol              | Parameter                  | Min | Max | Units |

|---------------------|----------------------------|-----|-----|-------|

| Vcc                 | Low-side supply voltage    | 10  | 20  | V     |

| V <sub>IN</sub>     | Bus input voltage          |     | 400 | V     |

| V <sub>out</sub>    | Switch node output voltage |     | 420 | V     |

| I <sub>OUT</sub>    | Switch node output current |     | 10  | Α     |

| V <sub>IH</sub>     | Logic "1" input voltage    | 1.7 | 2.4 | V     |

| V <sub>IL</sub>     | Logic "0" input voltage    | 0.7 | 1.1 | V     |

| t <sub>ON/OFF</sub> | Propogation delay          |     | 200 | ns    |

Important notice

#### **Important notice**

"Evaluation Boards and Reference Boards" shall mean products embedded on a printed circuit board (PCB) for demonstration and/or evaluation purposes, which include, without limitation, demonstration, reference and evaluation boards, kits and design (collectively referred to as "Reference Board").

Environmental conditions have been considered in the design of the Evaluation Boards and Reference Boards provided by Infineon Technologies. The design of the Evaluation Boards and Reference Boards has been tested by Infineon Technologies only as described in this document. The design is not qualified in terms of safety requirements, manufacturing and operation over the entire operating temperature range or lifetime.

The Evaluation Boards and Reference Boards provided by Infineon Technologies are subject to functional testing only under typical load conditions. Evaluation Boards and Reference Boards are not subject to the same procedures as regular products regarding returned material analysis (RMA), process change notification (PCN) and product discontinuation (PD).

Evaluation Boards and Reference Boards are not commercialized products, and are solely intended for evaluation and testing purposes. In particular, they shall not be used for reliability testing or production. The Evaluation Boards and Reference Boards may therefore not comply with CE or similar standards (including but not limited to the EMC Directive 2004/EC/108 and the EMC Act) and may not fulfill other requirements of the country in which they are operated by the customer. The customer shall ensure that all Evaluation Boards and Reference Boards will be handled in a way which is compliant with the relevant requirements and standards of the country in which they are operated.

The Evaluation Boards and Reference Boards as well as the information provided in this document are addressed only to qualified and skilled technical staff, for laboratory usage, and shall be used and managed according to the terms and conditions set forth in this document and in other related documentation supplied with the respective Evaluation Board or Reference Board.

It is the responsibility of the customer's technical departments to evaluate the suitability of the Evaluation Boards and Reference Boards for the intended application, and to evaluate the completeness and correctness of the information provided in this document with respect to such application.

The customer is obliged to ensure that the use of the Evaluation Boards and Reference Boards does not cause any harm to persons or third party property.

The Evaluation Boards and Reference Boards and any information in this document is provided "as is" and Infineon Technologies disclaims any warranties, express or implied, including but not limited to warranties of non-infringement of third party rights and implied warranties of fitness for any purpose, or for merchantability.

Infineon Technologies shall not be responsible for any damages resulting from the use of the Evaluation Boards and Reference Boards and/or from any information provided in this document. The customer is obliged to defend, indemnify and hold Infineon Technologies harmless from and against any claims or damages arising out of or resulting from any use thereof.

Infineon Technologies reserves the right to modify this document and/or any information provided herein at any time without further notice.

#### **Safety precautions**

#### **Safety precautions**

Note: Please note the following warnings regarding the hazards associated with development systems.

#### Table 2Safety precautions

**Warning:** The DC link potential of this board is up to 400 VDC. When measuring voltage waveforms by oscilloscope, high voltage differential probes must be used. Failure to do so may result in personal injury or death.

**Warning**: The evaluation or reference board contains DC bus capacitors which take time to discharge after removal of the main supply. Before working on the drive system, wait five minutes for capacitors to discharge to safe voltage levels. Failure to do so may result in personal injury or death. Darkened display LEDs are not an indication that capacitors have discharged to safe voltage levels.

**Caution:** The heat sink and device surfaces of the evaluation or reference board may become hot during testing. Hence, necessary precautions are required while handling the board. Failure to comply may cause injury.

**Caution:** Only personnel familiar with the drive, power electronics and associated machinery should plan, install, commission and subsequently service the system. Failure to comply may result in personal injury and/or equipment damage.

**Caution:** The evaluation or reference board contains parts and assemblies sensitive to electrostatic discharge (ESD). Electrostatic control precautions are required when installing, testing, servicing or repairing the assembly. Component damage may result if ESD control procedures are not followed. If you are not familiar with electrostatic control procedures, refer to the applicable ESD protection handbooks and guidelines.

#### **Table of contents**

## **Table of contents**

| Abou  | ut this documentut this document     | 1  |

|-------|--------------------------------------|----|

| Impo  | ortant notice                        | 2  |

| Safet | ety precautions                      | 3  |

| Table | le of contents                       | 4  |

| 1     | The board at a glance                | 5  |

| 1.1   | Delivery content                     |    |

| 1.2   | Block diagram                        | 5  |

| 1.3   | Main features                        | 5  |

| 1.4   | Board parameters and technical data  | 6  |

| 2     | System and functional description    | 7  |

| 2.1   | Commissioning                        |    |

| 2.2   | Description of the functional blocks | 7  |

| 2.2.1 | Example: Basic operation             | 7  |

| 2.2.3 | Example: Design tips                 | 8  |

| 3     | System design                        | 9  |

| 3.1   | Schematics                           | 9  |

| 3.2   | Layout                               | 9  |

| 3.3   | Bill of material                     |    |

| 3.4   | Connector details                    | 10 |

| 4     | System performance                   | 11 |

| 4.1   | Test points                          | 11 |

| 4.2   | Test results                         | 11 |

| 5     | References and appendices            | 13 |

| 5.1   | Abbreviations and definitions        | 13 |

| 5.2   | References                           | 13 |

| 5.3   | Additional information               | 13 |

| Revis | sion history                         | 14 |

The board at a glance

## 1 The board at a glance

UG-2021-14, this user guide describes the below board:

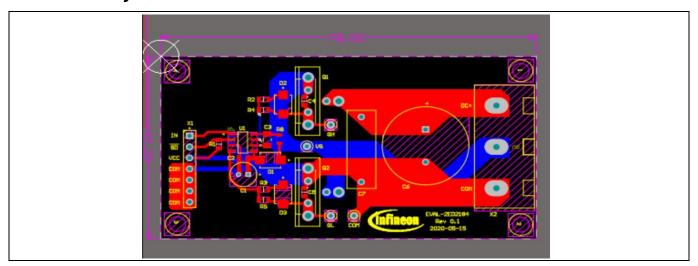

Figure 1: 2ED2184 general purpose demo board

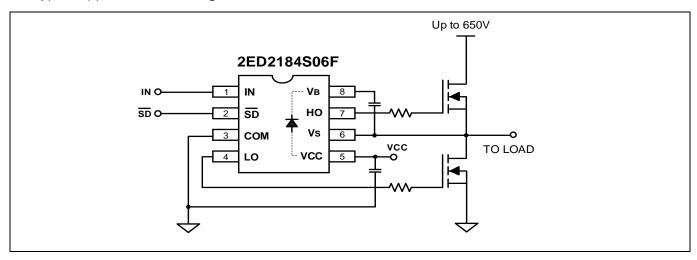

This demo board has two high voltage MOSFETs in a half bridge configuration driven by 2ED2184S06F gate high-side, low-side gate driver. The inputs to the gate driver are provided at X1 connector and the half bridge can be loaded at X2 connector.

#### 1.1 Delivery content

The demo board comes with the 2ED2184S06F and the IPD60R280P7 MOSFETs in half bridge configuration. It can be used to test the various parameters of the gate driver including double pulse tests, basic functionality tests and high frequency performance of the 2ED2184S06F.

## 1.2 Block diagram

The typical application block diagram is as below:

Figure 2: Functional block diagram

#### 1.3 Main features

The demo board features new SOI gate driver IC 2ED2184S06F having:

- Unique Infineon Thin-Film-Silicon On Insulator (SOI)-technology

- Floating channel designed for bootstrap operation

- Integrated ultra-fast, low resistance bootstrap diode

#### The board at a glance

- Logic operational up to -11 V on VS Pin

- Negative voltage tolerance on inputs of -5 V

- Independent under voltage lockout for both channels

- Schmitt trigger inputs with hysteresis

- 3.3 V, 5 V and 15 V input logic compatible

- Maximum VCC supply voltage of 25 V

- Shutdown input turns off both channels

## 1.4 Board parameters and technical data

The demo board is designed to operate as below:

#### Table 3

| Symbol              | Parameter                               | Min | Max | Units |

|---------------------|-----------------------------------------|-----|-----|-------|

| $V_{cc}$            | Low-side supply voltage                 | 10  | 20  | V     |

| $V_{IN}$            | Bus Input Voltage                       |     | 400 | V     |

| V <sub>OUT</sub>    | Switch Node Output Voltage              |     | 420 | V     |

| l <sub>out</sub>    | Switch Node Output Current              |     | 10  | А     |

| $V_{IH}$            | V <sub>IH</sub> Logic "1" input voltage |     | 2.4 | V     |

| $V_{IL}$            | V <sub>IL</sub> Logic "0" input voltage |     | 1.1 | V     |

| T <sub>ON/OFF</sub> | Propogation Delay                       |     | 200 | ns    |

System and functional description

## 2 System and functional description

## 2.1 Commissioning

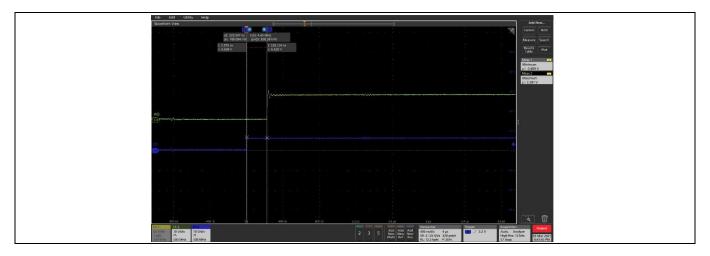

The board has been tested for DC bus voltages upto 400 V. Load inductor of 1 mH, 2 mH have been used to characterize the double pulse performance.

#### 2.2 Description of the functional blocks

The 2ED2184S06F is a high voltage, high speed power MOSFET driver with independent high and low side referenced output channels. Based on Infineon's SOI-technology there is an excellent ruggedness and noise immunity with capability to maintain operational logic at negative voltages of up to - 11 V on VS pin ( $V_{cc} = 15 \text{ V}$ ) on transient voltages. There are not any parasitic thyristor structures present in the device, hence no parasitic latch up may occur at all temperature and voltage conditions. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3 V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET, SiC MOSFET or IGBT in the high side configuration, which operate up to 650 V.

#### 2.3 Example: Basic operation

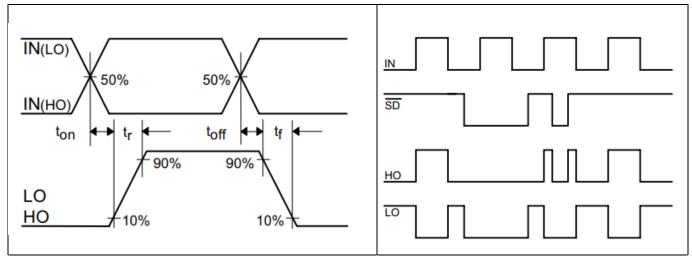

The relationships between the input and output signals of the 2ED2184S06F are illustrated below in Figure 1 and Figure 4. From these figures, we can see the definitions of several timing parameters (i.e.  $t_{ON}$ ,  $t_{OFF}$ ,  $t_R$ , and  $t_F$ ) associated with this device.

Figure 3 Switching timing diagram

Figure 4 Input/output logic diagram

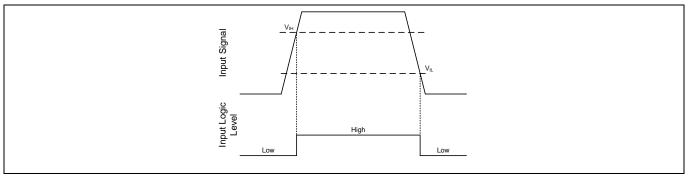

The input pins of are based on a TTL and CMOS compatible input-threshold logic that is independent of the Vcc supply voltage. With typical high threshold ( $V_{IH}$ ) of 2.1 V and typical low threshold ( $V_{IL}$ ) of 0.9 V, along with very little temperature variation as summarized in Figure 5, the input pins are conveniently driven with logic level PWM control signals derived from 3.3 V and 5 V digital power-controller devices. Wider hysteresis (typically 0.9 V) offers enhanced noise immunity compared to traditional TTL logic implementations, where the hysteresis is typically less than 0.5 V. 2ED218x family also features tight control of the input pin threshold voltage levels which eases system design considerations and ensures stable operation across temperature. The 2ED218x features floating input protection wherein if any of the input pin is left floating, the output of the corresponding stage is held in the low state. This is achieved using pull-down resistors on all the input pins (HIN, LIN) as shown in the block diagram. The 2ED218x family has input pins that are capable of sustaining voltages higher than the bias voltage applied on the Vcc pin of the device.

## System and functional description

Figure 5 IN input thresholds

## 2.3.1 Example: Design tips

The general-purpose board can be used for evaluating the complete 2ED218x family of gate drivers by modifying the PWM input schemes. The entire family details are as below:

| Part No.     | Package  | Drive<br>current<br>source /<br>sink | Input<br>logic | Cross<br>conduction<br>prevention<br>logic | Deadtime                         | Ground<br>pins | t <sub>on</sub> /t <sub>off</sub> |

|--------------|----------|--------------------------------------|----------------|--------------------------------------------|----------------------------------|----------------|-----------------------------------|

| 2ED2181S06F  | DSO - 8  | + 2.5 A /<br>- 2.5 A                 |                |                                            |                                  | СОМ            |                                   |

| 2ED21814S06J | DSO - 14 | + 2.5 A /<br>- 2.5 A                 | HIN, LIN N     | No                                         | None                             | VSS /<br>COM   |                                   |

| 2ED2182S06F  | DSO - 8  | + 2.5 A /<br>- 2.5 A                 |                |                                            | Internal 400 ns                  | СОМ            |                                   |

| 2ED21824S06J | DSO - 14 | + 2.5 A /<br>- 2.5 A                 | HIN, LIN       | Yes                                        | Programmable<br>400 ns - 5000 ns | VSS /<br>COM   | 200 ns /<br>200 ns                |

| 2ED2183S06F  | DSO - 8  | + 2.5 A /<br>- 2.5 A                 | HIN, LIN       | Yes                                        | Internal 400 ns                  | СОМ            |                                   |

| 2ED21834S06J | DSO - 14 | + 2.5 A /<br>- 2.5 A                 |                |                                            | Programmable<br>400 ns - 5000 ns | VSS /<br>COM   |                                   |

| 2ED2184S06F  | DSO - 8  | + 2.5 A /<br>- 2.5 A                 | IN, SD         | Yes                                        | Internal 400 ns                  | СОМ            | 600 ns /<br>200 ns                |

| 2ED21844S06J | DSO - 14 | + 2.5 A /<br>- 2.5 A                 |                |                                            | Programmable<br>400 ns - 5000 ns | VSS /<br>COM   |                                   |

System design

## 3 System design

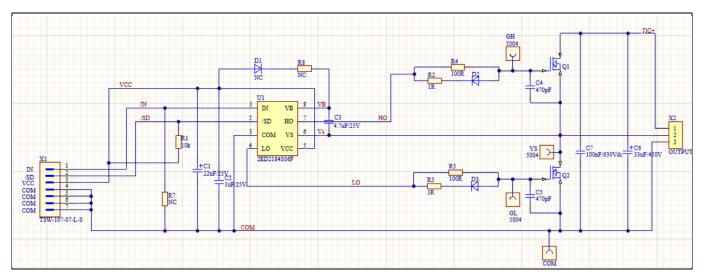

#### 3.1 Schematics

Figure 6: 2ED2184S06F demo board schematics

The schematics show the 2ED2184S06F driving a half bridge. The output can be connected to the load inductor and DC bus. The load inductor is to be connected between 2 and 3 and the DC bus positive to 1 and DC bus negative to 3 of the output connector.

The schematic shows provisions for modifying turn on and turn off dv/dt for both the high side and low side MOSFETs. Turn on dv/dt can be modified by changing R4 / R5 and turn off dv/dt can be modified by changing R2 / R3 for top and bottom MOSFETs respectively.

At X1, input to power the 2ED2184S06F is to be provided. VCC of 15 V between VCC and COM pins, HIN and LIN inputs between HIN-COM and LIN-COM pins.

#### 3.2 Layout

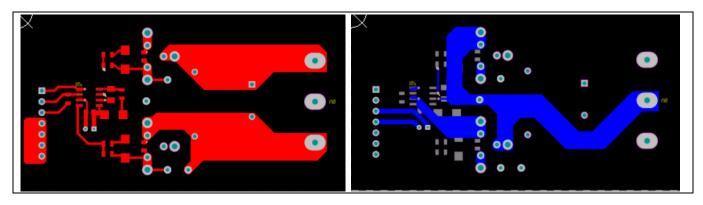

Figure 7: 2ED2184S06F demo board layout

#### System design

Figure 8: Top layer and bottor layer of 2ED2184S06F demo board

The board layout is as shown above. On the output side, the track thickness enable load current of around 10 A. The gate drive loop is kept to a minimum to ensure no false turn-on event takes place.

#### 3.3 Bill of material

The complete bill of material is available on the download section of the Infineon homepage. A log-in is required to download this material.

Table 4 BOM of the most important/critical parts of the evaluation or reference board

| S. No. | Ref Designator | Description                                              | Value       | Manufacturer<br>P/N |

|--------|----------------|----------------------------------------------------------|-------------|---------------------|

| 1      | C1             | Miniature Aluminum Electrolytic Capacitor                | 22uF/25V    |                     |

| 2      | C2             | Surface Mount Multilayer Ceramic Chip Capacitor  1uF/25V |             |                     |

| 3      | C3             | Multilayer Ceramic Chip Capacitor                        | 4.7uF       |                     |

| 4      | C4, C5         | Chip Monolithic Ceramic Capacitor                        | 470pF/25V   |                     |

| 5      | C6             | Aluminum Electrolytic Capacitor, Wide Temperature Range  | 33uF/450V   |                     |

| 6      | C7             | EMI Suppression Capacitor                                | 100nF/630V  |                     |

| 7      | D2, D3         | Ultrafast Power Rectifier, 1A, 200V                      | MURS120T3G  |                     |

| 8      | Q1, Q2         | 600V CoolMOS CFD7 Power Transistor                       | IPD60R360P7 |                     |

| 9      | R2, R3         | Standard Thick Film Chip Resistor                        | 1R          |                     |

| 10     | R4, R5         | Standard Thick Film Chip Resistor                        | 100R        |                     |

| 11     | U1             | High Voltage SOI Gate Driver                             | 2ED2184S06F |                     |

Bill of Material of critical components is as above. Infineon parts are highlighted in bold. The remaining parts are generic and can be substituted with other manufacturers with same ratings.

#### 3.4 Connector details

Table 5 Connectors

| PIN    | Label | Function                                  |

|--------|-------|-------------------------------------------|

| Input  | X1    | Input connector for VCC and IN PWM and SD |

| Output | X2    | Output connector for VBUS and Load        |

#### **System performance**

## 4 System performance

## 4.1 Test points

Various test points are provided on board to measure the gate and drain voltages on the high side and low side MOSFETs.

#### 4.2 Test results

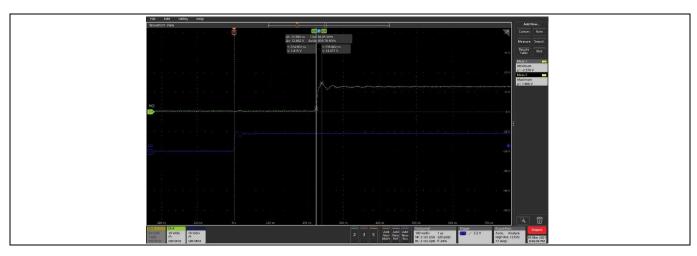

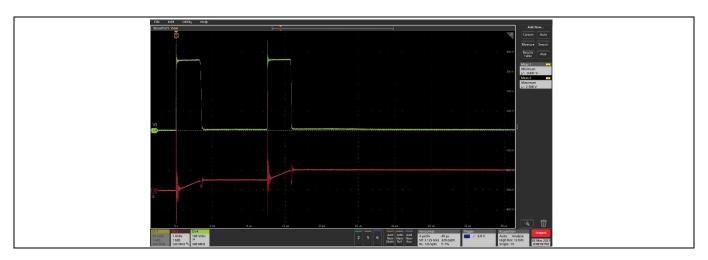

Below test results show some of the measurements taken on the demo board.

Figure 9 2ED2184S06F rise time measurement result

Figure 9 2ED2184S06F propogation delay measurement results

## **System performance**

Figure 10: 2ED2184S0FS double pulse test results

#### **References and appendices**

## 5 References and appendices

#### 5.1 Abbreviations and definitions

#### Table 6 Abbreviations

| Abbreviation | Meaning                      |

|--------------|------------------------------|

| EMI          | Electromagnetic interference |

|              |                              |

#### 5.2 References

Several technical documents related to the use of HVICs are available at <a href="www.infineon.com">www.infineon.com</a>; use the Site Search function and the document number to quickly locate them. Below is a short list of some of these documents.

#### **Application Notes:**

**Understanding HVIC Datasheet Specifications**

**HV Floating MOS-Gate Driver ICs**

**Use Gate Charge to Design the Gate Drive Circuit for Power MOSFETs and IGBTs**

**Bootstrap Network Analysis: Focusing on the Integrated Bootstrap Functionality**

#### **Design Tips:**

**Double Pulse Testing**

**Using Monolithic High Voltage Gate Drivers**

Alleviating High Side Latch on Problem at Power Up

**Keeping the Bootstrap Capacitor Charged in Buck Converters**

**Managing Transients in Control IC Driven Power Stages**

**Simple High Side Drive Provides Fast Switching and Continuous On-Time**

## 5.3 Additional information: Infineon online community resources

The Gate Driver community is live at Infineon.com (<a href="https://community.infineon.com/t5/Gate-Driver-IC-s/bd-p/GateDriverICs">https://community.infineon.com/t5/Gate-Driver-IC-s/bd-p/GateDriverICs</a>). Here the Infineon gate driver community comes to the assistance of our customers to provide technical guidance – how to use gate driver ICs, existing and new gate driver information, application information, availability of demo boards, online training materials for over 500 gate driver ICs. The Gate Driver community also serves as a repository of FAQs where the user can review solutions to common or specific issues faced in similar applications.

Register online at the community and learn the nuances of efficiently driving a power switch in any given power electronic application.

**Revision history**

## **Revision history**

| Document version | Date of release | Description of changes |

|------------------|-----------------|------------------------|

| 1                | 2021-01-10      | Initial version        |

|                  |                 |                        |

|                  |                 |                        |

#### Trademark

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-01-10

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2024 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference

UG xxx (user guide number)

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.