**FLE** ON

# FLE ON Industrial SD 6.1 Read-Only Mode (ROM) 3D TLC

Version 1.0

Address: 28 Genting Ln, #09-03/04/05 Platinum 28, Singapore 349585 Tel: +65-6493 5035 Fax: +65-6493 5037 Website: http://www.flexxon.com Email: flexxon@flexxon.com

# - FLE�ON

# TABLE OF CONTENTS

| 1. | GENER                  | AL DESCRIPTION                 | 1   |

|----|------------------------|--------------------------------|-----|

|    | 1.1 In                 | troduction                     | 1   |

|    | 1.2 Pi                 | roduct Overview                | 2   |

|    |                        | /orkflow                       |     |

| 2. | PRODU                  | ICT SPECIFICATIONS             | 4   |

|    | 2.1 Pe                 | erformance                     | 4   |

|    | 2.2 Pe                 | ower                           | 4   |

|    | 2.3 M                  | (TBF                           | 4   |

| 3. | ENVIRG                 | DNMENTAL SPECIFICATIONS        | 5   |

| 4. | ELECTR                 | RICAL SPECIFICATIONS           | 6   |

|    | 4.1 D<br>4.1.<br>4.1.2 | 1 8 8                          | 6   |

|    | 4.2 A                  | C Characteristic               |     |

|    | 4.2.                   |                                |     |

|    | 4.2.1<br>4.2.1         |                                |     |

|    | 4.2.4                  |                                |     |

| 5. | PAD AS                 | SSIGNMENT                      | 15  |

|    |                        |                                | 1.5 |

| 6. |                        | ad Assignment and Descriptions |     |

|    |                        |                                |     |

| 7. | PHYSIC                 | AL DIMENSION                   | 16  |

| 8. | ORDER                  | ING INFORMATION                | 16  |

#### **1. GENERAL DESCRIPTION**

#### **1.1** Introduction

The Read-Only Mode is highly effective in a memory device to ensure data security. Read-Only mode provides a tamper-proof data storage solution by making it unalterable and the crucial files remain safe.

**FLEXXON Read Only Mode (ROM) SD Card** provides security function to prevent the stored data from being stolen, tampered or modified by others. Once you activate the Read-Only mode into the memory card, all the stored data enables access for reading only. None can change, delete, or overwrite anything from the stored data. So, you can preserve the authenticity of the essential files into the memory card and prohibit it from the risk of alteration. Write access could only be enabled by authorized user with specific tool and correct password.

**FLEXXON ROM SD Card** plays an important role in various applications where ensuring data authenticity is extremely important. For example, in medical and healthcare facilities, financial institutes, business organizations, the cybersecurity industry, etc. will be beneficial by utilizing Read-Only Mode memory card.

The read only mode is an additional feature, which will not affect the standard product specification.

#### 1.2 Product Overview

| • | Flash                                                | • | Support SD System                |

|---|------------------------------------------------------|---|----------------------------------|

|   | 3D TLC                                               |   | Specification 6.1                |

| • | Capacity<br>32GB to 512GB                            | • | Support SD SPI Mode              |

| ٠ | Support Data Encrption                               | • | Support Auto Read<br>Refreshment |

| • | Read disturbance<br>management                       | • | Adaptive wear leveling           |

| • | Support management of sudden power fails             | ٠ | SMART function support           |

| • | Temperature Range                                    |   |                                  |

|   | Operation (Gold):                                    |   |                                  |

|   |                                                      |   |                                  |

|   | -25°C ~ 85°C                                         |   |                                  |

|   | -25°C ~ 85°C<br>Operation (Diamond):<br>-40°C ~ 85°C |   |                                  |

| • | Operation (Diamond):                                 |   |                                  |

...

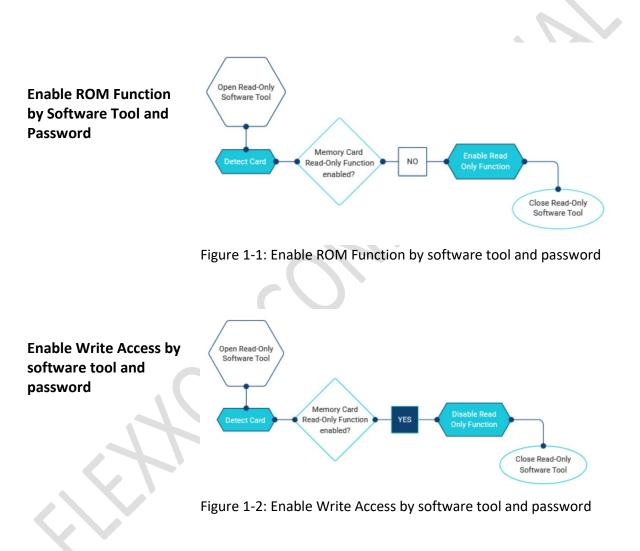

# **1.3 Workflow FLEXXON ROM SD Card** is a normal mode by default. User could set the password to enable read only mode by software tool.

Note: User is required to eject and re-insert the after set the password.

User could enable write access by the legal host with security tool and enter correct password. When user power off the host or reinsert the card, the card will return to read only mode.

### 2. PRODUCT SPECIFICATIONS

#### 2.1 Performance

| Capacity | Sequ        | ential       |

|----------|-------------|--------------|

|          | Read (MB/s) | Write (MB/s) |

| 32GB     | 85          | 25           |

| 64GB     | 85          | 25           |

| 128GB    | 85          | 48           |

| 256GB    | 85          | 50           |

| 512GB    | 85          | 50           |

#### Table 2-1 Performance of SD Card

#### NOTES:

- 1. The performance is obtained from TestMetrix

- 2. Performance may vary from flash configuration and platform.

#### 2.2 Power

2.3 MTB

| Capacity | Read | Write | Standby |

|----------|------|-------|---------|

|          | (mA) | (mA)  | (uA)    |

| 32GB     | 55   | 42    | 220     |

| 64GB     | 62   | 49    | 200     |

| 128GB    | 63   | 73    | 200     |

| 256GB    | 64   | 75    | 220     |

| 512GB    | 60   | 75    | 340     |

# Table 2-2 Typical Power Consumption of SD Card

MTBF, an acronym for Mean Time Between Failures, is a measure of a device's reliability. Its value represents the average time between a repair and the next failure. The higher the MTBF value, the higher the reliability of the device. The predicted result of SD Card is more than 3,000,000 hours.

# **3. ENVIRONMENTAL SPECIFICATIONS**

| Test Items            | Test Conditions                                              |

|-----------------------|--------------------------------------------------------------|

| Storage Temperature   | -40°C ~ 85°C                                                 |

| Operating Temperature | Gold: -25°C ~ 85°C<br>Diamond: -40°C ~ 85°C                  |

| Storage Humidity      | 40°C, 93% RH                                                 |

| Operating Humidity    | 25°C, 95% RH                                                 |

| Shock                 | 1500G, Half Sin Pulse Duration 0.5ms                         |

| Vibration             | 80Hz ~ 2000Hz/20G, 20Hz ~ 80Hz/1.52mm, 3<br>axis/30min       |

| Drop                  | 150cm free fall, 6 face of each unit                         |

| Bending               | ≥ 10N, Hold 1 min/5 times                                    |

| Torque                | 0.1N-m or +/-2.5 deg, Hold 30 seconds/5 times                |

| ESD                   | Contact: +/- 4KV each item 25 times<br>Air: +/- 8KV 10 times |

**Table 3-1 Environmental Specification**

## 4. ELECTRICAL SPECIFICATIONS

#### 4.1 DC Characteristics

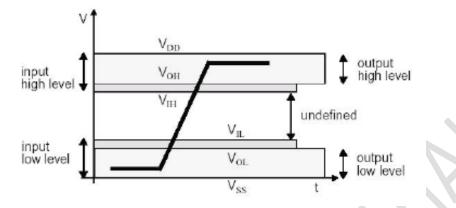

#### 4.1.1 Bus Operation Conditions for 3.3V Signaling

| Parameter           | Symbol          | Min.                  | Max                   | Unit | Condition                                 |

|---------------------|-----------------|-----------------------|-----------------------|------|-------------------------------------------|

| Supply Voltage      | $V_{\text{DD}}$ | 2.7                   | 3.6                   | V    |                                           |

| Output High Voltage | V <sub>OH</sub> | 0.75*V <sub>DD</sub>  |                       | V    | I <sub>OH</sub> =-2mA V <sub>DD</sub> Min |

| Output Low Voltage  | V <sub>OL</sub> |                       | 0.125*V <sub>DD</sub> | V    | I <sub>OL</sub> =2mA V <sub>DD</sub> Min  |

| Input High Voltage  | VIH             | 0.625*V <sub>DD</sub> | V <sub>DD</sub> +0.3  | V    |                                           |

| Input Low Voltage   | VIL             | V <sub>SS</sub> -0.3  | 0.25*V <sub>DD</sub>  | V    |                                           |

| Power Up Time       |                 |                       | 250                   | ms   | From OV to $V_{DD}$ min                   |

#### Table 4-1 Threshold Level for High Voltage Range

| Parameter           | Symbol            | Min.                 | Max  | Unit | Condition                    |  |  |

|---------------------|-------------------|----------------------|------|------|------------------------------|--|--|

| Supply Voltage      | $V_{DD}$          | 2.7                  | 3.6  | V    |                              |  |  |

| Regulator Voltage   | V <sub>DDIO</sub> | 1.7                  | 1.95 | V    | Generated by $V_{\text{DD}}$ |  |  |

| Output High Voltage | V <sub>OH</sub>   | 1.4                  | -    | V    | I <sub>OH</sub> =-2mA        |  |  |

| Output Low Voltage  | Vol               | -                    | 0.45 | V    | I <sub>OL</sub> =2mA         |  |  |

| Input High Voltage  | ViH               | 1.27                 | 2.00 | V    |                              |  |  |

| Input Low Voltage   | V <sub>IL</sub>   | V <sub>ss</sub> -0.3 | 0.58 | V    |                              |  |  |

# Table 4-2 Threshold Level for 1.8V Signaling

| Parameter             | Symbol | Min | Max. | Unit | Remarks                       |

|-----------------------|--------|-----|------|------|-------------------------------|

| Input Leakage Current |        | -2  | 2    | uA   | DAT3 pull-up is disconnected. |

#### Table 4-3 Input Leakage Current for 1.8V Signaling

| Parameter                 | Symbol | Min  | Max.                 | Unit | Remarks |  |  |

|---------------------------|--------|------|----------------------|------|---------|--|--|

| Peak voltage on all lines |        | -0.3 | V <sub>DD</sub> +0.3 | V    |         |  |  |

| All Inputs                |        |      |                      |      |         |  |  |

| Input Leakage Current     |        | -10  | 10                   | uA   |         |  |  |

| All Outputs               |        |      |                      |      |         |  |  |

| Output Leakage Current    |        | -10  | 10                   | uA   |         |  |  |

#### Table 4-4 Peak Voltage and Leakage Current

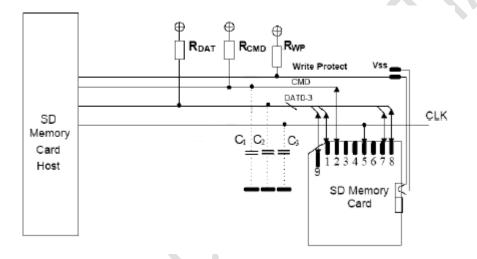

#### 4.1.2 Bus Signal Line Load

#### **Bus Operation Conditions – Signal Line's Load**

Total Bus Capacitance =  $C_{HOST} + C_{BUS} + N C_{CARD}$

| Parameter                        | symbol            | Min | Max             | Unit | Remark                                    |

|----------------------------------|-------------------|-----|-----------------|------|-------------------------------------------|

| Pull-up resistance               | R <sub>CMD</sub>  | 10  | 100             | kΩ   | to prevent bus floating                   |

|                                  | Rdat              |     |                 |      |                                           |

| Total bus capacitance for each   | CL                |     | 40              | рF   | 1 card                                    |

| signal line                      |                   |     |                 |      | С <sub>ноsт</sub> +С <sub>виs</sub> shall |

|                                  |                   |     |                 |      | not exceed 30 pF                          |

| Card Capacitance for each signal | CCARD             |     | 10 <sup>1</sup> | рF   |                                           |

| pin                              |                   |     |                 |      |                                           |

| Maximum signal line inductance   |                   |     | 16              | nH   |                                           |

| Pull-up resistance inside card   | R <sub>DAT3</sub> | 10  | 90              | kΩ   | May be used for card                      |

| (pin1)                           |                   |     |                 |      | detection                                 |

| Capacity Connected to Power      | Cc                |     | 5               | uF   | To prevent inrush current                 |

| Line                             |                   |     |                 |      |                                           |

#### Table 4-5 Peak Voltage and Leakage Current

#### 4.2 AC Characteristic

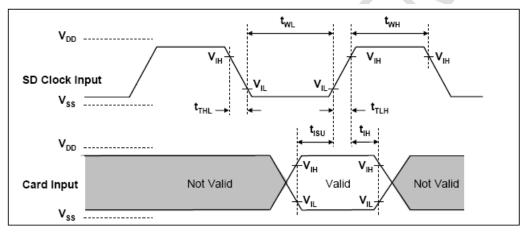

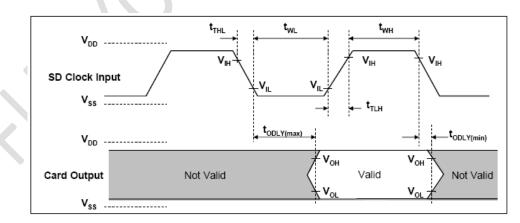

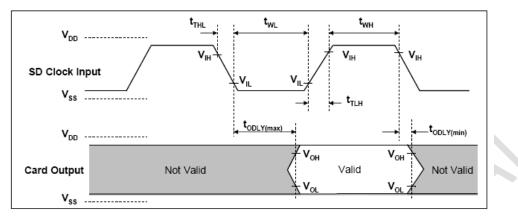

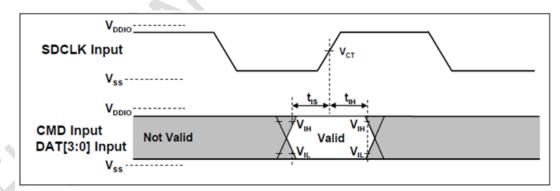

#### 4.2.1 SD Interface timing (Default)

Card Input Timing (Default Speed Card)

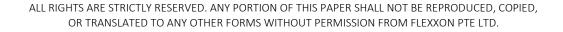

#### Card Output Timing (Default Speed Mode)

| Parameter                | Symbol          | Min        | Max         | Unit | Remark                    |

|--------------------------|-----------------|------------|-------------|------|---------------------------|

| Clock CLK (Al            |                 |            |             |      |                           |

| Clock frequency Data     | f <sub>PP</sub> | 0          | 25          | MHz  | C <sub>card</sub> ≤ 10 pF |

| Transfer Mode            |                 |            |             |      | (1 card)                  |

| Clock frequency          | f <sub>OD</sub> | 0(1)/100   | 400         | KHz  | C <sub>card</sub> ≤ 10 pF |

| Identification Mode      |                 |            |             |      | (1 card)                  |

| Clock low time           | $t_{WL}$        | 10         |             | ns   | C <sub>card</sub> ≤ 10 pF |

|                          |                 |            |             |      | (1 card)                  |

| Clock high time          | t <sub>wн</sub> | 10         |             | ns   | C <sub>card</sub> ≤ 10 pF |

|                          |                 |            |             |      | (1 card)                  |

| Clock rise time          | $t_{TLH}$       |            | 10          | ns   | C <sub>card</sub> ≤ 10 pF |

|                          |                 |            |             |      | (1 card)                  |

| Clock fall time          | $t_{THL}$       |            | 10          | ns   | C <sub>card</sub> ≤ 10 pF |

|                          |                 |            |             |      | (1 card)                  |

| In                       | puts CMD, [     | DAT (refer | enced to CL | к)   |                           |

| Input set-up time        | tisu            | 5          |             | ns   | C <sub>card</sub> ≤ 10 pF |

|                          |                 |            |             |      | (1 card)                  |

| Input hold time          | t <sub>IH</sub> | 5          |             | ns   | C <sub>card</sub> ≤ 10 pF |

|                          |                 |            |             |      | (1 card)                  |

| Out                      | tputs CMD,      | DAT (refe  | renced to C | LK)  |                           |

| Output Delay time during | todly           | 0          | 14          | ns   | C <sub>L</sub> ≤ 40 pF    |

| Data Transfer Mode       |                 |            |             |      | (1 card)                  |

| Output Delay time during | todly           | 0          | 50          | ns   | C∟≤ 40 pF                 |

| Identification Mode      |                 |            |             |      | (1 card)                  |

(1) OHz means to stop the clock. The given minimum frequency range is for cases where continues clock is required.

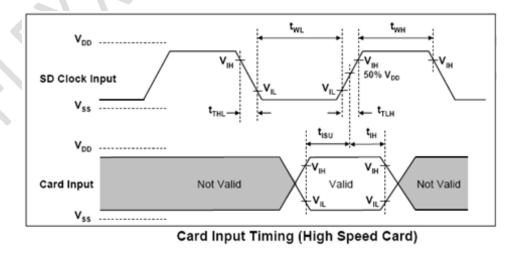

#### 4.2.2 SD Interface Timing (High-Speed Mode)

| Card Output | Timina | (Default | Speed | Mode) |

|-------------|--------|----------|-------|-------|

| eara eacpac |        | (Doladic | epoou | moucy |

| Parameter                                                                 | Symbol            | Min         | Max        | Unit | Remark                       |  |  |  |

|---------------------------------------------------------------------------|-------------------|-------------|------------|------|------------------------------|--|--|--|

|                                                                           | -                 |             |            |      | Kemark                       |  |  |  |

| Clock CLK (All values are referred to min( $V_{IH}$ ) and max( $V_{IL}$ ) |                   |             |            |      |                              |  |  |  |

| Clock frequency Data Transfer                                             | f <sub>PP</sub>   | 0           | 50         | MHz  | $C_{card} \le 10 \text{ pF}$ |  |  |  |

| Mode                                                                      |                   |             |            |      | (1 card)                     |  |  |  |

| Clock low time                                                            | t <sub>wL</sub>   | 7           |            | ns   | $C_{card} \le 10 \text{ pF}$ |  |  |  |

|                                                                           |                   |             |            |      | (1 card)                     |  |  |  |

| Clock high time                                                           | twн               | 7           |            | ns   | $C_{card} \le 10 \text{ pF}$ |  |  |  |

|                                                                           |                   |             |            |      | (1 card)                     |  |  |  |

| Clock rise time                                                           | t <sub>TLH</sub>  |             | 3          | ns   | $C_{card} \le 10 \text{ pF}$ |  |  |  |

|                                                                           |                   |             |            |      | (1 card)                     |  |  |  |

| Clock fall time                                                           | t <sub>тнL</sub>  |             | 3          | ns   | $C_{card} \le 10 \text{ pF}$ |  |  |  |

|                                                                           |                   |             |            |      | (1 card)                     |  |  |  |

| Inputs                                                                    | CMD, DAT          | (reference  | ed to CLK) |      |                              |  |  |  |

| Input set-up time                                                         | tisu              | 6           |            | ns   | $C_{card} \le 10 \text{ pF}$ |  |  |  |

|                                                                           |                   |             |            |      | (1 card)                     |  |  |  |

| Input hold time                                                           | t <sub>IH</sub>   | 2           |            | ns   | $C_{card} \le 10 \text{ pF}$ |  |  |  |

|                                                                           |                   |             |            |      | (1 card)                     |  |  |  |

| Output                                                                    | ts CMD, DA        | T (referenc | ed to CLK) |      |                              |  |  |  |

| Output Delay time during Data                                             | t <sub>ODLY</sub> |             | 14         | ns   | C <sub>L</sub> ≤ 40 pF       |  |  |  |

| Transfer Mode                                                             |                   |             |            |      | (1 card)                     |  |  |  |

| Output Hold time                                                          | Т <sub>ОН</sub>   | 2.5         |            | ns   | C <sub>L</sub> ≤ 15 pF       |  |  |  |

|                                                                           |                   |             |            |      | (1 card)                     |  |  |  |

| Total System capacitance of                                               | CL                |             | 40         | рF   | CL ≤ 15 pF                   |  |  |  |

| each line <sup>1</sup>                                                    |                   |             |            |      | (1 card)                     |  |  |  |

(1) In order to satisfy severe timing, the host shall drive only one card.

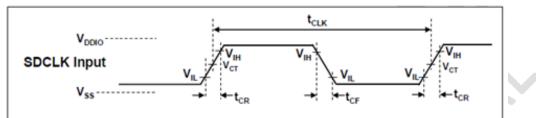

#### 4.2.3 SD Interface timing (SDR12, SDR25, SDR50 and SDR104 Modes)

Input:

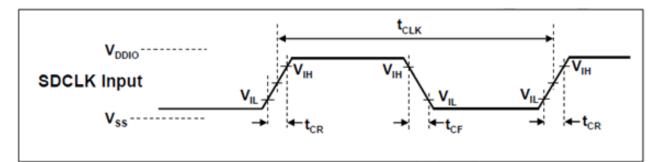

**Clock Signal Timing**

| Symbol                            | Min  | Max                   | Unit | Remark                                                                                                                                                                                                                                                                                   |

|-----------------------------------|------|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tсıк                              | 4.80 | -                     | ns   | 208MHz (Max.), Between rising edge, V <sub>CT</sub> =<br>0.975V                                                                                                                                                                                                                          |

| t <sub>CR</sub> , t <sub>CF</sub> | -    | 0.2* t <sub>CLK</sub> | ns   | t <sub>CR</sub> , t <sub>CF</sub> < 0.96ns (max.) at 208MHz, C <sub>CARD</sub> =10pF<br>t <sub>CR</sub> , t <sub>CF</sub> < 2.00ns (max.) at 100MHz, C <sub>CARD</sub> =10pF<br>The absolute maximum value of t <sub>CR</sub> , t <sub>CF</sub> is 10ns<br>regardless of clock frequency |

| Clock Duty                        | 30   | 70                    | %    |                                                                                                                                                                                                                                                                                          |

**Clock Signal Timing**

#### SDR50 and SDR104 Input Timing:

#### **Card Input Timing**

| Symbol          | Min  | Max | Unit | SDR104 Mode                                       |

|-----------------|------|-----|------|---------------------------------------------------|

| tıs             | 1.40 | -   | ns   | C <sub>CARD</sub> =10pF, V <sub>CT</sub> = 0.975V |

| t <sub>ін</sub> | 0.8  | -   | ns   | C <sub>CARD</sub> = 5pF, V <sub>CT</sub> = 0.975V |

| Symbol          | Min  | Max | Unit | SDR50 Mode                                        |

| t <sub>is</sub> | 3.00 | -   | ns   | C <sub>CARD</sub> =10pF, V <sub>CT</sub> = 0.975V |

| t <sub>IH</sub> | 0.8  | -   | ns   | C <sub>CARD</sub> = 5pF, V <sub>CT</sub> = 0.975V |

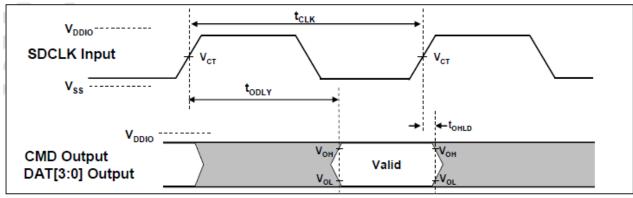

#### Output (SDR12, SDR25, SDR50):

#### Output Timing of Fixed Data Window

| Symbol            | Min | Max | Unit | Remark                                                                          |  |  |  |  |

|-------------------|-----|-----|------|---------------------------------------------------------------------------------|--|--|--|--|

| t <sub>ODLY</sub> | -   | 7.5 | ns   | t <sub>CLK</sub> >=10.0ns, C <sub>L</sub> =30pF, using driver Type B, for SDR50 |  |  |  |  |

| t <sub>ODLY</sub> | -   | 14  | ns   | $t_{CLK}$ >=20.0ns, C <sub>L</sub> =40pF, using driver Type B, for SDR25        |  |  |  |  |

|                   |     |     |      | and SDR12,                                                                      |  |  |  |  |

| Тон               | 1.5 | -   | ns   | Hold time at the $t_{ODLY}$ (min.), $C_L=15pF$                                  |  |  |  |  |

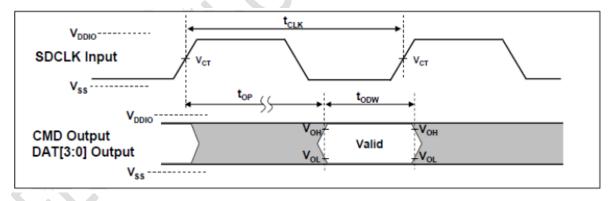

#### Output (SDR104 Mode):

| Symbol           | Min  | Max   | Unit | Remark                                                |

|------------------|------|-------|------|-------------------------------------------------------|

| t <sub>op</sub>  | 0    | 2     | UI   | Card Output Phase                                     |

| ∆t <sub>op</sub> | -350 | +1550 | ps   | Delay variable due to temperature change after tuning |

| t <sub>odw</sub> | 0.60 | -     | UI   | t <sub>obw</sub> = 2.88ns at 208MHz                   |

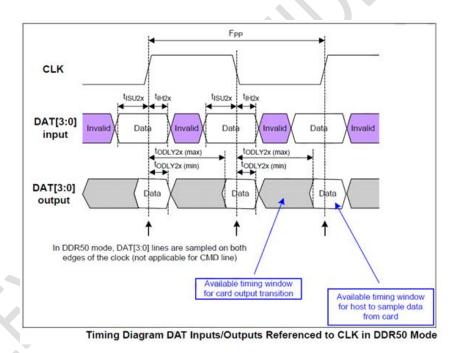

#### 4.2.4 SD Interface timing (DDR50 Modes)

#### Clock Signal Timing

| Symbol                            | Min | Max                   | Unit | Remark                                                         |

|-----------------------------------|-----|-----------------------|------|----------------------------------------------------------------|

| t <sub>clk</sub>                  | 20  | -                     | ns   | 50MHz (Max.), Between rising edge                              |

| t <sub>CR</sub> , t <sub>CF</sub> | -   | 0.2* t <sub>CLK</sub> | ns   | $t_{CR}$ , $t_{CF}$ < 4.00ns (max.) at 50MHz, $C_{CARD}$ =10pF |

| Clock Duty                        | 45  | 55                    | %    |                                                                |

| Parameter            | Symbol                                                   | Min      | Max           | Unit         | Remark                    |  |  |

|----------------------|----------------------------------------------------------|----------|---------------|--------------|---------------------------|--|--|

| In                   | put CMD (refe                                            | renced   | to CLK risin  | g edge)      |                           |  |  |

| Input set-up time    | tisu                                                     | 3        | -             | ns           | C <sub>card</sub> ≤ 10 pF |  |  |

|                      |                                                          |          |               |              | (1 card)                  |  |  |

| Input hold time      | t <sub>IH</sub>                                          | 0.8      | -             | ns           | C <sub>card</sub> ≤ 10 pF |  |  |

|                      |                                                          |          |               |              | (1 card)                  |  |  |

| Ou                   | tput CMD (ref                                            | erenced  | d to CLK risi | ng edge)     |                           |  |  |

| Output Delay time    | todly                                                    |          | 13.7          | ns           | C <sub>L</sub> ≤ 30 pF    |  |  |

| during Data Transfer |                                                          |          |               |              | (1 card)                  |  |  |

| Mode                 |                                                          |          |               |              |                           |  |  |

| Output Hold time     | Тон                                                      | 1.5      | -             | ns           | C∟≥ 15 pF                 |  |  |

|                      |                                                          |          |               |              | (1 card)                  |  |  |

| Inputs D             | <b>DAT</b> (reference                                    | d to CLI | < rising and  | falling edge | s)                        |  |  |

| Input set-up time    | t <sub>ISU2x</sub>                                       | 3        | -             | ns           | C <sub>card</sub> ≤ 10 pF |  |  |

|                      |                                                          |          |               |              | (1 card)                  |  |  |

| Input hold time      | t <sub>IH2x</sub>                                        | 0.8      | -             | ns           | C <sub>card</sub> ≤ 10 pF |  |  |

|                      |                                                          |          |               |              | (1 card)                  |  |  |

| Outputs              | Outputs DAT (referenced to CLK rising and falling edges) |          |               |              |                           |  |  |

| Output Delay time    | todly2x                                                  | -        | 7.0           | ns           | C∟≤ 25 pF                 |  |  |

| during Data Transfer |                                                          |          |               |              | (1 card)                  |  |  |

| Mode                 |                                                          |          |               |              |                           |  |  |

| Output Hold time     | T <sub>OH2x</sub>                                        | 1.5      | -             | ns           | C∟≥ 15 pF                 |  |  |

|                      |                                                          |          |               |              | (1 card)                  |  |  |

Table 4-6 Bus Timings – Parameters Values (DDR50 Mode)

# **5. PAD ASSIGNMENT**

#### 5.1 Pad Assignment and Descriptions

| pin |                  | SD                | Mode                  |      |              | SPI Mode               |

|-----|------------------|-------------------|-----------------------|------|--------------|------------------------|

|     | Name             | Type <sup>1</sup> | Description           | Name | Туре         | Description            |

| 1   | CD/DAT3          | I/O/PP            | Card Detect/          | CS   | <sup>3</sup> | Chip Select (net true) |

|     | 2                | 3                 | Data Line[bit3]       |      |              |                        |

| 2   | CMD              | PP                | Command/Response      | DI   | I            | Data In                |

| 3   | V <sub>SS1</sub> | S                 | Supply voltage ground | VSS  | S            | Supply voltage ground  |

| 4   | V <sub>DD</sub>  | S                 | Supply voltage        | VDD  | S            | Supply voltage         |

| 5   | CLK              |                   | Clock                 | SCLK | I            | Clock                  |

| 6   | V <sub>SS2</sub> | S                 | Supply voltage ground | VSS2 | S            | Supply voltage ground  |

| 7   | DAT0             | I/O/PP            | Data Line[bit0]       | DO   | O/PP         | Data Out               |

| 8   | DAT1             | I/O/PP            | Data Line[bit1]       | RSV  |              |                        |

| 9   | DAT2             | I/O/PP            | Data Line[bit2]       | RSV  |              |                        |

#### Table 5-1 SD Memory Card Pad Assignment

(1) S: power supply, I: input; O: output using push-pull drivers; PP: I/O using push-pull drivers.

(2) The extended DAT lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after SET\_BUS\_WIDTH command. The Host shall keep its own DAT1-DAT3 lines in input mode as well while they are not used. It is defined so in order to keep compatibility to MultiMedia Cards.

(3) At power up, this line has a 50KOhm pull up enabled in the card. This resistor serves two functions: Card detection and Mode Selection. For Mode Selection, the host can drive the line high or let it be pulled high to select SD mode. If the host wants to select SPI mode, it should drive the line low. For Card detection, the host detects that the line is pulled high. This pull-up should be disconnected by the user during regular data transfer with SET\_CLR\_CARD\_DETECT (ACMD42) command.

SET\_CLR\_CARD\_DETECT (ACMD42) command.

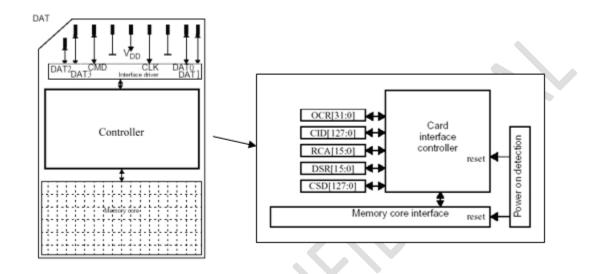

# 6. REGISTERS

| Name | Width  | Description                                                                                                                                    |

|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CID  | 128bit | Card identification number; card individual number for identification.                                                                         |

| RCA  | 16bit  | Relative card address; local system address of a card,<br>dynamically suggested by the card and approved by the host<br>during initialization. |

| DSR  | 16bit  | Driver Stage Register; to configure the card's output drivers.                                                                                 |

| CSD  | 128bit | Card Specific Data; Information about the card operation conditions.                                                                           |

| SCR  | 64bit  | SD Configuration Register; Information about the SD<br>Memory Card's Special Features capabilities                                             |

| OCR  | 32bit  | Operation conditions register.                                                                                                                 |

| SSR  | 512bit | SD Status; Information about the card proprietary features.                                                                                    |

| OCR  | 32bit  | Card Status; Information about the card status.                                                                                                |

Table 6-1 SD Registers

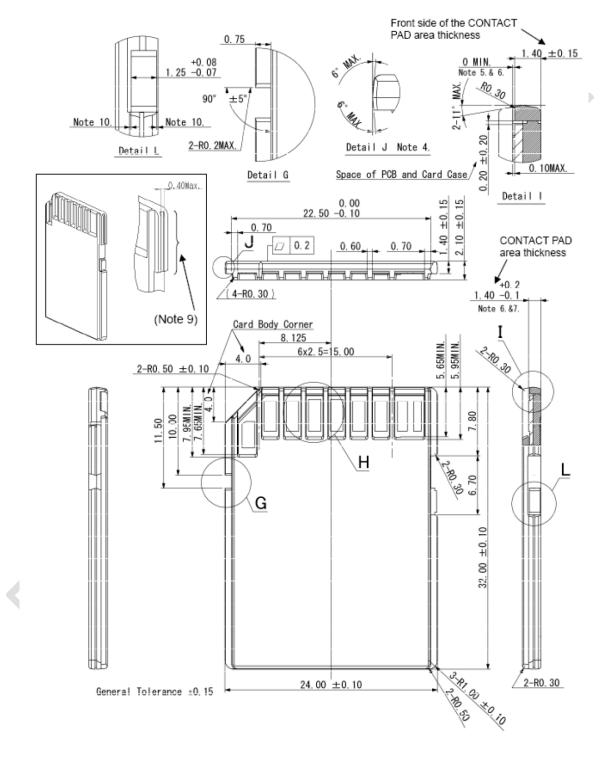

## 7. PHYSICAL DIMENSION

#### Dimension: 32mm(L) x 24mm(W) x 2.1mm(H)

# 8. ORDERING INFORMATION

| Capacity | MPN (Diamond Grade) | MPN (Gold Grade) |

|----------|---------------------|------------------|

| 32GB     | FDMS032GBE-XR00     | FDMS032GBG-XR00  |

| 64GB     | FDMS064GBE-XR00     | FDMS064GBG-XR00  |

| 128GB    | FDMS128GBE-XR00     | FDMS128GBG-XR00  |

| 256GB    | FDMS256GBE-XR00     | FDMS256GBG-XR00  |

| 512GB    | FDMS512GBE-XR00     |                  |

# **REVISION HISTORY**

| Revision | Date    | History       |

|----------|---------|---------------|

| 1.0      | 2023/09 | First Release |

|          |         |               |

|          |         |               |