# 1W, 1.5kV<sub>DC</sub>/3kV<sub>DC</sub>, Semi-Regulated Isolated DC/DC Converter

# **DESCRIPTION**

The MID1W0505A is a semi-regulated, isolated DC/DC converter that can support 4.5V to 5.5V input voltage ( $V_{IN}$ ) applications across a -40°C to +125°C operating temperature range. It has excellent load regulation, line regulation, and supports up to 1W of output power ( $P_{OUT}$ ).

The device integrates a power MOSFET, transformer, and feedback (FB) circuit all in one chip. The MID1W0505A is a small solution that provides high reliability compared to traditional isolated power modules.

Full protection features include short-circuit protection (SCP), over-current protection (OCP), and OTP protection.

The MID1W0505A requires a minimal number of readily available, standard external components. It is available in a low-profile, wide body SOICW-16 package.

#### **FEATURES**

- 4.5V to 5.5V Operating Input Voltage (V<sub>IN</sub>) Range

- 1.5KV<sub>DC</sub> or 3kV<sub>DC</sub> Isolation Voltage

- Up to 1W Output Power (P<sub>OUT</sub>)

- Max 54% Efficiency at Full Loads

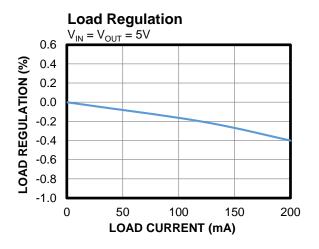

- 0.4% Load Regulation

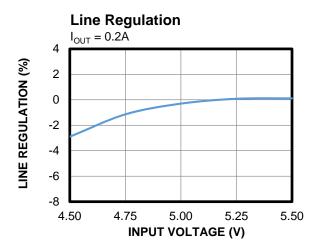

- 1.5% Line Regulation

- Excellent Transient Performance

- Continuous Short-Circuit Protection (SCP) with Hiccup Mode

- Over-Temperature Protection (OTP)

- Meets CISPR32 Class B Emissions

- UL1577 Certified

- CB Certified per IEC62368-1 3rd Edition

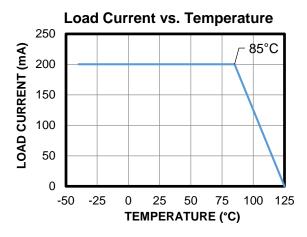

- -40°C to +125°C Operating Temperature Range

- Available in an SOICW-16 Package

## **APPLICATIONS**

- Industrial Automation Systems

- Isolated Bias Power for Digital Isolators

- Isolated Bias Power for RS-485, RS-422, and CAN Interfaces

- Isolated Sensor Power Supplies

- Telecom and Network Devices (e.g. 5G RRUs, Industrial CPE, and Network Gateways)

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

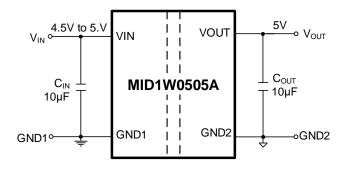

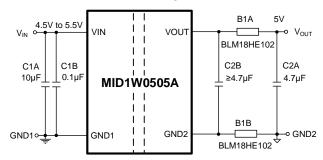

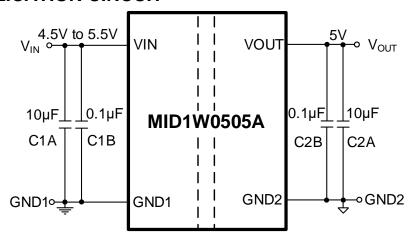

#### TYPICAL APPLICATION

# ORDERING INFORMATION

| Part Number       | Isolation Voltage   | Package  | Top Marking | MSL Rating |

|-------------------|---------------------|----------|-------------|------------|

| MID1W0505AGY-2S*  | 1.5kV <sub>DC</sub> | SOICW-16 | Coo Polow   | 2          |

| MID1W0505AGY-3S** | 3kV <sub>DC</sub>   | 301CW-16 | See Below   | 3          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MID1W0505AGY-2S-Z).

# **TOP MARKING (MID1W0505AGY-2S)**

MPS YYWW 1W0505A2 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code

1W0505A2: First eight digits of the part number

LLLLLLL: Lot number

# **TOP MARKING (MID1W0505AGY-3S)**

MPS YYWW 1W0505A3 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code

1W0505A3: First eight digits of the part number

LLLLLLL: Lot number

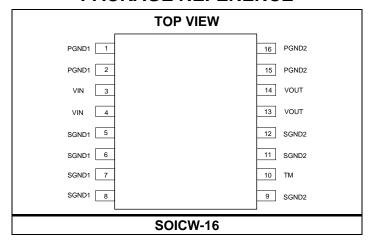

# **PACKAGE REFERENCE**

<sup>\*\*</sup> For Tape & Reel, add suffix -Z (e.g. MID1W0505AGY-3S-Z).

# PIN FUNCTIONS

| Pin #      | Name  | Description                                                                                                                                                                                        |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2       | PGND1 | <b>Power ground side 1.</b> Connect the PGND1 pin using large copper traces and multiple vias to improve thermal performance.                                                                      |

| 3, 4       | VIN   | <b>Power input pin.</b> Connect the VIN pin to a 4.5V to 5.5V power supply. Connect a $10\mu F$ capacitor and a $0.1\mu F$ capacitor between the VIN and PGND1 pins to stabilize the IC.           |

| 5, 6, 7, 8 | SGND1 | <b>Signal ground side 1.</b> Connect the SGND1 and PGND1 pins using large copper traces to improve thermal performance.                                                                            |

| 9, 11, 12  | SGND2 | <b>Signal ground side 2.</b> Connect the SGND2 and PGND2 pins using a thin trace. Do not connect SGND2 using large copper traces, as this can increase EMI.                                        |

| 10         | TM    | Test mode pin. Factory use only. Float this pin in applications.                                                                                                                                   |

| 13, 14     | VOUT  | <b>Power output pin.</b> It is recommended to connect a $10\mu F$ capacitor and a $0.1\mu F$ capacitor between VOUT and PGND2 to decrease the output voltage (V <sub>OUT</sub> ) ripple and noise. |

| 15, 16     | PGND2 | <b>Side 2 power ground pin.</b> Do not connect PGND2 using large copper areas, as this can increase EMI.                                                                                           |

# **ABSOLUTE MAXIMUM RATINGS** (1)

| VIN to PGND1 or SGND1          | 0.3V to +6V                   |

|--------------------------------|-------------------------------|

| VOUT to PGND2 or SGND2         | 0.3V to +6V                   |

| Continuous power dissipation ( | $T_A = 25^{\circ}C)^{(2)(4)}$ |

|                                | 2.65W                         |

| Junction temperature           | 150°C                         |

| Lead temperature               | 260°C                         |

| Storage temperature            | -65°C to +150°C               |

# ESD Ratings

| Human body model (HBM)     | 6000V |

|----------------------------|-------|

| Charged-device model (CDM) | 2000V |

# **Recommended Operating Conditions (3)**

| <del>-</del>                       | _            |

|------------------------------------|--------------|

| Input voltage (V <sub>IN</sub> )   | 4.5V to 5.5V |

| Output voltage (V <sub>OUT</sub> ) | 5V           |

| Operating junction temp            |              |

| Thermal Resistance  | $oldsymbol{	heta}$ JA | $oldsymbol{	heta}$ JC |       |

|---------------------|-----------------------|-----------------------|-------|

| EV1W0505A-Y-00A (4) | 47                    | 11                    | °C/W  |

| SOICW-16 (5)        | 48                    | 23                    | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A.$  The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}.$  Exceeding the maximum allowable power dissipation can produce an excessive die temperature, which may cause the converter to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- Measured on EV1W0505A-Y-00A (51mmx51mm), 1oz, 2layer PCB.

- 5) The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = V_{OUT} = 5V$ ,  $T_J = -40$ °C to +125°C (6), typical values are tested at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                     | Symbol                   | Condition                                                                                                                            | Min   | Тур  | Max   | Units            |

|-----------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|

| Under-voltage lockout (UVLO) rising threshold | V <sub>UVLO_RISING</sub> | Rising                                                                                                                               | 2.4   | 2.61 | 2.8   | V                |

| UVLO hysteresis                               | V <sub>UVLO_HYS</sub>    |                                                                                                                                      |       | 190  |       | mV               |

| Input current                                 | lin                      | Load = 0A                                                                                                                            |       | 7    |       | mA               |

| Input current                                 | IIN                      | Load = 0.2A                                                                                                                          |       | 370  |       | mA               |

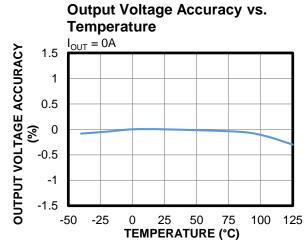

| Output valtage (\/ )                          |                          | $V_{IN} = 4.5V$ to 5.5V, load = 0A, $T_{J} = 25$ °C                                                                                  | 4.925 | 5    | 5.075 | V                |

| Output voltage (Vout) accuracy                | Vout_acc                 | $V_{IN} = 4.5V$ to 5.5V, load = 0A,<br>$T_{J} = -40^{\circ}\text{C}$ to +125°C                                                       | 4.9   | 5    | 5.1   | V                |

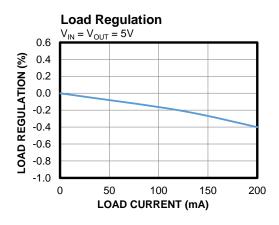

| Load Regulation                               |                          | Load = 0A to 0.2A                                                                                                                    |       | 0.4  | 2.5   | %                |

| Line Degulation                               |                          | Load = 0.2A, V <sub>IN</sub> = 4.75V to 5.25V                                                                                        |       | 1.5  |       | %                |

| Line Regulation                               |                          | Load = $0.2A$ , $V_{IN} = 4.5V$ to $5.5V$                                                                                            |       | 3    |       | %                |

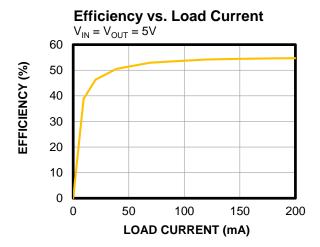

| Efficiency                                    |                          | Load = 0.2A                                                                                                                          |       | 54   |       | %                |

| Ripple                                        |                          | Load = 0A to 0.2A, T <sub>A</sub> = 25°C                                                                                             |       | 50   | 100   | mV               |

| Capacitive Load                               |                          | With 40Ω resistance load                                                                                                             | 330   |      |       | μF               |

| Isolation voltage<br>(MID1W0505AGY-2S)        | V <sub>ISO_2S</sub>      | V <sub>TEST</sub> = V <sub>ISO</sub> for 60s (qualification),<br>V <sub>TEST</sub> = 1.2 x V <sub>ISO</sub> for 1s (100% production) | 1.5   |      |       | kV <sub>DC</sub> |

| Isolation voltage<br>(MID1W0505AGY-3S)        | V <sub>ISO_3S</sub>      | $V_{TEST} = V_{ISO}$ for 60s (qualification),<br>$V_{TEST} = 1.2 \text{ x } V_{ISO}$ for 1s (100% production)                        | 3     |      |       | kV <sub>DC</sub> |

| Thermal shutdown (7)                          | T <sub>SD</sub>          |                                                                                                                                      |       | 160  |       | °C               |

| Thermal shutdown hysteresis (7)               | T <sub>SD_HYS</sub>      |                                                                                                                                      |       | 20   |       | °C               |

# **PACKAGE PARAMETERS**

| Parameter                            | Symbol           | Condition                                                                                                                                         | Min | Тур | Max | Units |

|--------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Minimum external air gap (clearance) | L <sub>101</sub> |                                                                                                                                                   |     | 8   |     | mm    |

| Minimum external tracking (creepage) | L <sub>IO2</sub> |                                                                                                                                                   |     | 8   |     | mm    |

| Input to output capacitance (7)      | Cı-o             | Measure as a 2-terminal device, pin 1 to pin 8 are shorted together, pin 9 to pin 16 are shorted together, f <sub>SW</sub> = 1MHz                 |     | 7   |     | pF    |

| Input to output resistance (7)       | RI-O             | Measure as a 2-terminal device, pin 1 to pin 8 are shorted together, pin 9 to pin 16 are shorted together, V <sub>TEST</sub> = 500V <sub>DC</sub> | 50  |     |     | GΩ    |

- 6) Guaranteed by over-temperature correlation. Not tested in production.

- 7) Guaranteed by sample characterization. Not tested in production.

# TYPICAL CHARACTERISTICS

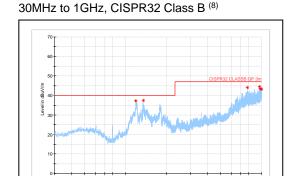

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $C_{IN} = C_{OUT} = 10\mu F$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

**Radiated Emission**

#### Note:

8) See Figure 2 on page 9 and Figure 3 on page 10 for details on the EMI circuit and PCB layout.

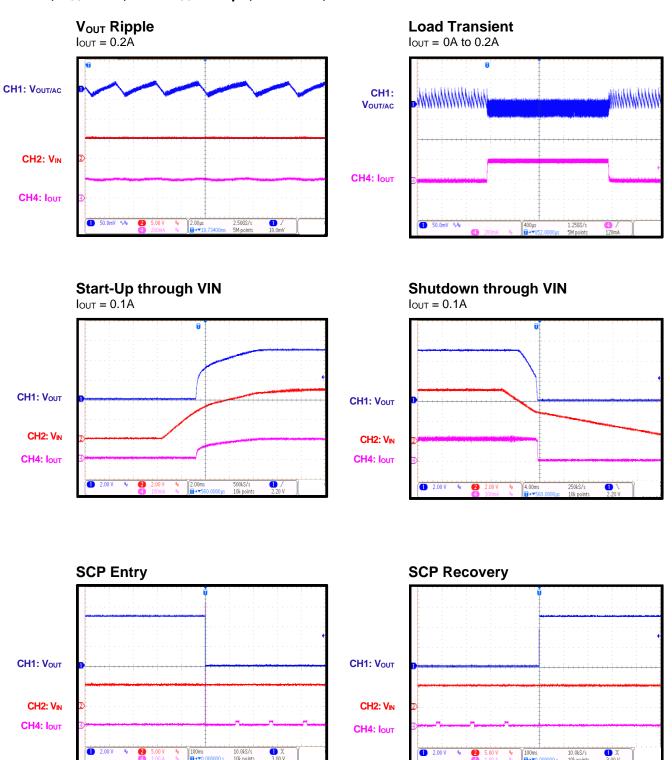

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $C_{IN} = C_{OUT} = 10\mu F$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

© 2023 MPS. All Rights Reserved.

6

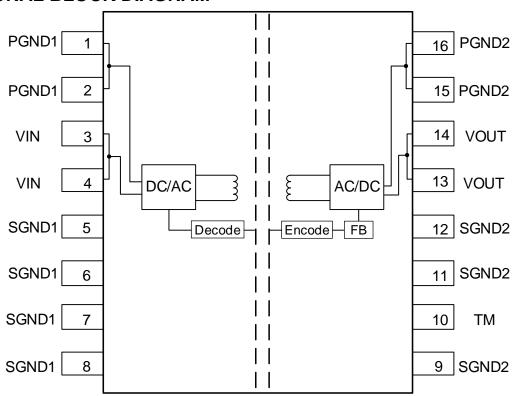

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

7

#### **OPERATION**

The MID1W0505A is a semi-regulated, isolated DC/DC converter that can support 4.5V to 5.5V input voltage ( $V_{IN}$ ) applications across a -40°C to +125°C operating temperature range. It has excellent load regulation, line regulation, and supports up to 1W of output power ( $P_{OUT}$ ).

# **Under-Voltage Lockout (UVLO) Protection**

The MID1W0505A has input under-voltage lockout (UVLO) protection to ensure reliable  $P_{\text{OUT}}$ . The MID1W0505A starts up once  $V_{\text{IN}}$  exceeds the UVLO rising threshold. The device shuts down when  $V_{\text{IN}}$  drops below the UVLO falling threshold. This function prevents the device from operating at an insufficient voltage. UVLO is a non-latch protection.

#### **Isolation Power Conversion**

The MID1W0505A integrates a power MOSFET, transformer, and feedback (FB) circuit all in one chip, making it a high-performance, small-sized solution.

If  $V_{\text{OUT}}$  is below the target voltage, the IC starts switching to deliver power from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$ . If  $V_{\text{OUT}}$  exceeds the target voltage, the device stops switching.

# Power Converter Soft Start (SS) and Short-Circuit Protection (SCP)

To avoid overshoot and inrush current during start-up, the MID1W0505A has built-in internal soft start (SS) that gradually ramps up the output current ( $I_{OUT}$ ).

The soft-start time ( $t_{SS}$ ) is internally set to about 15ms. If  $V_{OUT}$  does not exceed 2.61V after  $t_{SS}$

due to a short circuit or large capacitive load, the MID1W0505A enters hiccup mode. The hiccup off time ( $t_{\text{OFF}}$ ) is about 150ms. After the hiccup mode  $t_{\text{OFF}}$ , the MID1W0505A initiates another SS. If the short circuit is removed, then the MID1W0505A resumes normal operation.

### **Semi-Regulated Output Voltage Regulation**

The MID1W0505A is a 1W (5V/200mA), isolated converter with 0.4%  $V_{\text{OUT}}$  regulation accuracy at typical input voltages (e.g. 5V) across the full 0A to 200mA load range. Under corner case conditions, such as low input voltages (e.g. 4.5V), full loads (e.g. 200mA) and high temperatures (e.g.  $T_A = 85^{\circ}\text{C}$ ),  $V_{\text{OUT}}$  regulation accuracy may drop to 10%. Therefore,  $V_{\text{OUT}}$  is considered semi-regulated. Semi-regulated output accuracy is adequate for most applications. In applications with a smaller  $V_{\text{OUT}}$  regulation requirement (<2%), it is recommended to operate the device at input voltages above 4.75V.

A semi-regulated device is more advantageous than an unregulated device. An unregulated device can cause damage to downstream devices, and may require an external dummy load.

#### **Thermal Protection**

The MID1W0505A monitors the IC temperature internally. If the die temperature exceeds 160°C, the driver outputs are disabled. Once the junction temperature (T<sub>J</sub>) drops to 140°C, the driver outputs are enabled again and the device resumes normal operation.

# **APPLICATION INFORMATION**

## **Selecting the Input and Output Capacitors**

For stable operation, connect a decoupling capacitor between the VIN and PGND1 pins at the input side, and one between the VOUT and PGND2 pins at the output side. Place these decoupling capacitors as close to VIN and VOUT as possible.

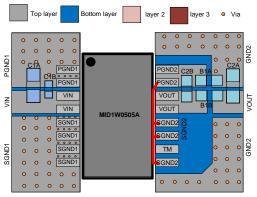

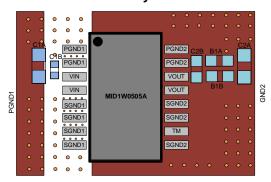

## **EMI Optimization**

The first technique to reduce EMI is to build a low-ESL Y-capacitor using a 4-layer PCB layout to filter high-frequency noise on the secondary side. The Y-capacitor is formed with the two overlapping middle layers. Mid-layer 1 is the PGND1 copper plane, which forms the Y-capacitor's top plate. Mid-layer 2 is the ground after the ferrite bead (GND2), which forms the Y-capacitor's bottom plate. More overlap in these layers provides a larger Y-capacitor value, which further reduces EMI. The second technique to reduce EMI is to use stitching vias

on the GND planes to suppress electromagnetic transmissions.

Aside from the two PCB layout techniques described above, a pair of ferrite beads are required to form a CLC structure filter (see Figure 2). Place this filter as close to VOUT and PGND2 as possible. The capacitor closest to the IC (C2B) should be ≥4.7µF to ensure a stable output. Do not place large copper areas on the secondary side pins, as this can increase switching noise and EMI. Connect SGND2 and PGND2 using a thin trace.

Figure 2: Recommended EMI Schematic

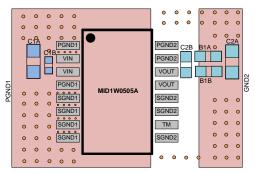

# **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation. For the best results, refer to Figure 3 and follow the guidelines below:

- For safety, the primary side and secondary side should be physically separated. Ensure that the creepage/clearance meets the standards for the specified application.

- 2. To reduce output noise, minimize the loop area between VIN, the input capacitor, and PGND1, as well as VOUT, the output capacitor, and PGND2.

- 3. Place enough copper and vias around the IC's primary pin output to improve thermal performance.

- 4. Connect SGND1 and PGND1 using large copper traces and multiple vias to improve thermal dissipation.

- 5. Connect SGND2 and PGND2 using a thin trace (below the red trace in Figure 3) to reduce radiation.

**Top Layer and Bottom Layer**

Mid-Layer 1

Mid-Layer 2

Figure 3: Recommended PCB Layout

# TYPICAL APPLICATION CIRCUIT

**Figure 4: Application Circuit**

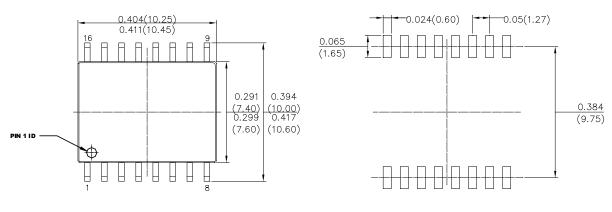

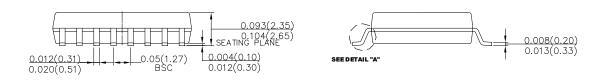

# **PACKAGE INFORMATION**

# SOICW-16

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

#### **FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-013, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

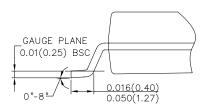

# **CARRIER INFORMATION**

| Part Number           | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Quantity/<br>Tray | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|-----------------------|------------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|

| MID1W0505AGY-<br>2S-Z | COLOW 40               | 4000              | 4.4               | NI/A              | 40in             | 0.4 =====                | 10                       |

| MID1W0505AGY-<br>3S-Z | SOICW-16               | 1000              | 44                | N/A               | 13in             | 24mm                     | 12mm                     |

# **REVISION HISTORY**

| Revision # | Revision Date | Description                                                                 | Pages Updated |

|------------|---------------|-----------------------------------------------------------------------------|---------------|

| 1.0        | 2/10/2023     | Initial Release                                                             | -             |

|            |               | Corrected typo in page 1 header                                             | 1             |

| 1.1        | 6/12/2023     | Updated descriptions for TM, VOUT, and PGND2 pins; minor formatting updates | 3             |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.