# 1-Cell to 2-Cell, 26V Input, 1A Linear Charger with EN Control and Configurable JEITA

#### DESCRIPTION

The MP2702 is a linear charger for 1-cell to 2-cell Li-ion, Li-polymer, and LiFePO4, and 2-cell to 6-cell NiMH batteries. The device can sustain a voltage up to 26V.

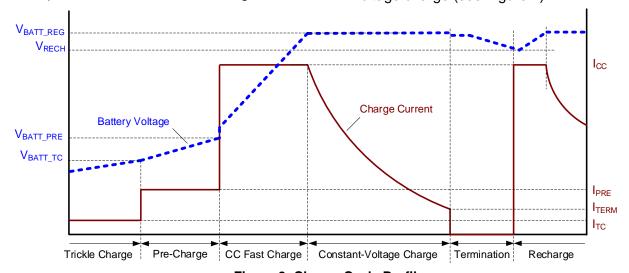

The MP2702 measures the battery voltage  $(V_{BATT})$  and automatically charges the battery in four phases: trickle charge, pre-charge, constant-current (CC) fast charge, and constant-voltage charge.

The MP2702 provides a dedicated ISET pin to set the charge current by connecting a resistor between ISET and ground. The device also provides a USBM pin to set the input current limit ( $I_{\text{IN\_LIM}}$ ) prior to setting the charge current. If the input power is overloaded, the MP2702 has a minimum input voltage limit ( $V_{\text{IN\_LIM}}$ ) to reduce battery current.

The MP2702 has robust protection features including input and battery over-voltage protection (OVP), a charge safety timer, and battery temperature protection compliant with the JEITA standard.

The MP2702 provides a dedicated EN pin to enable or disable charging. Once charging is disabled, the quiescent current (I<sub>Q</sub>) flowing into either the IN or BATT pin is minimized.

In addition, the MP2702 provides two opendrain pins to indicate the input power status and charge status. The ACOK pin indicates whether the input power is present. The CHG pin indicates several states of charging, including charging, termination, and fault events.

The MP2702 also offers flexible one-time programmable (OTP) memory to configure a variety of charge parameters.

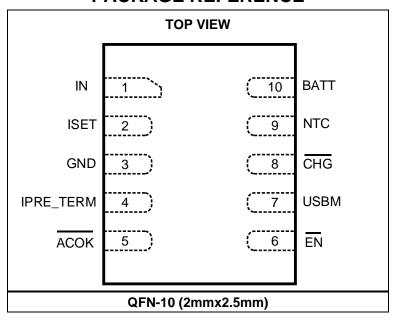

The MP2702 is available in a QFN-10 (2mmx2.5mm) package.

#### **FEATURES**

- Up to 26V of Sustainable Voltage

- Up to 1A of Charge Current Configurable via the ISET Pin

- ISET Pin Short-Circuit Protection (SCP)

- Additional Input Current Limit (I<sub>IN\_LIM</sub>) Setting via the USBM Pin

- Configurable Pre-Charge Current (I<sub>PRE</sub>)

- Configurable Termination Current (I<sub>TERM</sub>)

Threshold

- One-Time Programmable (OTP) Memory Selection for Three Levels of the Minimum Input Voltage Limit (V<sub>IN\_LIM</sub>)

- OTP Selection for Battery-Full Voltage from 2.4V to 4.5V Per Cell

- 0.5% Battery Regulation Voltage Accuracy

- OTP Selection for 1-Cell or 2-Cell Battery

- Integrated Chip Junction Temperature (T<sub>J</sub>) Regulation

- Battery Temperature Protection Compliant with JEITA Standard

- EN Pin to Enable the Whole Chip

- 100nA Battery Leakage Current in Shutdown Mode

- Down to 3mA I<sub>TERM</sub>

- Charge Status and Fault Indication

- Input Power Indication

- Integrated Charge Safety Timer

- OTP for Miscellaneous Parameters

- Provides Option for Charging 2-Cell to 6-Cell NiMH Battery

- Compatible with LiFePO4 Battery

- Available in a Compact QFN-10 (2mmx2.5mm) Package

#### **APPLICATIONS**

- Headphones

- Wearable Devices

- Emergency Calls

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

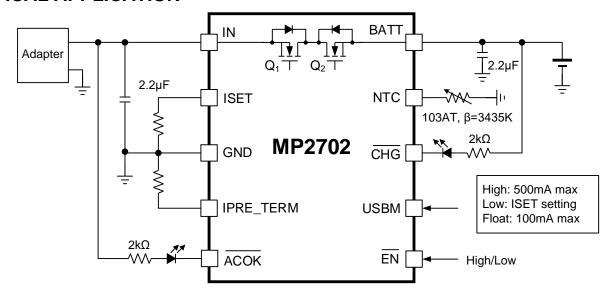

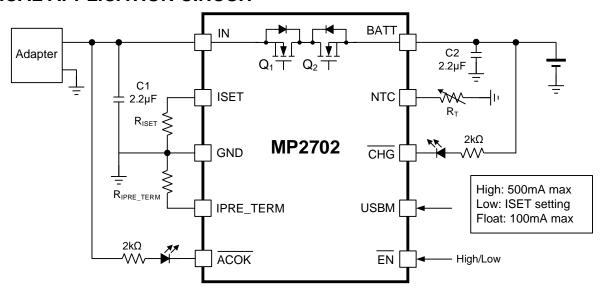

# **TYPICAL APPLICATION**

#### ORDERING INFORMATION

| Part Number*     | Package            | Top Marking | MSL Rating |

|------------------|--------------------|-------------|------------|

| MP2702GRP-xxxx** | QFN-10 (2mmx2.5mm) | See Below   | 1          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP2702GRP-xxxx-Z).

#### **TOP MARKING**

LCY

LLL

LC: Product code of MP2702GRP-xxxx

Y: Year code LLL: Lot number

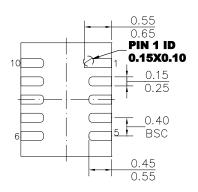

### **PACKAGE REFERENCE**

<sup>\*\*&</sup>quot;xxxx" is the register setting option. The factory default is "0000". This content can be viewed in the OTP register map. Please contact an MPS FAE to obtain an "xxxx" value.

# **PIN FUNCTIONS**

| Pin # | Name      | Type (1) | Description                                                                                                                                                                                                                        |

|-------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | IN        | Р        | <b>Power input of the IC.</b> Place a 1μF to 10μF bypass capacitor between the IN and GND pins.                                                                                                                                    |

| 2     | ISET      | AI       | <b>Charge current setting.</b> Connect a resistor between the ISET and GND pins to set the fast charge current, which should range between 20mA and 1A.                                                                            |

| 3     | GND       | Р        | Ground terminal.                                                                                                                                                                                                                   |

| 4     | IPRE_TERM | Al       | <b>Pre-charge and termination current setting.</b> Connect a resistor between the IPRE_TERM and GND pins to set the pre-charge current (I <sub>PRE</sub> ) and termination current (I <sub>TERM</sub> ).                           |

| 5     | ACOK      | DO       | Input power status indication. The ACOK pin is an open-drain output. If the input voltage (V <sub>IN</sub> ) exceeds its under-voltage lockout (UVLO) threshold                                                                    |

|       |           |          | (V <sub>IN_UVLO</sub> ) and the battery voltage (V <sub>BATT</sub> ), then ACOK is pulled low.                                                                                                                                     |

| 6     | EN        | DI       | Chip enable control. The EN pin is active low. When EN is floated, the chip is enabled by default. When the chip is disabled, all blocks including the ACOK indicator do not work.                                                 |

| 7     | USBM      | DI       | Input current limit setting. The USBM pin configures the input current limit (I <sub>IN_LIM</sub> ) for USB or adapter sources, where high = 500mA max, low = ISET setting, and floating = 100mA max. Do not pull USBM above 3.6V. |

| 8     |           | DO       | Charge status indication. If the CHG pin is pulled low, this indicates                                                                                                                                                             |

| 0     | CHG       | ВО       | charging. If CHG is open drain, this indicates either no charging or charge complete.                                                                                                                                              |

| 9     | NTC       | AI       | <b>Temperature-sense input.</b> Connect a negative temperature coefficient (NTC) thermistor between the NTC and GND pins. Pull the NTC pin to ground to disable charging.                                                          |

| 10    | BATT      | Р        | <b>Battery terminal.</b> Place a $1\mu F$ to $10\mu F$ bypass capacitor between the BATT and GND pins.                                                                                                                             |

#### Note:

1) Al refers to analog input, DI refers to digital input, DO refers to digital output, and P refers to power.

#### **ABSOLUTE MAXIMUM RATINGS (2)**

| IN, ACOK, CHG to GND0.3V to +26V                             |

|--------------------------------------------------------------|

| BATT to GND 0.3V to +26V<br>All other pins to GND0.3V to +5V |

| Continuous power dissipation ( $T_A = 25^{\circ}C$ ) (3)     |

| 1.78W                                                        |

| Junction temperature (T <sub>J</sub> )150°C                  |

| Lead temperature (solder)260°C                               |

| Storage temperature65°C to +150°C                            |

| ESD Ratings                                                  |

| Human body model (HBM) (4) 1.5kV                             |

| Charged-device model (CDM) (5)                               |

| Recommended Operating Conditions (6)                         |

| Supply voltage (V <sub>IN</sub> )Up to 13.5V                 |

| Input current (I <sub>IN</sub> )Up to 1A                     |

| Constant-current fast charge current (I <sub>CC</sub> )      |

| <del>-</del>                                                 |

| Up to 1A                                                     |

| Battery voltage (V <sub>BATT</sub> )Up to 1A                 |

| Thermal Resistance (7) | $oldsymbol{	heta}$ JA | $oldsymbol{	heta}$ JC |      |

|------------------------|-----------------------|-----------------------|------|

| QFN-10 (2mmx2.5mm)     | 88                    | 13                    | °C/W |

#### Notes:

- 2) Exceeding these ratings may damage the device.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A)$  /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation may generate an excessive die temperature, which can cause the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 4) Per ANSI/ESDA/JEDEC JS-001, all pins.

- 5) Per ANSI/ESDA/JEDEC JS-002, all pins.

- 6) The device is not guaranteed to function outside of its operating conditions.

- 7) Measured on a JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 5V$ ,  $V_{BATT} = 3.7V$ ,  $V_{BATT\_REG} = 4.2V/cell$ ,  $T_A = -40$ °C to +125°C, unless otherwise noted.

| Parameter                                                                 | Symbol                   | Condition                                                                  | Min  | Тур  | Max | Units   |

|---------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------|------|------|-----|---------|

| Input Power Characteristic                                                | s                        |                                                                            |      |      | •   | •       |

| Input under-voltage lockout (UVLO) threshold                              | V <sub>IN_UVLO</sub>     | V <sub>IN</sub> falling                                                    | 3.4  | 3.6  | 3.8 | V       |

| Input UVLO threshold hysteresis                                           | VIN_UVLO_HYS             | V <sub>IN</sub> rising                                                     |      | 340  |     | mV      |

|                                                                           |                          | V <sub>IN</sub> rising, 1 cell                                             |      | 200  |     | mV      |

| Input voltage (V <sub>IN</sub> ) vs. battery voltage (V <sub>BATT</sub> ) | V <sub>HDRM</sub>        | V <sub>IN</sub> rising, 2 cells                                            |      | 240  |     | mV      |

| headroom threshold                                                        | VHDRM                    | V <sub>IN</sub> falling, 1 cell                                            | 10   | 100  | 190 | mV      |

|                                                                           |                          | V <sub>IN</sub> falling, 2 cells                                           | 20   | 130  | 240 | mV      |

| Input power good (PG) rising deglitch time                                | $t_{VIN\_GD}$            | V <sub>IN</sub> rising                                                     |      | 30   |     | ms      |

| Input over-voltage                                                        | V                        | V <sub>IN</sub> rising, 1 cell                                             | 5.8  | 6    | 6.2 | V       |

| protection (OVP) threshold                                                | $V_{IN\_OVP}$            | V <sub>IN</sub> rising, 2 cells                                            | 13.8 | 14.4 | 15  | V       |

| Input OVP hysteresis                                                      | V <sub>IN_OVP_HYS</sub>  | V <sub>IN</sub> falling, 1 cell                                            |      | 220  |     | mV      |

| input OVF flysteresis                                                     | VIN_OVP_HYS              | V <sub>IN</sub> falling, 2 cells                                           |      | 550  |     | mV      |

| Input OVP deglitch time                                                   | tvin_ovp                 | V <sub>IN</sub> rising                                                     |      | 100  |     | μs      |

| Input OVP recovery deglitch time                                          |                          | V <sub>IN</sub> falling                                                    |      | 30   |     | ms      |

|                                                                           | Іш_Q                     | V <sub>IN</sub> = 5V, part is disabled via EN                              |      | 1    | 3.8 | μΑ      |

| Input shutdown current                                                    |                          | $V_{IN} = 5V$ , charge is disabled by pulling NTC to GND                   |      | 260  | 350 | μΑ      |

|                                                                           |                          | V <sub>IN</sub> = 5V, charge termination                                   |      | 460  | 550 | μΑ      |

| BATT leakage current in shutdown mode                                     | I <sub>BATT_SHDN</sub>   | V <sub>BATT</sub> = 4.2V (1 cell) or 8.4V (2 cells), V <sub>IN</sub> = GND |      | 0.1  | 1   | μΑ      |

| Battery quiescent current                                                 | I <sub>BATT_Q</sub>      | V <sub>IN</sub> = 5V, 1 cell, charge terminated                            |      | 3.8  | 5   | μΑ      |

| after termination                                                         |                          | V <sub>IN</sub> = 9V, 2 cells, charge terminated                           |      | 5.6  | 7.2 | μA      |

| Battery Charger ( $T_A = 0$ °C t                                          | o 70°C)                  |                                                                            |      |      |     |         |

| IN to BATT on resistance                                                  | Ron_Q1+Q2                |                                                                            |      | 370  |     | mΩ      |

| Trickle charge to pre-<br>charge threshold                                | Vватт_тс                 | V <sub>BATT</sub> rising                                                   | 0.9  | 1    | 1.1 | V/cell  |

| Trickle charge to pre-<br>charge threshold hysteresis                     | V <sub>BATT_TC_HYS</sub> | V <sub>BATT</sub> falling                                                  |      | 100  |     | mV/cell |

| Trickle charge current                                                    | I <sub>TC</sub>          | $R_{ISET} = 550\Omega$                                                     | 28   | 50   | 72  | mA      |

| THOME CHAIGE CUITEIL                                                      | 110                      | Minimum clamp                                                              | 1    | 3    | 5.5 | mA      |

|                                                                           |                          | VBATT_PRE = 2.5V/cell                                                      | 2.4  | 2.5  | 2.6 |         |

| Pre-charge to fast charge                                                 | V <sub>BATT_PRE</sub>    | VBATT_PRE = 2.8V/cell                                                      | 2.7  | 2.8  | 2.9 | Weell   |

| threshold                                                                 | A RATI_LKE               | VBATT_PRE = 3V/cell                                                        | 2.9  | 3    | 3.1 | V/cell  |

|                                                                           |                          | VBATT_PRE = 3.2V/cell                                                      | 3.1  | 3.2  | 3.3 |         |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $V_{BATT} = 3.7V$ ,  $V_{BATT\_REG} = 4.2V/cell$ ,  $T_A = -40$ °C to +125°C, unless otherwise noted.

| Parameter                                | Symbol                 | Condition                                                | Min   | Тур  | Max   | Units   |

|------------------------------------------|------------------------|----------------------------------------------------------|-------|------|-------|---------|

| Pre-charge to fast charge deglitch time  | tpre_cc                |                                                          |       | 30   |       | ms      |

| Fast charge to pre-charge deglitch time  | t <sub>CC_PRE</sub>    |                                                          |       | 30   |       | ms      |

|                                          |                        | Float IPRE_TERM, $R_{ISET} = 1.1k\Omega$                 | 88    | 100  | 112   | mA      |

|                                          |                        | Float IPRE_TERM, $R_{ISET} = 550\Omega$                  | 160   | 200  | 240   | mA      |

|                                          |                        | $R_{IPRE\_TERM} = 2.26k\Omega$ , $R_{ISET} = 1.1k\Omega$ | 75    | 100  | 125   | mA      |

| Pre-charge current                       | I <sub>PRE</sub>       | $R_{IPRE\_TERM} = 2.26k\Omega$ , $R_{ISET} = 550\Omega$  | 145   | 202  | 258   | mA      |

|                                          |                        | $R_{IPRE\_TERM} = 1.13k\Omega$ , $R_{ISET} = 1.1k\Omega$ | 32    | 50   | 66    | mA      |

|                                          |                        | $R_{IPRE\_TERM} = 1.13k\Omega$ , $R_{ISET} = 550\Omega$  | 70    | 100  | 130   | mA      |

|                                          |                        | Minimum clamp                                            | 1     | 3    | 5.5   | mA      |

|                                          |                        | R <sub>ISET</sub> = 786Ω                                 | 665   | 700  | 735   | mA      |

| Constant-current fast charge current     | Icc                    | $R_{ISET} = 11k\Omega$                                   | 45    | 50   | 55    | mA      |

| charge current                           |                        | $R_{ISET} = 27.5k\Omega$                                 | 15    | 20   | 25    | mA      |

| Over-charge (OC) current protection      | loc                    | $R_{ISET} = 0\Omega$                                     |       | 1.25 |       | Α       |

|                                          |                        | VBATT_REG = 3.6V/cell                                    | 3.582 | 3.6  | 3.618 |         |

|                                          |                        | VBATT_REG = 4.1V/cell                                    | 4.080 | 4.1  | 4.121 | 1       |

| Battery charge regulation voltage        | VBATT_REG              | VBATT_REG = 4.2V/cell                                    | 4.179 | 4.2  | 4.221 | V/cell  |

|                                          |                        | VBATT_REG = 4.35V/cell                                   | 4.328 | 4.35 | 4.372 |         |

|                                          |                        | VBATT_REG = 4.5V/cell                                    | 4.478 | 4.5  | 4.523 |         |

|                                          |                        | $R_{IPRE\_TERM} = 2.26k\Omega$ , $R_{ISET} = 1.1k\Omega$ | 38    | 50   | 62    | mA      |

|                                          |                        | RIPRE_TERM = $2.26k\Omega$ , RISET = $550\Omega$         | 74    | 100  | 126   | mA      |

| Battery charge termination threshold     | I <sub>TERM</sub>      | $R_{IPRE\_TERM} = 1.13k\Omega$ , $R_{ISET} = 1.1k\Omega$ | 12    | 22   | 31    | mA      |

| terrimation theshold                     |                        | $R_{IPRE\_TERM} = 1.13k\Omega$ , $R_{ISET} = 550\Omega$  | 32    | 48   | 64    | mA      |

|                                          |                        | Minimum clamp                                            | 1     | 3    | 5.5   | mA      |

| Charge termination deglitch time         | tterm_dgl              |                                                          |       | 30   |       | ms      |

| Automatic recharge voltage threshold     | V <sub>RECH</sub>      | Below VBATT_REG                                          | 135   | 200  | 265   | mV/cell |

| Automatic recharge voltage deglitch time | trech_dgl              |                                                          |       | 30   |       | ms      |

| Battery OVP threshold                    | V <sub>BATT_OVP</sub>  | Compared to VBATT_REG and VBATT rising                   | 85    | 150  | 215   | mV/cell |

| Battery OVP threshold                    | V <sub>BATT_OVP_</sub> | Compared to VBATT_OVP and VBATT                          |       | 30   |       | mV/cell |

| hysteresis                               | HYS                    | falling                                                  |       |      |       | ,       |

| Input Voltage and Input C                | urrent Regul           |                                                          |       |      | 1.55  | 1       |

| Input current limit                      | I <sub>IN_LIM</sub>    | Float USBM                                               | 80    | 90   | 100   | mA      |

| •                                        |                        | USBM = high                                              | 405   | 450  | 500   |         |

|                                          |                        | VIN_LIM = 4.375V/cell                                    | 4.25  | 4.37 | 4.49  | 1       |

| Minimum V <sub>IN</sub> limit            | $V_{IN\_LIM}$          | VIN_LIM = 4.5V/cell                                      | 4.37  | 4.5  | 4.6   | V/cell  |

|                                          |                        | VIN_LIM = 4.75V/cell                                     | 4.63  | 4.75 | 4.87  |         |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $V_{BATT} = 3.7V$ ,  $V_{BATT\_REG} = 4.2V/cell$ ,  $T_A = -40$ °C to +125°C, unless otherwise noted.

| Parameter                                                          | Symbol                  | Condition                                        | Min  | Тур  | Max  | Units |

|--------------------------------------------------------------------|-------------------------|--------------------------------------------------|------|------|------|-------|

| Thermal Protection                                                 |                         |                                                  |      |      |      |       |

| Thermal shutdown rising threshold <sup>(8)</sup>                   | T <sub>J_SHDN</sub>     | T <sub>J</sub> rising                            |      | 160  |      | °C    |

| Thermal shutdown hysteresis (8)                                    | T <sub>J_SHDN_HYS</sub> |                                                  |      | 20   |      | °C    |

| Thermal regulation (8)                                             | $T_{J\_REG}$            |                                                  |      | 120  |      | °C    |

| <b>Battery Temperature Mor</b>                                     | nitoring and F          | Protection                                       |      |      |      |       |

| Negative temperature coefficient (NTC) bias current                | I <sub>NTC</sub>        |                                                  | 47.5 | 50   | 52   | μΑ    |

| Cold temperature threshold                                         | Vcold                   | V <sub>NTC</sub> = 1V to 1.5V, VCOLD = 0°C       | 1363 | 1377 | 1391 | mV    |

| Cold temperature threshold hysteresis                              | Vcold_Hys               | V <sub>NTC</sub> = 1.5V to 1V, VCOLD = 0°C       |      | 90   |      | mV    |

| Cool temperature threshold                                         | V <sub>COOL</sub>       | $V_{NTC} = 0.5V$ to 1V, VCOOL = 10°C             | 893  | 902  | 915  | mV    |

| Cool temperature threshold hysteresis                              | Vcool_hys               | V <sub>NTC</sub> = 1V to 0.5V, VCOOL = 10°C      |      | 34   |      | mV    |

| Warm temperature threshold                                         | Vwarm                   | V <sub>NTC</sub> = 0.5V to 0.2V,<br>VWARM = 45°C | 239  | 245  | 251  | mV    |

| Warm temperature threshold hysteresis                              | Vwarm_hys               | V <sub>NTC</sub> = 0.2V to 0.5V,<br>VWARM = 45°C |      | 11   |      | mV    |

| Hot temperature threshold                                          | V <sub>НОТ</sub>        | V <sub>NTC</sub> = 0.2 to 0.1V, VHOT = 60°C      | 138  | 151  | 157  | mV    |

| Hot temperature threshold hysteresis                               | V <sub>HOT_HYS</sub>    | V <sub>NTC</sub> = 0.1 to 0.2V, VHOT = 60°C      |      | 11   |      | mV    |

| NTC enable charge threshold                                        |                         | V <sub>NTC</sub> = 0V to 0.15V                   | 75   | 90   | 105  | mV    |

| NTC enable charge threshold hysteresis                             |                         | V <sub>NTC</sub> = 0.15V to 0V                   |      | 15   |      | mV    |

| NTC bias current when<br>the charge is disabled via<br>the NTC pin |                         | V <sub>NTC</sub> = 0V                            | 20   | 30   | 40   | μΑ    |

| NTC charge termination disable threshold                           |                         | V <sub>NTC</sub> rising                          | 2.4  | 2.5  | 2.6  | V     |

| NTC charge termination disable threshold hysteresis                |                         | V <sub>NTC</sub> falling                         |      | 100  |      | mV    |

| NTC minimum bias current when NTC is floated                       | I <sub>NTC_FLT</sub>    | V <sub>NTC</sub> = 3V                            | 3    | 4.5  | 6    | μΑ    |

| Floated NTC voltage                                                | V <sub>NTC_FLT</sub>    |                                                  |      | 3.6  |      | V     |

#### Note:

8) Guaranteed by design.

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $V_{BATT} = 3.7V$ ,  $V_{BATT\_REG} = 4.2V/cell$ ,  $T_A = -40$ °C to +125°C, unless otherwise noted.

| Parameter                               | Symbol                                  | Condition                  | Min | Тур | Max  | Units    |  |  |

|-----------------------------------------|-----------------------------------------|----------------------------|-----|-----|------|----------|--|--|

| Open-Drain Pin Characte                 | Open-Drain Pin Characteristics          |                            |     |     |      |          |  |  |

| CHG pin output voltage                  |                                         | Isink = 5mA                |     |     | 0.4  | V        |  |  |

| ACOK pin output voltage                 |                                         | Isink = 5mA                |     |     | 0.4  | <b>V</b> |  |  |

| Logic Levels on the USB                 | Logic Levels on the USBM and EN Pins    |                            |     |     |      |          |  |  |

| Logic low input voltage                 | VIL                                     |                            |     |     | 0.4  | V        |  |  |

| Logic high input voltage                | VIH                                     |                            | 1.4 |     |      |          |  |  |

| Floated USBM voltage                    | $V_{FLT}$                               |                            | 700 | 900 | 1100 | mV       |  |  |

| Timing Characteristics (T               | $A = 0^{\circ}C \text{ to } 70^{\circ}$ | °C)                        |     |     |      |          |  |  |

| Charge timer                            | t <sub>TMR</sub>                        | t <sub>MR_SET</sub> = 10hr | 8   | 10  | 12   | hr       |  |  |

| Trickle charge and pre-<br>charge timer |                                         |                            | 0.8 | 1   | 1.2  | hr       |  |  |

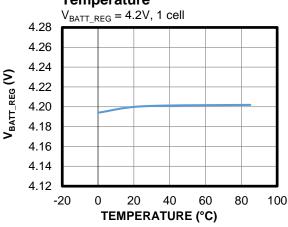

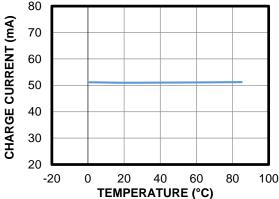

#### TYPICAL CHARACTERISTICS

$V_{IN} = 5V$ ,  $I_{CC} = 1A$ ,  $V_{BATT} = \text{full range}$ , 1 cell,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

# Battery Regulation Voltage vs. Temperature

# Charge Current vs. Temperature $I_{CC} = 50 \text{mA}, V_{IN} = 5 \text{V}, V_{BATT} = 3.8 \text{V}$

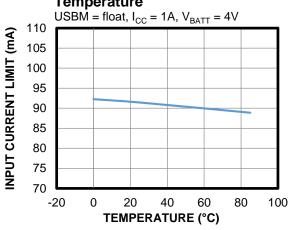

# Input Current Limit vs. Temperature

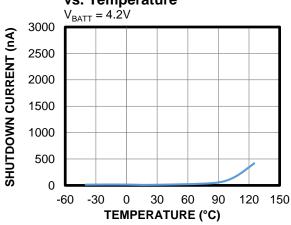

# Battery Shutdown Current vs. Temperature

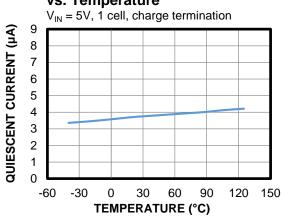

# **Battery Quiescent Current** vs. Temperature

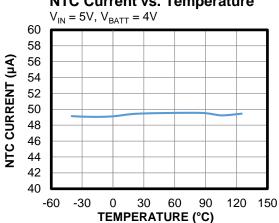

#### **NTC Current vs. Temperature**

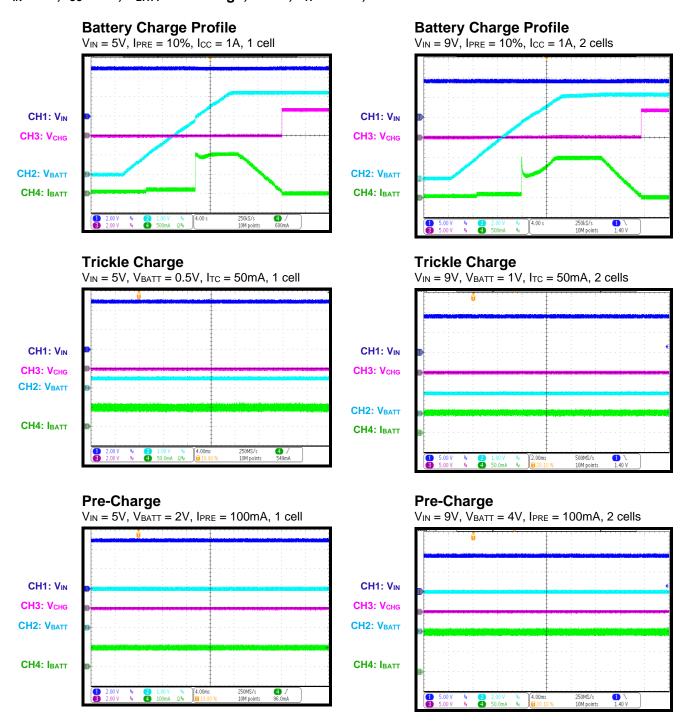

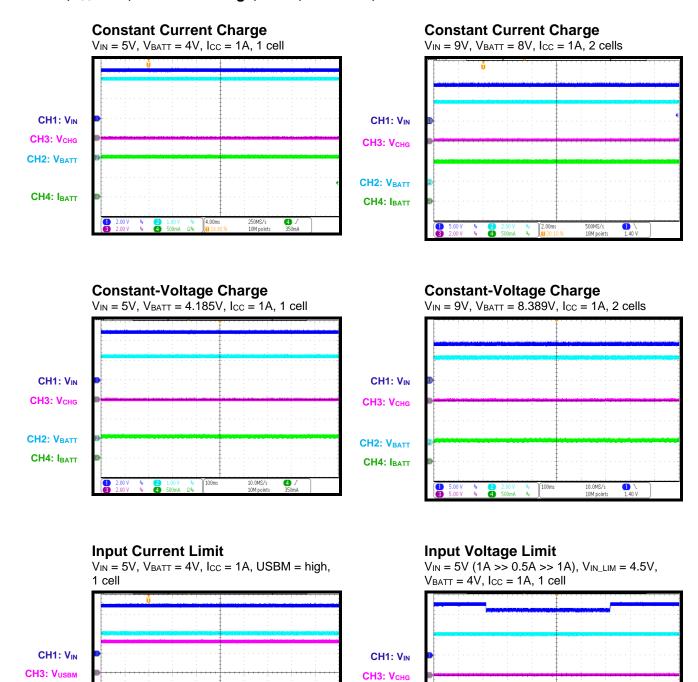

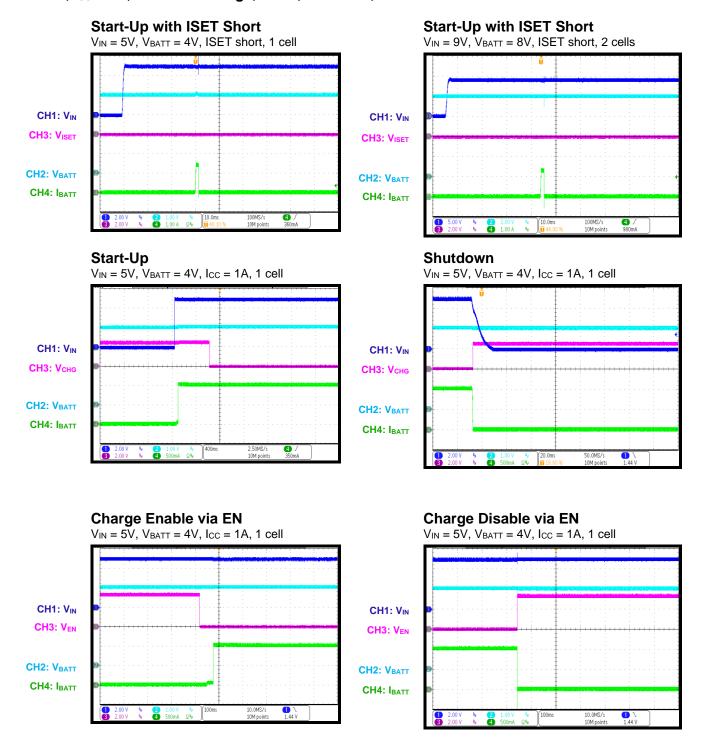

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 5V,  $I_{CC}$  = 1A,  $V_{BATT}$  = full range, 1 cell,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 5V$ ,  $I_{CC} = 1A$ ,  $V_{BATT} =$ full range, 1 cell,  $T_A = 25$ °C, unless otherwise noted.

CH2: VBATT

CH4: IBATT

CH2: VBATT

CH4: IBATT

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 5V$ ,  $I_{CC} = 1A$ ,  $V_{BATT} =$ full range, 1 cell,  $T_A = 25$ °C, unless otherwise noted.

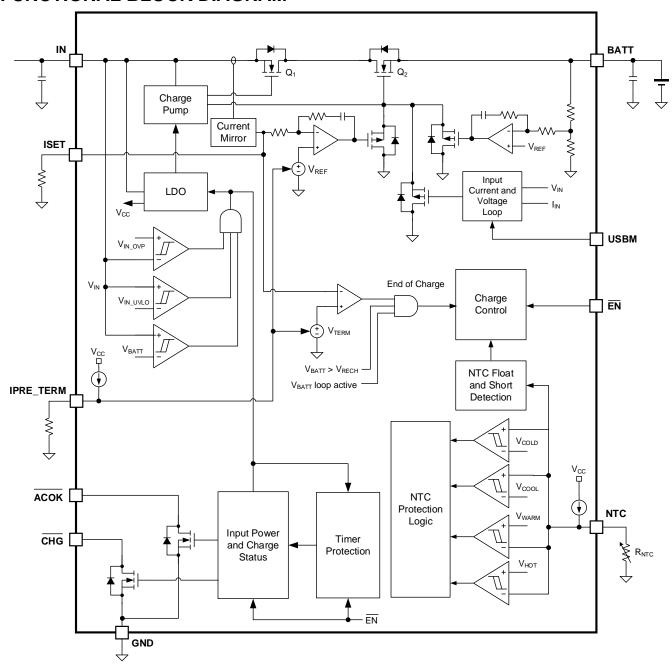

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

#### Introduction

The MP2702 is a linear charger for 1-cell to 2cell Li-ion, Li-polymer, and LiFePO4 battery applications, and 2-cell to 6-cell NiMH battery applications. The device can sustain an input voltage (V<sub>IN</sub>) up to 26V and achieve up to 1A of charge current.

#### **Power Supply**

The IC is powered by the input. Once  $V_{IN}$ exceeds its under-voltage lockout threshold (V<sub>IN UVLO</sub>), the internal control and logic circuit starts to operate. If VIN exceeds both VIN LIVLO and the sum of the battery voltage (VBATT) and the V<sub>IN</sub> vs. V<sub>BATT</sub> headroom threshold (V<sub>HDRM</sub>) (V<sub>BATT</sub> + V<sub>HDRM</sub>), the IC indicates power good (PG), and the ACOK pin is pulled down to GND.

#### **Charge Cycle**

When the input power is qualified as a good power supply, the IC checks V<sub>BATT</sub> and provides four charging phases: trickle charge, pre-charge, constant-current fast charge, and constantvoltage charge (see Figure 2).

Figure 2: Charge Cycle Profile

## Phase 1 (Trickle Charge)

If V<sub>BATT</sub> is below the trickle charge to pre-charge threshold (V<sub>BATT TC</sub>), a trickle charging current is applied on the battery to reset the protection circuit in the battery pack. The trickle charge current ( $I_{TC}$ ) is 5% of the set fast charge current. Once the constant-current fast charge current (I<sub>CC</sub>) x 5% is below 3mA, I<sub>TC</sub> is clamped at 3mA.

#### Phase 2 (Pre-Charge)

If  $V_{BATT}$  exceeds  $V_{BATT}$  TC but remains below the pre-charge to fast charge threshold (V<sub>BATT PRE</sub>), the IC charges the battery with the pre-charge current (I<sub>PRE</sub>). There are four one-time programmable (OTP) memory options available for V<sub>BATT PRE</sub>.

I<sub>PRE</sub> is proportional to the fast charge current and can be configured via the IPRE TERM pin.

#### Phase 3 (Constant-Current Fast Charge)

If  $V_{BATT}$  exceeds  $V_{BATT PRE}$ , the IC enters constant-current fast charge phase. Icc can be set via the ISET pin.

#### Phase 4 (Constant-Voltage Charge)

If V<sub>BATT</sub> rises to the battery charge regulation voltage (V<sub>BATT REG</sub>), the charge current starts to decrease. Once the charge current reaches the battery charge termination threshold (ITERM), the charge cycle is considered complete after the charge termination deglitch time (t<sub>TERM DGL</sub>). If I<sub>TERM</sub> is not reached before the safety charge timer expires, then the charge cycle stops and the corresponding timeout fault signal asserts.

#### **Charge Termination**

If  $V_{BATT}$  reaches the full voltage regulation threshold and the charge current is below  $I_{TERM}$ , charging is terminated after a deglitch time of 30ms. The charge termination can be disabled by floating the NTC pin.

#### **Automatic Recharge**

Once the battery charge cycle completes, the IC remains off. During this time, the external load consumes battery power or the battery self-discharges. A new charge cycle automatically begins once  $V_{BATT}$  drops below the automatic recharge threshold for the 30ms deglitch time. The safety charge timer resets when the automatic recharge cycle begins.

#### **Input Current Limit**

The MP2702 provides an USBM pin to set the input current limit ( $I_{\text{IN\_LIM}}$ ), which has higher priority than configuring the ISET pin. Table 1 shows the  $I_{\text{IN\_LIM}}$  setting. If the charge current exceeds  $I_{\text{IN\_LIM}}$  when USBM is floated or set high, the charge current is limited by  $I_{\text{IN\_LIM}}$ . The logic high voltage at USBM must be below 3.6V.

Table 1: IIN\_LIM Setting

| USBM Level | lin                       |

|------------|---------------------------|

| High       | 500mA max                 |

| Low        | Depending on ISET setting |

| Float      | 100mA max                 |

#### **Minimum Input Voltage Limit**

The MP2702 includes a minimum input voltage limit ( $V_{IN\_LIM}$ ) regulation loop. If the charge current or  $I_{IN\_LIM}$  exceeds the input power supply current rating, the MP2702 automatically reduces the charge current once  $V_{IN}$  reaches  $V_{IN\_LIM}$ . There are three options for setting  $V_{IN\_LIM}$ . See the One-Time Programmable (OTP) Memory Map section on page 21.

#### **Cell Selection**

The MP2702 can support 1-cell and 2-cell batteries. The battery cell counts can be set via the OTP. See the One-Time Programmable (OTP) Memory Map section on page 21.

For 2-cell applications, battery hot insertion or short is not allowed when  $V_{\text{IN}}$  is present and charge is enabled.

#### **Battery Regulation Voltage**

The MP2702 can support a variety of batteryfull voltages ranging between 2.4V/cell to 4.5V/cell with a 50mV step, which are set via the OTP.

#### **Setting the Fast Charge Current**

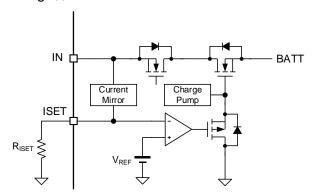

An external resistor connected between the ISET and GND pins configures the fast charge current.

The relationship between  $I_{CC}$  and the ISET resistor ( $R_{ISET}$ ) can be calculated with Equation (1):

$$V_{RFF} = k \times I_{CC} \times R_{ISFT}$$

(1)

Where k is the sense gain of the current mirror.

Icc can be calculated with Equation (2):

$$I_{CC} = \frac{V_{REF}/k}{R_{ISFT}}$$

(2)

Where the reference voltage ( $V_{REF}$ ) is 1.2V, and the k factor is 2.18 x 10<sup>-3</sup>.

Figure 3 shows the functional diagram for setting I<sub>CC</sub> via ISET.

Figure 3: Functional Diagram of Setting Icc via the ISET Pin

The actual fast charge current is the lower value between I<sub>IN\_LIM</sub> and I<sub>CC</sub>. Table 2 on page 17 shows an example of the actual fast charge current at different ISET and USBM settings.

Table 2: Example of Real Fast Charge Current at Different ISET and USBM Settings

| Icc   | USBM =<br>High   | USBM =<br>Float               | USBM =<br>Low    |

|-------|------------------|-------------------------------|------------------|

| 80mA  | 80mA<br>typical  | 80mA<br>typical/<br>100mA max | 80mA<br>typical  |

| 300mA | 300mA<br>typical | 100mA max                     | 300mA<br>typical |

| 600mA | 500mA<br>max     | 100mA max                     | 600mA<br>typical |

#### **Over-Current Protection (OCP)**

If the charge current is set too high erroneously, the MP2702 provides over-current protection (OCP). For example, if ISET is shorted to GND, the charge current is clamped at 1.25A, and the part latches off after a deglitch time of 1ms. This fault can be reset by re-plugging  $V_{IN}$ , pulling NTC to GND, or toggling the EN pin.

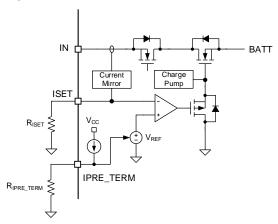

#### **Setting the Pre-Charge Current**

Connect a resistor between the IPRE\_TERM and GND pins to configure the proportion of  $I_{PRE}$  to  $I_{CC}$ .

Figure 4 shows the functional diagram for setting  $I_{\text{PRE}}$ .

Figure 4: Functional Diagram for Setting IPRE

The ratio of  $I_{PRE}$  to  $I_{CC}$  can be calculated with Equation (3):

$$I_{PRE} / I_{CC} = R_{IPRE \ TERM} / K_{PRE-CC}$$

(3)

Where  $K_{PRE-CC}$  is 112.36 $\Omega$ /%.

For example, to set the proportion of  $I_{PRE}$  /  $I_{CC}$  to 10%, connect a 1.13k $\Omega$  resistor between the IPRE\_TERM pin and ground.

When IPRE\_TERM pin is floated,  $I_{PRE}$  is fixed at 20% of the  $I_{CC}$  setting.

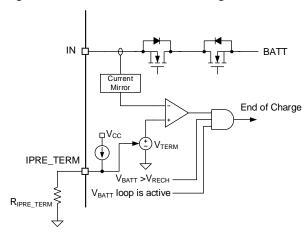

#### **Setting the Charge Termination Threshold**

If V<sub>BATT</sub> reaches the full voltage, the battery voltage loop is initiated and the charge current declines. Once the three conditions below are satisfied, charging terminates:

- 1. The  $V_{BATT}$  loop is active.

- 2.  $V_{BATT}$  exceeds the automatic recharge voltage threshold ( $V_{RECH}$ ).

- 3. The battery current (I<sub>BATT</sub>) is below I<sub>TERM</sub>.

$I_{\text{TERM}}$  is also proportional to  $I_{\text{CC}}$ . This threshold ( $I_{\text{TERM}}$  /  $I_{\text{CC}}$ ) can be configured via the resistor placed between IPRE\_TERM and ground, and can be calculated with Equation (4):

$$I_{\text{TERM}} / I_{\text{CC}} = R_{\text{IPRE TERM}} / K_{\text{TERM-CC}}$$

(4)

Figure 5 shows the functional diagram of I<sub>TERM</sub>.

Figure 5: Functional Diagram of ITERM

Where  $K_{TERM-CC}$  is 224.72 $\Omega$ /%.

For example, if  $R_{IPRE\_TERM}$  is 1.13k $\Omega$ , then the proportion of  $I_{TERM}$  to  $I_{CC}$  is 5%.

When IPRE\_TERM pin is floated,  $I_{TERM}$  is fixed at 10% of the set  $I_{CC}$ .

#### Battery Temperature Monitor via the Negative Thermal Coefficient (NTC) Thermistor

Thermistor is the generic name for thermally sensitive resistors. Negative temperature coefficient (NTC) thermistors are typically called thermistors. Depending on the manufacturing method and structure, there are many shapes and characteristics for various purposes.

The thermistor resistances, unless otherwise specified, are classified at a standard temperature of 25°C. The temperature resistance is solely a function of its absolute temperature.

Refer to the thermistor datasheet for the mathematic expression that relates the resistance and absolute temperature of a thermistor. The resistance at absolute temperature T1 (R1) can be calculated with Equation (5):

R1 = R2 x e<sup>$$\beta x \left(\frac{1}{T_1} - \frac{1}{T_2}\right)$$</sup> (5)

Where R2 is the resistance at absolute temperature T2, and  $\beta$  is a constant that depends on the material of the thermistor.

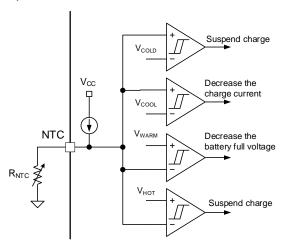

The MP2702 continuously monitors the battery's temperature by measuring the NTC pin voltage ( $V_{NTC}$ ), which is generated by a precise current flowing from the NTC pin through the NTC resistor ( $R_{NTC}$ ) to ground.

The MP2702 compares  $V_{\text{NTC}}$  to an internal threshold to determine the fault type that occurs and takes different actions accordingly. The current from the NTC pin is only active when  $V_{\text{IN}}$  is present.

Figure 6 shows the functional diagram of the NTC protection circuit.

Figure 6: Functional Diagram of NTC Protection Circuit

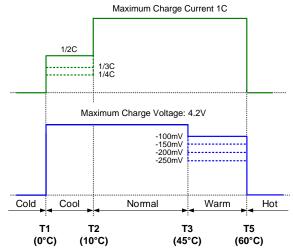

To satisfy the JEITA requirements, the MP2702 provides four temperature thresholds: cold (0°C by default), cool (10°C by default), warm (45°C by default), and hot (60°C by default). For a given NTC thermistor, these temperatures

correspond to  $V_{COLD}$ ,  $V_{COOL}$ ,  $V_{WARM}$ , and  $V_{HOT}$ , respectively. If  $V_{NTC}$  is below  $V_{HOT}$ , or  $V_{NTC}$  exceeds  $V_{COLD}$ , then charging and the timers are suspended. If  $V_{HOT} < V_{NTC} < V_{WARM}$ , or if  $V_{COOL} < V_{NTC} < V_{COLD}$ , then the charging behavior is configured via the OTP. The preset thresholds are defined based on a thermistor where  $\beta = 3435 K$ . Figure 7 shows the NTC JEITA profile.

Figure 7: NTC JEITA Profile

#### **EN Pin Control**

The MP2702 provides a dedicated EN pin to disable the entire chip completely. In this situation, the quiescent current (I<sub>Q</sub>) at the IN and BATT pins is minimized. When the chip is disabled by the EN pin, both the ACOK and CHG pins enter a high-impedance (Hi-Z) state.

#### **Charge Enable Control**

In addition to EN pin control, charging can be disabled by pulling the NTC pin to GND. This allows the ACOK pin to remain low, provided a normal input is available. To enable charging, the five conditions below must be met:

- 1. Pull the EN pin to ground or leave the pin floating to enable the chip.

- The NTC pin is not pulled to GND.

- 3. There are no NTC faults that can suspend charging.

- 4. There is no timer fault present.

- 5. There is no thermal fault present.

#### Floated NTC Mode

When the NTC pin is floated,  $V_{\rm NTC}$  is 3.6V. Since this exceeds the 2.5V charge termination disable threshold, the charge termination and safety timer are disabled.

To avoid overlap between the termination disable threshold and the cold temperature threshold, an internal loop can decrease the NTC bias current when  $V_{\text{NTC}}$  exceeds 2V. This prevents a cold thermistor from setting  $V_{\text{NTC}}$  above 2.5V.

#### Input Over-Voltage Protection (OVP)

The MP2702 provides input over-voltage protection (OVP). When  $V_{IN}$  rises to the input OVP threshold ( $V_{IN\_OVP}$ ), the MP2702 stops charging. Once  $V_{IN}$  drops back to its normal range, the device starts charging automatically.

$V_{\text{IN\_OVP}}$  is set to 6V for 1-cell applications and 14.4V for 2-cell applications.

#### **Battery Over-Voltage Protection (OVP)**

If  $V_{BATT}$  exceeds the battery OVP threshold  $(V_{BATT\_OVP})$ , charging stops. If  $V_{BATT}$  is below the

V<sub>BATT\_OVP</sub> falling threshold, the battery state transitions from battery OVP to charge termination.

#### Safety Charge Timer

The MP2702 provides a backup charge timer to ensure charge safety. When any new charge cycle starts, if the charging stays in trickle charge and pre-charge for 1 hour, or the entire charge process lasts for 10 hours (configurable via the OTP), charging automatically stops and the fault is reported. Once charging transitions from fast charge to pre-charge, the pre-charge timer resets.

After the safety timer expires, it can be reset by one of the actions below:

- Pull the EN pin high

- Re-plug V<sub>IN</sub>

- Pull the NTC pin to GND

#### **Operation Indication**

The MP2702 has two open-drain indicators to report the  $V_{IN}$  and charging status. Table 3 shows the ACOK pin indication.

**Table 3: ACOK Indication**

| V <sub>IN</sub> Status                                                                                  | ACOK |

|---------------------------------------------------------------------------------------------------------|------|

| V <sub>IN</sub> UVLO                                                                                    | Hi-Z |

| V <sub>IN</sub> OVP                                                                                     | Hi-Z |

| $V_{IN} < V_{BATT} + V_{HDRM}$                                                                          | Hi-Z |

| Normal input ( $V_{IN} > V_{BATT} + V_{HDRM}$ , and $V_{IN\_UVLO} < V_{IN} < V_{IN\_OVP}$ ), $EN = low$ | Low  |

| <br>EN = high                                                                                           | Hi-Z |

For CHG indication, the CHG pin is set low when charging is in process. After charge termination, the CHG pin enters a Hi-Z state. When charging is disabled by the NTC pin, the CHG pin also enters a Hi-Z state. In addition, the CHG pin can indicate fault events including NTC faults, timer faults, and charge OCP.

After the input power on or the charge being enabled, there is a 600ms deglitch time for the CHG indicator, which remains in a Hi-Z state during this blanking time.

Table 4 on page 20 shows the CHG pin indication.

Table 4: CHG Indication

| Charging Status                          | CHG            |

|------------------------------------------|----------------|

| Invalid input                            | Hi-Z           |

| EN= high                                 | Hi-Z           |

| Charge disabled by pulling NTC to ground | Hi-Z           |

| Charge termination                       | Hi-Z           |

| Charge in process                        | Low            |

| NTC fault, timer fault, charge OCP       | Blinking (1Hz) |

#### Thermal Regulation and Thermal Shutdown

During the battery charging process, the MP2702 continuously monitors the internal junction temperature  $(T_J)$  to avoid overheating the chip. If the internal temperature reaches the thermal regulation threshold  $(T_{J\_REG})$ , the MP2702 starts to reduce the charge current to prevent higher power dissipation.

If  $T_J$  reaches the thermal shutdown threshold  $(T_{J\_SHDN})$ , the MP2702 stops

charging immediately. Once  $T_J$  drops below the  $T_{J\_SHDN}$  falling threshold, the device resumes normal operation.

#### One-Time Programmable (OTP) Memory

The MP2702 provides OTP memory to configure the default value of several parameters. See the One-Time Programmable (OTP) Memory Map section on page 21 for the configurable parameters. Contact MPS to obtain a custom OTP setting.

# ONE-TIME PROGRAMMABLE (OTP) MEMORY MAP

### **REG00h: Battery Voltage Threshold Setting**

This register sets the battery cells' information and battery regulation voltage for each cell.

| Bits | Bit Name  | Default   | Description                                                                                                   |

|------|-----------|-----------|---------------------------------------------------------------------------------------------------------------|

|      | CELLS     | 1'b0      | Selects the battery cell.                                                                                     |

| 7    |           |           | 0: 1 cell (default) 1: 2 cells                                                                                |

| 6    | RESERVED  | 1'b0      | Reserved.                                                                                                     |

|      |           |           | Sets the battery regulation voltage.                                                                          |

| 5:0  | VBATT_REG | 6'b100100 | Range: 2.4V/cell (000000) to 4.5V/cell (101010) Offset: 2.4V/cell Step: 50mV/cell Default: 4.2V/cell (100100) |

#### **REG01h: Timer and Thermal Setting**

This register sets the safety charge timer and internal junction temperature (T<sub>J</sub>) regulation threshold.

| Bits | Bit Name | Default | Description                                                                                                                                       |

|------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | TMR_PRE  | 1'b1    | Sets the safety timer for trickle charge and pre-charge.  0: Disabled  1: 1 hour (default)                                                        |

| 6    | TMR_EN   | 1'b1    | Sets the safety timer enable control.  0: Disabled  1: Enabled (default)                                                                          |

| 5:3  | TMR_SET  | 3'b010  | Sets the safety timer for entire charge process.  Range: 2 hours (000) to 30 hours (111)  Offset: 2 hours  Step: 4 hours  Default: 10 hours (010) |

| 2    | RESERVED | 1'b0    | Reserved.                                                                                                                                         |

| 1    | TJ_REG   | 1'b1    | Sets the T <sub>J</sub> regulation loop. 0: 100°C 1: 120°C                                                                                        |

| 0    | RESERVED | 1'b0    | Reserved.                                                                                                                                         |

## **REG02h: Input Voltage Limit Setting**

This register sets the input voltage  $(V_{IN})$  limit loop threshold. If  $V_{IN}$  drops below this threshold, charge current decreases to prevent  $V_{IN}$  from dropping further.

| Bits | Bit Name | Default | Description                                                                                          |

|------|----------|---------|------------------------------------------------------------------------------------------------------|

| 7:6  | RESERVED | 2'b00   | Reserved.                                                                                            |

| 5:4  | VIN_LIM  | 2'b10   | Sets the V <sub>IN</sub> limit.  00: Reserved 01: 4.375V/cell 10: 4.5V/cell (default) 11: 4.75V/cell |

| 3:0  | RESERVED | 4'b0000 | Reserved.                                                                                            |

## **REG03h: JEITA Temperature Threshold Setting**

This register sets the JEITA hot, warm, cool, and cold temperature thresholds.

| Bits | Bit Name | Default | Description                                                                                                          |

|------|----------|---------|----------------------------------------------------------------------------------------------------------------------|

| 7:6  | VHOT     | 2'b10   | Sets the hot falling threshold.  00: 0.208V (50°C)  01: 0.176V (55°C)  10: 0.151V (60°C, default)  11: 0.129V (65°C) |

| 5:4  | VWARM    | 2'b01   | Sets the warm falling threshold.  00: 0.291V (40°C) 01: 0.245V (45°C, default) 10: 0.205V (50°C) 11: 0.176V (55°C)   |

| 3:2  | VCOOL    | 2'b10   | Sets the cool rising threshold.  00: 1.377V (0°C) 01: 1.111V (5°C) 10: 0.902V (10°C, default) 11: 0.737V (15°C)      |

| 1:0  | VCOLD    | 2'b01   | Sets the cold rising threshold.  00: 1.732V (-5°C)  01: 1.377V (0°C, default)  10: 1.111V (5°C)  11: 0.902V (10°C)   |

# **REG04h: JEITA Protection Setting**

This register sets the charge behavior during the JEITA warm and cool temperature windows.

| Bits | Bit Name   | Default | Description                                                                                                                                                                                                                                      |  |  |

|------|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      |            |         | Sets the charge action when the NTC is warm.                                                                                                                                                                                                     |  |  |

| 7:6  | WARM_ACT   | 2'b01   | 00: No action. Charging stops when the NTC is hot 01: Reduce V <sub>BATT_REG</sub> when the NTC is warm (default) 10: Reduce I <sub>CC</sub> when the NTC is warm 11: Reduce both V <sub>BATT_REG</sub> and I <sub>CC</sub> when the NTC is warm |  |  |

|      |            |         | Sets the charge action when the NTC is cool.                                                                                                                                                                                                     |  |  |

| 5:4  | COOL_ACT   | 2'b10   | 00: No action. Charging stops when NTC is cold 01: Reduce V <sub>BATT_REG</sub> when the NTC is cool 10: Reduce I <sub>CC</sub> when the NTC is cool (default) 11: Reduce both V <sub>BATT_REG</sub> and I <sub>CC</sub> when the NTC is cool    |  |  |

| 3:2  | JEITA_VSET | 2'b00   | 00: VBATT_REG - 100mV/cell (default) 01: VBATT_REG - 150mV/cell 10: VBATT_REG - 200mV/cell 11: VBATT_REG - 250mV/cell                                                                                                                            |  |  |

| 1:0  | JEITA_ISET | 2'b00   | 00: 50% of lcc (default) 01: 33% of lcc 10: 25% of lcc 11: 0% of lcc (disable charge)                                                                                                                                                            |  |  |

© 2023 MPS. All Rights Reserved.

# **REG05h: Pre-Charge Threshold Setting**

This register sets the pre-charge threshold.

| Bits | Bit Name  | Default   | Description                                                                                          |

|------|-----------|-----------|------------------------------------------------------------------------------------------------------|

| 7:2  | RESERVED  | 6'b000000 | Reserved.                                                                                            |

| 1:0  | VBATT_PRE | 2'b01     | Sets the pre-charge threshold.  00: 2.5V/cell  01: 2.8V/cell (default)  10: 3.0V/cell  11: 3.2V/cell |

## **APPLICATION INFORMATION**

#### **Setting the Fast Charge Current**

A resistor connected between the ISET and GND pins sets  $I_{CC}$ . The relationship between  $I_{CC}$  and  $R_{ISET}$  can be calculated with Equation (6):

$$I_{CC} = \frac{V_{REF}/k}{R_{ISET}}$$

(6)

Where  $V_{REF}$  is 1.2V, and k is 2.18 x 10<sup>-3</sup>.

For example,  $R_{\text{ISET}}$  must be set to 550 $\Omega$  to set  $I_{\text{CC}}$  to 1A.

# Setting the Pre-Charge Current and Termination Current

The pre-charge current is set as percentage of  $I_{CC}$  by connecting a resistor between the IPRE\_TERM and GND pins.

The ratio of  $I_{PRE}$  to  $I_{CC}$  can be calculated with Equation (7):

$$I_{PRE} / I_{CC} = R_{IPRE \ TERM} / K_{PRE-CC}$$

(7)

Where  $K_{PRE-CC}$  is 112.36 $\Omega$ /%.

For example, to set  $I_{PRE}$  /  $I_{CC}$  to 10%, connect a 1.13k $\!\Omega$  resistor between the IPRE\_TERM and GND pins.

When IPRE\_TERM pin is floated,  $I_{PRE}$  is fixed at 20% of the set  $I_{CC}$ .

I<sub>TERM</sub> is fixed as 50% of I<sub>PRE</sub>.

#### Setting the Battery Cell

The MP2702 supports 1-cell and 2-cell batteries, where the battery cell is configured via the OTP.

For 2-cell applications, the battery hot insertion or short is not allowed when  $V_{\text{IN}}$  is present, and charge is enabled.

#### **Selecting the Input Capacitor**

An input capacitor ( $C_{\text{IN}}$ ) is typically required for stable operation. In the MP2702, a minimum 1µF capacitor must be connected between the IN and GND pins to achieve stable operation across a full load current range. The capacitor's voltage rating must exceed the normal  $V_{\text{IN}}$  level. A low-ESR ceramic capacitor (X5R or X7R) is recommended.

#### Selecting the BATT to GND Capacitor

The capacitor connected between BATT and GND is also required for the MP2702. A minimum 1µF ceramic capacitor (X5R or X7R) is suitable for most applications.

#### Selecting the NTC Resistor

The MP2702 supports configurable JEITA that is based on a precise 50µA current source flowing through the external NTC thermistor. To use this function, connect a 10k $\Omega$  NTC thermistor with  $\beta$  = 3435K between the NTC and GND pins.

The JEITA threshold can be configured via the OTP.

If NTC is not used, connect a fixed  $10k\Omega$  resistor between the NTC and GND pins.

#### **PCB Layout Guidelines**

Place the external capacitors as close to the IC as possible to ensure the smallest input and output inductances and ground impedance.

# TYPICAL APPLICATION CIRCUIT

**Figure 8: Typical Application Circuit**

Table 5 shows the key bill of materials for Figure 8.

Table 5: Key Bill of Material for Figure 8

| Qty | Ref | Value | Description                        | Package | Manufacturer |

|-----|-----|-------|------------------------------------|---------|--------------|

| 1   | C1  | 2.2µF | Ceramic capacitor, 25V, X5R or X7R | 0603    | Any          |

| 1   | C2  | 2.2µF | Ceramic capacitor, 16V, X5R or X7R | 0603    | Any          |

| 1   | R⊤  | 10kΩ  | β = 3435K                          | Any     | Any          |

© 2023 MPS. All Rights Reserved.

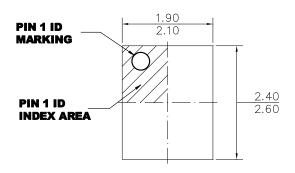

# **PACKAGE INFORMATION**

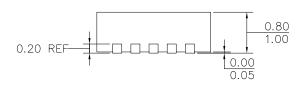

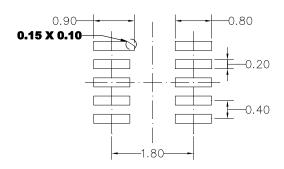

# QFN-10 (2mmx2.5mm)

**TOP VIEW**

**BOTTOM VIEW**

#### **SIDE VIEW**

**RECOMMENDED LAND PATTERN**

#### **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

- 3) JEDEC REFERENCE IS MO-220.

- 4) DRAWING IS NOT TO SCALE.

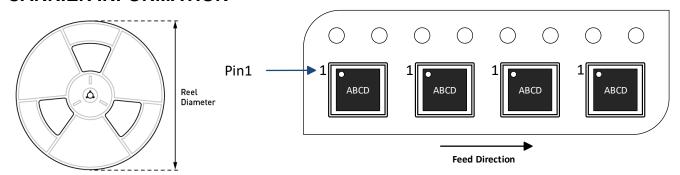

# **CARRIER INFORMATION**

| Part Number          | Package               | Quantity/ | Quantity/ | Quantity/ | Reel     | Carrier    | Carrier    |

|----------------------|-----------------------|-----------|-----------|-----------|----------|------------|------------|

|                      | Description           | Reel      | Tube      | Tray      | Diameter | Tape Width | Tape Pitch |

| MP2702GRP-<br>xxxx-Z | QFN-10<br>(2mmx2.5mm) | 5000      | N/A       | N/A       | 13in     | 12mm       | 8mm        |

# **REVISION HISTORY**

| Revision # | Revision Date | Description     | Pages Updated |

|------------|---------------|-----------------|---------------|

| 1.0        | 9/15/2023     | Initial Release | -             |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.