# MP5990

$\begin{array}{l} 16V,\,50A,\,1m\Omega\;R_{\text{DS(ON)}},\\ \text{Fully Integrated Hot-Swap Solution}\\ \text{with PMBus Interface} \end{array}$

# DESCRIPTION

The MP5990 is a fully integrated, PMBus compatible, compact hot-swap protection device. It contains a hot-swap controller and a high-side power MOSFET (HS-FET), which allow it to operate as a standalone device. The MP5990 can also operate as a hot-swap controller in parallel with the multi-phase MP5991. The device can achieve up to 50A of continuous output current ( $I_{OUT}$ ) per device at room temperature, and up to 60A of continuous  $I_{OUT}$  with airflow.

The device limits the backplane voltage drop by limiting the inrush current to the load while a circuit card is inserted into a live backplane power source. The MP5990 limits the internal MOSFET current ( $I_{FET}$ ) by controlling the gate voltage ( $V_{GATE}$ ) via the current limit ( $I_{LIMIT}$ ) reference input and soft-start ramp.

The MP5990 provides many features to simplify system design, such as an integrated current mirror to monitor  $I_{OUT}$  and integrated on-die temperature-sensing. This eliminates the need for an external current-sense power resistor, power MOSFET, and temperature-sense device.

The MP5990 provides rich fault protections, such as input voltage ( $V_{IN}$ ) over-voltage protection (OVP),  $I_{OUT}$  over-current protection (OCP), short-circuit protection (SCP), and over-temperature protection (OTP). The MP5990 detects power MOSFET gate, source, and drain short conditions. The fault status can be indicated with the fault report output (GOK). The MP5990 also provides V<sub>IN</sub> under-voltage warning (UVW), output over-current warning (D\_OC) and power good (PG) indication.

The PMBus interface provides  $V_{IN}$ , input current  $(I_{IN})$ , input energy  $(E_{IN})$ , output voltage  $(V_{OUT})$ ,  $I_{OUT}$ , input power  $(P_{IN})$ , and output power  $(P_{OUT})$  telemetry. The MP5990 monitors and reports fault statuses through the PMBus interface.

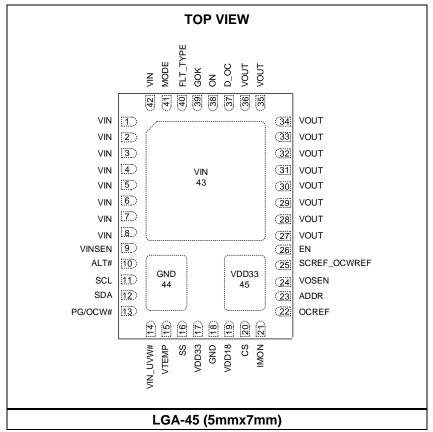

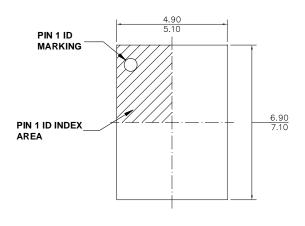

The MP5990 is available in an LGA-45 (5mmx7mm) package.

# FEATURES

- 4V to 16V Operating Input Voltage (V<sub>IN</sub>) Range

- Maximum 50A of Output Current (IOUT)

- Supports 60A of  $I_{\text{OUT}}$  with Air Flow

- 1mΩ Integrated Power MOSFET

- PMBus/l<sup>2</sup>C 1.3 Compatible

- ±1% IMON Reporting Accuracy

- Built-In MOSFET Driver

- Integrated Current-Sense with Sense Output

- Configurable Over-Current Limit

- Configurable Short-Circuit Current Limit

- Built-In Insertion Delay

- Configurable Soft Start (SS)

- Built-In Fuse Health Reporting

- Fault Signal Output (GOK)

- Power Good Indication (PG)

- V<sub>IN</sub> Under-Voltage Warning (UVW)

- Fault Type Indication (FLT\_TYPE)

- Faults Auto-Record to the NVM

- V<sub>IN</sub> OVP, SCP, OCP, and OTP with Options for No Action, Latch, Retry, or Hiccup Mode

- Intelli-Fuse Junction Temperature Monitoring

- Intelli-Fuse Controller

- Built-in NVM to Store Custom Configurations

- High Precision E<sub>IN</sub>, P<sub>IN</sub>, P<sub>OUT</sub>, and I<sub>OUT</sub> Reporting

- Configurable TON\_DELAY and TOFF\_DELAY

- NVM Write Protection

- Available in an LGA-45 (5mmx7mm) Package

# APPLICATIONS

- Hot Swaps

- PC Cards

- Disk Drives

- Servers

- 5G Telecom

- Networking

- Laptops

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

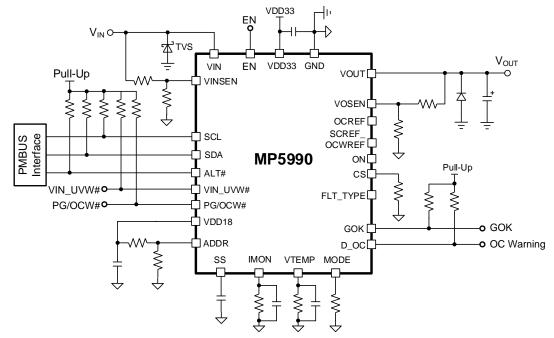

# TYPICAL APPLICATION

Figure 1: MP5990 Standalone Application Circuit

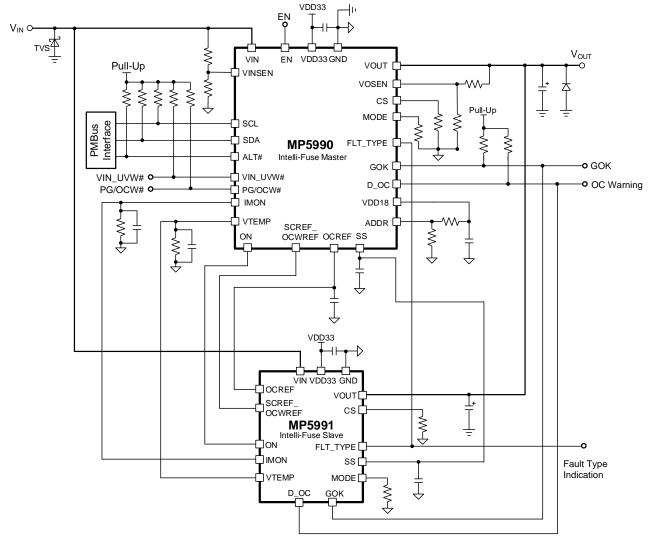

# **TYPICAL APPLICATION** (continued)

Figure 2: MP5990 (Master) + 1-Phase MP5991 (Slave) – Parallel Operation

#### **ORDERING INFORMATION**

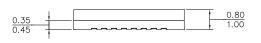

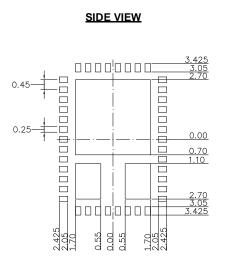

| Part Number*     | Package          | Top Marking | MSL Rating |

|------------------|------------------|-------------|------------|

| MP5990GMA-xxxx** | LGA-45 (5mmx7mm) | See Below   | 3          |

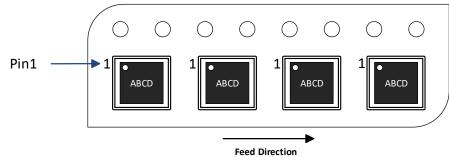

\* For Tape & Reel, add suffix -Z (e.g. MP5990GMA-xxxx-Z).

\*\* "xxxx" is the configuration code identifier for the register settings stored in the NVM. Each "x" can be a hexadecimal value between 0 & F. Contact an MPS FAE to create this unique number. "-0000" is the universal configuration code with default values.

# **TOP MARKING**

# MPSYYWW MP5990 LLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP5990: Part number LLLLLLL: Lot number

# **PIN FUNCTIONS**

| Pin #                                | Name     | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4,<br>5, 6, 7, 8,<br>42, 43 | VIN      | A [I]   | System input power supply. The VIN pin is connected to the drain of the integrated power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                |

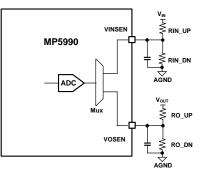

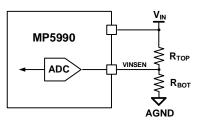

| 9                                    | VINSEN   | A [I]   | <b>Input voltage (VIN) sensing.</b> The VINSEN pin reads back $V_{IN}$ through the internal analog-to-digital converter (ADC). Connect VINSEN to the VIN rail via a resistor divider.                                                                                                                                                                                                                                                                                           |

| 10                                   | ALT#     | D [O]   | PMBus alert signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11                                   | SCL      | D [I]   | PMBus clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12                                   | SDA      | D [I/O] | PMBus data signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13                                   | PG/OCW#  | D [O]   | <b>Multi-function pin.</b> The PG/OCW# pin can be configured for power good (PG) or over-current warning (OCW) indication via register C7h, bit[13]. When this pin is set to PG, this pin is the open-drain PG indicator. If the SS pin's voltage exceeds 340mV and $V_{OUT}$ exceeds the PG setting threshold, PG asserts high. When this pin is set to OCW#, it acts as an open-drain OCW indicator. If the sensed $I_{OUT}$ exceeds the OCW threshold, this pin asserts low. |

| 14                                   | VIN_UVW# | D [O]   | <b>Input under-voltage warning (UVW) open-drain indicator.</b> If V <sub>IN</sub> drops below its configured UVW threshold, the VIN_UVW# pin asserts low.                                                                                                                                                                                                                                                                                                                       |

| 15                                   | VTEMP    | A [I]   | <b>Junction temperature (T<sub>J</sub>) sense.</b> Connect all the VTEMP pins of the e-fuse slaves to the MP5990's VTEMP pin. Place a minimum 10k $\Omega$ resistor and a maximum 1nF capacitor in parallel from VTEMP to AGND. The MP5990 senses the voltage on the VTEMP pin and reports the maximum T <sub>J</sub> of all Intelli-Fuse phases.                                                                                                                               |

| 16                                   | SS       | A [O]   | <b>Soft-start time (t</b> <sub>SS</sub> ) <b>setting.</b> $t_{SS}$ is set by an external capacitor connected to the SS pin. The internal circuitry controls the V <sub>OUT</sub> slew rate during start-up.                                                                                                                                                                                                                                                                     |

| 17, 45                               | VDD33    | Power   | <b>Internal 3.3V LDO output.</b> Place a $1\mu$ F decoupling capacitor close to the VDD33 and GND pins.                                                                                                                                                                                                                                                                                                                                                                         |

| 18, 44                               | GND      | Α       | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 19                                   | VDD18    | Power   | <b>1.8V LDO output.</b> The VDD18 pin provides the power supply for the internal digital circuit. Connect a $1\mu$ F bypass capacitor from VDD18 to AGND.                                                                                                                                                                                                                                                                                                                       |

| 20                                   | CS       | A [O]   | <b>Current-sense output.</b> The CS pin's voltage (V <sub>CS</sub> ) is compared to V <sub>OCREF</sub> to determine the Intelli-Fuse over-current (OC) limit. V <sub>CS</sub> can assert the D_OC pin when it is compared to the OCWREF pin's voltage (V <sub>OCWREF</sub> ). Connect a resistor from the CS pin to GND to generate V <sub>CS</sub> .                                                                                                                           |

| 21                                   | IMON     | A [I/O] | <b>Current monitor output.</b> The IMON pin's output current ( $I_{OUT}$ ) is proportional to the current flowing through the device. Place a resistor and a 2.2nF to 100nF capacitor in parallel from IMON to AGND. The MP5990 senses the voltage on IMON and converts the voltage into the total $I_{OUT}$ report.                                                                                                                                                            |

| 22                                   | OCREF    | A [O]   | <b>OC limit reference.</b> V <sub>OCREF</sub> is the digital-to-analog converter (DAC) output of the internal OC limit reference. The MP5990 compares V <sub>OCREF</sub> and V <sub>CS</sub> to determine the Intelli-Fuse OC limit.                                                                                                                                                                                                                                            |

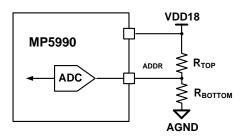

| 23                                   | ADDR     | A [I]   | <b>PMBus address 4 LSB setting.</b> Connect a resistor divider from the VDD18 to AGND pin to set the 4LSB of the PMBus address based on the ADDR pin's voltage.                                                                                                                                                                                                                                                                                                                 |

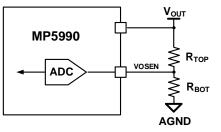

| 24                                   | VOSEN    | A [I]   | <b>Output voltage (Vout) sensing.</b> The VOSEN pin reads back Vout through the internal ADC. Connect VOSEN to the rail output via a resistor divider.                                                                                                                                                                                                                                                                                                                          |

# PIN FUNCTIONS (continued)

5

ΠР

| Pin #                                           | Name             | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25                                              | SCREF_<br>OCWREF | A [O]   | Short-circuit current limit reference and over-current warning (OCW) reference. The SCREF_OCWREF pin is a DAC output that sets the short-circuit current limit and OCW current limit. If $V_{SS} > 340$ mV and ON is high, the pin transits from SCREF to OCWREF.                                                                                                                                                                                                                                                                                                                                    |

| 26                                              | EN               | D [I]   | <b>Enable control.</b> The EN pin is a digital input that turns the MP5990 on and off. Drive EN high to turn on the MP5990; drive it low to turn off the device.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27, 28, 29,<br>30, 31, 32,<br>33, 34, 35,<br>36 | VOUT             | A [O]   | <b>Output voltage.</b> The VOUT pin is connected to the source of the integrated power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 37                                              | D_OC             | D [O]   | <b>OC indication digital output.</b> The D_OC pin is an open-drain output. If $V_{CS}$ exceeds $V_{OCWREF}$ , D_OC asserts low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 38                                              | ON               | D [O]   | <b>Power MOSFET on/off control.</b> Pull the ON pin above 2V to turn on the e-<br>fuse power MOSFET; pull ON below 0.6V to turn off the e-fuse power<br>MOSFET. The e-fuse power MOSFET cannot be turned off by pulling ON low<br>externally.                                                                                                                                                                                                                                                                                                                                                        |

| 39                                              | GOK              | D [I/O] | Intelli-Fuse open-drain fault reporting output, and multi-phase slave fault detection input. The GOK pin is an open-drain output. If a fault occurs, GOK asserts low and latches. The faults that can trigger GOK include input overvoltage (OV) faults, output OC faults, short-circuit faults, over-temperature (OT) faults, and FET health faults. When the MP5990 operates in parallel with the MP5991, the GOK pin works as the input for the slave phases' (MP5991) fault detections. If GOK is pulled low by the slaves, then the master (MP5990) pulls the ON pin low to disable the output. |

| 40                                              | FLT_TYPE         | A [I]   | <b>Intelli-Fuse fault type indication output.</b> The FLT_TYPE pin reports the fault type. During multi-phase operation, connect the FLT_TYPE pins together to indicate the most serious fault in the system.                                                                                                                                                                                                                                                                                                                                                                                        |

| 41                                              | MODE             | A [I]   | <b>Mode selection.</b> Connect a $120k\Omega$ (±10%) resistor from the MODE pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>IN</sub> (DC)0.3V to +20V                         |

|----------------------------------------------------------|

| V <sub>IN</sub> (1µs)                                    |

| V <sub>IN</sub> (25ns)                                   |

| V <sub>OUT</sub> 0.3V to +20V                            |

| VDD330.3V to +4V                                         |

| VDD180.3V to +2.2V                                       |

| IMON, VINSEN, ADDR, FLT_TYPE, VTEMP,                     |

| VOSEN0.3V to +2.2V                                       |

| All other pins0.3V to +4V                                |

| Continuous power dissipation $(T_A = 25^{\circ}C)^{(2)}$ |

| 5.46W                                                    |

| Junction temperature150°C                                |

| Lead temperature                                         |

| Storage temperature65°C to +150°C                        |

#### ESD Ratings (3)

Human body model (HBM) .....Class 1C Charged device model (CDM).....Class C2B

#### **Recommended Operating Conditions** <sup>(4)</sup>

# Thermal Resistance (5) $\theta_{JA}$ $\theta_{JC}$

LGA-45 (5mmx7mm).....22.9....10.1...°C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Followed ANSI/ESDA/JEDEC JS-001 for HBM and ANSI/ESDA/JEDEC JS-002 for CDM.

- The device is not guaranteed to function outside of its operating conditions.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

#### $V_{IN}$ = 12V, EN = high, $R_{CS}$ = 2k $\Omega$ , $R_{IMON}$ = 2k $\Omega$ , $T_A$ = 25°C, unless otherwise noted.

| Parameters                                                                 | Symbol               | Condition                                                                | Min  | Тур          | Max  | Units |

|----------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------|------|--------------|------|-------|

| Supply Current                                                             |                      | · · · · · · · · · · · · · · · · · · ·                                    |      |              |      |       |

|                                                                            |                      | EN is low, low-power mode                                                |      | 1.2          | 2.5  | mA    |

|                                                                            |                      | EN is low, regular power mode                                            |      | 11           | 22.5 | mA    |

| Quiescent current                                                          | Iqin                 | Both EN and ON are high, no load                                         |      | 11.2         | 22.7 | mA    |

|                                                                            |                      | Fault latch off                                                          |      | 11           | 22.4 | mA    |

| VDD33 Regulator and Unde                                                   | r-Voltage Locko      | ut (UVLO)                                                                |      |              |      | 1     |

| VDD33 regulator output voltage                                             | VDD33                | IVDD33 = 0mA                                                             | 3.22 | 3.32         | 3.42 | V     |

| VDD33 regulator load                                                       |                      | I <sub>VDD33</sub> = 25mA                                                |      |              | 2    | %     |

| capability                                                                 | $\Delta$ VDD33       | IvDD33 = 40mA                                                            |      |              | 3.5  | %     |

| VDD33 UVLO rising threshold                                                | VDD33 <sub>VTH</sub> |                                                                          | 2.55 | 2.7          | 2.85 | V     |

| VDD33 UVLO falling threshold                                               | VDD33vtl             |                                                                          | 2.15 | 2.3          | 2.45 | V     |

| VDD33 UVLO hysteresis                                                      | VDD33 <sub>HYS</sub> |                                                                          |      | 400          |      | mV    |

| VDD18 Regulator                                                            |                      | 1                                                                        |      | L            | L    | I     |

| 1.8V regulator output voltage                                              |                      |                                                                          | 1.78 | 1.8          | 1.82 | V     |

| 1.8V regulator load<br>capability                                          | $\Delta$ VDD18       | Ivdd18 = 30mA                                                            |      |              | 2    | %     |

| VIN Under-Voltage Protectio                                                | n (UVP) and Ove      | er-Voltage Protection (OVP)                                              |      | 1            | 1    | 1     |

| V <sub>IN</sub> analog UVLO rising threshold                               | Vin_vthr_ana         | Disable digital V <sub>IN</sub> UVLO (C4h,                               | 3.05 | 3.2          | 3.35 | V     |

| V <sub>IN</sub> analog UVLO falling threshold                              | Vin_vthf_ana         | bit[7] = 0)                                                              | 2.55 | 2.7          | 2.95 | V     |

| V <sub>IN</sub> digital on/off threshold configurable range <sup>(6)</sup> | VIN_ON_OFF_DGTL      | Set by 35h, bits[6:0] and 36h, bits[6:0]                                 |      | 0 to<br>63.5 |      | V     |

| V <sub>IN</sub> analog OVP threshold                                       | VIN_OVP_ANA          | Set the digital OVP threshold to 20V via 55h, bits[6:0]                  | 17   | 18.5         | 20   | V     |

| V <sub>IN</sub> analog OVP hysteresis                                      | Vin_ovp_ana_hys      | Auto-retry mode, set the digital OVP threshold to 20V via 55h, bits[6:0] |      | 1.2          |      | V     |

| V <sub>IN</sub> digital OV configurable range <sup>(6)</sup>               | Vin_ovp_dgtl         | Set by 55h, bits[6:0]                                                    |      | 0 to<br>63.5 |      | V     |

| Enable (EN)                                                                |                      |                                                                          |      |              |      |       |

| EN rising threshold                                                        | Ven_on               |                                                                          |      | 1.2          |      | V     |

| EN falling threshold                                                       | Ven_off              |                                                                          |      | 0.83         |      | V     |

| EN high leakage                                                            | I <sub>IH(EN)</sub>  | EN = 3.3V                                                                |      | 3.6          |      | μA    |

| Enable delay                                                               | tdly_lp              | Low-power mode, EN high to<br>ON high, TON_DELAY = 0                     |      | 130          |      | μs    |

|                                                                            | tdly_rp              | Regular power mode, EN high<br>to ON high, TON_DELAY = 0                 |      | 0.5          | 10   | μs    |

| Power MOSFET                                                               |                      |                                                                          |      |              |      |       |

| On resistance                                                              | R <sub>DS(ON)</sub>  | $T_J = 25^{\circ}C, I_{FET} = 2A$                                        |      | 1            | 1.25 | mΩ    |

|                                                                            |                      | $T_J = 125^{\circ}C, I_{FET} = 2A^{(6)}$                                 |      | 1.35         | 1.7  |       |

| Off-state leakage current                                                  | OFF                  | V <sub>IN</sub> = 16V, power MOSFET off                                  |      |              | 1    | μA    |

# ELECTRICAL CHARACTERISTICS (continued)

#### $V_{IN} = 12V$ , EN = high, $R_{CS} = 2k\Omega$ , $R_{IMON} = 2k\Omega$ , $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                          | Symbol                | Condition                                                                           | Min   | Тур         | Max   | Units |

|-----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-------|-------------|-------|-------|

| ON                                                  | · · · · ·             |                                                                                     |       |             |       |       |

| ON output low voltage                               | Volon                 |                                                                                     |       |             | 0.6   | V     |

| ON output high voltage                              | Vohon                 |                                                                                     | 2     |             |       | V     |

| ON output at no power                               | Vonini                | VDD33 < UVLO threshold, EN = 0,<br>sink current = $100\mu$ A                        |       |             | 0.6   | V     |

| FET on insertion delay time                         | t <sub>DLY_ON</sub>   | V <sub>IN</sub> and VDD33 > UVLO threshold                                          | 0.8   | 1.3         | 1.8   | ms    |

| ON blanking time                                    | t <sub>onblank</sub>  | ON reset from fault status, high level trig mode                                    | 0.7   | 1           | 1.5   | ms    |

| Analog-to-Digital Converte                          | r (ADC)               |                                                                                     |       |             |       |       |

| Voltage range <sup>(6)</sup>                        | FSADC                 |                                                                                     |       | 0 to<br>1.6 |       | V     |

| Reference voltage                                   |                       |                                                                                     | -0.5% | 1.6         | +0.5% | V     |

| ADC resolution (6)                                  |                       |                                                                                     |       | 10          |       | bits  |

| DNL <sup>(6)</sup>                                  |                       |                                                                                     |       | 1           |       | LSB   |

| INL <sup>(6)</sup>                                  |                       |                                                                                     |       | 1           |       | LSB   |

| Sample rate (6)                                     |                       |                                                                                     |       | 780         |       | kHz   |

| Current Monitor Output (IN                          | ION)                  |                                                                                     |       |             |       |       |

| IMON sense gain                                     | ,<br>                 | louт > 4А                                                                           | 9.9   | 10          | 10.1  | µA/A  |

| IMON sense offset                                   |                       | louт > 4А                                                                           | -1    |             | +1    | μA    |

| Current-Sense (CS) Output                           | for Over-Cur          |                                                                                     |       |             |       |       |

| CS gain                                             | Ics / Iout            | louт > 4А                                                                           | 9.6   | 10          | 10.4  | µA/A  |

| CS gain offset                                      |                       | I <sub>OUT</sub> > 4A                                                               | -1    |             | +1    | μA    |

| Over-Current Limit Referer                          | nce (OCREF)           | 1                                                                                   |       |             |       |       |

|                                                     | ,                     | $V_{BE}$ at $V_{OUT}$ < 80% of $V_{IN}$ , $T_J$ = 25°C                              | 570   | 635         | 699   | mV    |

| OCREF internal max<br>current limit clamp           | Vocre <u>f_</u> clamp | $V_{BE}$ at $V_{OUT} < 80\%$ of $V_{IN}$ ,<br>T <sub>J</sub> = 125°C <sup>(6)</sup> | 370   | 440         | 570   | mV    |

|                                                     |                       | V <sub>OUT</sub> ≥ 80% of V <sub>IN</sub>                                           | 1.9   | 2           | 2.1   | V     |

| OCREF over-current (OC) regulation timer            | toc_reg               | $V_{OUT} \ge 90\%$ of $V_{IN}$ , $V_{OCREF} \ge 0.3V$                               |       | 220         |       | μs    |

| OCREF DAC operating range <sup>(6)</sup>            | FSdacocref            |                                                                                     |       | 0 to<br>1.8 |       | V     |

| DAC reference                                       | Vocrefref             |                                                                                     | 1.74  | 1.76        | 1.78  | V     |

| Decelution (6)                                      | Resolution            |                                                                                     |       | 6           |       | bit   |

| Resolution <sup>(6)</sup>                           | $\Delta$ dac_ocref    |                                                                                     |       | 28          |       | mV    |

| OCREF DAC buffer sink                               |                       | ISINK = 200µA, VOCREF = 0.31V                                                       |       | 6           |       | %     |

| ability                                             | $\Delta$ ocref_si     | Isink = 200µA , Vocref = 1.76V                                                      |       | 1           |       | %     |

| OCREF DAC buffer source                             |                       | ISOURCE = $200\mu A$ , Vocref = $0.31V$                                             |       | -4          |       | %     |

| ability                                             | $\Delta$ ocref_so     | Isource = 200µA, Vocref = 1.76V                                                     |       | -1          |       | %     |

| Short Circuit Current Limit                         | Reference (S          |                                                                                     |       |             |       |       |

|                                                     | <b>_</b>              | SC limit = 40A                                                                      |       | 0           | 0.16  | V     |

|                                                     |                       | SC limit = 60A                                                                      | 0.24  | 0.3         | 0.36  | V     |

| SCREF voltage range for                             | V <sub>SCLIMIT</sub>  | SC limit = 80A                                                                      | 0.48  | 0.6         | 0.72  | V     |

| short-circuit current limit                         |                       | SC limit = 120A                                                                     | 0.96  | 1.2         | 1.44  | V     |

|                                                     |                       | SC limit = 100A                                                                     | 1.68  |             |       | V     |

| Short-circuit current limit accuracy <sup>(6)</sup> | ILIMITSC              | V <sub>SCREF</sub> > 1.68V                                                          |       | 100         |       | А     |

# ELECTRICAL CHARACTERISTICS (continued)

#### $V_{IN}$ = 12V, EN = high, $R_{CS}$ = 2k $\Omega$ , $R_{IMON}$ = 2k $\Omega$ , $T_A$ = 25°C, unless otherwise noted.

| Parameters                                             | Symbol              | Condition                                                                                       | Min  | Тур         | Max  | Units           |

|--------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|------|-------------|------|-----------------|

| Short-circuit protection response time <sup>(6)</sup>  | tsc                 |                                                                                                 |      | 200         |      | ns              |

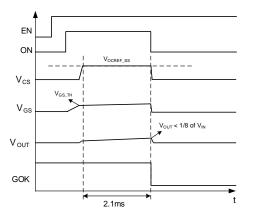

| Short-circuit start-up<br>protection timer             | tsc_timer           | $V_{OUT}$ < 1/8 of $V_{IN}$ , MOSFET current is regulated by $V_{BE}$                           |      | 2.1         | 3.2  | ms              |

| SCREF DAC voltage range (6)                            | FSDAC SCREF         |                                                                                                 |      | 0 to<br>1.8 |      | V               |

| SCREF DAC reference                                    | VSCREF REF          |                                                                                                 | 1.74 | 1.76        | 1.78 | V               |

| Becalution (6)                                         | Resolution          |                                                                                                 |      | 6           |      | bits            |

| Resolution <sup>(6)</sup>                              | $\Delta$ dac ocref  |                                                                                                 |      | 28          |      | mV              |

| SCREF DAC buffer sink                                  |                     | $I_{SINK} = 200 \mu A$ , $V_{SCREF} = 0.31 V$                                                   |      | 6           |      | %               |

| ability                                                | $\Delta$ SCREF_SI   | $I_{SINK} = 200 \mu A, V_{SCREF} = 1.76 V$                                                      |      | 1           |      | %               |

| SCREF DAC buffer source                                |                     | ISOURCE = $200\mu$ A, VSCREF = $0.31$ V                                                         |      | -2          |      | %               |

| ability                                                | $\Delta$ SCREF_SO   | ISOURCE = $200\mu A$ , VSCREF = $1.76V$                                                         |      | -1          |      | %               |

| Soft Start (SS)                                        |                     |                                                                                                 |      |             |      |                 |

| SS pull-up current                                     | lss                 | $V_{IN} = 12V, R_{SS} = 0.8M\Omega$                                                             | 13   | 15          | 17   | μA              |

| SS pull low voltage                                    | Vol_ss              | Sink current = 10mA                                                                             |      |             | 0.2  | V               |

| SS MOSFET off-state<br>leakage current                 | Ilkg_ss             | ON = 0, V <sub>SS</sub> = 3.3V                                                                  |      |             | 1    | μA              |

| SS internal comparator threshold                       | Vss th              | Transit from SCREF to<br>OCWREF                                                                 |      | 340         |      | mV              |

| <b>GOK Output and Comparator</b>                       | •                   |                                                                                                 |      |             |      |                 |

| Output low voltage                                     | Vol_gok             | Sink current = 10mA                                                                             |      |             | 0.3  | V               |

| GOK off-state leakage current                          | LKG_GOK             | V <sub>GOK</sub> = 3.3V                                                                         |      |             | 3    | μA              |

| GOK internal pull-up resistor                          | Rgok_int            |                                                                                                 |      | 370         |      | kΩ              |

| GOK comparator low threshold                           | V <sub>GOK_TH</sub> | Fault status                                                                                    | 1.05 | 1.16        | 1.3  | V               |

| GOK comparator hysteresis                              | Vgok hys            |                                                                                                 |      | 900         |      | mV              |

| GOK fault delay time                                   |                     |                                                                                                 |      | 10          | 15   | μs              |

| D_OC Output                                            |                     |                                                                                                 |      |             |      |                 |

| Output low voltage                                     | Vol_doc             | Sink current 10mA                                                                               |      |             | 0.3  | V               |

| D_OC bar off-state leakage current                     | ILKG_DOC            | V <sub>DOC</sub> = 3.3V                                                                         |      |             | 1    | μA              |

| D_OC high to low threshold                             | Vdoc_th             | $V_{OUT} \ge 90\%$ of $V_{IN}$ ,<br>$0.3V \le V_{OCWREF} \le 1.8V$ ,<br>$R_{MODE} = 120k\Omega$ | 95%  | 100%        | 105% | Vocwref         |

| OCW Output                                             |                     |                                                                                                 |      |             |      |                 |

| OCW low voltage                                        | Volgok              | Sink current = 10mA                                                                             |      |             | 0.3  | V               |

| OCW high leakage current                               | ILgok               | V <sub>OCW</sub> = 3.3V                                                                         |      | 1.5         | 2.3  | μA              |

| FET Short Detection                                    |                     |                                                                                                 |      |             |      |                 |

| FET drain-to-source short<br>analog entry threshold    | Vout_dsth           |                                                                                                 | 85%  | 90%         | 95%  | Vin             |

| FET drain-to-source short<br>analog recovery threshold | Vout_faulth         |                                                                                                 | 65%  | 70%         | 75%  | V <sub>IN</sub> |

| GS short protection delay time <sup>(6)</sup>          | tgs_s⊤              | V <sub>SS</sub> > VDD33 - 0.7                                                                   | 200  | 250         | 300  | ms              |

# ELECTRICAL CHARACTERISTICS (continued)

#### $V_{IN}$ = 12V, EN = high, $R_{CS}$ = 2k $\Omega$ , $R_{IMON}$ = 2k $\Omega$ , $T_A$ = 25°C, unless otherwise noted

| Parameters                                             | Symbol                         | Condition                                                              | Min   | Тур | Max   | Units |

|--------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|-------|-----|-------|-------|

| Fault Type Indication Outp                             | ut (FLT_TYPE)                  | Total 6 Types                                                          |       |     |       |       |

| FLT_TYPE voltage during SCP <sup>(6)</sup>             | VFLT_TYPESC                    | Short-circuit fault                                                    |       | 1.5 |       | V     |

| FLT_TYPE voltage during OCP                            | VFLT_TYPEOC                    | OC fault during normal operation and soft start                        | 1.16  | 1.2 | 1.24  | V     |

| FLT_TYPE voltage during<br>OTP and V <sub>IN</sub> OVP | VFLT_TYPEOT                    | Ove-temperature (OT) fault,<br>V <sub>IN</sub> over-voltage (OV) fault | 0.865 | 0.9 | 0.935 | V     |

| FLT_TYPE voltage during<br>FET GS and DS short         | VFLT_TYPEDSS                   | FET DS and GS short event                                              | 0.57  | 0.6 | 0.63  | V     |

| FLT_TYPE voltage during<br>GOK fault                   | V <sub>FLT_TYPEGSS</sub>       | GOK fault event                                                        | 0.275 | 0.3 | 0.325 | V     |

| FLT_TYPE voltage at other faults                       | VFLT_TYPEOTHER                 |                                                                        | 0.08  | 0.1 | 0.12  | V     |

| MODE                                                   |                                |                                                                        |       |     |       |       |

| MODE source current                                    | IMODE                          |                                                                        | 9     | 10  | 11    | μA    |

| MODE voltage setting<br>window                         | V <sub>MODE</sub>              | $R_{MODE} = 120 k\Omega$                                               | 0.96  | 1.2 | 1.44  | V     |

| VTEMP                                                  |                                |                                                                        |       |     |       |       |

| VTEMP sense gain <sup>(6)</sup>                        |                                |                                                                        |       | 8.7 |       | mV/°C |

| VTEMP sense output <sup>(6)</sup>                      |                                | $T_J = 25^{\circ}C$                                                    |       | 370 |       | mV    |

| Thermal Shutdown                                       |                                |                                                                        |       |     |       |       |

| OT threshold (6)                                       | $T_{J_OTP}$                    |                                                                        |       | 145 |       | °C    |

| <b>PMBus Timing Characteris</b>                        | tics (1MHz) <sup>(6) (7)</sup> | )                                                                      |       |     |       |       |

| Operating frequency range                              |                                |                                                                        | 10    |     | 1000  | kHz   |

| Bus free time                                          |                                | Between a stop and start condition                                     | 0.5   |     |       | μs    |

| Hold time                                              |                                |                                                                        | 0.26  |     |       | μs    |

| Repeated start condition<br>set-up time                |                                |                                                                        | 0.26  |     |       | μs    |

| Stop condition setup time                              |                                |                                                                        | 0.26  |     |       | μs    |

| Data hold time                                         |                                |                                                                        | 0     |     |       | ns    |

| Data set-up time                                       |                                |                                                                        | 50    |     |       | ns    |

| Clock low timeout                                      |                                |                                                                        | 25    |     | 35    | ms    |

| Clock low period                                       |                                |                                                                        | 0.5   |     |       | μs    |

| Clock high period                                      |                                |                                                                        | 0.26  |     | 50    | μs    |

| Clock/data falling time                                |                                |                                                                        |       |     | 120   | ns    |

| Clock/data rising time                                 |                                |                                                                        |       |     | 120   | ns    |

Note:

6) Guaranteed by design or characterization data. Not tested in production.

7) The device supports 100kHz, 400kHz, and 1MHz bus speeds. The PMBus timing parameters in this table are for operation at 1MHz. If the PMBus operating frequency is 100kHz or 400kHz, refer to the SMBus specifications for timing parameters.

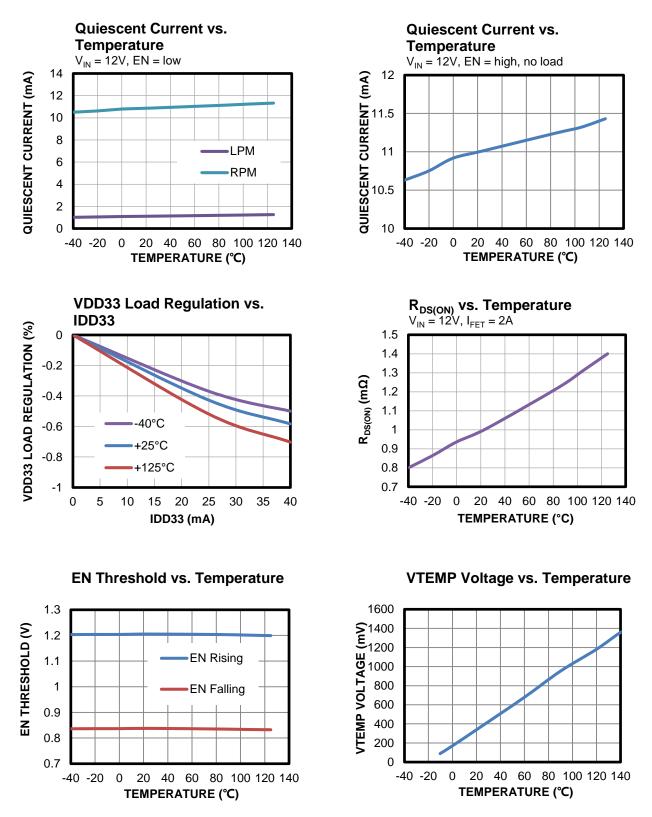

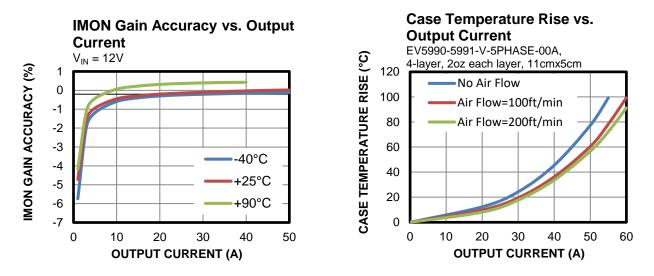

# **TYPICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $C_{OUT}$  = 330µF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $C_{OUT}$  = 330µF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted.

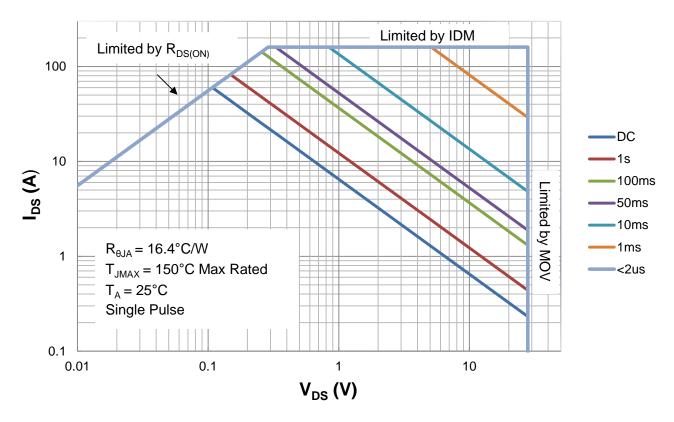

#### Safe Operation Area (SOA)

Tested on the EV5990-5991-V-5PHASE-00A, 4-layer (2oz per layer), 11cmx15cm

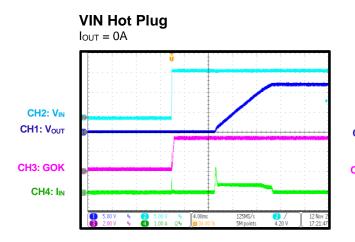

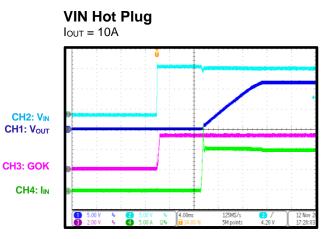

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN}$  = 12V,  $C_{OUT}$  = 330µF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted.

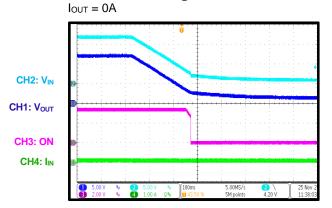

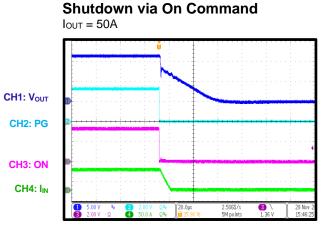

Shutdown through VIN

Shutdown through VIN IOUT = 50A

MP5990 Rev. 1.1

4/19/2024

3 \ 1.36 V

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $C_{OUT}$  = 330µF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted.

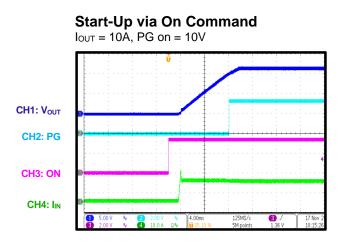

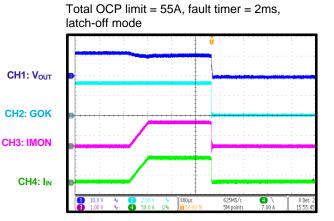

**Total OCP**

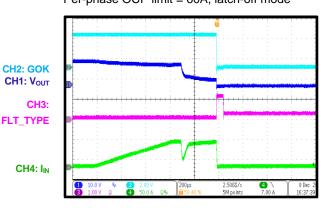

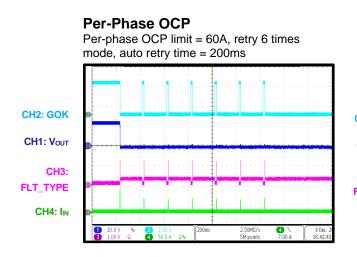

**Per-Phase OCP** Per-phase OCP limit = 60A, latch-off mode

#### MP5990 Rev. 1.1 4/19/2024

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $C_{OUT}$  = 330µF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted.

CH2: VIN CH1: Vour CH3: CS CH4: IN CH4: IN CH3: CS

#### VIN OVP in Latch-Off Mode

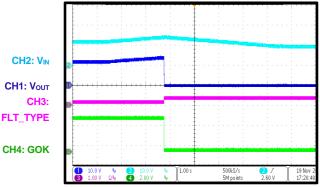

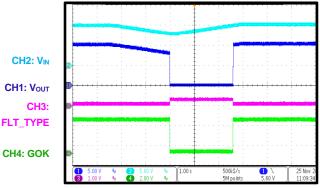

CH2: VIN CH1: GOK CH3: ON CH4: IIN OV rising = 14V, OV falling = 13V, apply 14V to VIN, then reduce  $V_{IN}$

# CH2: V<sub>IN</sub> CH2: V<sub>IN</sub> CH3:

VIN UVP UV rising =

UV rising = 10V, UV falling = 8V, reduce VIN, then increase  $V_{\text{IN}}$

FLT\_TYPE

CH4: GOK

2

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $C_{OUT}$  = 330µF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted.

28

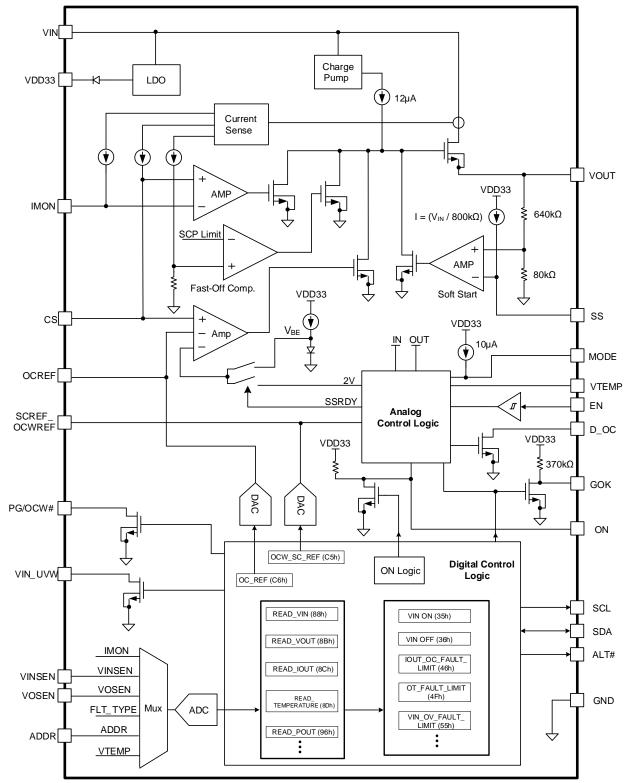

## FUNCTIONAL BLOCK DIAGRAM

Figure 3: Functional Block Diagram

# OPERATION

The MP5990 is a fully integrated, PMBus compatible, compact hot-swap protection device. It contains a hot-swap controller and a high-side power MOSFET (HS-FET), which allow it to operate as a standalone device. The MP5990 can also operate as a hot-swap controller that works in parallel with the multiphase MP5991. The device can achieve up to 50A of continuous output current ( $I_{OUT}$ ) per device at room temperature, and up to 60A of continuous  $I_{OUT}$  with airflow.

The device limits the backplane voltage drop by limiting the inrush current to the load while a circuit card is inserted into a live backplane power source. The MP5990 limits the internal MOSFET current ( $I_{FET}$ ) by controlling the gate voltage ( $V_{GATE}$ ) via the current limit ( $I_{LIMIT}$ ) reference input and soft-start ramp.

The MP5990 provides rich fault protections, such as input voltage  $(V_{IN})$  over-voltage protection (OVP),  $I_{OUT}$  over-current protection (OCP), short-circuit protection (SCP), and over-temperature protection (OTP). The MP5990 detects power MOSFET gate, source, and drain short conditions. The fault status can be indicated with fault report output (GOK). The MP5990 also provides  $V_{IN}$  under-voltage warning (UVW), output over-current warning (D\_OC) and power good (PG) indication.

#### Enable (EN) Control and Low-Power Mode

The EN pin controls the MP5990's on/off state. When  $V_{IN}$  exceeds its rising threshold, VDD33 is generated, regardless of the EN pin's status. The MP5990 provides regular power mode and low-power mode (LPM). In regular power mode, the PMBus interface, access to the non-volatile memory (NVM), and control circuitries are all live, even when EN is low. EN controls the output of the ON pin, which turns the MOSFET on and off. When EN is low, the quiescent current (I<sub>QIN</sub>) is about 11mA in regular power mode.

When LPM is enabled (ADVANCE\_CTRL (F1h), bit[12] = 1) and EN is low, most of the control circuitries are disabled to reduce the power consumption to 1.2mA. The PMBus interface and NVM are still accessible when the MP5990 is disabled. Connect EN to VDD33 for automatic start-up via VIN.

#### MOSFET On/Off Control (ON)

The ON pin is an output signal that turns the MOSFET on and off. In standalone operation, the MP5990 drives ON above 2V to turn on the power MOSFET. The MP5990 internally pulls ON below 0.6V to turn it off.

In multi-phase applications, the ON pins of the e-fuse slaves are connected to the MP5990's ON pin. Then the MP5990 works as a master to control the system's on/off sequence.

#### Soft Start (SS)

The MP5990 limits the inrush current with a controlled output voltage ( $V_{OUT}$ ) ramp-up slew rate. The SS capacitor ( $C_{SS}$ ) determines the soft-start time ( $t_{SS}$ ). When ON is pulled high and the insertion delay time ends, a constant current source proportional to  $V_{IN}$  charges  $C_{SS}$ .  $V_{OUT}$  rises at a similar slew rate to  $V_{SS}$ .  $C_{SS}$  can be calculated with Equation (1):

$$C_{\rm SS} = \frac{9 \times t_{\rm SS}}{R_{\rm SS}} \tag{1}$$

#### Where $R_{SS}$ is 0.8M $\Omega$ .

For example, a 100nF capacitor sets  $t_{SS}$  to 8.9ms. If the load capacitance is extremely large, the current required to maintain the preset  $t_{SS}$  exceeds the start-up current limit. In this scenario, the rising time is limited by the load capacitor and the start-up current limit ( $I_{LIMIT_SU}$ ). Float the SS pin to generate a fast ramp-up voltage. A current source (12µA) pulls up the MOSFET gate. The gate charge current controls the V<sub>OUT</sub> rising time. Meanwhile,  $t_{SS}$  is about 1.5ms, which is the minimum soft-start time.

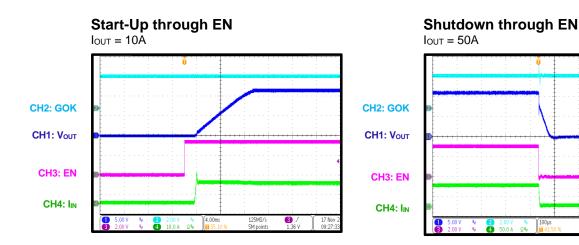

#### Start-Up Sequence

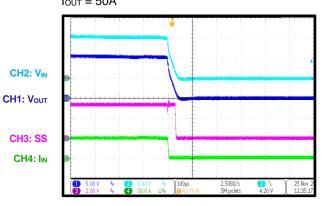

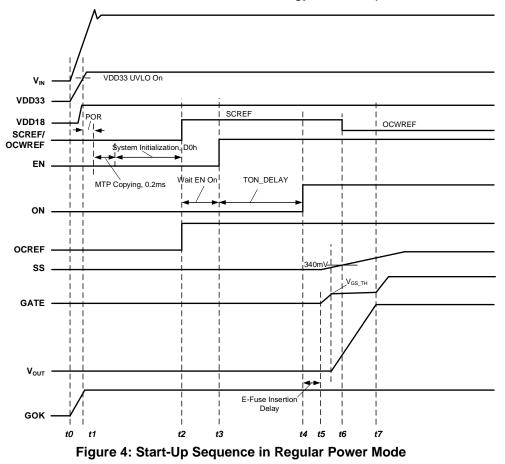

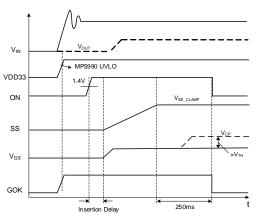

Figure 4 on page 20 shows the start-up sequence in regular power mode.

<u>t0 to t1</u>: At t0,  $V_{IN}$  rises immediately once the MP5990 is hot plugged into a live backplane. After  $V_{IN}$  exceeds its UVLO threshold, VDD33 starts ramping up. At t1, VDD33 reaches its UVLO rising threshold. Once the VDD33 power is ready, the GOK pin is high by default.

<u>t1 to t2</u>: The power-on reset (POR) signal waits for all power supplies to be stable. After POR, the data in the multiple-time programmable (MTP) memory starts loading into the operating registers to initialize system configuration. After MTP copying ends, the system initialization delay (configured via D0h) starts. All analog-todigital converter (ADC) channels start except for the ADDR channel. ON is low during this stage to keep the MOSFET off.

<u>t2 to t3</u>: Once the system initialization delay ends, the OCREF and SCREF\_OCWREF pins output their limit settings.

The PMBus address is set by detecting the ADDR pin voltage. Once the ADDR sample is obtained, the PMBus starts communication. If the MP5990 is configured for LPM, the device enters LPM once the system initialization delay ends.

t3 to t4: At t3, EN asserts high. If OPERATION (01h) is set to 0x80 (its default value) before t3, TON\_DELAY starts counting. TON\_DELAY does not start if an ON command is not received.

<u>t4 to t5</u>: When the TON\_DELAY time expires, ON pulls high to initiate the power MOSFET insertion delay time.

<u>t5 to t6</u>: At t5, the insertion delay time ends and the gate current source starts to charge the power MOSFET's gate. Once the MOSFET's gate voltage exceeds the turn-on threshold, the MP5990 starts to turn on the MOSFET with the controlled  $V_{OUT}$  slew rate to limit the inrush current.

<u>t6 to t7</u>: When the MP5990 detects that  $V_{SS}$  exceeds 340mV and ON is high, the output of SCREF\_OCWREF transitions from the SCP limit (SCREF) to the over-current warning limit (OCWREF). The SCREF and OCWREF levels can be set via register OCW\_SC\_REF (C5h). If  $V_{OUT}$  reaches the PG high threshold and the PG/OCW pin is selected to be PG, then PG asserts high.

t7 to t8: At t8, soft start ends. At this point, the MOSFET is fully enhanced and can deliver energy to the output.

MP5990 Rev. 1.1 4/19/2024

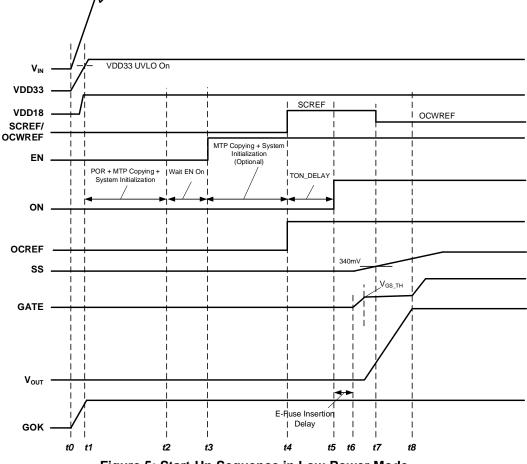

Figure 5 shows the start-up sequence in LPM. In LPM, ADVANCE\_CTRL (F1h), bit[13] selects whether the device should enter the optional MTP copying mode or initiate the system initialization delay time after EN pulls high. If bit[13] is set to 0, then the MP5990 starts TON\_DELAY after EN goes high. This sequence is different from regular power mode.

Figure 5: Start-Up Sequence in Low-Power Mode

#### **Current-Sense Output (CS)**

The CS pin provides a current proportional to  $I_{OUT}$  flowing through the device.  $V_{CS}$  is used for over-current (OC) limiting, OC warning indication, and parallel operation with start-up current balancing. The current-sense gain is 10µA/A while the MOSFET is fully on. A resistor (Rcs) on the CS pin generates V<sub>CS</sub>. I<sub>CS</sub> can be estimated with Equation (2):

$$I_{\rm CS} = I_{\rm OUT} \times 10 \mu \text{A/A}$$

(2)

$V_{CS}$  can be calculated with Equation (3):

$$V_{\rm CS} = I_{\rm CS} \times R_{\rm CS} \tag{3}$$

Once  $V_{CS}$  reaches  $V_{OCREF}$ , the internal circuit regulates  $V_{GATE}$  to maintain a constant I<sub>FET</sub>.

#### **Output Current Monitor (IMON)**

The MP5990 provides a high-accuracy MOSFET current monitor output (IMON). The current monitor gain is  $10\mu$ A/A. Connect a resistor (R<sub>IMON</sub>) between the IMON and GND pins. The recommended IMON voltage (V<sub>IMON</sub>) range is 0V to 1.6V, which is also within the internal ADC-sensing limit. IMON can be estimated with Equation (4):

$$I_{\rm IMON} = I_{\rm OUT} \times 10 \mu {\rm A} / {\rm A}$$

(4)

$V_{IMON}$  can be calculated with Equation (5):

١

$$V_{\rm IMON} = I_{\rm IMON} \times R_{\rm IMON}$$

(5)

If there is no bandwidth requirement, place a 2.2nF to 100nF capacitor from IMON to GND to smooth the indicator voltage.

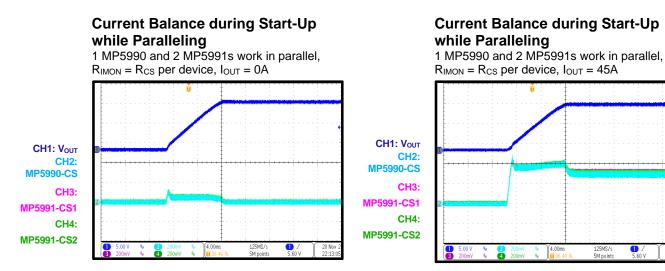

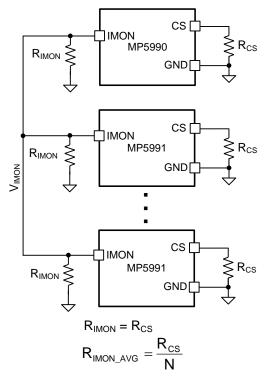

The MP5990 can operate in parallel with multiple MP5991s or other devices for highcurrent applications. The current-balance loop balances the start-up current for each active channel. Connect the IMON pins of all devices together for current balancing. The sensed current from each active IMON pin is summed, then divided by the number of active channels. The resulting average load current ( $I_{LOAD}$ ) provides a value for the total  $I_{LOAD}$ .

Start-up current balancing is essential to achieve the thermal advantages of parallel operation. Current sharing/balancing can aid power loss by dissipating the heat across the devices and the large area.

The MP5991's current balance is achieved by comparing the sensed CS current ( $I_{CS}$ ) of each device to the average current. This creates an appropriate V<sub>GATE</sub> adjustment for each Intelli-Fuse during start-up. The equivalent average R<sub>IMON</sub> (R<sub>IMON\_AVG</sub>) can be calculated with Equation (6):

$$R_{\rm IMON\_AVG} = R_{\rm CS} / N$$

(6)

Where N is the number of active devices.

#### **Over-Current Limit Reference (OCREF)**

The OCREF pin is a DAC output that sets the over-current reference ( $V_{OCREF}$ ), which can be configured to be between 0V and 1.76V via register OC\_REF (C6h).

The MP5990's I<sub>LOAD</sub> is limited by V<sub>OCREF</sub> and the external current-sense resistor (R<sub>CS</sub>). To regulate V<sub>GATE</sub>, V<sub>CS</sub> is compared to V<sub>OCREF</sub> through an amplifier. This prevents the Intelli-Fuse current from exceeding the current limit set by V<sub>OCREF</sub>.

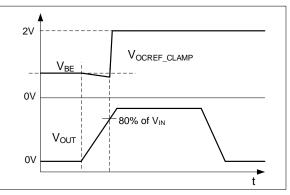

To protect the MP5990 from overheating during start-up, the OCREF pin has an internal clamp voltage ( $V_{OCREF_CLAMP}$ ) that depends on  $V_{IN}$  and  $V_{OUT}$  (see Figure 6). If  $V_{OUT}$  is below 80% of  $V_{IN}$ , then  $V_{OCREF_CLAMP}$  is  $V_{BE}$  (about 635mV with a negative temperature coefficient). If  $V_{OUT}$  exceeds 80% of  $V_{IN}$ , then  $V_{OCREF_CLAMP}$  is released to 2V.

Figure 6: OCREF Internal Clamp Voltage

If  $V_{OCREF}$  is below  $V_{OCREF\_CLAMP}$ , the actual current-limit reference voltage is determined by  $V_{OCREF}$ . If  $V_{OCREF}$  exceeds  $V_{OCREF\_CLAMP}$ , the actual current-limit reference voltage is determined by  $V_{OCREF\_CLAMP}$ .

#### **Over-Current Protection (OCP)**

The MP5990 provides two types of OCP:  $V_{IMON}$ -based total OCP and  $V_{CS}$ -based OCP on the Intelli-Fuse.

In multi-phase applications, Intelli-Fuse OCP can set the per-phase OCP limit. The total OCP limit can set the system's total OC limit.

The Intelli-Fuse over-current limit ( $I_{LIMIT}$ ) is a function of the CS resistor ( $R_{CS}$ ), current-sense gain ( $G_{CS}$ ), and  $V_{OCREF}$ .  $I_{LIMIT}$  can be calculated with Equation (7):

$$I_{\text{LIMIT}} = \frac{V_{\text{OCREF}}}{G_{\text{CS}} \times R_{\text{CS}}}$$

(7)

The MP5990's current limit can exceed the normal maximum load current, allowing for tolerances in the current-sense value.

#### Intelli-Fuse OCP during Start-Up

If  $V_{CS}$  exceeds  $V_{OCREF}$  during SS,  $V_{GATE}$  is regulated to maintain a constant I<sub>FET</sub>. If  $V_{OUT}$  is below 1/8 of  $V_{IN}$  and the MOSFET current is regulated by  $V_{OCREF}$  for 2.1ms, then the MOSFET turns off as a faulty latch condition and GOK is pulled low (see Figure 7 on page 23).

Figure 7: Failed Start-Up with Output Hard Short

#### Intelli-Fuse OCP at Normal Operation

If  $V_{OUT}$  exceeds 80% of  $V_{IN}$ , then the internal clamp voltage ( $V_{OCREF\_CLAMP}$ ) is released to 2V and  $V_{GATE}$  is close to the internal charge pump voltage. Once SS finishes, the MP5990 begins normal operation.

Once  $V_{CS}$  (configured via an external resistor) exceeds  $V_{OCREF}$ , the internal circuitry regulates  $V_{GATE}$  to maintain a constant current on the MOSFET. To limit  $I_{OUT}$ , the MOSFET's gate-tosource (GS) voltage ( $V_{GS}$ ) is regulated from 3.3V to 1V. The response time is about 14µs.  $I_{OUT}$  may have a small overshoot during this response time.

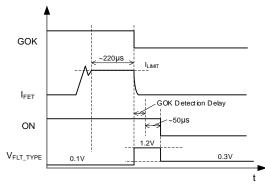

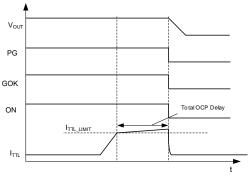

If  $I_{OUT}$  exceeds the current limit ( $I_{LIMIT}$ ), then the internal fault timer (220µs) starts. If  $I_{OUT}$  drops below  $I_{LIMIT}$  within the fault timer period, then the device resumes normal operation. If  $I_{OUT}$  exceeds  $I_{LIMIT}$  for 220µs, then the MOSFET latches off and GOK pulls low (see Figure 8).

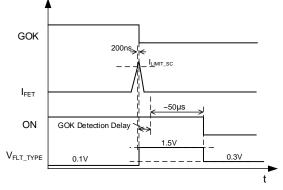

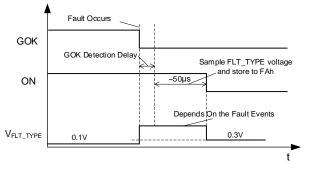

If an Intelli-Fuse OC fault occurs, FLT\_TYPE outputs 1.2V for about 50µs to indicate an OCP\_FUSE fault. Then FLT\_TYPE releases to 0.3V since ON is pulled low internally. The MP5990 samples the FLT\_TYPE voltage during the 50µs hold time, then stores the detailed fault types to FAh, bits[2:0].

In latch-off mode, FLT\_TYPE can be reset to 0.1V by cycling the power on VIN, VDD33, or EN, or by sending an ON command. Then the MOSFET turns on with soft start.

In hiccup mode, the MOSFET tries to soft start automatically and GOK is released high after the retry delay time ends. FLT\_TYPE reset back to 0.1V after the retry delay time expires.

#### Total OCP

The MP5990 senses the total output current  $(I_{TTL})$  through  $V_{IMON}$ . The sensed ADC value is converted into a direct  $I_{OUT}$ .  $R_{IMON}$  can be configured via IOUT\_CAL\_GAIN (38h) and stored in the NVM. The sensed  $I_{OUT}$  can be used for  $I_{OUT}$  reporting, OCW, and OCP. The total phase number should be configured via IOUT\_GAIN\_PHASE (4Dh) and stored in the NVM.

The total over-current limit ( $I_{TTL\_LIMIT}$ ) is configured via IOUT\_OC\_FAULT\_LIMIT (46h), and the total OC delay time ( $t_{TTL\_DELAY}$ ) is configured by register PRT\_DELAY (E8h). Total OCP can be configured for different protection modes via RETRY\_TIMES (F4h) and PROTECT\_CFG (E6h). These modes include no action, latch-off, retry (1 time to 14 times), and hiccup mode.

If the total current exceeds  $I_{TTL\_LIMIT}$  for the total OCP fault timer, then the MP5990 pulls ON low to turn off all the paralleled devices. Then GOK pulls low to indicate that the fault event occurred. Meanwhile, the PG and SS pins pull low and the FLT\_TYPE pin pulls to 0.3V (see Figure 9).

Figure 9: Total OCP Behavior

#### Short-Circuit Current Limit (SCREF)

If the load current increases rapidly due to a short circuit, the current may exceed  $I_{LIMIT}$  before the hot-swap OC control loop can respond. If the Intelli-Fuse current reaches the short-circuit current limit ( $I_{LIMIT\_SC}$ ), a fast turn-off circuit in the Intelli-Fuse is enabled to turn the MOSFET off. The total short-circuit response time is about 200ns. If a short-circuit event occurs, the ON and GOK pins pull low.

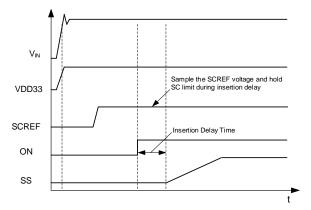

To determine  $I_{\text{LIMIT}_SC}$ , the MP5990 samples the SCREF voltage during the insertion delay time after ON exceeds its UVLO threshold (see Figure 10). The short-circuit current limit is held once the insertion delay time ends. Changing the SCREF voltage after the insertion delay time does not affect the short-circuit current. To select a new short-circuit current limit, the user must initiate the next insertion delay.

#### Figure 10: SCREF Samples and Holds the Short-Circuit Limit

The MP5990 provides five short-circuit levels. The level is selected by the SCREF voltage, which can be configured via OCW\_SC\_REF (C5h) and stored in the NVM. Table 1 shows the short-circuit current limit at different SCREF voltages.

| Table1: S | SCP Limit | Selection | Table |

|-----------|-----------|-----------|-------|

|-----------|-----------|-----------|-------|

| V <sub>SCREF</sub> (V) | SCP Limit (A) |

|------------------------|---------------|

| <0.16                  | 40            |

| 0.24 to 0.36           | 60            |

| 0.48 to 0.72           | 80            |

| 0.96 to 1.44           | 120           |

| >1.68                  | 100           |

The MP5990 provides short-circuit protection (SCP) to protect the part from a severe OC events, such as an output hard short to ground.

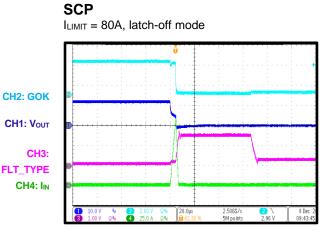

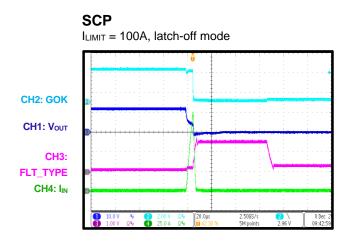

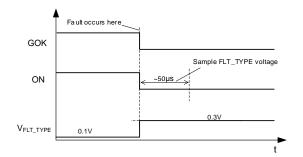

If the MOSFET current exceeds I<sub>LIMIT\_SC</sub>, the MOSFET turns off immediately, and GOK and SS pull low. FLT\_TYPE indicates 1.5V for about 50µs to indicate SCP has occurred, then the ON pin is pulled low internally (see Figure 11).

Figure 11: SCP Behavior

When a fault is cleared in latch-off mode, FLT\_TYPE can be reset to 0.1V by cycling the power on VIN, VDD33, or EN, or by sending an ON command. Then the power MOSFET turns on with soft start.

In hiccup mode, the MOSFET tries to SS automatically, and GOK pulls high after the retry delay time ends. FLT\_TYPE resets back to 0.1V after the retry delay time expires.

#### Input Voltage Sensing (VINSEN)

The MP5990 senses  $V_{IN}$  through the VINSEN pin. A resistor divider is connected from VIN to GND and tapped to VINSEN. Figure 12 shows the  $V_{IN}$  sense connection.

Figure 12: VIN and VOUT Sensing

The recommended top resistance for VINSEN is  $75k\Omega$ , and the recommended bottom resistance is  $4.99k\Omega$ . Place a 10nF capacitor in parallel with the bottom resistor.

# $\mathbf{MP5990} = 16V, 50A, 1m\Omega, INTELLIGENT HOT-SWAP SOLUTION WITH PMBUS$

The sensed ADC value is converted into a direct  $V_{IN}$  value. The VINSEN divider ratio can be configured via VIN\_SCALE (E4h) and stored in the NVM. The sensed  $V_{IN}$  is used for  $V_{IN}$  reporting,  $P_{IN}$  reporting,  $E_{IN}$  reporting, power MOSFET drain-to-source short detection,  $V_{IN}$  UVW alerts, and  $V_{IN}$  OVP.

#### **Output Voltage Sensing (VOSEN)**

The MP5990 senses  $V_{OUT}$  through the VOSEN pin. A resistor divider is connected from VOUT to GND and tapped to VOSEN. Figure 12 on page 24 shows the  $V_{OUT}$  sense connection. The recommended top resistor for VOSEN is 75k $\Omega$ , and the bottom resistor is 4.99k $\Omega$ . Place a 10nF capacitor in parallel with the bottom resistor.

The sensed ADC value is converted into a direct  $V_{OUT}$  value. The VOSEN divider ratio can be configured via VOUT\_SCALE\_LOOP (29h) and stored in the NVM. The sensed  $V_{OUT}$  is used for  $V_{OUT}$  reporting,  $P_{OUT}$  reporting, MOSFET drain-to-source short detection, and PG indication.

#### Temperature Sensing (VTEMP)

The MP5990 senses the on-die temperature and reports this value to the PMBus. When VDD33 exceeds its UVLO threshold and the MP5990 is in active mode, the VTEMP pin outputs a voltage proportional to  $T_J$ . The VTEMP output voltage (V<sub>TEMP</sub>) is 8.7mV/°C with a 152.5mV offset. V<sub>TEMP</sub> can be calculated with Equation (8):

$V_{\text{TEMP}} = T_{\text{I}} \times 8.7 \text{mV} + 152.5 \text{mV}$  (8)

For example, if  $T_J$  is 100°C, then  $V_{TEMP}$  is about 1.022V. If  $V_{TEMP}$  is 0V, then  $T_J$  is about -18°C. The total temperature sense range is -18°C to +140°C. When  $T_J$  is below -18°C, VTEMP remains at 0V.

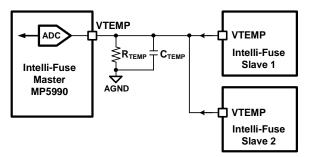

In multi-phase applications, the VTEMP pins of each Intelli-Fuse can be connected to the MP5990's VTEMP pin (see Figure 13). VTEMP indicates the highest T<sub>J</sub> of all the Intelli-Fuses. The MP5990 senses the voltage on VTEMP and reports the maximum temperature to the PMBus. The sensed temperature is used for system temperature monitoring, overtemperature warning (OTW), and OTP. Place a maximum 1nF capacitor and a minimum 10k $\Omega$ resistor on the VTEMP pin to filter noise.

#### Figure 13: Multi-Fuse Temperature-Sense in Parallel Operation

#### Power Good (PG) Indicator

The PG/OCW# pin can be configured to PG or OCW# via ON\_HICCUP\_DLY (C7h), bit[13]. When this pin is set as PG, PG stays low until all of the following conditions are met:

- The ON pin is high

- V<sub>SS</sub> > 340mV

- V<sub>OUT</sub> > the PG rising threshold, which is configured via POWER\_GOOD\_ON (5Eh)

- No DS short event is occurring

PG pulls low if any of the following events occur:

- <u>Shutdown events</u>: EN turns off, V<sub>IN</sub> UVLO, VDD33 UVLO, or an off command is received

- <u>Fault events</u>: DS short, total OCP, V<sub>IN</sub> OVP, OTP, or GOK fault (slave fault). If any of the above fault events are detected, PG deasserts low immediately

- V<sub>OUT</sub> < PG falling threshold, which is configured via POWER\_GOOD\_OFF (5Fh)

- V<sub>SS</sub> < 340mV, which is enabled when EFUSE\_CFG (C4h), bit[11] is set to 1

#### **GOK Report**

The GOK pin is an open drain with an internal, weak pull-up, active-low signal that reports Intelli-Fuse faults. If a fault occurs, GOK pulls low.

Pull GOK up to the VDD33 via a  $10k\Omega$  to  $100k\Omega$  resistor. During start-up, the GOK voltage (V<sub>GOK</sub>) rises according to V<sub>DD33</sub>.

In multi-phase applications, the GOK pins of each Intelli-Fuse are connected together. The MP5990 provides a comparator on the GOK pin for control during parallel operation. If the GOK voltage is below 1.5V, the MP5990 registers a system fault and pulls ON low to turn off all paralleled devices. If any of the paralleled devices has fault event, the system shuts down.

#### D\_OC and OCW# Reporting

The MP5990 provides two OCW indicators: D\_OC and OCW#.

The D\_OC pin is an open-drain, active-low output that reports an OCW condition when  $V_{OUT} \ge 90\%$  of  $V_{IN}$ . If  $V_{CS}$  exceeds the OCWREF voltage ( $V_{OCWREF}$ ), D\_OC is driven low. Once  $V_{CS}$  drops below  $V_{OCWREF}$  (the typical hysteresis voltage is 25mV), D\_OC is released high again. Pull D\_OC up to the VDD33 pin via a 10k $\Omega$  to 100k $\Omega$  resistor.

If PG/OCW# is set as OCW# and  $I_{TTL}$  exceeds the total OCW threshold, then OCW# pulls low immediately to indicate a total OCW event. Once  $I_{TTL}$  drops below the total OCW threshold, OCW# is released high again. The total OCW limit can be configured via IOUT\_OC\_WARN\_LIMIT (4Ah).

#### VIN\_UVW# Reporting

The VIN\_UVW# pin is an open-drain, active-low output. Once  $V_{IN}$  drops below the  $V_{IN}$  undervoltage warning (UVW) threshold, VIN\_UVW# pulls low immediately. When  $V_{IN}$  rises above the  $V_{IN}$  UVW threshold, VIN\_UVW# is released high again. The  $V_{IN}$  UVW threshold can be configured via VIN\_UV\_WARN\_LIMIT (58h).

Pull VIN\_UVW# up to the VDD33 voltage via a  $10k\Omega$  to  $100k\Omega$  resistor.

#### Fault Type Indication (FLT\_TYPE)

The MP5990 reports the fault type via the FLT\_TYPE pin's voltage. Table 3 shows the FLT\_TYPE voltage ( $V_{FLT_TYPE}$ ) for each fault condition.

| Table 2. Fault Type indication                                            |           |  |  |  |  |