# MPM54524

# Fully Integrated, 16V, Quad 5A Output Power Module with I<sup>2</sup>C Interface

# DESCRIPTION

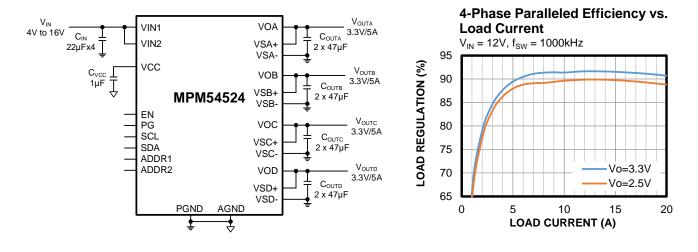

The MPM54524 is an integrated, quad 5A power module with an I<sup>2</sup>C interface. The device offers a complete power solution with built-in turn-on/-off sequencing control, configurable soft start (SS), compensation, and various protection thresholds.

Constant-on-time (COT) control provides ultrafast transient response. The output voltage  $(V_{OUTx})$  (where x = A, B, C, or D) is adjustable via the I<sup>2</sup>C bus or preset via the multiple-time programmable (MTP) memory. The power-on/off sequence is also configurable via the MTP or can be controlled via the I<sup>2</sup>C.

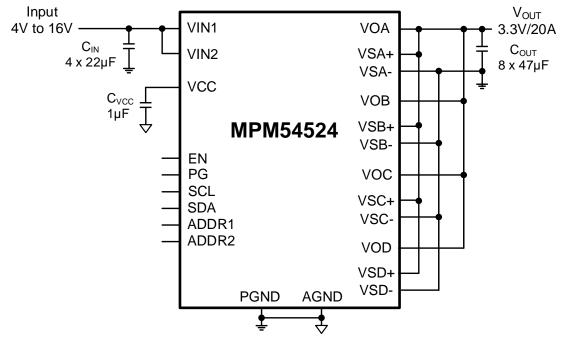

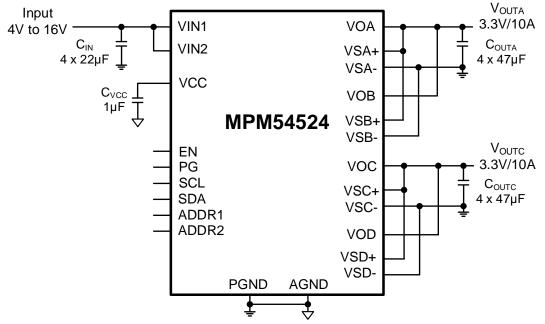

The MPM54524 offers configurable active voltage positioning (AVP), which generates a droop voltage ( $V_{DROOP}$ ). This allows four channels in parallel with passive current balancing. In addition, buck regulator A (buck A) and buck regulator B (buck B) can operate in parallel for up to 10A in interleaving mode, which enables active current balancing. Full protection features include under-voltage lockout (UVLO), over-current protection (OCP), over-voltage protection (UVP), and thermal shutdown.

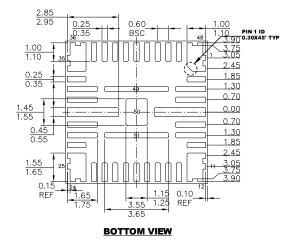

The MPM54524 requires a minimal number of external components, and is available in a compact ECLGA (8mmx8mmx2.9mm) package.

# FEATURES

- Wide 4V to 16V Input Voltage (V<sub>INx</sub>) (where x = 1 or 2) Range

- Adaptive Constant-On-Time (COT) for Ultra-Fast Transient Response

- Parallel Operation with Passive or Active Current Balancing

- I<sup>2</sup>C-Configurable Output Voltage (V<sub>OUTx</sub>) (where x = A, B, C, or D)

- Configurable Switching Frequency (f<sub>SW</sub>): 500kHz to 1000kHz

- Differential V<sub>OUTx</sub> Remote Sense (where x = A, B, or C)

- Accurate V<sub>OUTx</sub>, Output Current (I<sub>OUTx</sub>) (where x= A, B, C, or D), and Junction Temperature (T<sub>J</sub>) Monitoring via the I<sup>2</sup>C

- Open-Drain Power Good (PG) Indication

- Configurable I<sup>2</sup>C Slave Address

- Selectable Pulse-Frequency Modulation (PFM)/Pulse-Width Modulation (PWM) Mode, Adjustable Frequency, and Current Limit via the I<sup>2</sup>C

- Pre-Biased Start-Up

- Protections Include Over-Current Protection (OCP), Under-Voltage Protection (UVP), Under-Voltage Lockout (UVLO), Thermal Shutdown, and Over-Voltage Protection (OVP)

- Available in an ECLGA (8mmx8mmx2.9mm) Package

# APPLICATIONS

- FPGA and ASIC Power Supplies

- Networking and Telecommunications

- Optical Module Power Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

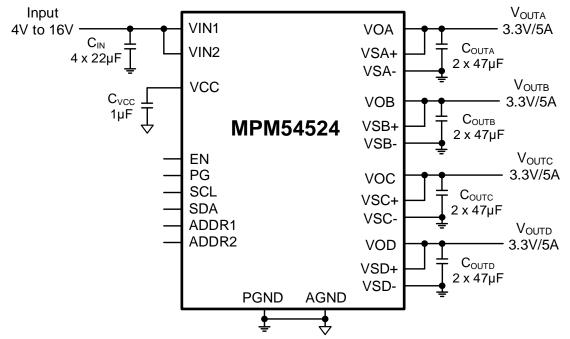

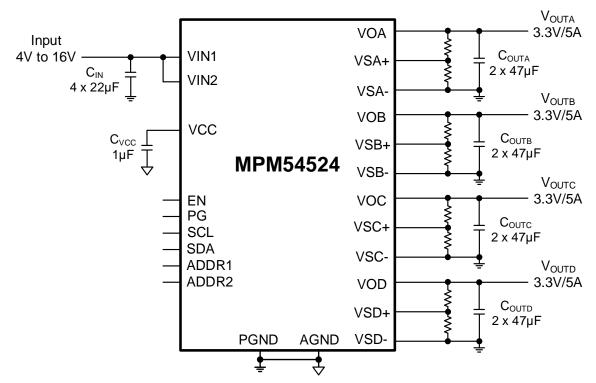

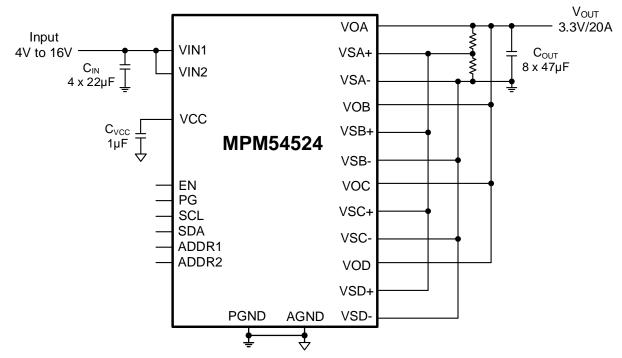

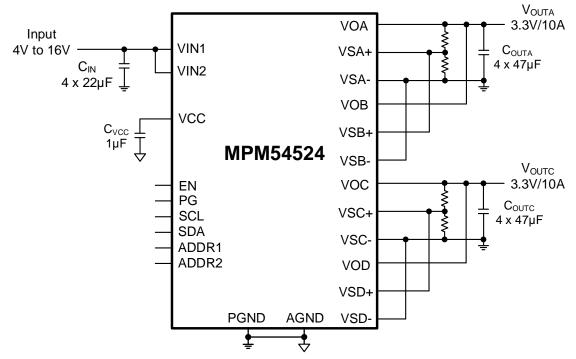

# **TYPICAL APPLICATION**

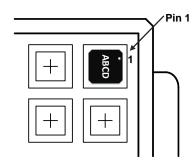

| •                  | Part Number* Package Top Marking MSL Rating   PM54524GCQ-xxxx** ECLGA-51 See Below 3 |             |            |  |

|--------------------|--------------------------------------------------------------------------------------|-------------|------------|--|

| Part Number*       | Package                                                                              | Top Marking | MSL Rating |  |

| MPM54524GCQ-xxxx** | ECLGA-51<br>(8mmx8mmx2.9mm)                                                          | See Below   | 3          |  |

| MPM54524GCQ-0000** | ECLGA-51<br>(8mmx8mmx2.9mm)                                                          | See Below   | 3          |  |

# **ORDERING INFORMATION**

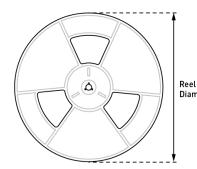

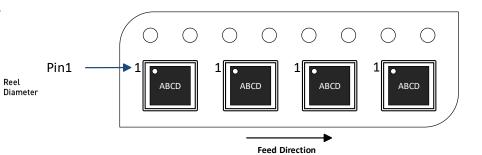

\* For Tray, add suffix -T (e.g. MPM54524GCQ-xxxx-T).

\* For Tape & Reel, add suffix -Z (e.g. MPM54524GCQ-xxxx-Z).

\*\* "xxxx" is the configuration code identifier for the register setting stored in the multiple-time programmable (MTP) memory. The default code is "0000". Each "x" can be a hexadecimal value between 0 and F. Work with an MPS FAE to create this unique number, even if ordering the "0000" code. See Table 3 on page 51 for the MPM54524GCQ-0000 detailed configuration.

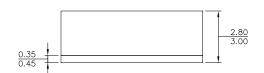

TOP MARKING <u>MPSYYWW</u> MP54524 LLLLLLLL M

MPS: MPS prefix YY: Year code WW: Week code MP54524: Part number LLLLLLLL: Lot number M: Module

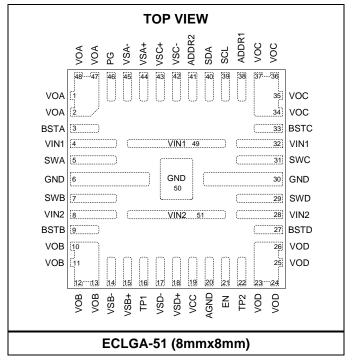

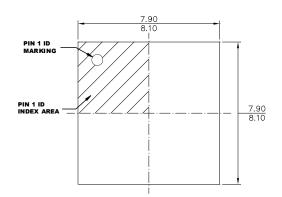

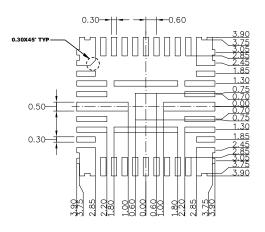

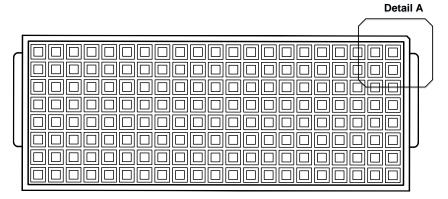

# **PACKAGE REFERENCE**

#### MPM54524 Rev. 1.0 4/15/2024 MF

MonolithicPower.com

4 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2024 MPS. All Rights Reserved.

# **PIN FUNCTIONS**

| Pin #             | Name  | Description                                                                                                                                                                                                                 |

|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 47,<br>48   | VOA   | Buck regulator A (buck A) output. The VOA pin is the output of buck A.                                                                                                                                                      |

| 3                 | BSTA  | Buck A bootstrap. Float the BSTA pin.                                                                                                                                                                                       |

| 4, 32, 49         | VIN1  | Supply voltage input of buck A and buck regulator C (buck C). Ceramic capacitors are required to decouple the input rail. Connect the VIN1 and VIN2 pins using a wide PCB trace.                                            |

| 5                 | SWA   | Buck A switching node. Float the SWA pin.                                                                                                                                                                                   |

| 6, 30, 50         | GND   | <b>Power ground.</b> The GND pin requires special consideration during PCB layout. Connect GND using copper traces and vias.                                                                                                |

| 7                 | SWB   | Buck B switching output. Float the SWB pin.                                                                                                                                                                                 |

| 8, 28, 51         | VIN2  | Supply voltage input of buck regulator B (buck B) and buck regulator D (buck D).<br>Ceramic capacitors are required to decouple the input rail. Connect the VIN1 and VIN2<br>pins using a wide PCB trace.                   |

| 9                 | BSTB  | Buck B bootstrap. Float the BSTB pin.                                                                                                                                                                                       |

| 10, 11,<br>12, 13 | VOB   | Buck B output. The VOB pin is the output of buck B.                                                                                                                                                                         |

| 14                | VSB-  | <b>Remote-sense ground of buck B.</b> Kelvin connect the VSB- pin to the ground node of the output capacitor ( $C_{OUT}$ ) for buck B.                                                                                      |

| 15                | VSB+  | Positive feedback of buck B. Connect the VSB+ pin to buck B's output.                                                                                                                                                       |

| 16                | TP1   | Test pin. Float the TP1 pin.                                                                                                                                                                                                |

| 17                | VSD-  | <b>Ground of buck D.</b> Kelvin connect the VSD- pin to the ground node of $C_{OUT}$ for buck D.                                                                                                                            |

| 18                | VSD+  | Positive feedback of buck D. Connect the VSD+ pin to buck D's output.                                                                                                                                                       |

| 19                | VCC   | <b>Internal 3.3V low-dropout (LDO) output.</b> The driver and control circuits are powered from the VCC pin voltage (V <sub>CC</sub> ). Decouple VCC using a $1\mu$ F ceramic capacitor placed as close to VCC as possible. |

| 20                | AGND  | Analog ground. Connect the AGND pin to the power GND pin.                                                                                                                                                                   |

| 21                | EN    | Enable control. Pull the EN pin high to enable the module; pull EN low to disable the module.                                                                                                                               |

| 22                | TP2   | Test pin. Float the TP2 pin.                                                                                                                                                                                                |

| 23, 24,<br>25, 26 | VOD   | Buck D output. The VOD pin is the output of Buck D.                                                                                                                                                                         |

| 27                | BSTD  | Buck D bootstrap. Float the BSTD pin.                                                                                                                                                                                       |

| 29                | SWD   | Buck D switching output. Float the SWD pin.                                                                                                                                                                                 |

| 31                | SWC   | Buck C switching output. Float the SWC pin.                                                                                                                                                                                 |

| 33                | BSTC  | Buck C bootstrap. Float the BSTC pin.                                                                                                                                                                                       |

| 34, 35,<br>36, 37 | VOC   | Buck C output. The VOC pin is the output of buck C.                                                                                                                                                                         |

| 38                | ADDR1 | <b>I<sup>2</sup>C bus address.</b> There are 9 selectable I <sup>2</sup> C addresses. To select the I <sup>2</sup> C address, pull the ADDR1 pin high, low, or float the pin.                                               |

| 39                | SCL   | I <sup>2</sup> C clock.                                                                                                                                                                                                     |

| 40                | SDA   | I <sup>2</sup> C data.                                                                                                                                                                                                      |

| 41                | ADDR2 | I <sup>2</sup> C address. There are 9 I <sup>2</sup> C selectable addresses by pulling the ADDR2 pin high, low, or floating the pin.                                                                                        |

| 42                | VSC-  | Remote-sense ground of buck C. Kelvin connect the VSC- pin to the ground node of Cout for buck C.                                                                                                                           |

| Pin # | Name | Description                                                                                                                                                                         |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43    | VSC+ | Positive feedback of buck C. Connect the VSC+ pin to buck C's output directly.                                                                                                      |

| 44    | VSA+ | <b>Positive feedback of buck A.</b> Connect buck A's output to the VSA+ pin directly. In dual-<br>phase interleaving mode, VSA+ must be connected to VSB+.                          |

| 45    | VSA- | <b>Remote-sense ground of buck A.</b> Kelvin connect the VSA- pin to the ground node of $C_{OUT}$ for buck A.                                                                       |

| 46    | PG   | <b>Open-drain power good output.</b> Pull the PG pin low when any enabled regulator drops below the under-voltage (UV) threshold. Pull PG low when all the regulators are disabled. |

# PIN FUNCTIONS (continued)

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply voltage (V <sub>INx</sub> )     | 18V                         |

|----------------------------------------|-----------------------------|

| V <sub>SWx_DC</sub>                    |                             |

| V <sub>BSTx</sub>                      | V <sub>SW</sub> + 4V        |

| VOA, VOB, VOC, VOD                     | 6V                          |

| V <sub>cc</sub>                        |                             |

| V <sub>CC</sub> , ADDR1, ADDR2, PG (1s | s) <sup>(2)</sup>           |

|                                        | 6V                          |

| All other pins                         | 0.3V to +4.3V               |

| Continuous power dissipation           | $(T_A = 25^{\circ}C)^{(6)}$ |

|                                        |                             |

| Junction temperature (T <sub>J</sub> ) | 150°C                       |

| Storage temperature                    | 65°C to +150°C              |

# ESD Ratings

| Human body model (HBM)±2kV      |  |

|---------------------------------|--|

| Charged-device model (CDM) ±2kV |  |

# **Recommended Operating Conditions** <sup>(3)</sup>

| Supply voltage (V <sub>INx</sub> )        | 4V to 16V      |

|-------------------------------------------|----------------|

| Output voltage (V <sub>OUTx</sub> )       | 0.4V to 5.5V   |

| Operating junction temp (T <sub>J</sub> ) | 40°C to +125°C |

# Thermal Resistance (4) (5) (6) (7) (8)

| θ <sub>JA</sub>     | 16°C/W  |

|---------------------|---------|

| θ <sub>JC_TOP</sub> | 0.3°C/W |

| θ <sub>JB</sub>     | 4.4°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) Voltage rating during multiple-time programmable (MTP) memory configuring.

- 3) The device is not guaranteed to function outside of its operating conditions.

- θ<sub>JA</sub> is the junction-to-ambient thermal resistance, θ<sub>JC\_TOP</sub> is the junction-to-case top thermal characterization parameter, and θ<sub>JB</sub> is the junction-to-board thermal characterization parameter.

- 5) The thermal parameter is based on testing on the MPS evaluation board, EVM54524-CQ-00A, under no airflow cooling conditions in a standard enclosure. The EVM54524-CQ-00A is a 4-layer, 2oz board (8.1cmx8.1cm).

- 6) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature.

- 7) The junction-to-case top thermal characterization parameter,  $\theta_{JC\_TOP}$ , estimates the junction temperature in the real system, based on the equation,  $T_J = \theta_{JC\_TOP} \times P_{LOSS} + T_{CASE\_TOP}$ , where  $P_{LOSS}$  is the entire loss of the module in real application, and  $T_{CASE\_TOP}$  is the case top temperature.

- 8) The junction-to-board thermal characterization parameter,  $\theta_{JB}$ , estimates the junction temperature in the real system, based on the equation,  $T_J = \theta_{JB} \times P_{LOSS} + T_{BOARD}$ , where  $P_{LOSS}$  is the entire loss of the module in real application, and  $T_{BOARD}$  is the the board temperature.

# **ELECTRICAL CHARACTERISTICS**

# $V_{IN}$ = 12V, $T_J$ = -40°C to +125°C <sup>(9)</sup>, typical values are tested at $T_J$ = 25°C, unless otherwise noted.

| Parameter                                                                                                   | Symbol                        | Condition                                                                                        | Min  | Тур  | Max  | Units                    |

|-------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|--------------------------|

| Supply current (no switching)                                                                               | lin                           | No switching, FB high,<br>pulse-frequency modulation (PFM),<br>no I <sup>2</sup> C communication |      | 7.24 |      | mA                       |

| Default switching frequency                                                                                 | f <sub>sw</sub>               | 0Fh = 0xAA                                                                                       |      | 1000 |      | kHz                      |

| VIN1 or VIN2                                                                                                |                               |                                                                                                  |      |      |      |                          |

| $V_{INx}$ over-voltage (OV) rising threshold (where $x = 1$ or 2)                                           | VINx_OV_R                     | 90h, bit[0] = 1'b1                                                                               |      | 15   |      | V                        |

| V <sub>INx</sub> OV hysteresis                                                                              | VINx_OV_HYS                   |                                                                                                  |      | 0.25 |      | V                        |

| V <sub>INx</sub> under-voltage lockout<br>(UVLO) rising threshold                                           | VINx_UVLO_R                   | 90h, bit[1] = 1'b1,                                                                              | 2.85 | 3.05 | 3.25 | V                        |

| V <sub>INx</sub> UVLO hysteresis                                                                            | V <sub>INx_UVLO_</sub><br>HYS | AFh, bits[1:0] = 2'b00                                                                           |      | 0.25 |      | V                        |

| Enable (EN)                                                                                                 |                               |                                                                                                  |      |      |      |                          |

| EN logic high voltage                                                                                       | $V_{\text{EN}_{\text{H}}}$    |                                                                                                  | 1.2  |      |      | V                        |

| EN logic low voltage                                                                                        | $V_{\text{EN}_{L}}$           |                                                                                                  |      |      | 0.35 | V                        |

| EN internal pull-down resistance                                                                            | R <sub>EN_DOWN</sub>          |                                                                                                  |      | 2.7  |      | MΩ                       |

| ADDR1 or ADDR2                                                                                              |                               |                                                                                                  |      |      |      |                          |

| ADDR1 or ADDR2 logic high voltage                                                                           | V <sub>ADDRx_H</sub>          |                                                                                                  | 1.2  |      |      | V                        |

| ADDR1 or ADDR2 logic low voltage                                                                            | VADDRx_L                      |                                                                                                  |      |      | 0.35 | V                        |

| Buck Regulators (Buck A, B                                                                                  | uck B, Buck                   | C, or Buck D)                                                                                    |      |      |      |                          |

|                                                                                                             | $V_{FBA}$                     | 25h, bit[3] = 1'b1, 15h = 0x90                                                                   | 3.31 | 3.36 | 3.41 | V                        |

| Feedback (FB) voltage                                                                                       | V <sub>FBB</sub>              | 25h, bit[2] = 1'b1, 16h = 0x90                                                                   | 3.31 | 3.36 | 3.41 | V                        |

| accuracy                                                                                                    | V <sub>FBC</sub>              | 25h, bit[1] = 1'b1, 17h = 0x90                                                                   | 3.31 | 3.36 | 3.41 | V                        |

|                                                                                                             | V <sub>FBD</sub>              | 25h, bit[0] = 1'b1, 18h = 0x90                                                                   | 3.31 | 3.36 | 3.41 | V                        |

| Output voltage ( $V_{OUTx}$ ) (where $X = A, B, C, \text{ or } D$ ) under-<br>voltage (UV) rising threshold | V <sub>OUTx_UV_R</sub>        |                                                                                                  |      | 85   |      | % of<br>Vouт             |

| Voutx UV falling threshold                                                                                  | Voutx_uv_f                    |                                                                                                  |      | 80   |      | % of<br>Vouт             |

| Low-side (LS) current limit (source)                                                                        | ILS_VALLEY1                   | 26h = 0xAA                                                                                       |      | 5.5  |      | А                        |

| Minimum on time (10)                                                                                        | ton_min1                      |                                                                                                  |      | 30   |      | ns                       |

| Minimum off time (10)                                                                                       | t <sub>OFF_MIN1</sub>         |                                                                                                  |      | 120  |      | ns                       |

| Output over-voltage<br>protection (OVP) rising<br>threshold                                                 | Vovp1_h                       |                                                                                                  |      | 112  |      | % of<br>V <sub>REF</sub> |

| Output OVP recovery threshold                                                                               | Vovp1_L                       |                                                                                                  |      | 109  |      | % of<br>V <sub>REF</sub> |

# ELECTRICAL CHARACTERISTICS (continued)

# $V_{IN} = 12V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ <sup>(9)</sup>, typical values are tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                         | Symbol               | Condition                                                | Min  | Тур  | Max  | Units                    |

|---------------------------------------------------|----------------------|----------------------------------------------------------|------|------|------|--------------------------|

| Soft-start (SS) time of buck regulator A (buck A) | t <sub>SS_A</sub>    | 12h, bits[7:6] = 2b'10,<br>V <sub>OUT</sub> = 10% to 90% |      | 2    |      | ms                       |

| SS time of buck regulator B (buck B)              | t <sub>ss_в</sub>    | 12h, bits[5:4] = 2b'10,<br>V <sub>OUT</sub> = 10% to 90% |      | 2    |      | ms                       |

| SS time of buck regulator C (buck C)              | t <sub>ss_c</sub>    | 12h, bits[3:2] = 2b'10,<br>V <sub>OUT</sub> = 10% to 90% |      | 2    |      | ms                       |

| SS time of buck regulator D (buck D)              | tss_D                | 12h, bits[1:0] = 2b'10,<br>V <sub>OUT</sub> = 10% to 90% |      | 2    |      | ms                       |

| Discharge resistance                              | RDIS                 | 0Eh, bits[3:1] = 3b'000/111                              | -40% | 10/2 | +40% | Ω                        |

| Analog-to-Digital Converter                       | (ADC)                |                                                          |      |      |      |                          |

| VOUTx readback accuracy                           |                      | V <sub>OUTx</sub> = 3.3V                                 | 217  | 220  | 223  | LSB                      |

| Output current readback accuracy                  |                      | Iout = 4A                                                |      | 32   |      | LSB                      |

| Power Good (PG)                                   |                      |                                                          |      |      |      |                          |

| PG UV rising threshold                            | Vpg_uv_r             |                                                          |      | 98   |      | % of<br>V <sub>REF</sub> |

| PG UV falling threshold                           | Vpg_uv_f             |                                                          |      | 95   |      | % of<br>V <sub>REF</sub> |

| PG OV rising threshold                            | V <sub>PG_OV_R</sub> | 0Dh, bits[3:0] = 0000                                    |      | 105  |      | % of<br>V <sub>REF</sub> |

| PG OV falling threshold                           | V <sub>PG_OV_F</sub> |                                                          |      | 102  |      | % of<br>V <sub>REF</sub> |

| PG output port sink current capability            | Vpg_sink             | Sink 1mA                                                 |      |      | 0.4  | V                        |

| VCC Regulator                                     |                      |                                                          |      |      |      |                          |

| Vcc UVLO rising threshold                         | V <sub>CC_R</sub>    |                                                          | 2.5  | 2.7  | 2.9  | V                        |

| Vcc UVLO hysteresis                               | Vcc_hys              |                                                          |      | 300  |      | mV                       |

| VCC voltage                                       | Vcc                  | $I_{CC} = 25 \text{mA}$                                  |      | 3.3  |      | V                        |

| Vcc regulation                                    | Vcc_rg               | Icc = 0mA to 25mA                                        |      | 1    |      | %                        |

| Temperature Protections                           |                      |                                                          |      |      |      |                          |

| Thermal shutdown (10)                             | T <sub>OTP_R</sub>   |                                                          |      | 145  |      | °C                       |

| Thermal hysteresis (10)                           | T <sub>HYS</sub>     |                                                          |      | 20   |      | °C                       |

Notes:

9) Not tested in production. Guaranteed by over-temperature correlation.

10) Not tested in production. Guaranteed by engineering sample characterization.

# I<sup>2</sup>C PORT SIGNAL CHARACTERISTICS (11)

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ <sup>(9)</sup>, typical values are tested at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                                                    | Symbol Condition    | С <sub>в</sub> =                    | С <sub>в</sub> = 100рF |        | С <sub>в</sub> = 400рF    |     |     |

|----------------------------------------------------------------------------------------------|---------------------|-------------------------------------|------------------------|--------|---------------------------|-----|-----|

|                                                                                              |                     | Condition                           | Min                    | Max    | Min                       | Max |     |

| SCL clock frequency                                                                          | fschl               |                                     | 0                      | 3.4    | 0                         | 0.4 | MHz |

| Set-up time for a repeated start command                                                     | tsu_sta             |                                     | 160                    |        | 600                       |     | ns  |

| Hold time (repeated) for a start command                                                     | t <sub>HD_STA</sub> |                                     | 160                    |        | 600                       |     | ns  |

| SCL clock low period                                                                         | t <sub>LOW</sub>    |                                     | 160                    |        | 1300                      |     | ns  |

| SCL clock high period                                                                        | tніgн               |                                     | 60                     |        | 600                       |     | ns  |

| Data set-up time                                                                             | tsu_dat             |                                     | 10                     |        | 100                       |     | ns  |

| Data hold time                                                                               | thd_dat             |                                     | 0                      | 70     | 0                         |     | ns  |

| SCL signal rising time                                                                       | tr_cL               |                                     | 10                     | 40     | 20 х<br>0.1С <sub>в</sub> | 300 | ns  |

| Rising time of the SCL<br>signal after a repeated<br>start command and an<br>acknowledge bit | tr_c∟1              |                                     | 10                     | 80     | 20 х<br>0.1С <sub>в</sub> | 300 | ns  |

| SCL signal falling time                                                                      | t <sub>F_CL</sub>   |                                     | 10                     | 40     | 20 x<br>0.1Cb             | 300 | ns  |

| SDA signal rising time                                                                       | <b>t</b> fDA        |                                     | 10                     | 80     | 20 х<br>0.1С <sub>в</sub> | 300 | ns  |

| SDA signal falling time                                                                      | t <sub>F_DA</sub>   |                                     | 10                     | 80     | 20 х<br>0.1С <sub>в</sub> | 300 | ns  |

| Set-up time for stop command                                                                 | tsu_sто             |                                     | 160                    |        | 600                       |     | ns  |

| Bus free time between a stop and start condition                                             | t <sub>BUF</sub>    |                                     | 160                    |        | 1300                      |     | ns  |

| Data valid time                                                                              | t <sub>VD_DAT</sub> |                                     |                        | 16     |                           | 90  | ns  |

| Data valid acknowledge time                                                                  | tvd_acк             |                                     |                        | 160    |                           | 900 | ns  |

| Consolitive load for each                                                                    |                     | SDA and SCL line                    |                        | 100    |                           | 400 | pF  |

| Capacitive load for each bus line                                                            | Св                  | SDAH + SDA line,<br>SCLH + SCL line |                        | 400    |                           | 400 | pF  |

| Low-level noise margin                                                                       | С                   | For each connected device           |                        | 0.1Vcc | 0.1Vcc                    |     | V   |

| High-level noise margin                                                                      | V <sub>NH</sub>     | For each connected device           |                        | 0.2Vcc | 0.2Vcc                    |     | V   |

#### Note:

11) The maximum I<sup>2</sup>C bus voltage must be below 4V. A 1.8V or 3.3V typical bus voltage is recommended.

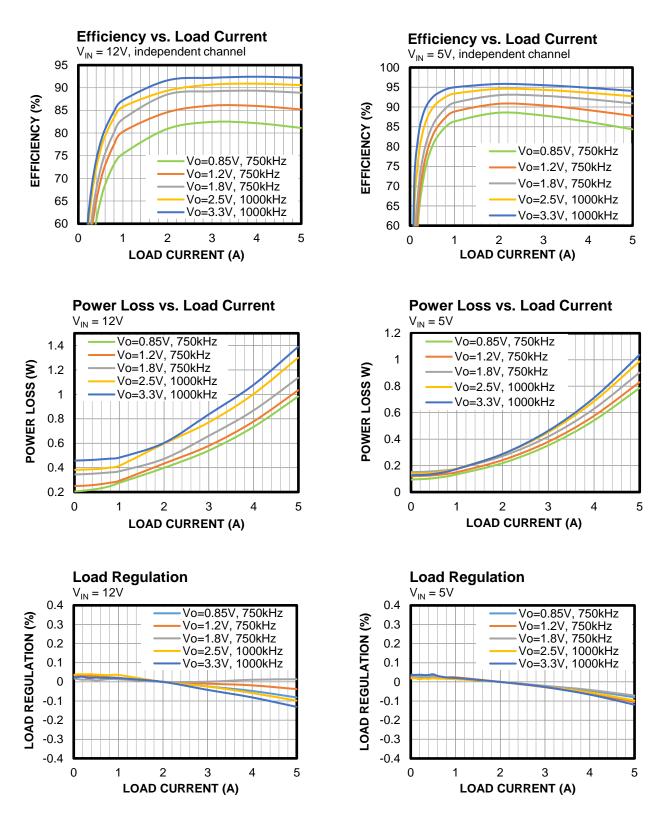

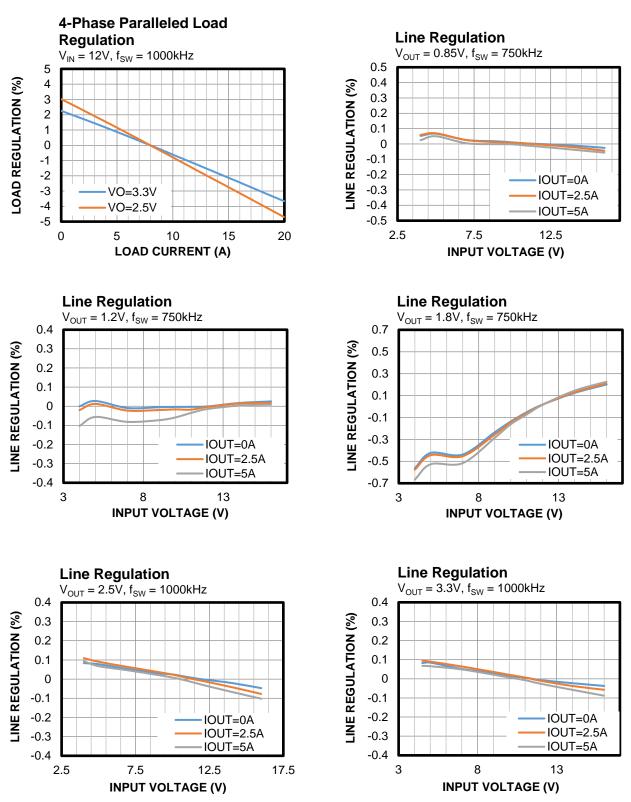

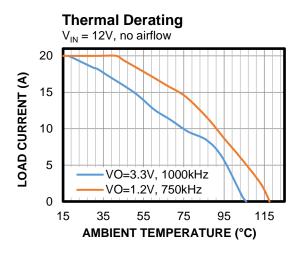

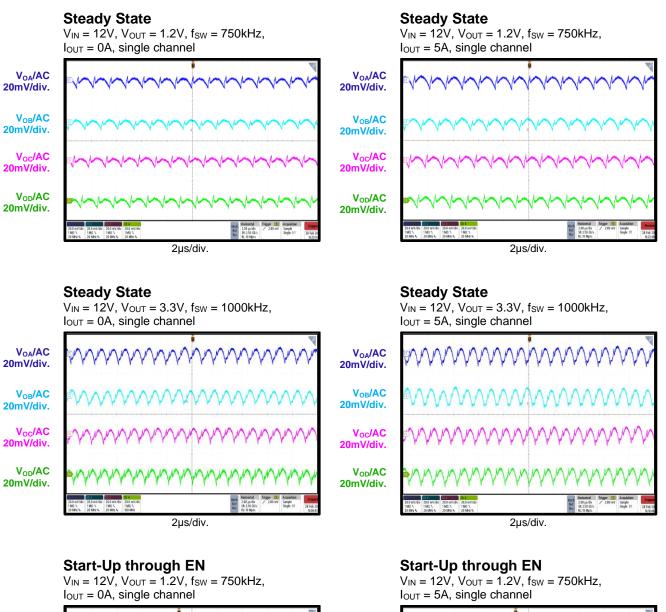

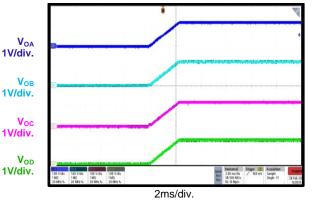

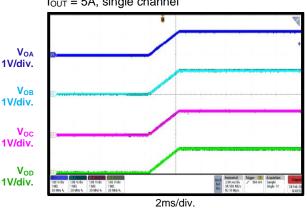

# **TYPICAL PERFORMANCE CHARACTERISTICS**

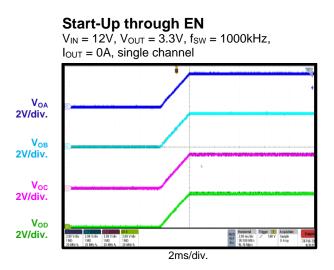

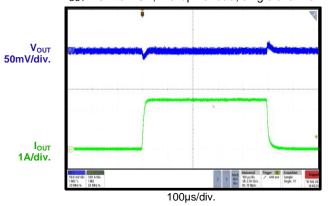

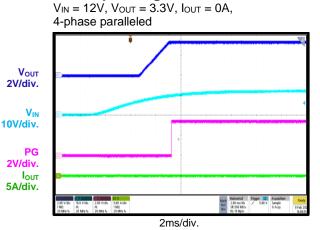

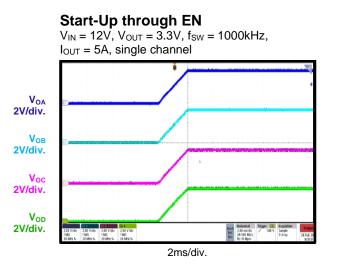

Performance curves are tested on the evaluation board.  $V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

MPM54524 Rev. 1.0 4/15/2024 M

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2024 MPS. All Rights Reserved.

Performance curves are tested on the evaluation board.  $V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

Performance curves are tested on the evaluation board.  $V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

Performance curves are tested on the evaluation board.  $V_{IN} = 12V$ ,  $T_A = 25$ °C, unless otherwise noted.

Performance curves are tested on the evaluation board.  $V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

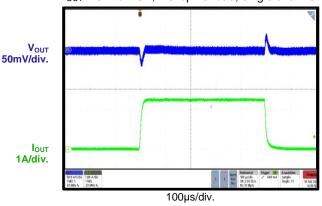

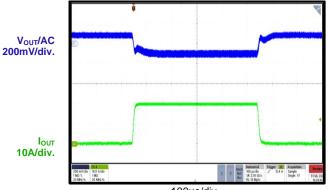

#### Load Transient

$V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 750$ kHz,  $I_{OUT} = 0A$  to 2.5A, 2.5A/µs e-load, single channel

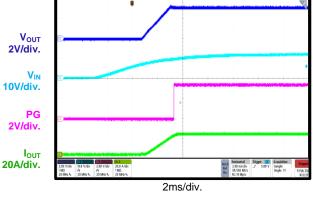

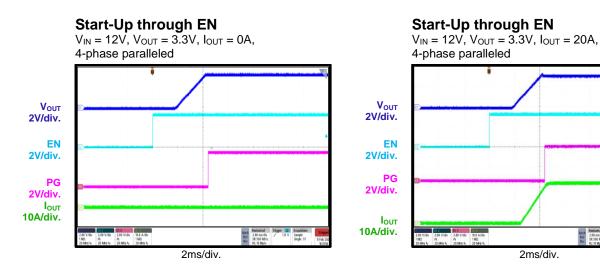

#### Start-Up through VIN

# Load Transient

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $f_{SW} = 1000$ kHz,  $I_{OUT} = 0A$  to 2.5A, 2.5A/µs e-load, single channel

# Start-Up through VIN

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 20A$ , 4-phase paralleled

Performance curves are tested on the evaluation board.  $V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

#### Load Transient

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 0A$  to 20A, 2.5A/µs e-load, 4-phase paralleled

100µs/div.

Trigger 2 Acquisition / 112 V Sample Single 1/1

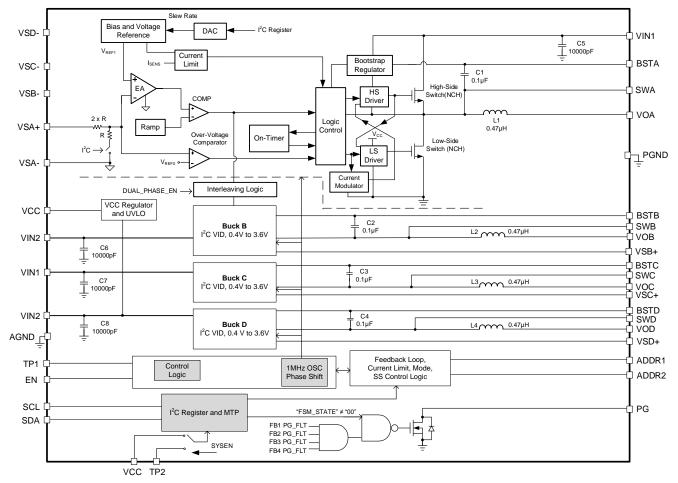

# FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

# OPERATION

The MPM54524 is a quad, synchronous, stepdown DC/DC power module that offers built-in soft start (SS), compensation, and protections including over-voltage protection (OVP), undervoltage protection (UVP), and over-current protection (OCP). Fixed-frequency constant-ontime (COT) control provides fast transient response.

# Power Supply Input and Under-Voltage Protection (UVP)

The input voltage ( $V_{INx}$ ) (where x = 1 or 2) is the power module's power supply. If  $V_{INx}$  exceeds the UVP rising threshold and all the other startup conditions are met, then the four-channel buck regulators start up. The bucks shut down once  $V_{INx}$  drops below the UVP falling threshold.

#### Internal VCC Supply

VCC is the internal driver and power supply of the control circuitries. A decoupling capacitor is required to stabilize the regulator and reduce ripple. This regulator takes the VINx input (where x = 1 or 2) and operates across the full V<sub>INx</sub> range. If V<sub>INx</sub> exceeds 3.5V, the regulator's output is in full regulation. If V<sub>INx</sub> drops below 3.5V, the regulator's output decreases according to the changes in V<sub>INx</sub>.

#### Enable (EN)

If  $V_{INx}$  exceeds the under-voltage lockout (UVLO) threshold, pull the EN pin above 1.2V to enable the MPM54524. Float EN or pull the pin down to ground to disable the MPM54524. There is an internal 2.7M $\Omega$  resistor connected between EN and ground.

If EN is pulled high and reaches the V<sub>IN</sub> UVLO threshold, BUCKX\_CTRL\_REG (0Ch), bits[7:4] can enable or disable the four channels after the power-on sequence is complete. If the power-on sequence set via 19h to 1Ch, bit[7] = 1'b0, then the outputs of the four channels are disabled by default. Once EN and VIN are ready, 0Ch can enable the four channels.

When the MPM54524 is disabled, the part goes into output discharge or soft shutdown mode if the two functions are enabled.

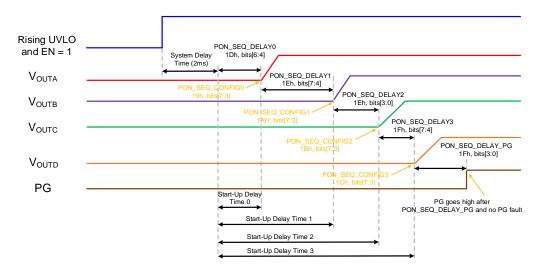

#### **Power-On Sequence**

Once the VINx supply is valid and EN is pulled high, the MPM54524 initiates the power-on sequences of configuration 0, configuration 1, configuration 2, and configuration 3 via 19h to 1Fh to enable the corresponding output regulators in the specified sequence. Figure 2 on page 17 shows the power-on sequence. After V<sub>IN</sub> reaches the UVLO threshold, EN goes high, and a 2ms system delay, each channel follows the start-up delay time, soft-start time (t<sub>SS x</sub>) (where x = A, B, C, or D), and PON\_SEQ\_DELAY0 time to execute the power-on sequence. Before enabling each channel, the MPM54524 loads the default voltage of each channel from the multiple-time programmable (MTP) memory registers.

$t_{SS_x}$  for each channel can be configured via 13h.

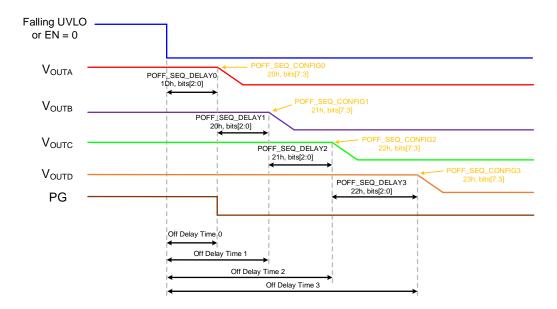

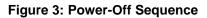

#### **Power-Off Sequence**

If the EN pin is logic low or  $V_{INx}$  is below its UVLO threshold, the MPM54524 enters the power-off sequence set via 1Dh to 23h. Figure 3 on page 17 shows the power-off sequence. After each channel finishes its off delay, the MPM54524 turns off each channel sequentially with discharge or soft shutdown if the two functions are enabled. The discharge enable/disable function and discharge resistor can be configured via 0Eh. The soft shutdown enable/disable and t<sub>SS\_x</sub> can be configured via 11h, bits[7:4] and 12h, bits[7:0].

During the power-off sequence at falling UVLO, if rising UVLO is detected again, all the channels continue to execute the power-off sequence, then turn on sequentially based on the new power-on sequence.

#### **Pre-Biased Start-Up**

The MPM54524 is designed for monotonic startup into pre-biased loads. If the output is prebiased to a set voltage during start-up, the internal bootstrap (BST) voltage ( $V_{BST}$ ) is refreshed and charged, and the voltage on the internal soft-start capacitor ( $C_{SS}$ ) is charged as well. If  $V_{BST}$  exceeds its rising threshold, and the  $C_{SS}$  voltage exceeds the sensed output voltage  $(V_{OUTx})$  (where x = A, B, C, or D) at the feedback pin (VSA+, VSB+, VSC+, or VSD+), then the part starts to work normally.

### Power Good (PG)

The MPM54524 provides a power good (PG) output to indicate whether the enabled buck's  $V_{OUTx}$  is ready. The PG pin is an open-drain output. Connect PG to VCC or another voltage source via a pull up resistor (e.g. 10k $\Omega$ ). PG is pulled high after the PON\_SEQ\_DELAY\_PG bit,

and all the channels finish soft start if they are enabled. During normal operation, PG is pulled low if any fault occurs.

### **Output Over-Voltage Protection (OVP)**

The MPM54524 monitors  $V_{OUTx}$  and enters OVP latch-off mode once  $V_{OUTx}$  exceeds the output OVP rising threshold ( $V_{OVP1_H}$ ). After triggering output OVP, all the channels turn off and PG is low. The MPM54524 does not automatically start up again until the OV fault is removed and recycling power on EN is initiated.

Figure 2: Power-On Sequence

# V<sub>INx</sub> Over-Voltage Protection (OVP)

If 90h, bit[0] = 1 and  $V_{INx}$  exceeds 15V for longer than 2µs, then the MPM54524 shuts down and VIN\_OV\_STATUS (00h, bit[1]) is set from 0 to 1. Even when the  $V_{INx}$  over-voltage (OV) fault is removed, the MPM54524 does not automatically start up until recycling power on EN is initiated. VIN\_OV\_STATUS remains set to 1 until power is recycled on EN, or the host clears the fault by writing the clear bit to 1 in 07h, bit[1].

#### Over-Current Protection (OCP) and Short-Circuit Protection (SCP)

The MPM54524 provides valley current limit control. When the low-side MOSFET (LS-FET) is on, the inductor current ( $I_L$ ) is monitored. If the sensed  $I_L$  exceeds the valley current limit threshold, the device indicates an over-current (OC) fault via 2Ah. The high-side MOSFET (HS-FET) is not allowed to turn on until the valley current drops below the OC threshold. Meanwhile,  $V_{OUTx}$  drops until it is below the under-voltage (UV) threshold.

Once the UV and OC conditions are triggered, OCP latches off the device. This means the MPM54524 disables the output power stage and does not automatically turn on again until the UV and OC faults are removed, and recycling power on EN is initiated.

# **Output Discharge**

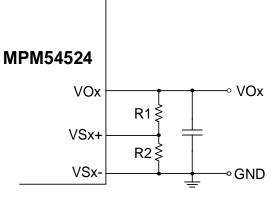

To discharge the energy of the output capacitor  $(C_{OUT})$  during the power-off sequence, there is a discharge path between the VOx pin and ground (where x = A, B, C, or D). The discharge function can be enabled via the MTP interface. The discharge resistor can also be changed via the MTP interface.

# Soft Start (SS) and Soft Shutdown

The MPM54524 employs a soft start and soft shutdown mechanism to ensure smooth output during start-up and shutdown.

When the MPM54524 is enabled and  $V_{BST}$  reaches its rising threshold, the internal digitalto-analog converter (DAC) outputs a ramp voltage as the reference voltage ( $V_{REF}$ ).  $V_{OUTx}$ smoothly ramps up with  $V_{REF}$ . Once the DAC output reaches the final voltage, it maintains a steady voltage. At this point, soft start finishes and enters steady-state operation. When the MPM54524 is disabled, the internal DAC ramps down  $V_{REF}$ .  $V_{OUTx}$  follows the soft shutdown slew rate with  $V_{REF}$  until the output drops to 0.15V. Then soft shutdown stops, and the output is discharged via a  $30\Omega$  discharge resistor.

The start-up delay, shutdown delay, soft-start and soft shutdown slew rate can be configured via the MTP.

# **Out-of-Phase Operation**

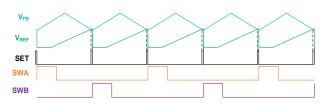

Figure 4 shows that buck regulator A (buck A), buck regulator B (buck B), buck regulator C (buck C), and buck regulator D (buck D) are frequency-locked with a fixed 90° phase shift, except for during interleaving mode.

Figure 4: Phase Shift Functional Diagram

When buck A and buck B work in interleaving parallel mode, the phase shift between buck A and buck B changes to 180° (see Figure 5 on page 19). Buck C and buck D cannot work in interleaving mode, with the phase shift remaining at 90°.

# Interleaving Mode for Buck A and Buck B

The MPM54524 supports 2-phase interleaving mode for buck A and buck B by setting 14h, bit[5] = 1. VSA+ must be connected to VSB+ in interleaving mode.

Figure 5 on page 19 shows the internal SET signal that is triggered when buck A or buck B's feedback (FB) signal is smaller than the internal REF signal. When the SET signal becomes high, only one phase's pulse-width modulation (PWM) output becomes high; the next time SET goes high, the next phase's PWM output goes high. This achieves automatic interleaving.

Figure 5: Dual-Phase Interleaving Mode

When buck A and buck B work in dual phase interleaving mode, the MPM54524 senses two-phase current and automatically tunes the buck's on time ( $t_{ON}$ ) to achieve current balance actively.

### Active Voltage Positioning (AVP)

The MPM54524 supports active voltage positioning (AVP) by setting the AVP\_EN\_X/X bit (where x = A/B or C/D) (71h, bit[7] and 79h, bit[7]) to 1 via the I<sup>2</sup>C. Once enabled, V<sub>OUTx</sub> of the corresponding channel drops in proportion with the load current, which is determined using Equation (1) and Equation (2).

The droop voltage ( $V_{DROOP}$ ) can be calculated with Equation (1):

$$V_{DROOP} = I_{OUT} \times R_{DROOP}$$

(1)

Where  $R_{DROOP}$  is the droop resistance with a typical value of about  $40m\Omega$ .

$V_{OUTx}$  can be calculated with Equation (2):

$$V_{OUTx} = V_{REFx} - V_{DROOP}$$

(2)

Where  $V_{\mathsf{REFx}}$  is the reference voltage of each channel.

The AVP functions enables on-demand parallel operation, where four outputs, three outputs, or two outputs can be connected in parallel in any combination without pre-setting any registers. The current of the paralleled channels is inherently balanced by  $V_{DROOP}$ , which is generated by the AVP function.

#### Thermal Shutdown

The MPM54524 employs thermal shutdown by internally monitoring the junction temperature (T<sub>J</sub>). If T<sub>J</sub> exceeds the 145°C threshold, the MPM54524 shuts down based on the soft shutdown ramping down slew rate. This is a non-latch protection. There is a hysteresis of about 20°C. Once T<sub>J</sub> drops to about 125°C, the MPM54524 initiates a soft start.

### Analog-to-Digital Converter (ADC)

The MPM54524 supports the analog-to-digital converter (ADC) to monitor the regulator's  $V_{INx}$ ,  $V_{OUTx}$ , output current ( $I_{OUTx}$ ), and output power ( $P_{OUTx}$ ) (where x = A, B, C, or D).

#### Multiple-Time Programmable (MTP) Configuration

After the MPM54524's  $V_{INx}$  starts up, the systemon-chip (SoC) configures the MPM54524's I<sup>2</sup>C register and MTP.

See the I<sup>2</sup>C Interface section on page 20 for more details on identifying a valid slave address. When the SoC writes to the I<sup>2</sup>C register, the I<sup>2</sup>C register takes effect immediately; it can also be burned into the MTP. During the buck's normal operation, the I<sup>2</sup>C master can read and write the register's data online.

# I<sup>2</sup>C INTERFACE

# I<sup>2</sup>C Serial Interface

The I<sup>2</sup>C is a 2-wire, bidirectional, serial interface consisting of a data line (SDA) and a clock line (SCL). The lines are pulled to a bus voltage externally when they are idle. When connecting to the line, a master device generates the SCL signal and device address, then arranges the communication sequence. The MPM54524 interface is an I<sup>2</sup>C slave. The I<sup>2</sup>C interface adds flexibility to the power supply solution.

# I<sup>2</sup>C Address Selection

Two ADDR pins are available to configure bit[0] to bit[3] of the l<sup>2</sup>C slave address according to Table 1, where bit[4] to bit[6] can be modified by writing to 73h, bit[1] to bit[3], respectively. Table 1 shows the l<sup>2</sup>C address setting via the ADDR1 and ADDR2 pins.

Table 1: I<sup>2</sup>C Address Setting via the ADDR1 and ADDR2 Pins

| ADDR1 | ADDR2 | I <sup>2</sup> C Address  |

|-------|-------|---------------------------|

| Low   | Low   | 0XXX 1001 <sup>(12)</sup> |

| Low   | Float | 0XXX 1100 <sup>(12)</sup> |

| Low   | High  | 0XXX 1110 <sup>(12)</sup> |

| Float | Low   | 0XXX 1010 <sup>(12)</sup> |

| Float | Float | 0XXX 1000 <sup>(12)</sup> |

| Float | High  | 0XXX 1111 <sup>(12)</sup> |

| High  | Low   | 0XXX 1011 <sup>(12)</sup> |

| High  | Float | 0XXX 1101 (12)            |

| High  | High  | 0XXX 0111 <sup>(12)</sup> |

#### Note:

12) "XXX" refers to the portion of the address that can be configured by the customer.

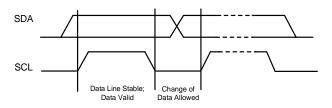

# **Data Validity**

One clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the clock's high period. The high or low state of the data line can only change when the clock signal on the SCL line is low (see Figure 6).

Figure 6: Bit Transfer on the I<sup>2</sup>C Bus

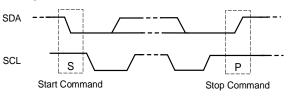

The start (S) and stop (P) commands are signaled by the master device, which signifies the beginning and the end of the  $I^2C$  transfer. The start command is defined as the SDA signal transitioning from high to low while SCL is high. The stop command is defined as the SDA signal transitioning from low to high while SCL is high (see Figure 7).

Figure 7: Start and Stop Commands

Start and stop commands are always generated by the master. The bus is busy after the start condition, and it is considered to be free again a minimum of 4.7µs after the stop command. The bus remains busy if a repeated start (Sr) is generated instead of a stop command. The start and repeated start conditions are functionally identical.

#### **Transfer Data**

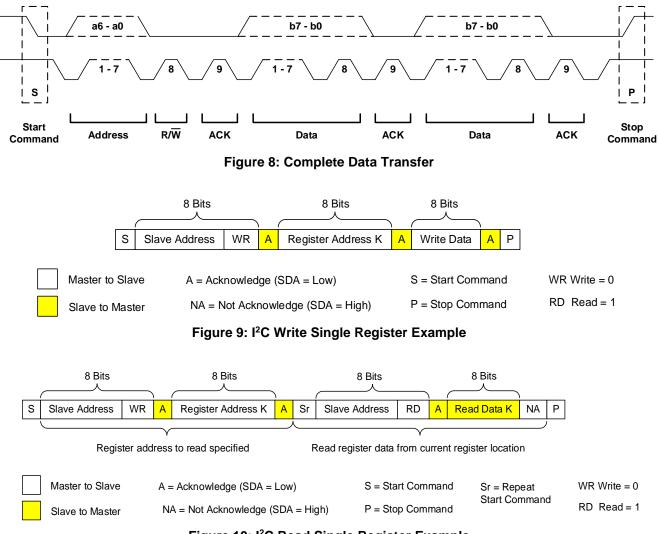

Every byte put on the SDA line must be 8 bits long. Each byte must be followed by an acknowledge (ACK) bit. The acknowledgerelated clock pulse is generated by the master. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable low during the clock pulse's high period.

Figure 8 on page 21 shows the data transfer format. After the start command, a slave address is sent. This address is 7 bits, followed by an 8th data direction bit (R/W). A 0 indicates a transmission (write), and a 1 indicates a request for data (read). A data transfer is always terminated by a stop command, which is generated by the master. If the master still wants to communicate on the bus, it can generate a repeated start command and address another slave without first generating a stop command.

The MPM54524 requires a start command, a valid I<sup>2</sup>C address, register address byte, and data byte for a single data update. After receiving each byte, the MPM54524 acknowledges by pulling the SDA line low during a single clock pulse's high period. A valid I<sup>2</sup>C address selects

the MPM54524. The MPM54524 performs an update on the LSB byte's falling edge.

Figure 9 shows an example of writing to a single register. Figure 10 shows an example of reading to a single register.

Figure 10: I<sup>2</sup>C Read Single Register Example

# SUPPORTED PMBUS COMMANDS

| Command Code | Command Name            | Туре | Bytes |

|--------------|-------------------------|------|-------|

| 00h          | STATUS_0                | R    | 1     |

| 01h          | STATUS_1                | R    | 1     |

| 02h          | BUCKA_CURRENT/PWR_METER | R    | 1     |

| 03h          | BUCKB_CURRENT/PWR_METER | R    | 1     |

| 04h          | BUCKC_CURRENT/PWR_METER | R    | 1     |

| 05h          | BUCKD_CURRENT/PWR_METER | R    | 1     |

| 06h          | BUCKX_VOLTAGE           | R    | 1     |

| 07h          | CLEAR_0                 | Send | 1     |

| 08h          | CLEAR_1                 | Send | 1     |

| 09h          | MASK_0                  | R/W  | 1     |

| 0Ah          | MASK_1                  | R/W  | 1     |

| 0Bh          | REMOTE_REG              | R/W  | 1     |

| 0Ch          | BUCKX_CTRL_REG          | R/W  | 1     |

| 0Dh          | PG_REG                  | R/W  | 1     |

| 0Eh          | DISCHARGE_R_REG         | R/W  | 1     |

| 0Fh          | SW_FREQ_REG             | R/W  | 1     |

| 10h          | MONITOR_EN_REG          | R/W  | 1     |

| 11h          | SOFT_STOP_EN_REG        | R/W  | 1     |

| 12h          | SOFT_STOP_REG           | R/W  | 1     |

| 13h          | SOFT_START_REG          | R/W  | 1     |

| 14h          | PROTECT_REG             | R/W  | 1     |

| 15h          | BUCKA_VOUT              | R/W  | 1     |

| 16h          | BUCKB_VOUT              | R/W  | 1     |

| 17h          | BUCKC_VOUT              | R/W  | 1     |

| 18h          | BUCKD_VOUT              | R/W  | 1     |

| 19h          | PON_CONFIG_0            | R/W  | 1     |

| 1Ah          | PON_CONFIG_1            | R/W  | 1     |

| 1Bh          | PON_CONFIG_2            | R/W  | 1     |

| 1Ch          | PON_CONFIG_3            | R/W  | 1     |

| 1Dh          | PON_OFF_DELAY0          | R/W  | 1     |

| 1Eh          | PON_SEQ_DELAY_1_2       | R/W  | 1     |

| 1Fh          | PON_SEQ_DELAY_3_PG      | R/W  | 1     |

| 20h          | POFF_SEQ_CONFIG_0       | R/W  | 1     |

| 21h          | POFF_SEQ_CONFIG_1       | R/W  | 1     |

| 22h          | POFF_SEQ_CONFIG_2       | R/W  | 1     |

| 23h          | POFF_SEQ_CONFIG_3       | R/W  | 1     |

| 24h          | ADC_TEMP                | R    | 1     |

| 25h          | VOUT_RANGE_SELECT       | R/W  | 1     |

| 26h          | CLP_BUCKX               | R/W  | 1     |

| 2Ah          | OC_STATUS_CLEAR         | R/W  | 1     |

| 30h          | MTP_AUTO_REG            | R/W  | 1     |

# SUPPORTED PMBUS COMMANDS (continued)

| Command Code | Command Name               | Туре | Bytes |

|--------------|----------------------------|------|-------|

| 31h          | PART_ID                    | R    | 1     |

| 35h          | CODE_ID                    | R    | 1     |

| 36h          | CODE_VERSION               | R    | 1     |

| 71h          | ACTIVE_POSITION_ENABLE_A/B | R/W  | 1     |

| 73h          | I2C_ADDRESS                | R/W  | 1     |

| 79h          | ACTIVE_POSITION_ENABLE_C/D | R/W  | 1     |

| 90h          | VIN_OV_REG                 | R/W  | 1     |

| AFh          | VIN_UVLO_REG               | R/W  | 1     |

# **REGISTER MAP**

### **Status Registers**

The status registers are updated to 1 if an event occurs, and they remain at 1 until the clear command is generated by the host, even if the failing condition is no longer present. In addition, when the input voltage  $(V_{INx})$  (where x = A, B, C, or D) drops below its under-voltage lockout (UVLO) threshold, the status register is initialized to 0. The PWR\_GOOD interrupt may be generated by the MPM54524 at the same time, depending on the type of event. The interrupts are only generated if they are not masked.

All read-only (RO) registers are one-time latched registers, meaning that once the MPM54524 sets the register flag, the host must explicitly clear the register. The MPM54524 does not automatically update the registers even if the event that triggered the status is no longer present.

# STATUS\_0 (00h)

Format: Unsigned binary

The STATUS\_0 command monitors statuses including over-temperature (OT), buck output power not good, and  $V_{INx}$  over-voltage (OV).

| Bits | Access | Bit Name                        | Default | Description                                                                                           |

|------|--------|---------------------------------|---------|-------------------------------------------------------------------------------------------------------|

| 7    | R      | RESERVED                        | N/A     | Reserved.                                                                                             |

| 6    | R      | OVER_TEMP_<br>STATUS            | 1'b0    | 1'b0: No critical temperature shutdown occurs<br>1'b1: A critical temperature shutdown occurs         |

| 5    | R      | BUCKA_POWER_<br>NOT_GOOD_STATUS | 1'b0    | 1'b0: The buck regulator A (buck A)'s output is power good<br>1'b1: Buck A's output is power not good |

| 4    | R      | BUCKB_POWER_<br>NOT_GOOD_STATUS | 1'b0    | 1'b0: The buck regulator B (buck B)'s output is power good<br>1'b1: Buck B's output is power not good |

| 3    | R      | BUCKC_POWER_<br>NOT_GOOD_STATUS | 1'b0    | 1'b0: The buck regulator C (buck C)'s output is power good<br>1'b1: Buck C's output is power not good |

| 2    | R      | BUCKD_POWER_<br>NOT_GOOD_STATUS | 1'b0    | 1'b0: The buck regulator D (buck D)'s output is power good<br>1'b1: Buck D's output is power not good |

| 1    | R      | VIN_OV_STATUS                   | 1'b0    | 1'b0: No V <sub>IN</sub> OV fault occurs<br>1'b1: A V <sub>IN</sub> OV fault occurs                   |

| 0    | R      | RESERVED                        | N/A     | Reserved.                                                                                             |

# STATUS\_1 (01h)

#### Format: Unsigned binary

The STATUS\_1 command monitors buck x output's OV and under-voltage (UV) status (where x = A, B, C, or D).

| Bits | Access | Bit Name        | Default | Description                                                                                |

|------|--------|-----------------|---------|--------------------------------------------------------------------------------------------|

| 7    | R      | BUCKA_OV_STATUS | 1'b0    | 1'b0: Buck A's output indicates no OV fault<br>1'b1: Buck A's output indicates an OV fault |

| 6    | R      | BUCKB_OV_STATUS | 1'b0    | 1'b0: Buck B's output indicates no OV fault<br>1'b1: Buck B's output indicates an OV fault |

| 5    | R      | BUCKC_OV_STATUS | 1'b0    | 1'b0: Buck C's output indicates no OV fault<br>1'b1: Buck C's output indicates an OV fault |

| 4    | R      | BUCKD_OV_STATUS | 1'b0    | 1'b0: Buck D's output indicates no OV fault<br>1'b1: Buck D's output indicates an OV fault |

| 3    | R      | BUCKA_UV_STATUS | 1'b0    | 1'b0: Buck A's output indicates no UV fault<br>1'b1: Buck A's output indicates an UV fault |

| 2 | R | BUCKB_UV_STATUS | 1'b0 | 1'b0: Buck B's output indicates no UV fault<br>1'b1: Buck B's output indicates an UV fault |

|---|---|-----------------|------|--------------------------------------------------------------------------------------------|

| 1 | R | BUCKC_UV_STATUS | 1'b0 | 1'b0: Buck C's output indicates no UV fault<br>1'b1: Buck C's output indicates an UV fault |

| 0 | R | BUCKD_UV_STATUS | 1'b0 | 1'b0: Buck D's output indicates no UV fault<br>1'b1: Buck D's output indicates an UV fault |

# BUCKA\_CURRENT/PWR\_METER (02h)

#### Format: Direct

The BUCKA\_CURRENT/PWR\_METER command monitors buck A's output current ( $I_{OUTA}$ ) and output power ( $P_{OUTA}$ ).

| Bits | Access                            | Bit Name                                                                                                                                                                         | Description                                                                                                                                                |  |  |

|------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      |                                   |                                                                                                                                                                                  | If 10h, bit[3] = 0, this measures buck A's $I_{OUTA}$ or $P_{OUTA}$ . The $I_{OUTA}$ analog-to-<br>digital converter (ADC) report values are listed below: |  |  |

|      | 7:0 R BUCKA_ADC_<br>CURRENT/POWER |                                                                                                                                                                                  | 8'b 0000 0000: Reserved<br>8'b 0000 0001: 0.125A or 125mW<br>8'b 0000 0010: 0.25A or 250mW<br>8'b 0000 0011: 0.375A or 375mW                               |  |  |

| 7.0  |                                   | BUCKA ADC                                                                                                                                                                        | 8'b 0011 1100 = 7.5A or 7500mW<br>8'b 0011 1101 = 7.625A or 7625mW<br>8'b 0011 1110 = 7.75A or 7750mW<br>8'b 0011 1111 ≥ 7.875A or 7875mW                  |  |  |

| 7:0  |                                   | If 10h, bit[3] = 1, this indicates the sum of $P_{OUTA}$ , buck B's output power ( $P_{OUTB}$ ), buck C's output power ( $P_{OUTC}$ ), and buck D's output power ( $P_{OUTD}$ ). |                                                                                                                                                            |  |  |

|      |                                   | 8'b 0000 0000: Reserved<br>8'b 0000 0001: 125mW<br>8'b 0000 0010: 250mW<br>8'b 0000 0011: 375mW                                                                                  |                                                                                                                                                            |  |  |

|      |                                   |                                                                                                                                                                                  | 8'b 1111 1100 = 31500mW<br>8'b 1111 1101 = 31625mW<br>8'b 1111 1110 = 31750mW<br>8'b 1111 1111 ≥ 31875mW                                                   |  |  |

# BUCKB\_CURRENT/PWR\_METER (03h)

#### Format: Direct

The BUCKB\_CURRENT/PWR\_METER command monitors buck B's output current (IOUTB) and POUTB.

| Bits | Access | Bit Name                    | Description                                                                                                                                                                                                                                                                                                                                                     |

|------|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | R      | BUCKB_ADC_<br>CURRENT/POWER | The I <sub>OUTB</sub> or P <sub>OUTB</sub> ADC report values are listed below:<br>8'b 0000 0000: Reserved<br>8'b 0000 0001: 0.125A or 125mW<br>8'b 0000 0010: 0.25A or 250mW<br>8'b 0000 0011: 0.375A or 375mW<br><br>8'b 0011 1100 = 7.5A or 7500mW<br>8'b 0011 1101 = 7.625A or 7625mW<br>8'b 0011 1110 = 7.75A or 7750mW<br>8'b 0011 1111 ≥ 7.875A or 7875mW |

# BUCKC\_CURRENT/PWR\_METER (04h)

### Format: Direct

The BUCKC\_CURRENT/PWR\_METER command monitors buck C's output current (Ioutc) and Poutc.

| Bits | Access | Bit Name                    | Description                                                                                                                                                                                                                                                                                                                             |

|------|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | R      | BUCKC_ADC_<br>CURRENT/POWER | The loute or Poute ADC report values are listed below:<br>8'b 0000 0000: Reserved<br>8'b 0000 0001: 0.125A or 125mW<br>8'b 0000 0010: 0.25A or 250mW<br>8'b 0000 0011: 0.375A or 375mW<br><br>8'b 0011 1100 = 7.5A or 7500mW<br>8'b 0011 1101 = 7.625A or 7625mW<br>8'b 0011 1110 = 7.75A or 7750mW<br>8'b 0011 1111 ≥ 7.875A or 7875mW |

# BUCKD\_CURRENT/PWR\_METER (05h)

#### Format: Direct

The BUCKD\_CURRENT/PWR\_METER command monitors buck D's output current (IOUTD) and POUTD.

| Bits | Access | Bit Name                    | Description                                                                                                                                                                                                                                                                                                                             |

|------|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | R      | BUCKD_ADC_<br>CURRENT/POWER | The loute or Poute ADC report values are listed below:<br>8'b 0000 0000: Reserved<br>8'b 0000 0001: 0.125A or 125mW<br>8'b 0000 0010: 0.25A or 250mW<br>8'b 0000 0011: 0.375A or 375mW<br><br>8'b 0011 1100 = 7.5A or 7500mW<br>8'b 0011 1101 = 7.625A or 7625mW<br>8'b 0011 1110 = 7.75A or 7750mW<br>8'b 0011 1111 ≥ 7.875A or 7875mW |

# BUCKX\_VOLTAGE (06h)

#### Format: Direct

The BUCKX VOLTAGE command monitors VOUTX.

| Bits | Access | Bit Name              | Description                                                               |

|------|--------|-----------------------|---------------------------------------------------------------------------|

|      |        |                       | Changes V <sub>OUTx</sub> based on 10h, bits[6:[5].                       |

| 7:0  | R      | BUCKX_ADC_<br>VOLTAGE | 8'b 0000 0000 = Undefined<br>8'b 0000 0001 = 15mV<br>8'b 0000 0010 = 30mV |

|      |        |                       | <br>8'b 1111 1111 ≥ 3825mV                                                |

# **Clear Registers**

For each real-time status register (00h and 01h), the MPM54524 offers a way to clear the status of events. All clear registers are write-1-to-clear (W1C) registers. If 1 is written to any of the clear registers, the MPM54524 updates the status registers to the default state and removes the interrupt condition on the PWR\_GOOD output signal, assuming that the event is no longer present. If the failing condition is still present, the status register remains at 1. Note that the PWR\_GOOD interrupt is only applicable if the event is not masked.

The MPM54524 offers a global clear command by writing 1 to 07h, bit[0]. This command works the same way as the individual clear command. This command can be used by the host if more than one clear command is required to different registers.

# CLEAR\_0 (07h)

#### Format: Unsigned binary

The CLEAR\_0 command clears the buck's output power not good and V<sub>INx</sub> over-voltage protection (OVP) status, in addition to providing a global clear.

| Bits | Access | Bit Name                                  | Default | Description                                  |

|------|--------|-------------------------------------------|---------|----------------------------------------------|

| 7:6  | R      | RESERVED                                  | N/A     | Reserved.                                    |

| 5    | R/W    | CLEAR_BUCKA_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Clears the status of 00h, bit[5]       |

| 4    | R/W    | CLEAR_BUCKB_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Clears the status of 00h, bit[4]       |

| 3    | R/W    | CLEAR_BUCKC_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Clears the status of 00h, bit[3]       |

| 2    | R/W    | CLEAR_BUCKD_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Clears the status of 00h, bit[2]       |

| 1    | R/W    | CLEAR_VIN_OVP_<br>STATUS                  | 1'b0    | 1'b1: Clears the status of 00h, bit[1]       |

| 0    | R/W    | CLEAR_GLOBAL                              | 1'b0    | 1'b1: Clears all the statuses of 00h and 01h |

# CLEAR\_1 (08h)

Format: Unsigned binary

The CLEAR\_1 command clears the buck x's OV and UV status (where x = A, B, C, or D).

| Bits | Access | Bit Name                  | Default | Description                            |

|------|--------|---------------------------|---------|----------------------------------------|

| 7    | R/W    | CLEAR_BUCKA_OV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[7] |

| 6    | R/W    | CLEAR_BUCKB_OV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[6] |

| 5    | R/W    | CLEAR_BUCKC_OV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[5] |

| 5    | R/W    | CLEAR_BUCKD_OV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[4] |

| 3    | R/W    | CLEAR_BUCKA_UV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[3] |

| 2    | R/W    | CLEAR_BUCKB_UV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[2] |

| 1    | R/W    | CLEAR_BUCKC_UV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[1] |

| 0    | R/W    | CLEAR_BUCKD_UV_<br>STATUS | 1'b0    | 1'b1: Clears the status of 01h, bit[0] |

# **Mask Registers**

For each real-time status register, the MPM54524 offers a way to mask the status of events.

### MASK\_0 (09h)

Format: Unsigned binary

The MASK\_0 command masks buck x's output power not good and the V<sub>INx</sub> OVP status.

| Bits | Access | Bit Name                                 | Default | Description                           |

|------|--------|------------------------------------------|---------|---------------------------------------|

| 7:6  | R      | RESERVED                                 | N/A     | Reserved.                             |

| 5    | R/W    | MASK_BUCKA_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Masks the status of 00h, bit[5] |

| 4    | R/W    | MASK_BUCKB_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Masks the status of 00h, bit[4] |

| 3    | R/W    | MASK_BUCKC_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Masks the status of 00h, bit[3] |

| 2    | R/W    | MASK_BUCKD_<br>POWER_NOT_GOOD_<br>STATUS | 1'b0    | 1'b1: Masks the status of 00h, bit[2] |

| 1    | R/W    | MASK_VIN_OVP_<br>STATUS                  | 1'b0    | 1'b1: Masks the status of 00h, bit[1] |

| 0    | R      | RESERVED                                 | N/A     | Reserved.                             |

#### MASK\_1 (0Ah)

#### Format: Unsigned binary

The MASK\_1 command masks buck x's output OV and over-current (OC) status.

| Bits | Access | Bit Name                 | Default | Description                           |

|------|--------|--------------------------|---------|---------------------------------------|

| 7    | R/W    | MASK_BUCKA_OV_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[7] |

| 6    | R/W    | MASK_BUCKB_OV_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[6] |

| 5    | R/W    | MASK_BUCKC_OV_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[5] |

| 4    | R/W    | MASK_BUCKD_OV_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[4] |

| 3    | R/W    | MASK_BUCKA_OC_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[3] |

| 2    | R/W    | MASK_BUCKB_OC_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[2] |

| 1    | R/W    | MASK_BUCKC_OC_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[1] |

| 0    | R      | MASK_BUCKD_OC_<br>STATUS | 1'b0    | 1'b1: Masks the status of 01h, bit[0] |

# **Threshold and Configuration Registers**

# REMOTE\_REG (0Bh)

Format: Unsigned binary

The REMOTE\_REG command sets buck x's remote sensing.

| Bits | Access | Bit Name        | Default | Description                                                                                       |

|------|--------|-----------------|---------|---------------------------------------------------------------------------------------------------|

| 7    | R/W    | BUCKA_REMOTE_EN | 1'b0    | Selects buck A's remote sensing.<br>1'b0: Disables remote sensing<br>1'b1: Enables remote sensing |

| 6    | R/W    | BUCKB_REMOTE_EN | 1'b0    | Selects buck's B remote sensing.<br>1'b0: Disables remote sensing<br>1'b1: Enables remote sensing |

| 5    | R/W    | BUCKC_REMOTE_EN | 1'b0    | Selects buck C's remote sensing.<br>1'b0: Disables remote sensing<br>1'b1: Enables remote sensing |

| 4:0  | R      | RESERVED        | N/A     | Reserved.                                                                                         |

# BUCKX\_CTRL\_REG (0Ch)

Format: Unsigned binary

The BUCKx\_CTRL\_REG command sets buck x's output regulator in pulse-frequency modulation (PFM) or pulse-width modulation (PWM) mode.

| Bits | Access | Bit Name  | Default | Description                                                                                  |

|------|--------|-----------|---------|----------------------------------------------------------------------------------------------|

| 7    | R/W    | BUCKA_EN  | 1'b1    | Enables buck A's output regulator.<br>1'b 0: Disabled<br>1'b 1: Enabled                      |

| 6    | R/W    | BUCKB_EN  | 1'b1    | Enables buck B's output regulator.<br>1'b0: Disabled<br>1'b1: Enabled                        |

| 5    | R/W    | BUCKC_EN  | 1'b1    | Enables buck C's output regulator.<br>1'b0: Disabled<br>1'b1: Enabled                        |

| 4    | R/W    | BUCKD_EN  | 1'b1    | Enables buck D's output regulator.<br>1'b0: Disabled<br>1'b1: Enabled                        |

| 3    | R/W    | PWM_BUCKA | 1'b0    | Sets buck A's automatic mode or forced PWM mode.<br>1'b0: Forced PWM<br>1'b1: Automatic mode |

| 2    | R/W    | PWM_BUCKB | 1'b0    | Sets buck B's automatic mode or forced PWM mode.<br>1'b0: Forced PWM<br>1'b1: Automatic mode |

| 1    | R/W    | PWM_BUCKC | 1'b0    | Sets buck C's automatic mode or forced PWM mode.<br>1'b0: Forced PWM<br>1'b1: Automatic mode |

|  | 0 | R/W | PWM_BUCKD | 1'b0 | Sets buck D's automatic mode or forced PWM mode.<br>1'b0: Forced PWM<br>1'b1: Automatic mode |

|--|---|-----|-----------|------|----------------------------------------------------------------------------------------------|

|--|---|-----|-----------|------|----------------------------------------------------------------------------------------------|

# PG\_REG (0Dh)

Format: Unsigned binary

The PG\_REG command sets buck x's power good (PG) threshold.

| Bits | Access | Bit Name   | Default | Description                                                 |

|------|--------|------------|---------|-------------------------------------------------------------|

| 7    | R      | RESERVED   | N/A     | Reserved.                                                   |

| 6    | R      | RESERVED   | N/A     | Reserved.                                                   |

| 5    | R      | RESERVED   | N/A     | Reserved.                                                   |

| 4    | R      | RESERVED   | N/A     | Reserved.                                                   |

| 3    | R/W    | PG_%_BUCKA | 1'b0    | Sets the PG threshold for buck A.<br>1'b0 = 5%              |

|      |        |            |         | 1'b1 = 7%                                                   |

| 2    | R/W    | PG_%_BUCKB | 1'b0    | Sets the PG threshold for buck B.<br>1'b0 = 5%<br>1'b1 = 7% |

| 1    | R/W    | PG_%_BUCKC | 1'b0    | Sets the PG threshold for buck C.<br>1'b0 = 5%<br>1'b1 = 7% |