# SR5E1E3, SR5E1E5, SR5E1E7

# Datasheet

SR5 E1 line of Stellar electrification MCUs — 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M7 automotive MCU 2x cores, 300 MHz, 2 MB flash, rich analog, 104 ps 24-ch high-resolution timer, HSM, and ASIL D

# **Features**

- AEC-Q100 automotive qualification on going

- going

- SR5 high-performance analog MCUs offering:

- Digital and analog high-frequency control requested by new widebandgap technologies (silicon carbide and gallium nitride)

- Superior real-time and functional safety performance (ASIL-D capability)

- Built-in fast and cost-optimized OTA (over-the-air) reprogramming capability (with built-in dual-image storage)

- High-speed security cryptographic services (HSM)

#### Cores

- 2× 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M7 with double-precision FPU, L1 cache and DSP instructions running at up to 300 MHz to reach 1284 DMIPS/2.14 DMIPS/MHz/ Core (Dhrystone 2.1)

- Split-lock configuration, allowing either 2 cores in parallel or 1 core in lockstep configuration

- 2 DMA engines in lockstep configuration

#### Memories

- Up to 2 MB on-chip flash memory with read while write support

- 1920 KB code flash memory split in two banks allowing 960 KB OTA reprogramming support

- 160 KB HSM dedicated code flash memory

- 96 KB data flash memory (64 KB + 32 KB dedicated to HSM)

- 488 KB on-chip general-purpose SRAM:

- 2× 32 KB instruction TCM + 2× 64 KB data TCM

- 256 KB system RAM

- 40 KB HSM dedicated system RAM

#### Security: hardware security module (HSM)

- On-chip high-performance security module with EVITA medium support with dedicated RAM and flash memory

- Based on Cortex<sup>®</sup>-M0+ core running at up to 150 MHz

- Hardware accelerator for symmetric cryptography

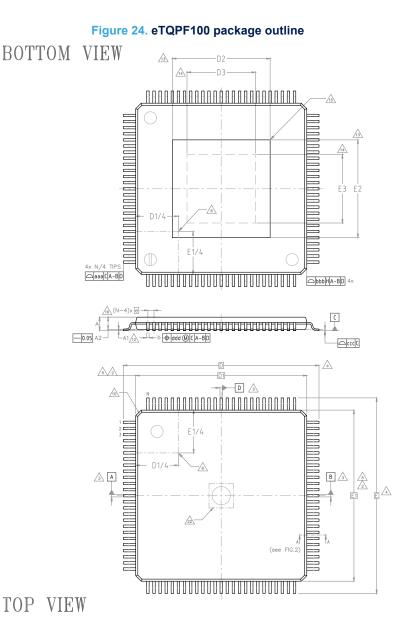

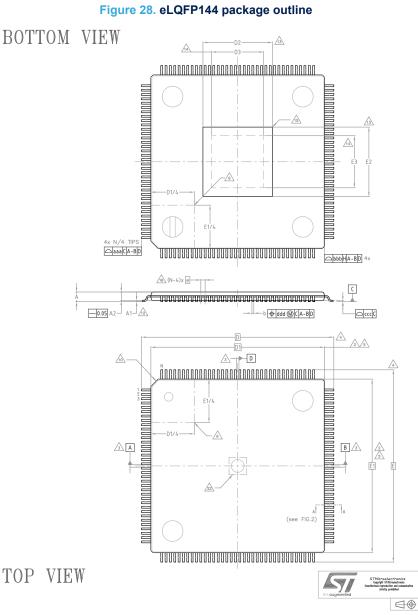

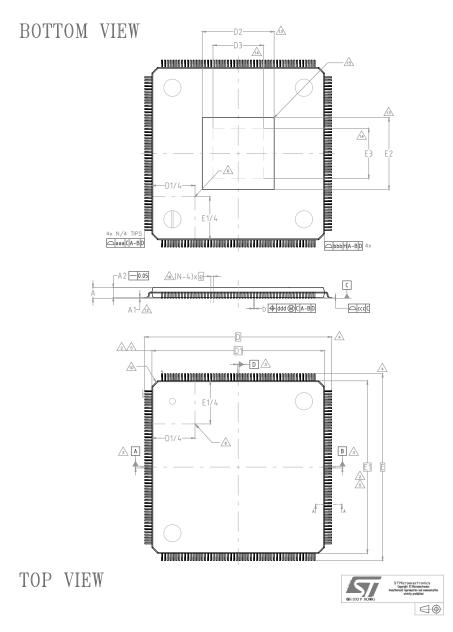

eTQFP100 (14 × 14 × 1.0 mm)

eTQFP144 (20 × 20 × 1.0 mm)

eLQFP176 (24 × 24 × 1.4 mm)

| Product s   | tatus link |

|-------------|------------|

| Part number | Package    |

| SR5E1E3     | eTQFP100   |

| SR5E1E5     | eTQFP144   |

| SR5E1E7     | eLQFP176   |

#### Safety: comprehensive new generation ASIL-D safety concept

- State of the art safety measures at all level of the architecture for most efficient implementation of ISO26262 ASIL-D functionalities

- FCCU for collection and reaction to failure notifications with enhanced configurability

- Memory error management unit (MEMU) for collection and reporting of error events in memories

- Cyclic redundancy check (CRC) unit

#### Enhanced peripherals for fast control loop capability

- 12 Timers:

- 2× HRTIM (high-resolution and complex waveform builder): 12× 16-bit counters, up to 102 ps resolution, 24 PWM in total

- 2× 16-bit 6-channel advanced control timers, with up to 12× PWM, in total

- 2× 32-bit general purpose timers, with up to 8× IC/OC/PWM or pulse counter and quadrature encoder input in total

- 4× 16-bit general purpose timers, with up to 11× PWM, 2 of which paired, in total

- 2× 16-bit basic timers

- Enhanced analog-to-digital converter system with:

- 5 separate 12-bit SAR analog converters, 8 channels each. Sampling rate up to 2.5 MSPS in single mode, 5 MSPS in dual mode

- 2 separate 16-bit sigma-delta analog converters

- 12-bit digital-to-analog converters (DAC)

- 2 buffered external channels 1 MSPS

- 8 unbuffered internal channels 15 MSPS

- 8 rail-to-rail analog comparators, 50 ns propagation delay

- Hardware accelerator

- 1× CORDIC for trigonometric functions acceleration

#### **Communication interfaces**

- 4 modular controller area network (MCAN) modules, all supporting flexible data rate (ISO CAN-FD)

- 3 UART modules with LIN functionality

- 4 serial peripheral interface (SPI) modules, 2 multiplexed with I<sup>2</sup>S interfaces

- 2 I<sup>2</sup>C modules

#### Advanced debug and trace for high-performance automotive application development

- Built around Arm<sup>®</sup> CoreSight<sup>™</sup>-600

- Debug interface: Arm<sup>®</sup> CoreSight<sup>™</sup> JTAG (IEEE 1149.1) or SWD

- 4 KB embedded trace FIFO for both on- and off-chip tracing

- Trace port for off-chip tracing: parallel trace port configurable from 1 to 8 data lines

#### Others

- Power efficiency management, through separate power modes for any selected cores, peripherals or memories

- Boot assist flash (BAF) supports factory programming using a serial loader through CAN or UART

- Junction temperature range -40 °C to 150 °C

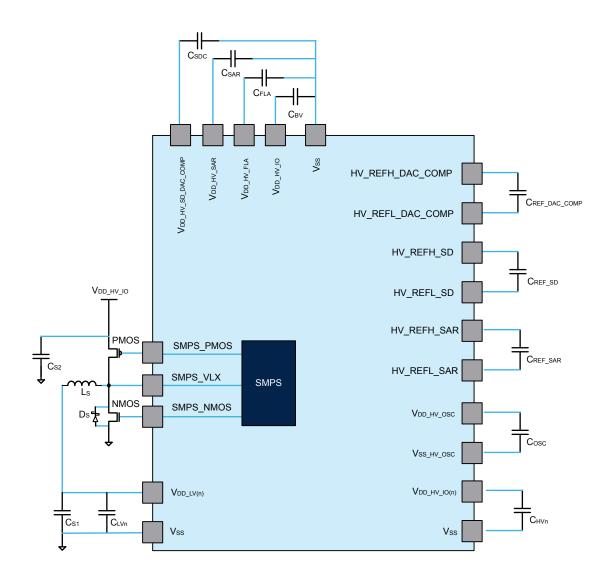

- Integrated power supply scheme:

- Integrated internal SMPS regulator

- 3.3 V supply & GPIOs

# 1 Introduction

## **1.1 Document overview**

This document provides electrical specifications, pin assignments, and package diagrams for the SR5E1E3, SR5E1E5, SR5E1E7 microcontroller units (MCUs). For functional characteristics, refer to the device reference manual. This device is a preliminary and superset implementation of family devices. Contact your local STMicroelectronics sales or marketing representative to receive the information on feature removal, improvement or addition, versus upcoming SR6 family devices.

*Note:* For information on the Cortex<sup>®</sup>-M7 and Cortex<sup>®</sup>-M0+ cores, refer to the technical reference manuals, available from the www.arm.com website.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

## 1.2 Description

The SR5E1E3, SR5E1E5, SR5E1E7 MCU family has been designed to meet the enhanced digital control and high-performance analog requested by the new wide bandgap power technologies, silicon carbide and GAN, from power conversion applications such as on-board charger and DC/DC converters as well as advanced motor control like traction inverter applications.

SR5E1E3, SR5E1E5, SR5E1E7 also offer superior real-time and safe performance with the highest ASIL-D capability, security cryptographic services (HSM) and high efficiency OTA reprogramming capability.

## **1.3 Device features**

The following table lists a summary of major features for the SR5E1E3, SR5E1E5, SR5E1E7. A detailed description of the functionality provided by each on-chip module is given later in this document.

| Feature                                           | Description                                                                                                                                                  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cores/memories                                    |                                                                                                                                                              |

| Cortex <sup>®</sup> -M7                           |                                                                                                                                                              |

| Number of cores/checker cores                     | 2 decoupled cores in split mode / 1 core with checker core in lock mode                                                                                      |

| Nominal frequency                                 | 300 MHz                                                                                                                                                      |

| Tightly coupled memory (TCM)                      | <ul><li>2× 32 KB instruction in split mode or 1× 64 KB instruction in lock mode</li><li>2× 64 KB data in split mode or 1× 128 KB data in lock mode</li></ul> |

| Floating-point unit                               | Single and double precision                                                                                                                                  |

| Cache                                             | 8 KB instruction (2 ways) for each core                                                                                                                      |

|                                                   | 16 KB data (4 ways) for each core                                                                                                                            |

| System memories                                   |                                                                                                                                                              |

| On-chip code flash memory                         | 2 MB                                                                                                                                                         |

| On-chip data flash memory                         | 64 KB                                                                                                                                                        |

| Built-in memory replication for OTA reprogramming | Up to 960 KB flash available                                                                                                                                 |

| System RAM                                        | 2× 128 KB (not including HSM dedicated RAM - see HSM)                                                                                                        |

| Others                                            |                                                                                                                                                              |

| Multichannel eDMA (paired in lockstep)            | 2 DMA engines, 8 streams each                                                                                                                                |

| Interrupt broadcasting system in lockstep         | Up to 190 sources                                                                                                                                            |

| Watchdogs                                         | 2 independent and 2 window watchdogs                                                                                                                         |

#### Table 1. Features list

Introduction

| Feature                                           | Description                                                                                                                               |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Security: hardware security module (HSM)          |                                                                                                                                           |

| Core                                              | Cortex <sup>®</sup> -M0 @ 150 MHz, as half device frequency.                                                                              |

|                                                   | Symmetric:                                                                                                                                |

| C3 cryptography engine                            | • AES-128/256, ECB, CBC, CMAC, GCM                                                                                                        |

| De l'acte d'Arch mennen                           | TRNG                                                                                                                                      |

| Dedicated flash memory                            | 160 KB                                                                                                                                    |

| Dedicated system RAM                              | 40 KB                                                                                                                                     |

| Dedicated data flash                              | 32 KB                                                                                                                                     |

| Peripheral, IOs                                   |                                                                                                                                           |

| Timer modules                                     |                                                                                                                                           |

| High-resolution timer                             | 2 modules, 6× 16-bit channels each, up to 102 ps resolution<br>Up to 24× PWM signals (or 12× paired)                                      |

|                                                   | 2 modules, 16-bit timer                                                                                                                   |

| Advance control timer                             | Up to 8 input capture, 12 output compare (8 of which paired)                                                                              |

|                                                   | 2 modules, 32-bit timer. Up to 8 input capture/output compare                                                                             |

| General purpose timer                             | 4 modules, 16-bit timer. Up to 11 input capture/output compare (2 of which paired)                                                        |

| Basic timer                                       | 2 modules, 16-bit timer                                                                                                                   |

| Enhanced analog-to-digital converter system       |                                                                                                                                           |

|                                                   | 5 modules, 8 channels each                                                                                                                |

| 12-bit SAR analog converters                      | Fast conversion, up to 2.5 MSPS in single mode, 5 MSPS in dual mode                                                                       |

|                                                   | 2 modules, 2 channels each (available only in eLQFP176 and eTQFP144 packages)                                                             |

| 16-bit sigma-delta analog converters              | Output conversion rate of 333 ksps (OSR = 24)                                                                                             |

| 12-bit analog comparators                         | 8 modules, rail-to-rail, 50 ns propagation delay                                                                                          |

| 12 hit digital to appled converters               | 2 buffered external channels, 1 MSPS                                                                                                      |

| 12-bit digital-to-analog convertors               | 8 unbuffered internal digital-to-analog channels, 15 MSPS                                                                                 |

| Hardware accelerator                              |                                                                                                                                           |

| CORDIC (for trigonometric functions acceleration) | 1 module                                                                                                                                  |

| Communication interfaces                          |                                                                                                                                           |

| UART modules (with LIN function)                  | 3                                                                                                                                         |

| MCAN supporting CAN-FD according to ISO 11898-1   | 4                                                                                                                                         |

| 2015                                              | CAN shared message RAM: 4 KB / MCAN (16 KB in total)                                                                                      |

| Serial peripheral interface (SPI)                 | 4                                                                                                                                         |

| I <sup>2</sup> C                                  | 2                                                                                                                                         |

| Software development/emulation features           |                                                                                                                                           |

| Arm <sup>®</sup> CoreSight <sup>™</sup> -600 libs | CoreSight <sup>™</sup> -600 libs for trace links, trace sink, and control components                                                      |

|                                                   | CoreSight <sup>™</sup> -400 libs for debug and trace source components                                                                    |

| Debug interfaces                                  | Arm <sup>®</sup> CoreSight <sup>™</sup> -600 compliant                                                                                    |

|                                                   | Debug port (JTAG+SWD)                                                                                                                     |

| Trace types                                       | Cortex <sup>®</sup> -M7 instruction and data trace                                                                                        |

| Off-chip trace                                    | Arm <sup>®</sup> CoreSight <sup>™</sup> parallel trace port (1 to 8 data lines, shared with user pins, not available in eTQFP100 package) |

| Advance cross-trigger and performance measurement | CoreSight <sup>™</sup> -600 CTI & CTM                                                                                                     |

Introduction

| Feature                 | Description                                                                                                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|

| Timestamp distribution  | Arm <sup>®</sup> CoreSight <sup>™</sup> timestamp generator                                                     |

| Security                | Arm <sup>®</sup> CoreSight <sup>™</sup> authentication                                                          |

| Security                | Password challenge with HSM                                                                                     |

|                         | External tool-host CPU mailbox                                                                                  |

| Debug controller        | Host-based debugging                                                                                            |

|                         | Debug-under-reset                                                                                               |

| Others                  |                                                                                                                 |

| Low power mode          | Clock gating management for selected cores, peripherals, and/or memories                                        |

| Low power mode          | Smart wake-up mechanisms through events or interrupts                                                           |

| Temperature sensor      | Yes                                                                                                             |

| Self-test controller    | Yes                                                                                                             |

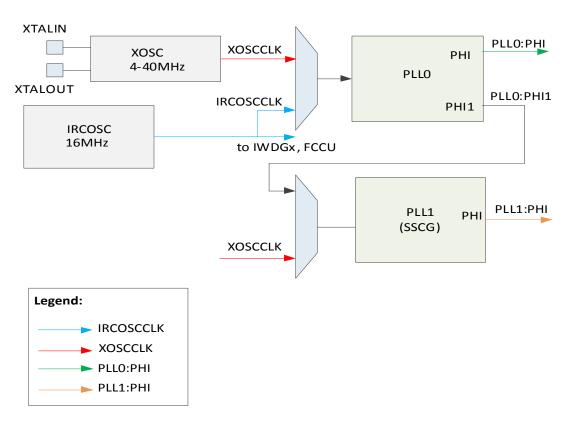

| PLL                     | 2 individual PLLs: 1 with a stable clock source for peripherals and 1 supporting frequency modulation for cores |

| Power supply            | Single internal SMPS regulator for 3.3 V supply and GPIOs                                                       |

| Boot assist flash (BAF) | Supports factory programming using a serial loader through the asynchronous CAN or UART                         |

| CRC channel(s)          | 1                                                                                                               |

## Table 2. SR5E1E3, SR5E1E5, SR5E1E7 product selector

| F                                          | eatures                       | SR5E1E3, SR5E1E5, SR5E1E7                |  |  |

|--------------------------------------------|-------------------------------|------------------------------------------|--|--|

| Corte                                      | x <sup>®</sup> -M7 cores      | 2 cores, either decoupled or in lockstep |  |  |

| Nominal fr                                 | requency in MHz               | 300                                      |  |  |

| Floati                                     | ng-point unit                 | Single and double precision              |  |  |

| Cache (instruction                         | n/data) per core in Kbyte     | 8 / 16                                   |  |  |

| Code flash in Mbyte                        | Overall included HSM in Mbyte | 2                                        |  |  |

| User cod                                   | e flash in Kbyte              | 1920                                     |  |  |

| HSM cod                                    | e NVM in Kbyte                | 160                                      |  |  |

| Code flash built-in memory replication for | Up to 2× 960                  |                                          |  |  |

|                                            | Overall included HSM          | 96                                       |  |  |

| Data flash in Kbyte                        | User data flash               | 64                                       |  |  |

|                                            | HSM data flash                | 32                                       |  |  |

|                                            | Overall                       | 488                                      |  |  |

| DAM in Khuta                               | TCM (instruction / data)      | 64 / 128                                 |  |  |

| RAM in Kbyte                               | User system RAM               | 256                                      |  |  |

|                                            | HSM system RAM                | 40                                       |  |  |

| Hardware sec                               | curity module (HSM)           | Yes                                      |  |  |

|                                            | Engine                        | 2                                        |  |  |

| DMA engines (number of channels)           | Channel                       | 2× 8                                     |  |  |

| Low power mode an                          | d smart wake-up schemes       | Yes                                      |  |  |

| LIN                                        | and UART                      | 3                                        |  |  |

| CAN (v                                     | vith CAN-FD)                  | 4                                        |  |  |

| SPI                                        |                               | 4                                        |  |  |

|                                            | Advanced control              | 2 (16-bit)                               |  |  |

|                                            | High-resolution               | 2 (16-bit)                               |  |  |

| Timers                                     | Conorel purpose               | 2 (32-bit)                               |  |  |

|                                            | General purpose               | 4 (16-bit)                               |  |  |

|                                            | Basic                         | 2 (16-bit)                               |  |  |

| 12-bit SAR                                 | analog converters             | 5                                        |  |  |

| 16-bit sigma-de                            | elta analog converters        | 2                                        |  |  |

| 12-bit analog compa                        | arators (with internal DAC)   | 8                                        |  |  |

| 12-bit                                     | external DAC                  | 2                                        |  |  |

| Debug port                                 | Main debug port (JTAG+SWD)    | Yes                                      |  |  |

| Debug port                                 | Secondary debug port (SWD)    | No                                       |  |  |

| Max temperature (target)                   | Ambient temperature           | 125 °C                                   |  |  |

| Junctio                                    | n temperature                 | 150 °C                                   |  |  |

|                                            | eTQFP100                      | х                                        |  |  |

| Packages                                   | eTQFP144                      | Х                                        |  |  |

|                                            | eLQFP176                      | Х                                        |  |  |

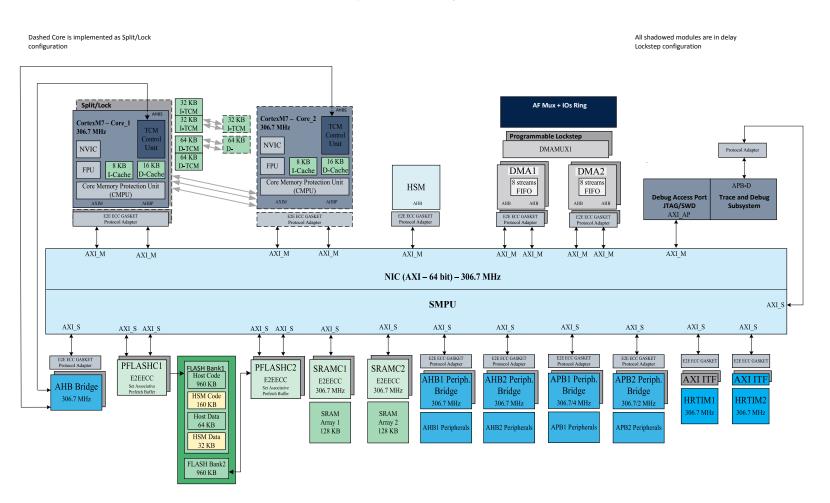

## 1.4 Block diagram

The figure below shows the top-level block diagram.

#### Figure 1. Block diagram

SR5E1E3, SR5E1E5, SR5E1E7 Introduction

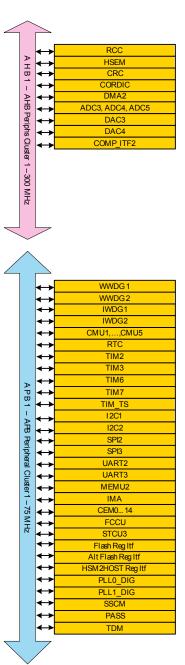

## The figure below shows the peripheral block diagram.

#### Figure 2. Peripheral allocation

| $\leq$ |                                           | $\geq$                                  |                                                                                                                                                                         |

|--------|-------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                           | $\leftrightarrow$                       | GPIOA                                                                                                                                                                   |

|        | ≥                                         | $\leftrightarrow$                       | GPIOB                                                                                                                                                                   |

|        | AHB2 -                                    | $\leftrightarrow$                       | GPIOC                                                                                                                                                                   |

|        | 2                                         | $\leftrightarrow$                       | GPIOD                                                                                                                                                                   |

|        | ⊳                                         | $\leftrightarrow$                       | GPIOE                                                                                                                                                                   |

|        | ΗB                                        | $\leftrightarrow$                       | GPIOF                                                                                                                                                                   |

|        | Per                                       | $\leftrightarrow$                       | GPIOG                                                                                                                                                                   |

|        | iph                                       | $\leftrightarrow$                       | GPIOH                                                                                                                                                                   |

|        | õ                                         | $\leftrightarrow$                       | GPIOI                                                                                                                                                                   |

|        | uste                                      | $\leftrightarrow$                       | DMA1                                                                                                                                                                    |

|        | Ň                                         | $\leftrightarrow$                       | DMAMUX1                                                                                                                                                                 |

|        | - 30                                      | $\leftrightarrow$                       | ADC1, ADC2                                                                                                                                                              |

|        | AHB Periphs Cluster 2 – 300 MHz           | $\leftrightarrow$                       | BDAC                                                                                                                                                                    |

|        | THI                                       | 4                                       | DAC1                                                                                                                                                                    |

|        |                                           | $\leftarrow$                            | DAC2                                                                                                                                                                    |

|        |                                           | $\leftarrow$                            | COMP ITF1                                                                                                                                                               |

| $\neg$ |                                           | Ś                                       |                                                                                                                                                                         |

|        |                                           |                                         |                                                                                                                                                                         |

|        |                                           |                                         | SYSCFG                                                                                                                                                                  |

|        |                                           | $\left( \right)$                        | SYSCFG<br>EXTI                                                                                                                                                          |

|        |                                           |                                         |                                                                                                                                                                         |

|        |                                           |                                         | EXTI                                                                                                                                                                    |

|        |                                           |                                         | EXTI<br>SMPU                                                                                                                                                            |

|        |                                           | 1                                       | EXTI<br>SMPU<br>PRAMC1                                                                                                                                                  |

|        |                                           | 1 1 1 1 1 1 1 1 1 1                     | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2                                                                                                                                        |

|        |                                           | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM                                                                                                        |

|        | AP                                        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2                                                                                                                    |

|        | A PB 2                                    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM                                                                                                        |

|        | A PB 2 -                                  | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM                                                                                            |

|        | A PB 2 – AP                               | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM<br>TIM4                                                                                    |

|        | APB2 – APBR                               |                                         | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM<br>TIM8_TM4<br>TIM5<br>TIM15<br>TIM15<br>TIM15                                             |

|        | A PB 2 – APB Perip                        | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM<br>TIM8_FWM<br>TIM4<br>TIM5<br>TIM15<br>TIM15<br>TIM16<br>SPI1                             |

|        | A PB 2 – APB Periphera                    | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM<br>TIM4<br>TIM5<br>TIM15<br>TIM15<br>TIM16<br>SPI1<br>SPI4                                 |

|        | A PB 2 – APB Peripheral Cl                | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM<br>TIM4<br>TIM5<br>TIM15<br>TIM15<br>TIM15<br>SPI1<br>SPI4<br>UART1                        |

|        | A PB 2 – APB Peripheral Cluste            | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM<br>TIM8_PWM<br>TIM5<br>TIM15<br>TIM15<br>TIM15<br>SPI1<br>SPI1<br>SPI4<br>UART1<br>SD_ADC1 |

|        | A PB 2 – AFB Peripheral Cluster 2         | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM4<br>TIM5<br>TIM5<br>TIM15<br>TIM15<br>SPI1<br>SPI4<br>UART1<br>SD_ADC1<br>SD_ADC2               |

|        | A PB 2 – APB Peripheral Cluster 2 – 150 M | 1                                       | EXTI<br>SMPU<br>PRAMC1<br>PRAMC2<br>NVMPC1<br>NVMPC2<br>TIM1_PWM<br>TIM8_PWM<br>TIM4<br>TIM5<br>TIM5<br>TIM5<br>TIM15<br>SPI1<br>SPI1<br>SPI4<br>UART1<br>SD_ADC1       |

SR5E1E3, SR5E1E5, SR5E1E7 Introduction

page 8/97

# 2 Package pinouts and signal descriptions

Refer to the SR5E1E3, SR5E1E5, SR5E1E7 IO definition technical note.

- Package pinouts

- Pin descriptions:

•

- Power supply and reference voltage pins

- System pins

- Generic pins

# **3 Electrical characteristics**

## 3.1 Introduction

The present document contains the target electrical specification for the 40 nm family 32-bit MCU SR5E1E3, SR5E1E5, SR5E1E7 products. Refer to the device reference manual for the details.

Note: This document provides target electrical specifications, based on previous designs, design simulations, or initial evaluation. Target electrical specification may not be guaranteed at this early stage of the product life cycle, however they are built to provide enough margin, ensuring production silicon meets customer requirements. Finalized specifications are published after completion of device characterization and device gualifications.

Parts described in this document are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" (controller characteristics) is included in the "Symbol" column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" (system requirement) is included in the "Symbol" column.

The electrical parameters shown in this document are classified by various methods. To give the customer a better understanding, the classifications listed in the table below are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are tested in production on each individual device.                                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table 3. Parameter classifications

# 3.2 Absolute maximum ratings

The table below describes the maximum ratings for the device. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

|                                |    |   |                                                                                                                                       |                                                         | Value |     |      | llmit |

|--------------------------------|----|---|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|-----|------|-------|

| Symbol                         |    | C | Parameter                                                                                                                             | Conditions                                              | Min   | Тур | Мах  | Unit  |

| V <sub>SS</sub>                | SR | D | Ground supply for the device. This is<br>covering both VSS_LV and VSS_HV for<br>the exposed pad device, unless specific<br>notations. | _                                                       | -0.3  | _   | 0.3  | V     |

| V <sub>DD_LV</sub>             | сс | D | Core voltage operating life range <sup>(1)</sup>                                                                                      |                                                         | -0.3  | _   | 1.45 | V     |

| V <sub>SS_HV_OSC</sub>         | SR | D | Ground supply for oscillator                                                                                                          | —                                                       | -0.3  | _   | 0.3  | V     |

| V <sub>DD_HV_OSC</sub>         | SR | D | High voltage power supply for oscillator                                                                                              | Reference to $V_{SS_HV_OSC}$                            | -0.3  | _   | 3.6  | V     |

| V <sub>DD_HV_IO</sub>          | SR | D | I/O supply voltage and high voltage<br>power supply for internal power<br>management unit <sup>(2)</sup>                              | Reference to $V_{\mbox{\scriptsize SS}}$                | -0.3  | _   | 3.8  | V     |

| V <sub>DD_HV_FLA</sub>         | SR | D | High voltage power supply for flash                                                                                                   | _                                                       | -0.3  | _   | 3.8  | V     |

| V <sub>DD_HV_SAR</sub>         | SR | D | SAR ADC supply voltage                                                                                                                | —                                                       | -0.3  | _   | 3.8  | V     |

| V <sub>DD_HV_SD_DAC_COMP</sub> | SR | D | High voltage power supply for SD ADC, DAC and comparator                                                                              | _                                                       | -0.3  | _   | 3.8  | V     |

| HV_REFL_SD                     | SR | D | SD ADC ground reference                                                                                                               | —                                                       | -0.3  | _   | 0.3  | V     |

| HV_REFH_SD                     | SR | D | SD ADC voltage reference                                                                                                              | Reference to HV_REFL_SD                                 | -0.3  | —   | 3.8  | V     |

| $HV_REFL_SD - V_{SS}$          | SR | D | SD ADC ground reference differential<br>voltage                                                                                       | _                                                       | -0.3  | _   | 0.3  | V     |

| HV_REFL_SAR                    | SR | D | SAR ADC ground reference and SAR<br>ADC analog ground                                                                                 | _                                                       | -0.3  | _   | 0.3  | V     |

| HV_REFH_SAR                    | SR | D | SAR ADC voltage reference                                                                                                             | Reference to HV_REFL_SAR                                | -0.3  | _   | 3.8  | V     |

| $HV\_REFL\_SAR - V_SS$         | SR | D | SAR ADC ground reference differential voltage                                                                                         | _                                                       | -0.3  |     | 0.3  | V     |

| HV_REFL_DAC_COMP               | SR | D | Ground reference for DAC and comparator                                                                                               | _                                                       | -0.3  | _   | 0.3  | V     |

| HV_REFH_DAC_COMP               | SR | D | Voltage reference for DAC and comparator                                                                                              | Reference to<br>HV_REFL_DAC_COMP                        | -0.3  |     | 3.8  | V     |

| $HV_REFL_DAC_COMP - V_{SS}$    | SR | D | DAC and comparator ground reference differential voltage                                                                              | _                                                       | -0.3  |     | 0.3  | V     |

| V <sub>IN</sub>                | SR | D | I/O input voltage range <sup>(3)(4)</sup>                                                                                             | Relative to V <sub>ss</sub>                             | -0.3  | _   | 3.8  | V     |

| T <sub>TRIN</sub>              | SR | D | Digital input pad transition time <sup>(5)</sup>                                                                                      |                                                         | —     | _   | TBD  | ms    |

| I <sub>INJ</sub>               | SR | т | Maximum DC injection current for each analog/digital PAD <sup>(6)</sup>                                                               |                                                         | -5    | _   | 5    | mA    |

| T <sub>STG</sub>               | SR | D | Maximum non-operating Storage temperature range                                                                                       |                                                         | -55   | _   | 125  | °C    |

| T <sub>STORAGE</sub>           | SR | D | Maximum storage time, assembled part programmed in ECU                                                                                | No supply; storage temperature in range -40 °C to 60 °C | _     | _   | 20   | years |

| T <sub>SDR</sub>               | SR | т | Maximum solder temperature Pb-free packaged <sup>(7)</sup>                                                                            | _                                                       |       |     | 260  | °C    |

| MSL                            | SR | Т | Moisture sensitivity level <sup>(8)</sup>                                                                                             |                                                         | _     | _   | 3    | _     |

#### Table 4. Absolute maximum ratings

**Electrical characteristics**

|  | Symbol                 |    | с | Parameter                   | Conditions                                                                      | Value |     |     | Unit |

|--|------------------------|----|---|-----------------------------|---------------------------------------------------------------------------------|-------|-----|-----|------|

|  |                        |    |   | Falallelei                  | Conditions                                                                      | Min   | Тур | Max |      |

|  | T <sub>XRAY</sub> dose | SR | т | Maximum cumulated XRAY dose | Typical range for X-rays source<br>during inspection:80 - 130 KV; 20<br>- 50 μA | _     | _   | 1   | gray |

V<sub>DD\_LV</sub>: allowed 1.36 V - 1.45 V for 60 seconds cumulative time at the given temperature profile. Remaining time allowed 1.345 V - 1.36 V for 10 hours cumulative time at the given temperature profile. Remaining time as defined in Section 3.3: Operating conditions.

- 2. V<sub>DD\_HV\_IO</sub>: allowed 3.45 V 3.8 V for 60 seconds cumulative time at the given temperature profile, for 10 hours cumulative time with the device in reset at the given temperature profile. Remaining time as defined in Section 3.3: Operating conditions.

- 3. The maximum input voltage on an I/O pin tracks with the associated I/O supply maximum. For the injection current condition on a pin, the voltage is equal to the supply plus the voltage drop across the internal ESD diode from I/O pin to supply. The diode voltage varies greatly across process and temperature, but a value of 0.3 V can be used for nominal calculations.

- 4. Relative value can be exceeded if design measures are taken to ensure injection current limitation (parameter INJ).

- 5. This limitation applies to pads with digital input buffer enabled. If the digital input buffer is disabled, there are no maximum limits to the transition time.

- 6. The limits for the sum of all normal and injected currents on all pads within the same supply segment can be found in Section 3.8.3: I/O pad current specifications.

- 7. Solder profile per IPC/JEDEC J-STD-020D.

- 8. Moisture sensitivity per JDEC test method A112.

#### — Related links -

3.3 Operating conditions on page 12

3.8.3 I/O pad current specifications on page 24

3.8.1 I/O input DC characteristics on page 18

3.12.1 ADC input description on page 35

3.12.2 SARADC 12-bit electrical specification on page 36

## 3.3 Operating conditions

The table below describes the operating conditions for the device, and for which all the specifications in the data sheet are valid, except where explicitly noted. The device operating conditions must not be exceeded or the functionality of the device is not guaranteed.

#### Table 5. Operating conditions

| $\mathbf{C}_{i}$ and $\mathbf{C}_{i}$ |    | с | Devementer                                                                               | Conditions             |                      | Unit  |                      |      |  |

|---------------------------------------|----|---|------------------------------------------------------------------------------------------|------------------------|----------------------|-------|----------------------|------|--|

| Symbol <sup>(1)</sup>                 |    |   | Parameter                                                                                | Conditions             | Min                  | Тур   | Мах                  | Unit |  |

| F <sub>SYS</sub>                      | SR | Ρ | Operating system clock frequency <sup>(2)</sup>                                          | -                      | _                    | _     | 306.7                | MHz  |  |

| TJ                                    | SR | Ρ | Operating Junction temperature                                                           | High temperature range | -40                  | _     | 150                  | °C   |  |

| T <sub>A</sub>                        | SR | Ρ | Operating Ambient temperature                                                            |                        | -40                  | —     | 125                  | °C   |  |

| V <sub>DD_LV</sub>                    | CC | D | Core supply voltage <sup>(3)</sup>                                                       | _                      | 1.225 <sup>(4)</sup> | 1.285 | 1.345 <sup>(5)</sup> | V    |  |

| V <sub>SS_HV_OSC</sub>                | SR | С | Ground supply for oscillator                                                             | _                      | -0.3                 | —     | 0.3                  | V    |  |

| V <sub>DD_HV_OSC</sub>                | SR | С | High voltage supply for oscillator                                                       |                        | 3.15 <sup>(6)</sup>  | —     | 3.45                 | V    |  |

| V <sub>DD_HV_IO</sub>                 | SR | Ρ | IO supply voltage and high<br>voltage power supply for internal<br>power management unit | _                      | 3.15 <sup>(6)</sup>  | _     | 3.45 <sup>(7)</sup>  | V    |  |

| V <sub>DD_HV_SAR</sub>                | SR | Ρ | SAR ADC supply voltage                                                                   | _                      | 3.15 <sup>(6)</sup>  | —     | 3.45 <sup>(7)</sup>  | V    |  |

| V <sub>DD_HV_SD_DAC_COMP</sub>        | SR | Ρ | High voltage power supply for SD ADC, DAC and comparator                                 | _                      | 3.15 <sup>(6)</sup>  |       | 3.45 <sup>(7)</sup>  | V    |  |

**Electrical characteristics**

| <b>O</b> :                                     |    | с |                                                                                                       | Constitution of                  |                     | Unit |                       |      |  |

|------------------------------------------------|----|---|-------------------------------------------------------------------------------------------------------|----------------------------------|---------------------|------|-----------------------|------|--|

| Symbol <sup>(1)</sup>                          |    | C | Parameter                                                                                             | Conditions                       | Min                 | Тур  | Мах                   |      |  |

| V <sub>DD_HV_FLA</sub>                         | SR | Р | High voltage power supply for<br>flash                                                                | _                                | 3.15 <sup>(6)</sup> | _    | 3.45 <sup>(7)</sup>   | V    |  |

| HV_REFH_SD                                     | SR | Р | SD ADC supply reference voltage <sup>(8)</sup>                                                        |                                  | 2.9                 | _    | 3.45                  | v    |  |

| HV_REFH_SD -<br>V <sub>DD_HV_SD_DAC_COMP</sub> | SR | D | SD ADC reference differential voltage                                                                 | _                                | _                   | _    | 0 (Not<br>allowed)    | mV   |  |

| HV_REFL_SD                                     | SR | Р | SD ADC ground reference voltage                                                                       |                                  | _                   | 0    |                       | V    |  |

| HV_REFL_SD - V <sub>SS</sub>                   | SR | D | SD ADC ground differential voltage                                                                    | _                                | -25                 | _    | 25                    | mV   |  |

| HV_REFH_SAR                                    | SR | Р | SAR ADC supply reference voltage <sup>(9)</sup>                                                       |                                  | 2.7                 | _    | 3.45                  | V    |  |

| HV_REFH_SAR -<br>V <sub>DD_HV_SAR</sub>        | SR | D | SAR ADC reference differential voltage                                                                |                                  | _                   | _    | 0 (Not<br>allowed)    | mV   |  |

| HV_REFL_SAR                                    | SR | Р | SAR ADC ground reference voltage and SAR ADC analog ground                                            |                                  | 0                   | _    | 0.1                   | V    |  |

| HV_REFL_SAR - V <sub>SS</sub>                  | SR | D | SAR ADC ground differential voltage                                                                   |                                  | -25                 | _    | 25                    | mV   |  |

| HV_REFL_DAC_COMP                               | SR | Р | Ground reference for DAC and comparator                                                               |                                  | _                   | 0    |                       | V    |  |

| HV_REFH_DAC_COMP                               | SR | Р | Voltage reference for DAC and comparator                                                              | Reference to<br>HV_REFL_DAC_COMP | 3.0                 | _    | 3.45                  | V    |  |

| HV_REFL_DAC_COMP -<br>V <sub>SS</sub>          | SR | D | DAC and comparator ground reference differential voltage                                              |                                  | -25                 | _    | 25                    | mV   |  |

| V <sub>RAMP_HV</sub>                           | SR | D | Slew rate on HV power supply                                                                          |                                  | 33                  | _    | 100                   | V/ms |  |

| V <sub>IN</sub>                                | SR | Р | I/O input voltage range and high voltage power supply for internal power management unit              | _                                | 0                   | _    | V <sub>DD_HV_IO</sub> | v    |  |

| I <sub>INJ1</sub>                              | SR | т | Injection current (per pin) without<br>performance degradation <sup>(10)(11)</sup><br><sup>(12)</sup> | Digital pins and analog pins     | -3                  | _    | 3                     | mA   |  |

| I <sub>INJ2</sub>                              | SR | D | Dynamic injection current (per<br>pin) with performance<br>degradation <sup>(10)(13)</sup>            | Digital pins and analog pins     | -10                 | _    | 10                    | mA   |  |

1. The ranges in this table are design targets and actual data may vary in the given range.

2. Maximum operating frequency is applicable to the cores and platform of the device. Refer to the device reference manual, Clocking chapter, for more information on the clock limitations for the various IP blocks on the device.

- 3. Core voltage is measured on device pin to guarantee published silicon performance. This value is provided as information, but it is controlled internally by PMU. External low voltage supply is not supported in functional mode.

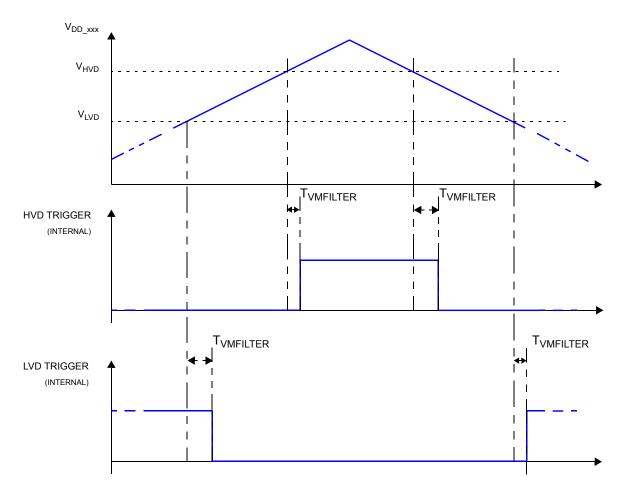

- 4. In the range [1.265-1.225] V the device functionality and specifications are guaranteed, but this interval is to be considered as a transient, in accordance with the mission profile, to guarantee the product reliability and to reduce the false LVD triggers recurrence. In the range [1.225-1.19] V, the device functionality is granted and the device is expected to receive a flag by the internal LVD119 monitors to warn that the regulator providing the VDD\_LV supply, exited the expected operating conditions. If the internal LVD119 monitors are disabled by the application, then an external voltage monitor with minimum threshold of V<sub>DD\_LV</sub>(min) = 1.19 V measured at the device pad, has to be implemented. Refer to Section 3.13.3: Voltage monitors for the list of available internal monitors and to the device reference manual for the configurability of the monitors.

- 5. In the range [1.31-1.345] V the device functionality and specifications are guaranteed, but this interval is to be considered as a transient, in accordance with the mission profile, to guarantee the product reliability and to reduce the false HVD triggers recurrence. In the range [1.345-1.4] V the device functionality is granted and the device is expected to receive a flag by the internal HVD140 monitors to warn that the regulator providing the V<sub>DD\_LV</sub> supply, exited the expected operating conditions. Refer to Section 3.13.3: Voltage monitors for the list of available internal monitors and to the device reference manual for the configurability of the monitors. Possible permanent failure over 1.4 V.

- 6. In the range [3.02-3.15] V, the device functionality and specifications are guaranteed, but this interval is to be considered as a transient, in accordance with the mission profile, to guarantee the product reliability and to reduce the false LVD triggers recurrence. In the range [3.012-2.898] the device functionality and specifications are granted and the device is expected to receive a flag by the internal LVD290 monitors. Refer to Section 3.13.3: Voltage monitors for the list of available internal monitors and to the Reference Manual for the configurability of the monitors.

- 7. In the range [3.45-3.65]V, the device functionality and specifications are guaranteed, but this interval is to be considered as a transient, in accordance with the mission profile, to guarantee the product reliability and to reduce the false UVD triggers recurrence. In the range [3.651-3.799] the device functionality and specifications are granted and the device is expected to receive a flag by the internal UVD380 monitors. Refer to Section 3.13.3: Voltage monitors for the list of available internal monitors and to the Reference Manual for the configurability of the monitors.

- 8. To be always ensured  $V_{DD_HV_SD_DAC_COMP} \ge HV_REFH_SD$ .

- 9. To be always ensured  $V_{DD_HV_SAR} \ge HV_REFH_SAR$ .

- 10. The limits for the sum of all normal and injected currents on all pads within the same supply segment can be found in Section 3.8.3: I/O pad current specifications.

- 11. The I/O pins on the device are clamped to the I/O supply rails for ESD protection. When the voltage of the input pins is above the supply rail, current is injected through the clamp diode to the supply rails. For external RC network calculation, assume typical 0.3 V drop across the active diode. The diode voltage drop varies with temperature.

- 12. Full device lifetime. I/O and analog input specifications are only valid if the injection current on adjacent pins is within these limits. Refer to Section 3.2: Absolute maximum ratings for maximum input current for reliability requirements.

- 13. Positive and negative dynamic current injection pulses are allowed up to this limit, with different specifications for I/O, ADC accuracy and analog input. Refer to the dedicated chapters for the different specification limits. See the Table 4. Absolute maximum ratings for maximum input current for reliability requirements. Refer to the following pulses definitions: Pulse1 (ISO 7637-2:2011), Pulse 2a(ISO 7637-2:2011 5.6.2), Pulse 3a (ISO 7637-2:2011 5.6.3), Pulse 3b (ISO 7637-2:2011 5.6.3).

#### Table 6. TCM wait states configuration

| Symbol               |    | C Parameter |                                      | Conditions | Value |     |     | Unit |

|----------------------|----|-------------|--------------------------------------|------------|-------|-----|-----|------|

|                      |    |             |                                      | Conditions | Min   | Тур | Мах | Unit |

| Core ITCM waitstates | СС | D           | ITCM access wait state from own core | _          |       | 0   |     | WS   |

| Core DTCM waitstates | СС | D           | DTCM access wait state from own core |            | 0     |     | WS  |      |

#### Table 7. PRAM wait states configuration

| Symbol            |    |   | Parameter                        | Conditions           |     | Unit |   |    |

|-------------------|----|---|----------------------------------|----------------------|-----|------|---|----|

| Symbol            |    |   | r al allietei                    | Conditions Min Typ M | Мах |      |   |    |

| PRAMC MEMACC_WAIT | SR | D | System RAM read/write wait state | —                    | 0   | 0    | 0 | WS |

#### — Related links –

3.2 Absolute maximum ratings on page 11

3.8.3 I/O pad current specifications on page 24

3.12.1 ADC input description on page 35

3.13.3 Voltage monitors on page 56

#### 3.3.1 Power domains and power up/down sequencing

The following table shows the constraints and relationships for the different power domains. Supply1 (on rows) can exceed Supply2 (on columns), only if the cell at the given row and column is reporting 'ok'. This limitation is valid during power-up and power-down phases, as well as during normal device operation.

#### Table 8. Device supply relation during power-up/power-down sequence

|         |                        |                |            |            | Sup            | ply2               |             |            |                  |

|---------|------------------------|----------------|------------|------------|----------------|--------------------|-------------|------------|------------------|

|         |                        | V_bHv_lo       | VpD_HV_osc | Vdd_hv_fla | Vdd_hv_sar     | Vdd_Hv_sd_dac_comp | HV_REFH_SAR | HV_REFH_SD | HV_REFH_DAC_COMP |

|         | V <sub>DD_HV_IO</sub>  |                | ОК         | ОК         | ОК             | ОК                 | ОК          | ОК         | ОК               |

|         | V <sub>DD_HV_OSC</sub> | OK             |            | ОК         | ОК             | ОК                 | ОК          | ОК         | OK               |

|         | V <sub>DD_HV_FLA</sub> | ОК             | OK         |            | ОК             | ОК                 | ОК          | ОК         | OK               |

|         | V <sub>DD_HV_SAR</sub> | ОК             | OK         | ОК         |                | ОК                 | ОК          | ОК         | OK               |

| Supply1 | VDD_HV_SD_DAC_COMP     | Not<br>allowed | ОК         | ОК         | ОК             |                    | ОК          | ОК         | ОК               |

|         | HV_REFH_SAR            | ОК             | ОК         | ОК         | Not<br>allowed | ОК                 |             | ОК         | ОК               |

|         | HV_REFH_SD             | Not<br>allowed | ОК         | ОК         | ОК             | Not<br>allowed     | ОК          |            | ОК               |

|         | HV_REFH_DAC_COMP       | ОК             | ОК         | ОК         | ОК             | Not<br>allowed     | ОК          | ОК         |                  |

During power-up, all functional terminals are maintained in a known state as described in the device pinout Excel file attached to the SR5E1E3, SR5E1E5, SR5E1E7 IO definition technical note.

## **3.4 Electrostatic discharge (ESD)**

The following table describes the ESD ratings of the device.

#### Table 9. ESD ratings

| Symbol  |    | C | Parameter <sup>(1)(2)</sup>                                      | Conditions       |     | Unit |                                                                  |      |

|---------|----|---|------------------------------------------------------------------|------------------|-----|------|------------------------------------------------------------------|------|

| Symbol  |    | Č |                                                                  | Conditions       | Min | Тур  | Мах                                                              | Onit |

| ESD_HBM | SR | Т | ESD for human body model (HBM) <sup>(3)</sup>                    | All pins         | —   | —    | 2000                                                             | V    |

| ESD CDM | SR | Т | ESD for field induced observed device model (CDM) <sup>(4)</sup> | All terminals    | _   |      | 500                                                              | V    |

|         | SR | Т | ESD for field induced charged device model (CDM) <sup>(4)</sup>  | Corner terminals | _   | _    | Typ         Max           —         2000           —         500 | V    |

1. Device failure is defined as: "If after exposure to ESD pulses, the device does not meet the device specification requirements, which includes the complete DC parametric and functional testing at room temperature and hot temperature. Maximum DC parametrics variation within 10% of maximum specification".

2. All ESD testing is in conformity with CDF-AEC-Q100 stress test qualification for automotive grade integrated circuits.

3. This parameter tested in conformity with ANSI/ESD STM5.1-2007 electrostatic discharge sensitivity testing.

4. This parameter tested in conformity with ANSI/ESD STM5.3-1990 charged device model - component level.

## 3.5 Electromagnetic emission characteristics

EMC measurements at integrated circuit level IEC standards can be requested to STMicroelectronics.

300 MHz nominal frequency is not suggested as operative frequency due to possible EMC emission in the GNSS band. Suggested operative (max) frequency is 306.7 MHz, refer to Reference Manual "Clock tree" and PLLs divider registers (PLL0DV and PLL1DV).

## 3.6 Temperature profile

The device is qualified in accordance to AEC-Q100 Grade1 and customers' requirements.

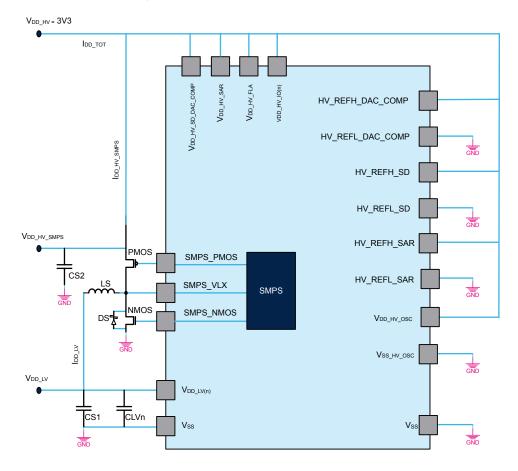

## 3.7 Device consumption

The total device consumption seen from the HV domain is the sum of the total dynamic current on the high voltage supply and the leakage current seen on the high voltage domain (from LV domain through SMPS) for the selected temperature. So, it is:  $I_{TOT} = I_{DD_HV} + I_{DD_HV_SMPS_LKG}$ .

The following table reports each single contributor factor to the device consumption.

Refer to Figure 3. Device consumption measurement to see where each contributor is measured.

| Symbol <sup>(1)</sup>                 |                         | _            | Parameter                                                      | Conditions                                                         | Value |     |     | Unit |

|---------------------------------------|-------------------------|--------------|----------------------------------------------------------------|--------------------------------------------------------------------|-------|-----|-----|------|

| Symbol                                |                         |              |                                                                | Conditions                                                         | Min   | Тур | Max | Unit |

|                                       |                         |              | High voltage domain (V <sub>DD</sub> _                         | HV)                                                                |       |     |     |      |

|                                       | I <sub>DD_HV</sub> CC - |              | Total dynamic current on a high voltage supply                 | Motor control application profile <sup>(3)</sup><br>Freq = 300 MHz | _     | 105 | 150 | mA   |

| UD_HV                                 | CC                      | Ρ            | (V <sub>DD_HV</sub> )                                          | Full case profile <sup>(4)</sup><br>Freq = 300 MHz                 |       | 150 | 205 | mA   |

| I                                     | сс                      | С            | Leakage current is seen on the high voltage domain             | Tamb = 25 °C                                                       | _     | 10  | 40  | m۸   |

| DD_HV_SMPS_LKG                        |                         | Ρ            | (from LV domain through SMPS)                                  | Tamb = 125 °C                                                      | _     | 105 | 430 | mA   |

| 1                                     | сс                      | Ρ            |                                                                | Motor control application profile <sup>(3)</sup><br>Freq = 300 MHz | _     | 90  | 145 | mA   |

| IDD_HV_SMPS                           |                         | Ρ            | Dynamic current on external MOSFETs                            | Full case profile <sup>(4)</sup><br>Freq = 300 MHz                 | _     | 125 | 190 | mA   |

|                                       |                         |              | Low voltage domain (V <sub>DD</sub> _                          | Lv)                                                                |       | 1   |     |      |

| <b>1</b> · · · - (2)(5)               | сс                      | С            | Leakage current on digital supply (V <sub>DD LV</sub> )        | Tamb = 25 °C                                                       | —     | 21  | 80  | mA   |

| I <sub>DD_LKG</sub> <sup>(2)(5)</sup> |                         | Ρ            |                                                                | Tamb = 125 °C                                                      | _     | 170 | 750 | mA   |

| . (5)                                 | сс                      | T<br>Dy<br>T | Dynamic current on digital supply (V <sub>DD LV</sub> )        | Motor control application profile <sup>(3)</sup><br>Freq = 300 MHz | _     | 205 | 240 | mA   |

| I <sub>DD_LV</sub> <sup>(5)</sup>     |                         | т            |                                                                | Full case profile <sup>(4)</sup><br>Freq = 300 MHz                 | _     | 270 | 310 | mA   |

| I <sub>DD_MAIN_m7</sub>               | сс                      | т            | Main core dynamic current                                      | Motor control application based <sup>(6)</sup><br>Freq = 300 MHz   | _     | 42  | 48  | mA   |

| IDD_MAIN_Csleep                       | сс                      | т            | Dynamic current reduction with main core in CSleep             | Full case profile <sup>(7)</sup><br>Freq = 300 MHz                 | _     | 4   | 8   | mA   |

| I <sub>SPIKE</sub>                    | СС                      | Т            | Maximum short term current spike                               | < 20 µs observation window                                         | _     | _   | 100 | mA   |

| dl                                    | SR                      | D            | Current difference ratio to average current (dl/avg(l))        | 20 µs observation window                                           | _     | _   | 20  | %    |

| I <sub>SR</sub> <sup>(8)</sup>        | сс                      | D            | Current variation during power up/down                         | Refer to footnote <sup>(9)</sup>                                   | _     | _   | 200 | mA   |

| IDDOFF                                | СС                      | Т            | Power-off current on high voltage supply rails <sup>(10)</sup> | V <sub>DD_HV</sub> = 2.5 V                                         | 100   | _   | _   | μA   |

#### Table 10. Device consumption

1. The ranges in this table are design targets and actual data may vary in the given range.

- 2. The leakage considered is the sum of core logic and RAM memories. The contribution of analog modules is not considered, and they are computed in the dynamic I<sub>DD\_LV</sub> and I<sub>DD\_HV</sub> parameters.

- Motor control application configured to drive single field-oriented control (FOC) 3-phase permanent magnet motors with ICS topology power stage (in open-loop). Position sensors used are encoder and sensor-less algorithms. IPs involved: Single core, 2× ADC channels, 6× timer channels (PWM generation), 2× timer channels (encoder), UART, DAC, CORDIC, GPIOs.

- Full case profile 2× M7 cores in lockstep. IPs involved: 5× SARADCs, 2× SDADCs, COMPs, 6× timer channels (PWM generation), 24× HRTIM channels (PWM generation), UART, DAC, CORDIC, 2× SPIs, CAN, GPIOs.

- 5. I<sub>DD\_LKG</sub> (leakage current) and I<sub>DD\_LV</sub> (dynamic current) are reported as separate parameters, to give an indication of the consumption contributors. The tests used in validation, characterization and production are verifying that the total consumption (leakage+dynamic) is lower than or equal to the sum of the maximum values provided (I<sub>DD\_LKG</sub> + I<sub>DD\_LV</sub>). The two parameters, measured separately, may exceed the maximum reported for each, depending on the operative conditions and the software profile used.

- 6. Main core dynamic consumption contribution based on motor control profile. Dedicated I/D-caches and I/D-TCMs contribution are not included.

- 7. Dynamic current reduction with the main core in CSleep, based on the full case profile.

- 8. This specification is the maximum value and is a boundary for the dl specification.

- 9. Condition 1: for power, on period from 0 V up to normal operation with reset asserted. Condition 2: from reset asserting until PLL running free. Condition 3: increasing PLL from free frequency to full frequency. Condition 4: reverse order for power down to 0 V.

- 10. IDDOFF is the minimum ensured consumption of the device during power-up.

#### Figure 3. Device consumption measurement

# 3.8 I/O pad specification

The following table describes the different pad type configurations.

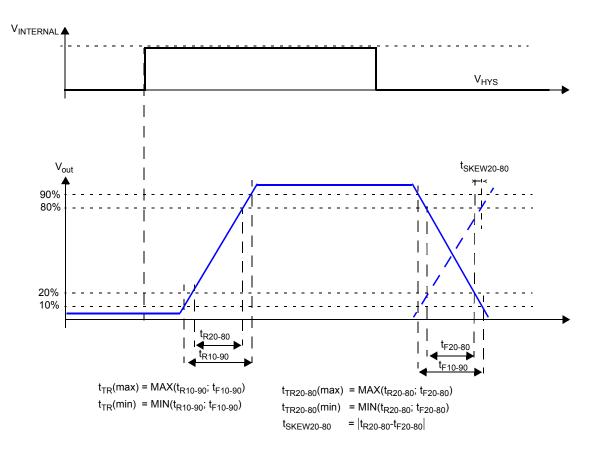

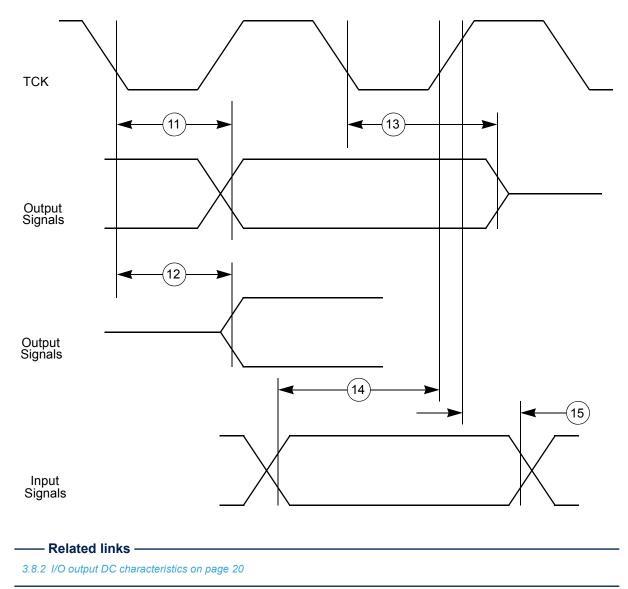

| Pad type                | Description                                                                                                                                                             |