# STGAP4S

Datasheet

# Automotive advanced isolated gate driver for IGBTs and SiC MOSFETs

STGAP4S

## Features

- AEC-Q100 qualified

- High voltage rail up to 1200 V

- Two output pins for direct driving of external MOSFET buffer

- Driver current capability:

- OUT1: 0.6/2.5 A sink/source

- OUT2: 2.4/0.6 A sink/source

- Negative gate drive ability

- dV/dt transient immunity ±100 V/ns in full temperature range

- Integrated controller for isolated flyback power supply

- Active Miller clamp driver for external N-channel MOSFET

- Programmable Desaturation detection

- Programmable Overcurrent detection

- Soft turn-off

- V<sub>CE</sub> active clamp

- Two diagnostic status outputs

- Programmable UVLO and OVLO on each supply

- Programmable input deglitch filter

- Asynchronous stop command

- Isolated 8-bit A/D converter

- Integrated temperature sensor

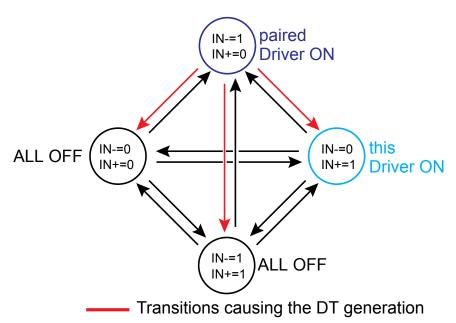

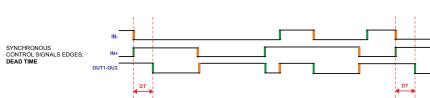

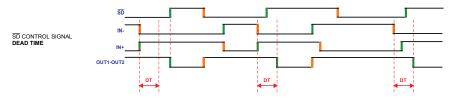

- Programmable deadtime, with violation error

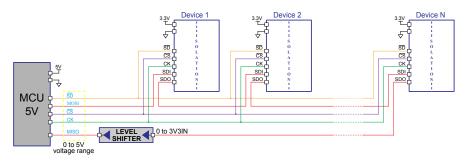

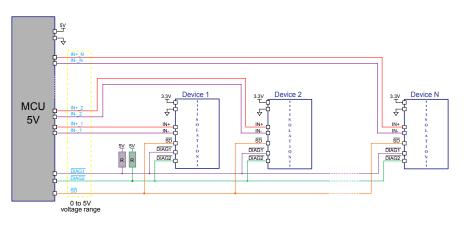

- SPI interface for parameters programming and extended diagnostic

- Temperature warning and shutdown protection

- Self-diagnostic routines for protection features

## **Applications**

- Inverters for EV/HEV

- 600/1200 V industrial inverters

- EV charging stations

- UPS equipment

- AC/AC converters

- DC/DC converters

- Solar inverters

## Description

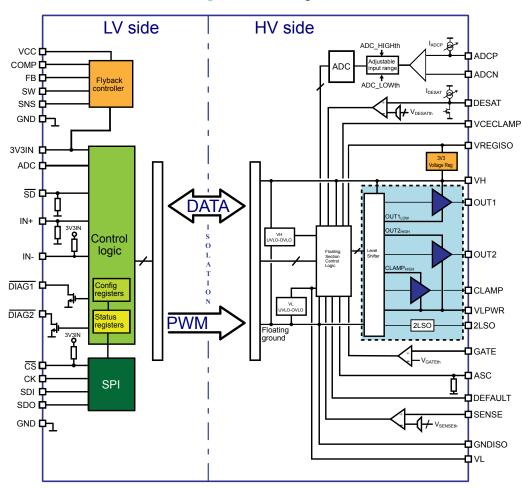

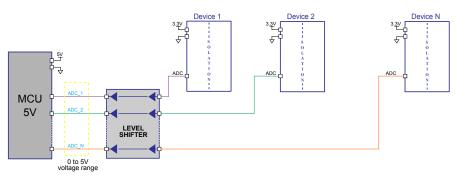

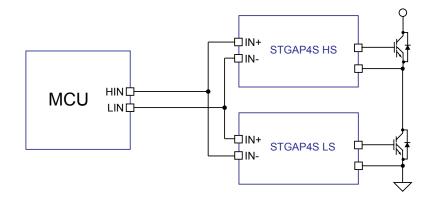

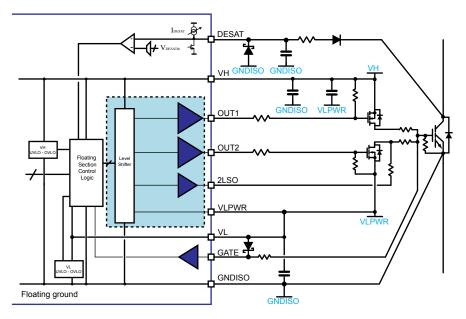

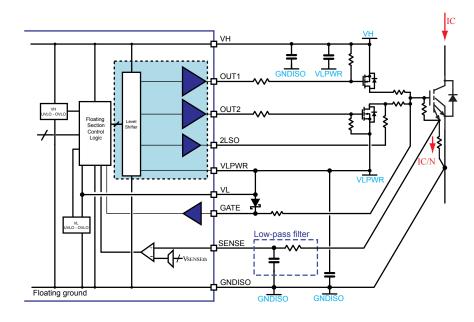

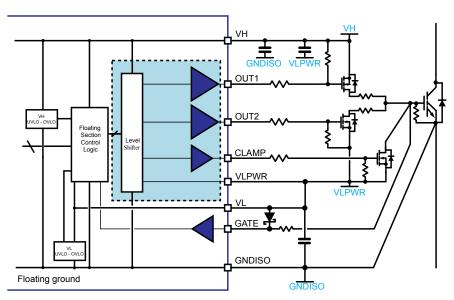

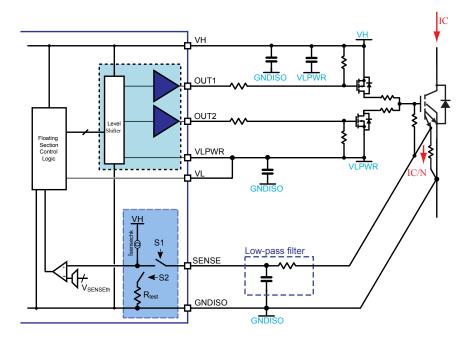

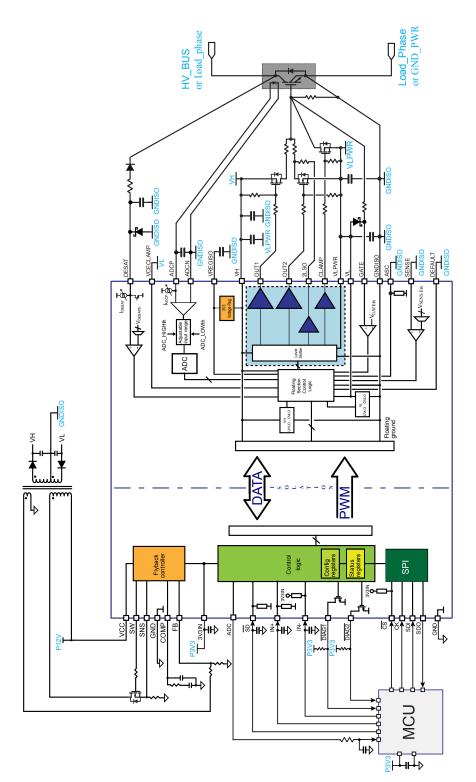

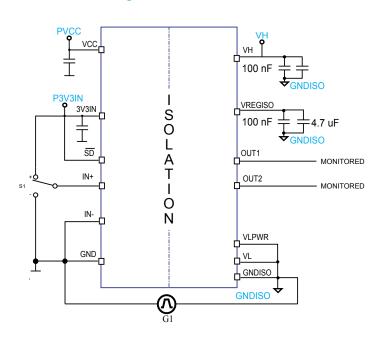

The STGAP4S is a galvanically isolated single gate driver for IGBTs and SiC MOSFETs with advanced protection, configuration and diagnostic features. The architecture of the STGAP4S isolates the channel gate driving from the control and the low voltage interface circuitry through true galvanic isolation.

The unique output architecture is designed to allow the use of an external MOSFET push-pull stage giving flexibility in terms of current capability dimensioning and easing the use of several power switches in parallel. The 2 pre-driver outputs are characterized by current capability and output voltage swing optimized for that topology and allow the use of a negative gate driving supply.

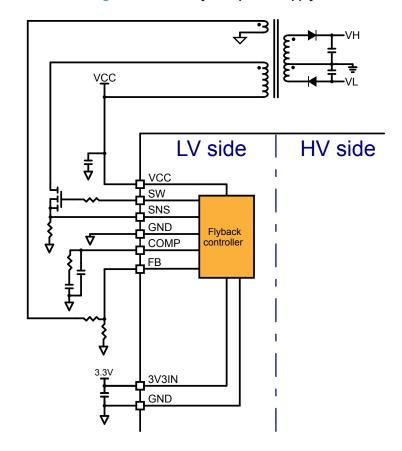

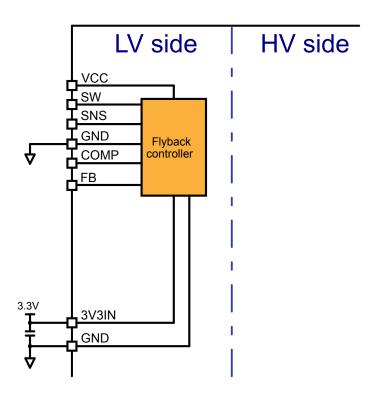

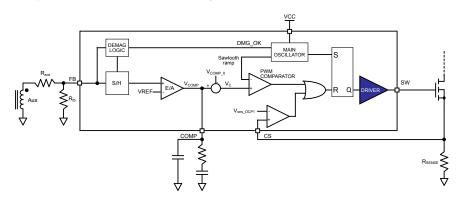

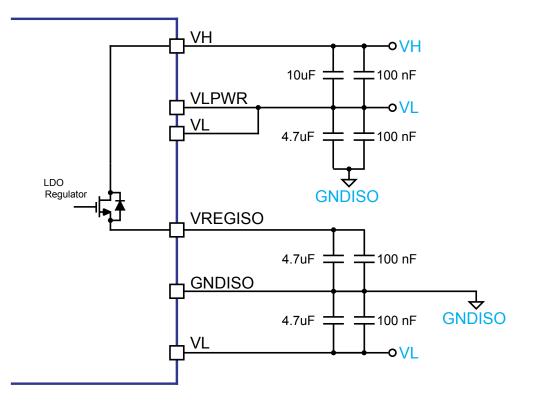

The integrated controller for isolated flyback power supply allows to generate positive and negative gate driver supply voltages with few external components, enabling PCB space saving.

Protection functions such as the Miller clamp driver, desaturation and overcurrent detection, UVLO and OVLO are included to easily design high reliability systems.

A temperature sensor is integrated in the driver.

Open drain diagnostic outputs are present and detailed device conditions can be monitored through the SPI. Each function's parameter can be programmed via the SPI, making the device very flexible and allowing it to fit in a wide range of applications.

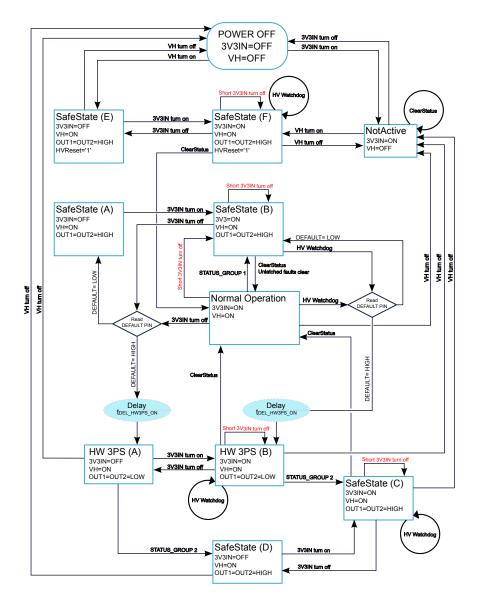

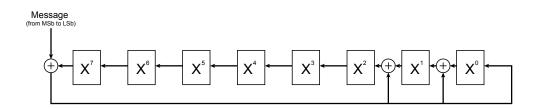

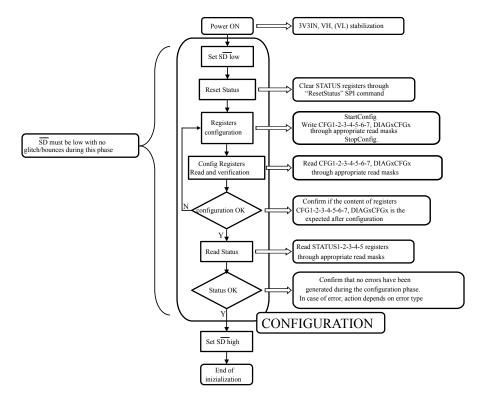

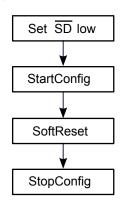

# 1 Block diagram

Figure 1. Block Diagram

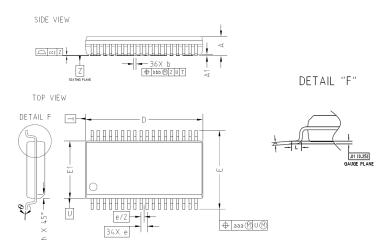

# Pin description and connection diagram

| vcc 🗖       | 1  | 36 | DESAT   |

|-------------|----|----|---------|

| sw 🗖        | 2  | 35 |         |

| SNS 🗖       | 3  | 34 |         |

| GND 🗖       | 4  | 33 |         |

| СОМР 🗖      | 5  | 32 | □ ASC   |

| FB 🗖        | 6  | 31 |         |

| SDO 🗖       | 7  | 30 |         |

| SDI 🗖       | 8  | 29 | CLAMP   |

| <u>cs</u> □ | 9  | 28 | 2LSO    |

| ск 🗖        | 10 | 27 | ⊐ ∨н    |

| SD 🗖        | 11 | 26 | GATE    |

| IN+ 🗖       | 12 | 25 | ADCP    |

| IN- 🗖       | 13 | 24 | ADCN    |

| ADC 🗖       | 14 | 23 | SENSE   |

| DIAG1       | 15 | 22 | DEFAULT |

| DIAG2       | 16 | 21 | VREGISO |

| 3∨3IN 🗖     | 17 | 20 | GNDISO  |

| GND 🗖       | 18 | 19 |         |

# Figure 2. Pin connection (top view)

| Table 1. Pin description |

|--------------------------|

|--------------------------|

| Pin #  | Pin Name | Туре              | Function                                                     |

|--------|----------|-------------------|--------------------------------------------------------------|

| 1      | VCC      | Power supply      | Flyback controller, power supply for external MOSFET driving |

| 2      | SW       | Analog output     | Flyback controller, switching pin for MOSFET gate driving    |

| 3      | SNS      | Analog input      | Flyback controller, external shunt resistor sensing          |

| 4, 18  | GND      | Ground            | Low voltage side ground                                      |

| 5      | COMP     | Analog input      | Flyback controller, compensation                             |

| 6      | FB       | Analog input      | Flyback controller, feedback                                 |

| 7      | SDO      | Logic output      | SPI serial data output                                       |

| 8      | SDI      | Logic input       | SPI serial data input                                        |

| 9      | CS       | Logic input       | SPI chip select (active low)                                 |

| 10     | СК       | Logic input       | SPI clock                                                    |

| 11     | SD       | Logic input       | Shutdown input (active low)                                  |

| 12     | IN+      | Logic input       | Gate command input                                           |

| 13     | IN-      | Logic input       | Gate command input                                           |

| 14     | ADC      | Logic output      | Pulse width modulated output for ADC conversion result       |

| 15     | DIAG1    | Open drain output | Open drain diagnostic output 1 (active low)                  |

| 16     | DIAG2    | Open drain output | Open drain diagnostic output 2 (active low)                  |

| 17     | 3V3IN    | Power supply      | Low voltage side power supply                                |

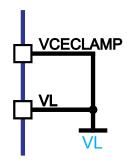

| 19, 33 | VL       | Power supply      | High voltage side negative supply or ground                  |

2

### STGAP4S Pin description and connection diagram

| GNDISO<br>VREGISO | Ground                                                                                           |                                                                                                                                                                     |

|-------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREGISO           |                                                                                                  | High voltage side ground                                                                                                                                            |

| TILEOIOO          | Power supply                                                                                     | High voltage side internal regulator output pin for decoupling capacitor                                                                                            |

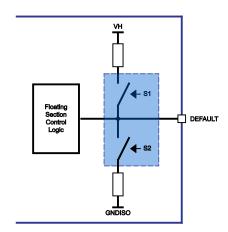

| DEFAULT           | Logic input                                                                                      | Configuration pin for the operation flow chart                                                                                                                      |

| SENSE             | Analog input                                                                                     | Sense input for overcurrent protection                                                                                                                              |

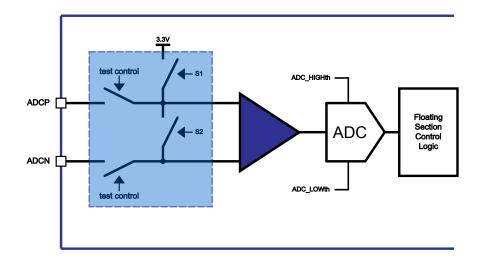

| ADCN              | Analog input                                                                                     | Analog measurement reference, must be connected to GNDISO                                                                                                           |

| ADCP              | Analog input                                                                                     | Analog measurement input                                                                                                                                            |

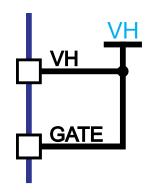

| GATE              | Analog input                                                                                     | Gate voltage feedback                                                                                                                                               |

| VH                | Power supply                                                                                     | High voltage side positive power supply                                                                                                                             |

| 2LSO              | Analog output                                                                                    | Soft turn-off output                                                                                                                                                |

| CLAMP             | Analog output                                                                                    | Miller clamp controller output                                                                                                                                      |

| OUT2              | Analog output                                                                                    | Pre-driver output 2, for external push-pull N-channel MOSFET                                                                                                        |

| OUT1              | Analog output                                                                                    | Pre-driver output 1, for external push-pull P-channel MOSFET                                                                                                        |

| ASC               | Digital input                                                                                    | Asynchronous stop command                                                                                                                                           |

| VLPWR             | Power supply                                                                                     | High voltage side negative power supply or ground for external push-pull driving, must be shorted to VL                                                             |

| VCECLAMP          | Analog input                                                                                     | VCE active clamping protection input                                                                                                                                |

| DESAT             | Analog input                                                                                     | Desaturation protection input                                                                                                                                       |

|                   | SENSE<br>ADCN<br>ADCP<br>GATE<br>/H<br>2LSO<br>CLAMP<br>DUT2<br>DUT1<br>ASC<br>/LPWR<br>/CECLAMP | Analog inputADCNAnalog inputADCPAnalog inputADCPAnalog inputGATEAnalog inputJUT2Analog outputDUT1Analog outputASCDigital inputVLPWRPower supplyVCECLAMPAnalog input |

# 3 Electrical data

57

# 3.1 Absolute maximum ratings

| Symbol                         | Parameter                                                     | Test condition                       | Min.                    | Max.                        | Unit |

|--------------------------------|---------------------------------------------------------------|--------------------------------------|-------------------------|-----------------------------|------|

| VCC                            | Low voltage side<br>power supply voltage<br>vs. GND           | _                                    | -0.30                   | 28                          | v    |

| FB                             | Feedback pin voltage                                          | I <sub>FB</sub> within AMR<br>limits | Self limited            | Self limited                | V    |

| I <sub>FB</sub>                | Feedback pin source/<br>sink current                          | -                                    | -2                      | 2                           | mA   |

| COMP                           | OTA output voltage                                            | -                                    | -0.30                   | 3.60                        | V    |

| SNS                            | Current sensing pin voltage                                   | -                                    | -0.30                   | 1                           | V    |

| SW                             | Gate driver output of flyback controller                      | -                                    | -0.30                   | (VCC + 0.3, 12) min.        | V    |

| 3V3IN                          | Low voltage side<br>power supply voltage<br>vs. GND           | -                                    | -0.30                   | 3.60                        | V    |

| VREGISO                        | High voltage side<br>internal regulator<br>voltage vs. GNDISO | -                                    | -0.30                   | 3.60                        | V    |

| VLOGIC_INPUT                   | Input logic pins voltage vs. GND                              | -                                    | -0.30                   | 6                           | V    |

| VLOGIC_OUTPUT                  | Output logic pins voltage vs. GND                             | -                                    | -0.30                   | 3.60                        | V    |

| V <sub>HL</sub>                | Differential supply voltage (VH vs. VL)                       | -                                    | -0.30                   | 36                          | V    |

| VH                             | Positive power supply<br>voltage (VH vs.<br>GNDISO)           | -                                    | -0.30                   | 36                          | V    |

| VL                             | Negative supply<br>voltage (VL vs.<br>GNDISO)                 | -                                    | -15                     | 0.30                        | V    |

| VLPWR                          | Negative power supply<br>voltage (VLPWR vs.<br>GNDISO)        | -                                    | -15                     | 0.30                        | V    |

| V <sub>PS</sub> <sup>(1)</sup> | Differential voltage<br>between VLPWR and<br>VL pin           | -                                    | -0.30                   | +0.30                       | V    |

| V <sub>OUT1</sub>              | Voltage on OUT1 pre-<br>driver output (OUT1<br>vs. VH)        | -                                    | (-20, VLPWR - 0.3) max. | +0.30                       | V    |

| I <sub>OUT1sink</sub>          | OUT1 pre-driver<br>output sink current                        | -                                    | -                       | Self limited <sup>(2)</sup> | mA   |

| I <sub>OUT1source</sub>        | OUT1 pre-driver<br>output source current                      | OUT1 = LOW                           | -                       | 10                          | mA   |

| V <sub>OUT2</sub>              | Voltage on OUT2 pre-<br>driver output (OUT2<br>vs. VLPWR)     | -                                    | -0.30                   | (+ 20, VH + 0.3) min        | V    |

## Table 2. Absolute maximum ratings

| Symbol                   | Parameter                                                  | Test condition         | Min.     | Max.                        | Unit |

|--------------------------|------------------------------------------------------------|------------------------|----------|-----------------------------|------|

| I <sub>OUT2sink</sub>    | OUT2 pre-driver<br>output sink current                     | OUT2 = HIGH            | -        | 10                          | mA   |

| I <sub>OUT2source</sub>  | OUT2 pre-driver<br>output source current                   | -                      | -        | Self limited <sup>(2)</sup> | mA   |

| V <sub>GATE</sub>        | Voltage on GATE pin vs. GNDISO                             | -                      | VL-0.30  | VH + 0.30                   | V    |

| V <sub>CLAMP</sub>       | Voltage on CLAMP<br>pre-driver output<br>(CLAMP vs. VLPWR) | -                      | -0.30    | (+ 20, VH + 0.3) min.       | V    |

| ICLAMPsink               | CLAMP pre-driver<br>output sink current                    | CLAMP = HIGH           | -        | 10                          | mA   |

| I <sub>CLAMPsource</sub> | CLAMP pre-driver<br>output source current                  | -                      | -        | Self limited <sup>(2)</sup> | mA   |

| V <sub>DESAT</sub>       | Voltage on DESAT pin vs. GNDISO                            | -                      | -0.30    | VH + 0.30                   | V    |

| V <sub>ADCP</sub>        | Voltage on ADCP pin vs. GNDISO                             | -                      | -0.30    | 3.6                         | V    |

| V <sub>ADCN</sub>        | Voltage on ADCN pin vs. GNDISO                             | -                      | -0.30    | +0.30                       | V    |

| V <sub>SENSE</sub>       | Voltage on SENSE pin vs. GNDISO                            | -                      | -2       | (VH +0.30, 20) min.         | V    |

| V <sub>CECLAMP</sub>     | Voltage on<br>VCECLAMP pin vs.<br>GNDISO                   | -                      | VL -0.30 | VH +0.30                    | V    |

| V2LTO_SOFTOFF            | Voltage on 2LSO pin vs. GNDISO                             | -                      | VL -0.30 | VH +0.30                    | V    |

| V <sub>ASC</sub>         | Voltage on ASC pin vs. GNDISO                              | -                      | -0.30    | VH +0.30                    | V    |

| Vdefault                 | Voltage on DEFAULT pin vs. GNDISO                          | -                      | -0.30    | VH +0.30                    | V    |

| V <sub>DIAGx</sub>       | Open drain output voltage                                  | -                      | -0.30    | 6                           | V    |

| Tj                       | Junction temperature                                       | -                      | -40      | 150                         | °C   |

| T <sub>STG</sub>         | Storage temperature                                        |                        | -50      | 150                         | °C   |

| T <sub>A</sub>           | Ambient temperature                                        | -                      | -40      | 125                         | °C   |

| P <sub>Din</sub>         | Power dissipation input chip                               | T <sub>A</sub> = 80 °C | -        | 600                         | mW   |

| P <sub>Dout</sub>        | Power dissipation output chip                              | T <sub>A</sub> = 80 °C | -        | 800                         | mW   |

| ESD                      | Human body model                                           | -                      |          | 2                           | kV   |

1.  $V_{PS} = VLPWR - VL$

2. Actual limit depends on power dissipation constraints

## 3.2 Thermal data

## Table 3. Thermal data

| Symbol              | Parameter                              | Value | Unit |

|---------------------|----------------------------------------|-------|------|

| R <sub>th(JA)</sub> | Thermal resistance junction to ambient | 51    | °C/W |

57

# 3.3 Recommended operating conditions

| Table 4. Recommended operating conditions |

|-------------------------------------------|

|-------------------------------------------|

| Symbol                         | Parameter                                                       | Test condition | Min.             | Max.                    | Unit |

|--------------------------------|-----------------------------------------------------------------|----------------|------------------|-------------------------|------|

| VH                             | High voltage side positive power supply voltage (VH vs. GNDISO) | -              | 5 <sup>(1)</sup> | 32                      | V    |

| VL                             | High voltage side negative supply voltage (VL vs. GNDISO)       | -              | -10              | 0 <sup>(2)</sup>        | V    |

| VREGISO                        | High voltage side logic supply voltage (VREGISO vs. GNDISO)     | -              | 3                | .3 ± 5%                 | V    |

| V <sub>HL</sub>                | Differential supply voltage (VH vs. VL)                         | -              | 5                | 32                      | V    |

| V <sub>PS</sub> <sup>(3)</sup> | Differential voltage between VLPWR and VL pin                   | -              | -100             | 100                     | mV   |

| VCC                            | Low voltage side power supply voltage vs. GND                   | -              | 7.2              | 24                      | V    |

| 3V3IN                          | Low voltage side power supply voltage vs. GND                   | -              | 3                | .3 ± 5%                 | V    |

| V <sub>LOGIC_INPUT</sub>       | Logic pins voltage vs. GND                                      | -              | 0                | 5.5                     | V    |

| V <sub>DIAGx</sub>             | Open drain output voltage                                       | -              | 0                | 5.5                     | V    |

| V <sub>ADCP</sub>              | ADCP voltage vs. GNDISO                                         | -              | 0                | 3.0                     | V    |

| V <sub>ADCN</sub>              | ADCN voltage vs. GNDISO                                         | -              | 0                | 100                     | mV   |

| GATE                           | GATE pin voltage vs. GNDISO                                     | -              | VL               | VH                      | V    |

| ASC                            | ASC pin voltage vs. GNDISO                                      | -              | 0                | (VH, 15) <sub>min</sub> | V    |

| DEFAULT                        | DEFAULT pin voltage vs. GNDISO                                  | -              | 0                | (VH, 15) <sub>min</sub> | V    |

| V <sub>DESATth</sub>           | Desaturation protection threshold                               | DESAT enabled  | -                | VH – 2 V                | V    |

| f <sub>SW</sub>                | Maximum switching frequency                                     | -              | -                | 80 (4)(5)               | kHz  |

1. When UVLO is enabled this value is  $VH_{on}$ , max

2. When UVLO is enabled this value is VL<sub>on</sub>, min

3.  $V_{PS} = VLPWR - VL$

4. Actual limit depends on power dissipation constraints

5. A lower switching frequency is suggested if continuous readings of HV side registers and ADC sampling are implemented

# 4 Electrical characteristics

# 4.1 AC operation

## Table 5. AC operation electrical characteristics

| Symbol                | Parameter                                               | Test condition                                                      | Min.     | Тур. | Max. | Unit |

|-----------------------|---------------------------------------------------------|---------------------------------------------------------------------|----------|------|------|------|

|                       |                                                         | INfilter = '01'                                                     | 50       | 70   | 90   | ns   |

| t <sub>deglitch</sub> | Input deglitch time                                     | INfilter = '10'                                                     | 100      | 160  | 220  | ns   |

|                       |                                                         | INfilter = '11'                                                     | 420      | 500  | 580  | ns   |

| t <sub>INmin</sub>    | Minimum propagated input pulse                          | INfilter = '00'                                                     | -        | -    | 20   | ns   |

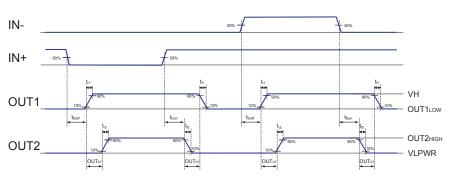

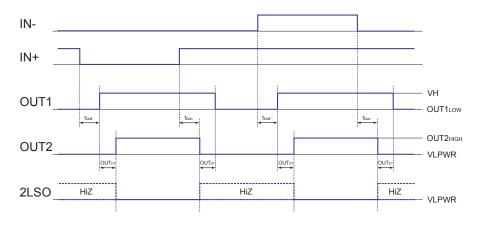

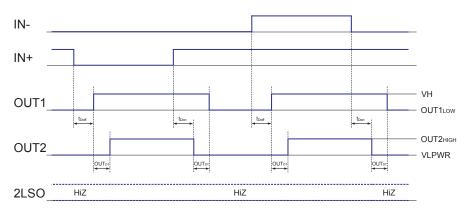

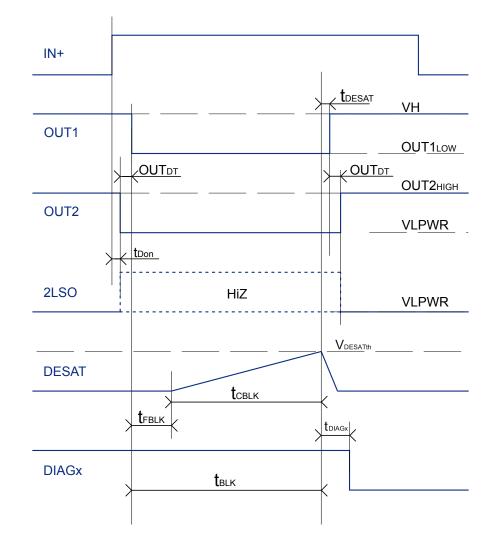

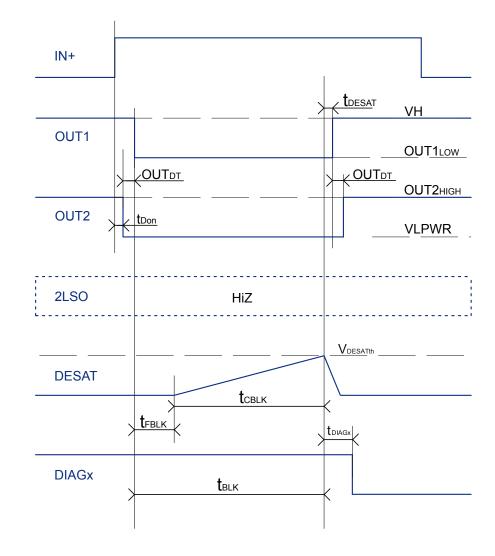

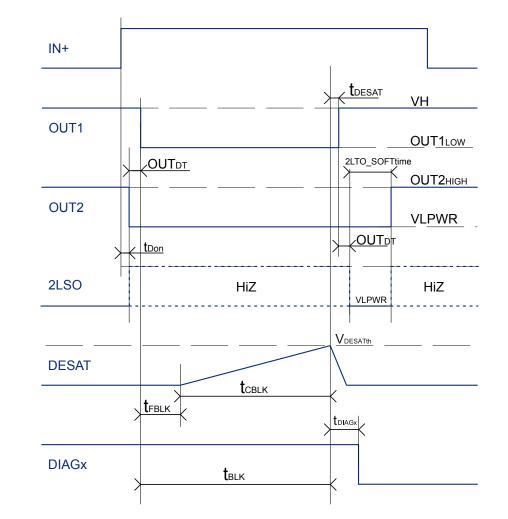

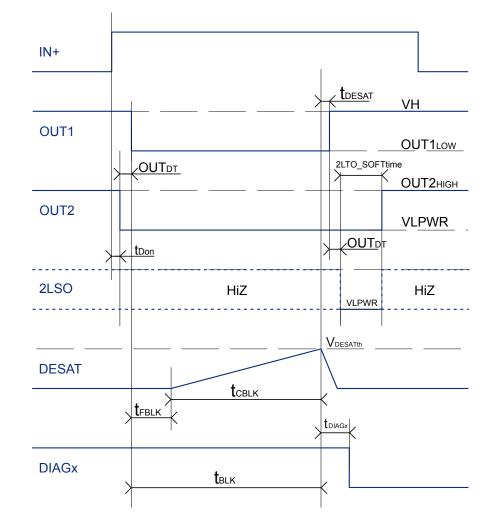

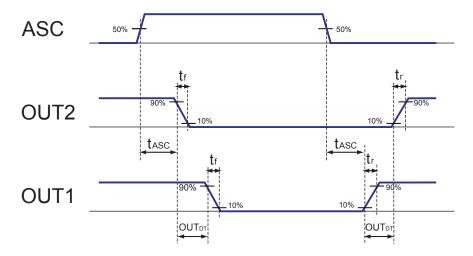

| t <sub>Don</sub>      | Input to output propagation delay ON                    | INfilter = '00', DTset = '000'<br>to OUT2, No load<br>See Figure 11 | 45       | 60   | 100  | ns   |

| t <sub>Doff</sub>     | Input to output propagation delay OFF                   | INfilter = '00', DTset = '000'<br>to OUT1, No load<br>Figure 11     | 45       | 60   | 100  | ns   |

| t <sub>r1</sub>       | OUT1 rise time                                          | C <sub>L</sub> = 1 nF, 10% ÷ 90%                                    | -        | -    | 15   | ns   |

| t <sub>f1</sub>       | OUT1 fall time                                          | C <sub>L</sub> = 1 nF, 90% ÷ 10%                                    | -        | -    | 45   | ns   |

| t <sub>r2,CLAMP</sub> | OUT2, CLAMP rise time                                   | C <sub>L</sub> = 1 nF, 10% ÷ 90%                                    | -        | -    | 45   | ns   |

| t <sub>f2,CLAMP</sub> | OUT2, CLAMP fall time                                   | C <sub>L</sub> = 1 nF, 90% ÷ 10%                                    | -        | -    | 15   | ns   |

| PWD                   | Pulse width distortion $ t_{Don} - t_{Doff} $           | t <sub>IN</sub> > 100 ns<br>INfilter = '00'                         | -        | 0    | 30   | ns   |

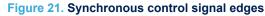

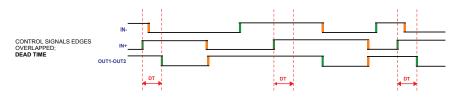

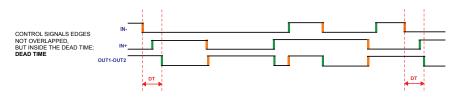

|                       | "OUT1 to OUT2" and "OUT2 to OUT1" deadtime              | OUT_DTth = '0'                                                      | 46       | 55   | 64   | ns   |

| OUT <sub>DT</sub>     |                                                         | OUT_DTth = '1'                                                      | 77       | 88   | 97   | ns   |

|                       |                                                         | DTset = '000'                                                       | Disabled |      |      |      |

|                       |                                                         | DTset = '001'                                                       | 205      | 250  | 310  |      |

|                       |                                                         | DTset = '010'                                                       | 410      | 500  | 610  |      |

| DT                    | Deadtime                                                | DTset = '011'                                                       | 615      | 750  | 905  | ns   |

|                       |                                                         | DTset = '100'                                                       | 820      | 1000 | 1200 |      |

|                       |                                                         | DTset = '101'                                                       | 1025     | 1250 | 1495 |      |

|                       |                                                         | DTset = '110'                                                       | 1230     | 1500 | 1790 |      |

|                       |                                                         | DTset = '111'                                                       | 1640     | 2000 | 2380 |      |

| t <sub>release</sub>  | Minimum flag release time                               | <del>SD</del> = '0', SD_FLAG = '1'                                  | -        | -    | 100  | μs   |

| CMTI <sup>(1)</sup>   | Common-mode transient immunity,   dV <sub>ISO</sub> /dt | V <sub>CM</sub> = 1200 V<br>see Figure 49                           | 100      | -    | -    | V/ns |

1. Characterization data, not tested in production.

# 4.2 DC operation

## Table 6. DC operation electrical characteristics

| Symbol                           | Parameter                            | Test condition                     | Min.         | Тур.         | Max.         | Unit |

|----------------------------------|--------------------------------------|------------------------------------|--------------|--------------|--------------|------|

| Logic inputs/output              |                                      |                                    |              |              |              |      |

| V <sub>ol</sub>                  | SDO, ADC logic "0" output voltage    | I = 4 mA                           | -            | -            | 0.15         | V    |

| V <sub>oh</sub>                  | SDO, ADC logic "1" output voltage    | I = 4 mA                           | 3V3IN - 0.15 | -            | -            | V    |

| IN+h                             | IN+ logic "1"<br>input bias current  | Vin = 3.3 V                        | 41           | 66           | 88           | μA   |

| IN+I                             | IN+ logic "0"<br>input bias current  | Vin = GND                          | -            | -            | 0.10         | μA   |

| IN-h                             | IN- logic "1" input bias current     | Vin = 3.3 V                        | -            | -            | 0.10         | μA   |

| IN-I                             | IN- logic "0"<br>input bias current  | Vin = GND                          | 12           | 18           | 26           | μA   |

| SD+h                             | SD logic "1" input bias current      | Vin = 3.3 V                        | 41           | 66           | 88           | μA   |

| SD+I                             | SD logic "0" input bias current      | Vin = GND                          | -            | -            | 0.10         | μA   |

| CSh                              | CS logic "1" input bias current      | Vin = GND                          | 35           | 60           | 95           | μA   |

| CSI                              | CS logic "0" input bias current      | Vin = 3.3 V                        | -            | -            | 0.10         | μA   |

| Rin_pd                           | IN+ and SD input pull-down resistors | Vin = 3.3 V                        | 37           | 50           | 81           | kΩ   |

| R <sub>in_IN-</sub>              | IN- input<br>pull-up resistor        | -                                  | 126          | 180          | 275          | kΩ   |

| R <sub>in_CS</sub>               | CS input pull-up resistor            | Vin = GND                          | 34           | 55           | 95           | kΩ   |

| VIL                              | Low logic level voltage              | -                                  | 0.29 · 3V3IN | 0.33 · 3V3IN | 0.37 · 3V3IN | V    |

| V <sub>IH</sub>                  | High logic level voltage             | -                                  | 0.62 · 3V3IN | 0.66 · 3V3IN | 0.72 · 3V3IN | V    |

| V <sub>hyst</sub>                | Logic input<br>threshold hysteresis  | -                                  | 1.05         | 1.15         | 1.25         | V    |

| Driver buffer section            | and CLAMP function                   |                                    |              |              |              |      |

| OUT1source                       | Source peak current                  | t <sub>pulse</sub> < 5 μs DC = 1 % | 1650         | 2500         | 3400         | mA   |

| OUT1sink                         | Sink peak current                    | t <sub>pulse</sub> < 5 μs DC = 1 % | 400          | 600          | 800          | mA   |

| OUT2source,<br>CLAMPsource       | Source peak current                  | t <sub>pulse</sub> < 5 μs DC = 1 % | 350          | 600          | 900          | mA   |

| OUT2sink,<br>CLAMPsink           | Sink peak current                    | t <sub>pulse</sub> < 5 μs DC = 1 % | 1700         | 2400         | 3100         | mA   |

| SOFTOFFsink                      | Sink peak current                    | t <sub>pulse</sub> < 5 μs DC = 1 % | 440          | 800          | 1400         | mA   |

|                                  | Source MOSFET<br>R <sub>DS_on</sub>  | I <sub>D</sub> = 100 mA            | 0.8          | 1.5          | 2.8          | Ω    |

| RDSonOUT2sink,<br>RDSonCLAMPsink | Sink MOSFET<br>R <sub>DS_on</sub>    | I <sub>D</sub> = 100 mA            | 0.5          | 0.8          | 1.8          | Ω    |

| RDSonSOFTOFFsink                 | Sink MOSFET<br>R <sub>DS_on</sub>    | I <sub>D</sub> = 20 mA             | 2.5          | 4.5          | 10           | Ω    |

| OUT1 <sub>LOW</sub>              | OUT1 low output<br>voltage           | No load, VH – VL = 15 V            | VH-13        | VH-11.7      | VH-10.5      | v    |

Max.

VL+1.1

VL+13

VH-0.4

2.3

-2.3

80

3.04

2.98

65

11.2

19.2

15.

Тур.

VL+0.7

VL+11.7

VH-0.7

2

-2

50

2.9

2.85

55

7

12

9.5

Unit

V

V

V

V

ns

v

V

mV

mA

| Symbol                   | Parameter                                                | Test condition                                                     | Min.    |

|--------------------------|----------------------------------------------------------|--------------------------------------------------------------------|---------|

| OUT1 <sub>LOW</sub>      | OUT1 low output voltage                                  | No load, VH – VL = 5 V                                             | VL+0.4  |

| OUT2 <sub>HIGH</sub> ,   | OUT2, CLAMP high                                         | No load, VH – VL = 15 V                                            | VL+10.5 |

| CLAMP <sub>HIGH</sub>    | output voltage                                           | No load, VH – VL = 5 V                                             | VH-1.1  |

| V <sub>GATEth_OFF</sub>  | CLAMP function voltage threshold                         | GATE vs. VL                                                        | 1.7     |

| V <sub>GATEth_ON</sub>   | GATE voltage ON threshold                                | GATE vs. VH                                                        | -1.7    |

| t <sub>CLAMP</sub>       | V <sub>GATEth_OFF</sub> to<br>CLAMP propagation<br>delay | OUT1 = HIGH<br>OUT2 = HIGH                                         | 30      |

| Supply voltage           |                                                          | 1                                                                  |         |

| UVLO3V3IN <sub>ON</sub>  | 3V3IN UVLO turn-on threshold                             | -                                                                  | 2.7     |

| UVLO3V3IN <sub>OFF</sub> | 3V3IN UVLO turn-off threshold                            | -                                                                  | 2.67    |

| UVLO3V3IN <sub>hys</sub> | 3V3IN UVLO<br>hysteresis                                 | -                                                                  | 45      |

|                          |                                                          | INx = GND                                                          | -       |

|                          | 3V3IN quiescent                                          | IN- = GND<br>IN+ = SD = 3V3IN                                      | -       |

| I <sub>Q3V3</sub>        | supply current                                           | IN- = GND<br>SD = 3V3IN<br>IN+: f = f <sub>SW,MAX</sub><br>D = 50% | -       |

| VCC <sub>on</sub>        | VCC UVLO<br>turn-on threshold                            | -                                                                  | 6.6     |

| VCC <sub>off</sub>       | VCC UVLO<br>turn-off threshold                           | -                                                                  | 6.4     |

| VCC <sub>hys</sub>       | VCC UVLO<br>hysteresis                                   | -                                                                  | 0.185   |

| IQCC                     | VCC quiescent<br>supply current                          | SW no load<br>F <sub>swDCDC</sub> = 400 kHz                        | -       |

|                          |                                                          | VHONth = '000'                                                     |         |

|                          |                                                          | VHONth = '001'                                                     | 10.35   |

|                          |                                                          | VHONth = '010'                                                     | 11.30   |

|                          | VH UVLO                                                  | VHONth = '011'                                                     | 12.25   |

| VH <sub>on</sub>         | turn-on threshold                                        | VHONth = '100'                                                     | 13.15   |

|                          |                                                          | VHONth = '101'                                                     | 14.10   |

|                          |                                                          | VHONth = '110'                                                     | 15.00   |

|                          |                                                          | $\lambda$ (LIONIth = (111)                                         | 45.05   |

| VL <sub>off</sub>  | VL UVLO                        | VLONth = '00'                               |          | Disabled |       |    |

|--------------------|--------------------------------|---------------------------------------------|----------|----------|-------|----|

| VH <sub>hyst</sub> | VH UVLO hysteresis             | -                                           | 0.7      | 1        | 1.3   | V  |

|                    |                                | VHONth = '111'                              | 15.00    | 16       | 17.00 |    |

|                    |                                | VHONth = '110'                              | 14.10    | 15       | 15.95 |    |

|                    |                                | VHONth = '101'                              | 13.15    | 14       | 14.70 |    |

| Pott               | turn-off threshold             | VHONth = '100'                              | 12.25    | 13       | 13.65 | V  |

| /H <sub>off</sub>  | VH UVLO                        | VHONth = '011'                              | 11.30    | 12       | 12.60 | v  |

|                    |                                | VHONth = '010'                              | 10.35    | 11       | 11.55 |    |

|                    |                                | VHONth = '001'                              | 9.40     | 10       | 10.60 |    |

|                    |                                | VHONth = '000'                              | Disabled |          |       |    |

|                    |                                | VHONth = '111'                              | 15.95    | 17       | 18.05 |    |

|                    |                                | VHONth = '110'                              | 15.00    | 16       | 17.00 |    |

|                    |                                | VHONth = '101'                              | 14.10    | 15       | 15.95 |    |

| 'H <sub>on</sub>   | turn-on threshold              | VHONth = '100'                              | 13.15    | 14       | 14.70 | V  |

|                    | VH UVLO                        | VHONth = '011'                              | 12.25    | 13       | 13.65 |    |

|                    |                                | VHONth = '010'                              | 11.30    | 12       | 12.60 |    |

|                    |                                | VHONth = '001'                              | 10.35    | 11       | 11.55 |    |

|                    |                                | VHONth = '000'                              |          | Disabled |       |    |

| QCC                | VCC quiescent supply current   | SW no load<br>F <sub>swDCDC</sub> = 400 kHz | -        | 2        | 4     | mA |

| /CC <sub>hys</sub> | VCC UVLO<br>hysteresis         | -                                           | 0.185    | 0.235    | 0.285 | v  |

| ′CC <sub>off</sub> | VCC UVLO<br>turn-off threshold | -                                           | 6.4      | 6.8      | 7.2   | v  |

| /CC <sub>on</sub>  | VCC UVLO<br>turn-on threshold  | -                                           | 6.6      | 7        | 7.4   | V  |

| Symbol               | Parameter                          | Test condition                                                | Min.  | Тур.     | Max.  | Unit                       |  |

|----------------------|------------------------------------|---------------------------------------------------------------|-------|----------|-------|----------------------------|--|

|                      |                                    | VLONth = '01'                                                 | -2.10 | -2       | -1.80 |                            |  |

| VL <sub>off</sub>    | turn-off threshold                 | VLONth = '10'                                                 | -4.25 | -4       | -3.80 | v                          |  |

|                      |                                    | VLONth = '11'                                                 | -6.35 | -6       | -5.70 |                            |  |

|                      |                                    | VLONth = '00'                                                 |       | Disabled |       |                            |  |

|                      | VL UVLO                            | VLONth = '01'                                                 | -3.15 | -3       | -2.80 | _                          |  |

| VL <sub>on</sub>     | turn-on threshold                  | VLONth = '10'                                                 | -5.25 | -5       | -4.70 | V                          |  |

|                      |                                    | VLONth = '11'                                                 | -7.35 | -7       | -6.55 |                            |  |

| VL <sub>hys</sub>    | VL UVLO hysteresis                 | -                                                             | 0.7   | 1        | 1.3   | V                          |  |

| OVVH <sub>on</sub>   |                                    | OVLOVHth = '00'                                               | 16.90 | 18       | 19.10 |                            |  |

|                      | VH OVLO                            | OVLOV Hth= '01'                                               | 18.80 | 20       | 21.20 | -                          |  |

| OVVH <sub>on</sub>   | turn-on threshold                  | OVLOVHth = '10'                                               | 20.70 | 22       | 23.35 | - V                        |  |

|                      |                                    | OVLOVHth = '11'                                               | 31.1  | 33       | 34.9  |                            |  |

|                      |                                    | OVLOVHth = '00'                                               | 17.85 | 19       | 20.15 |                            |  |

| 0.0.4.1              | VH OVLO                            | OVLOVHth = '01'                                               | 19.75 | 21       | 22.25 |                            |  |

| OVVH <sub>off</sub>  | turn-off threshold                 | OVLOVHth = '10'                                               | 21.60 | 23       | 24.40 | - V                        |  |

|                      |                                    | OVLOVHth = '11'                                               | 32.1  | 34       | 35.9  |                            |  |

| OVVH <sub>hys</sub>  | VH OVLO hysteresis                 | -                                                             | 0.7   | 1        | 1.3   | V                          |  |

| OVVL <sub>off</sub>  | VL OVLO<br>turn-off threshold      | -                                                             | -12.8 | -12      | -11.2 | V                          |  |

| OVVL <sub>on</sub>   | VL OVLO<br>turn-on threshold       | -                                                             | -11.8 | -11      | -10.2 | V                          |  |

| OVVL <sub>hyst</sub> | VL OVLO hysteresis                 | -                                                             | 0.7   | 1        | 1.3   | V                          |  |

|                      |                                    | SD = 3V3IN<br>IN+ = IN- = GND                                 | -     | 10       | 13    |                            |  |

| I <sub>QH</sub>      | VH quiescent supply<br>current     | SD = 3V3IN<br>IN- = GND<br>IN+: f = f <sub>SW,MAX</sub> D=50% | -     | 12       | 18    | mA                         |  |

|                      |                                    | SD = 3V3IN<br>IN+ = IN- = GND                                 | -     | 2.5      | 3.5   |                            |  |

| I <sub>QL</sub>      | VL quiescent supply<br>current     | SD= 3V3ININ- = GNDIN+: f = f <sub>SW,MAX</sub> D=50%          | -     | 3.2      | 5     | mA                         |  |

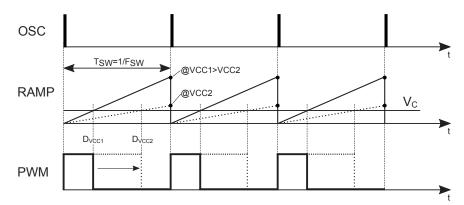

| Isolated Flyback C   | ontroller section – Osci           | llator                                                        |       | 1        | 1     |                            |  |

|                      |                                    | CONTROLLER_FREQ = '00'                                        | 370   | 400      | 430   |                            |  |

| F <sub>swDCDC</sub>  | Main oscillator                    | CONTROLLER_FREQ = '01'                                        | 180   | 200      | 220   | kHz                        |  |

| ' SWDCDC             | frequency                          | CONTROLLER_FREQ = '10'                                        | 270   | 300      | 330   | KI IZ                      |  |

|                      |                                    | CONTROLLER_FREQ = '11'                                        | 540   | 600      | 660   |                            |  |

| ∆F <sub>swDCDC</sub> | Frequency jittering peak amplitude | -                                                             | 1.4   | 1.75     | 2     | % of<br>F <sub>swDCE</sub> |  |

| F <sub>jit</sub>     | Jittering frequency                | -                                                             | 400   | 500      | 600   | Hz                         |  |

| Isolated Flyback C   | ontroller section – Dem            | agnetization Detector                                         |       |          |       |                            |  |

| I <sub>FB</sub>      | Static Input Bias<br>Current       | V <sub>FB</sub> = 2.5 V                                       | -     | 0.5      | 1     | μA                         |  |

| V <sub>FBH</sub>     | Upper Clamp<br>Voltage             | I <sub>FB</sub> = 1 mA                                        | 3     | 3.3      | 3.6   | V                          |  |

57

| Symbol                  | Parameter                                | Test condition                               | Min.           | Тур.  | Max.  | Unit |

|-------------------------|------------------------------------------|----------------------------------------------|----------------|-------|-------|------|

| / <sub>FBL</sub>        | Lower Clamp<br>Voltage                   | I <sub>FB</sub> = - 1 mA                     | -90            | -60   | -30   | mV   |

| IV <sub>FB</sub> /dt    | Minimum detectable slope                 | Voltage falling                              | 0.05           | 0.08  | 0.15  | V/µs |

| / <sub>FBA</sub>        | Arming Voltage                           | Positive-going edge,<br>% of sampled voltage | 69             | 75    | 81    | %    |

| / <sub>FBT</sub>        | Triggering Voltage                       | Negative-going edge,<br>% of sampled voltage | 61             | 67    | 73    | %    |

| BLANK                   | Demag detection blanking time            | After $V_{\mbox{SW}}$ going low              | 140            | 203   | 240   | ns   |

| solated Flyback Co      | ontroller section – Tran                 | sconductance Error Amplifie                  | er of PSR loop |       |       |      |

| REF Voltage Reference   |                                          | T <sub>J</sub> = 25 °C                       | 2.45           | 2.5   | 2.55  |      |

| REF                     | Voltage Reference                        | T <sub>J</sub> = -40 ÷ +125 °C               | 2.425          | -     | 2.575 | V    |

| Jm                      | Transconductance                         | V <sub>FB</sub> = 2.5 V                      | 1.6            | 2.3   | 3.1   | mS   |

|                         | Source Current                           | V <sub>COMP</sub> = 2.8 V                    | 0.65           | 1     | 1.3   | mA   |

| COMP                    | Sink Current                             | V <sub>COMP</sub> = 0.9 V                    | 1.3            | 2     | 2.5   | mA   |

| / <sub>COMPsat.hi</sub> | Upper saturation voltage                 | I <sub>COMP</sub> = 100 μA (source)          | 3V3IN -100mV   | -     | 3V3IN | v    |

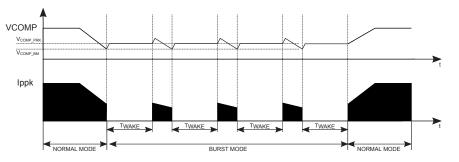

| solated Flyback Co      | ontroller section – burs                 | t mode                                       |                |       |       |      |

| √сомр_вм                | Burst-mode entry level                   | -                                            | 1.05           | 1.1   | 1.15  | V    |

| COMP_PRK                | Parking level during idle mode           | -                                            | 1.1            | 1.15  | 1.2   | V    |

| VCOMP_0                 | COMP offset                              | -                                            | 0.9            | 1.02  | 1.1   | V    |

| GFF                     | Feedforward gain                         | -                                            | 0.125          | 0.150 | 0.175 | -    |

| WAKE                    | Burst repetition time                    | -                                            | 400            | 500   | 600   | μs   |

| solated Flyback Co      | ontroller section – Curr                 | ent sensing                                  | 1              |       |       |      |

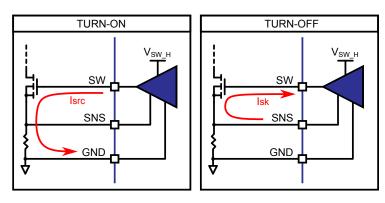

| sns                     | Bias current                             | $V_{sns} = 0.2 V,$<br>$V_{sw} = V_{sw_H}$    | -              | -     | 1     | μΑ   |

| d(H-L)                  | Delay to Output                          | dV <sub>CS</sub> /dt = 0.5 V/μs              | 20             | 45    | 70    | ns   |

| LEB                     | Leading Edge<br>Blanking time            | -                                            | 50             | 70    | 110   | ns   |

| /sns_OCP1               | Cycle-by-cycle OCP<br>level              | -                                            | 110            | 125   | 150   | mV   |

| √ <sub>sns_OCP2</sub>   | 2nd OCP level                            | -                                            | 170            | 200   | 230   | mV   |

| solated Flyback Co      | ontroller section – Inter                | nal soft-start                               | 1              |       |       |      |

| SS                      | Soft-start time                          | -                                            | 5              | 8     | 11    | ms   |

| solated Flyback Co      | ontroller section – Outp                 | ut undervoltage protection                   |                |       |       |      |

| V <sub>UVP</sub>        | UVP threshold                            | -                                            | 1.045          | 1.1   | 1.155 | V    |

| UVP                     | UVP blanking time                        | After soft-start end                         | 17             | 25    | 33    | ms   |

| UVP'                    |                                          | Continuos switching                          | -              | 4     | -     | 1113 |

| N <sub>UVP</sub>        | Consecutive cycles<br>for UVP triggering | Burt Mode wake up                            | -              | 3     | -     |      |

| solated Flyback Co      | ontroller section – Fault                |                                              |                | -     |       |      |

| RESTART                 | Restart delay after fault                | -                                            | 0.53           | 0.8   | 1.06  | s    |

| solated Flyback Co      |                                          | winding disconnection deter                  | ction          |       |       |      |

| FBON                    | Min. source current                      | SW = HIGH                                    | 20             | 40    | 55    | μA   |

|                         | ontroller section – Gate                 |                                              |                |       |       | P" 1 |

Unit V

V

А

ns ns kΩ

V

V

ns

μA

mA

ns

ns

| Symbol                 | Parameter                        | Test condition                                                                                | Min.  | Тур.  | Ма  |

|------------------------|----------------------------------|-----------------------------------------------------------------------------------------------|-------|-------|-----|

| V <sub>SW_L</sub>      | Output Low Voltage               | I <sub>sink</sub> = 100 mA                                                                    | 0.145 | 0.3   | 0.5 |

|                        |                                  | I <sub>source</sub> = 5 mA                                                                    | 8     | 9.5   | 1'  |

| V <sub>SW_H</sub>      | Output High voltage              | VCC > 7.6 V<br>I <sub>source</sub> = 5 mA                                                     | 6     | 7.5   | 9   |

|                        |                                  | VCC = VCC <sub>off</sub> + 100 mV<br>I <sub>source</sub> = 5 mA                               | 6.2   | 6.7   | 7.  |

| I <sub>src_pk</sub>    | Peak source current              | -                                                                                             | 0.220 | 0.550 | 0.8 |

| I <sub>sk_pk</sub>     | Peak sink current                | -                                                                                             | 0.517 | 1.1   | 1.6 |

| t <sub>f</sub>         | Fall time                        | C <sub>L</sub> = 1 nF, 80% ÷ 20%                                                              | 7     | 13    | 2   |

| t <sub>r</sub>         | Rise time                        | C <sub>L</sub> = 1 nF, 20% ÷ 80%                                                              | 5     | 20    | 4   |

| R <sub>UVLO</sub>      | R UVLO saturation                | -                                                                                             | 14    | 25    | 34  |

| V <sub>SW_OFF</sub>    | SW LOW without<br>3V3IN          | 3 < VCC < 24 V,<br>3V3IN = GND,<br>I <sub>sk</sub> = 1 mA                                     | 0.21  | 0.37  | 0.7 |

| Desaturation prot      | ection                           |                                                                                               |       |       |     |

|                        |                                  | DESATth = '000'                                                                               | 2.80  | 3     | 3.2 |

|                        | Desaturation<br>threshold        | DESATth = '001'                                                                               | 3.60  | 4     | 4.2 |

|                        |                                  | DESATth = '010'                                                                               | 4.60  | 5     | 5.3 |

| V <sub>DESATth</sub>   |                                  | DESATth = '011'                                                                               | 5.50  | 6     | 6.3 |

|                        |                                  | DESATth = '100'                                                                               | 6.50  | 7     | 7.4 |

|                        |                                  | DESATth = '101'                                                                               | 7.40  | 8     | 8.4 |

|                        |                                  | DESATth = '110'                                                                               | 8.30  | 9     | 9.4 |

|                        |                                  | DESATth = '111'                                                                               | 9.30  | 10    | 10. |

| t <sub>DESfilter</sub> | DESAT pin deglitch filter        | DESATth = '100' (1)                                                                           | -     | 20    | -   |

|                        |                                  | DESATcur = '00';<br>VDESAT = 0 V                                                              | 230   | 250   | 27  |

| I <sub>DESAT</sub>     | DESAT blanking                   | DESATcur = '01';<br>V <sub>DESAT</sub> = 0 V                                                  | 460   | 500   | 54  |

| DESAT                  | charge current                   | DESATcur = '10';<br>V <sub>DESAT</sub> = 0 V                                                  | 680   | 750   | 81  |

|                        |                                  | DESATcur = '11';<br>V <sub>DESAT</sub> = 0 V                                                  | 910   | 1000  | 10  |

| IDESoff                | DESAT blanking discharge current | V <sub>DESAT</sub> = 8 V<br>IN+= GND;                                                         | 35    | 70    | 9   |

| t <sub>FBLK</sub>      | DESAT fixed blanking time        | -                                                                                             | 160   | 250   | 34  |

| t <sub>DESAT</sub>     | DESAT intervention time          | DESATth = '000'<br>$0 \rightarrow 5 \text{ V}$ step on V <sub>DESAT</sub><br>Step to OUT1 10% | 80    | 150   | 22  |

| Soft turn-Off funct    | tion                             |                                                                                               |       |       |     |

|                        |                                  | 2LTO_SOFTtime = '1111'                                                                        | 0.22  | 0.25  | 0.  |

|                        |                                  | 2LTO_SOFTtime = '0000'                                                                        | 0.43  | 0.50  | 0.5 |

|                        | SOFTOFF MOSFET                   | 2LTO_SOFTtime = '0001'                                                                        | 0.64  | 0.75  | 0.8 |

• MOSFET 2LTO\_SOFTtime = '0001' 0.64 0.75 0.89 activation time when the Soft turn-off 2LTO\_SOFTtime = '0010' 0.89 1.00 1.15  $t_{\text{2LTO}\_\text{SOFTtime}}$ μs function is triggered (SAFE\_OF =1; SOFT\_2LTO=0) 2LTO\_SOFTtime = '0011' 1.36 1.50 1.65 2LTO\_SOFTtime = '0100' 1.83 2.00 2.18 2LTO\_SOFTtime = '0101' 2.30 2.50 2.70

57

### STGAP4S DC operation

| Symbol                     | Parameter                                                       | Test condition                                                                               | Min.      | Тур.      | Max.   | Unit |

|----------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------|-----------|--------|------|

|                            |                                                                 | 2LTO_SOFTtime = '0110'                                                                       | 2.77      | 3.00      | 3.23   |      |

|                            |                                                                 | 2LTO_SOFTtime = '0111'                                                                       | 3.25      | 3.50      | 3.75   |      |

|                            | SOFTOFF MOSFET                                                  | 2LTO_SOFTtime = '1000'                                                                       | 3.47      | 3.75      | 4.03   |      |

|                            | activation time when                                            | 2LTO_SOFTtime = '1001'                                                                       | 3.71      | 4.00      | 4.29   | μs   |

| <sup>t</sup> 2LTO_SOFTtime | the Soft turn-off<br>function is triggered                      | 2LTO_SOFTtime = '1010'                                                                       | 3.94      | 4.25      | 4.56   |      |

|                            | (SAFE_OF =1;<br>SOFT_2LTO=0)                                    | 2LTO_SOFTtime = '1011'                                                                       | 4.18      | 4.50      | 4.82   |      |

|                            |                                                                 | 2LTO_SOFTtime = '1100'                                                                       | 4.42      | 4.75      | 5.08   |      |

|                            |                                                                 | 2LTO_SOFTtime = '1101'                                                                       | 4.66      | 5.00      | 5.34   |      |

|                            |                                                                 | 2LTO_SOFTtime = '1110'                                                                       | 4.90      | 5.25      | 5.63   |      |

| SENSE overcurren           | t function                                                      | · · · · ·                                                                                    |           |           |        |      |

|                            |                                                                 | SENSEth = '000'                                                                              | 88        | 100       | 112    |      |

|                            |                                                                 | SENSEth = '001'                                                                              | 110       | 125       | 140    | _    |

|                            |                                                                 | SENSEth = '010'                                                                              | 135       | 150       | 165    |      |

|                            | SENSE protection                                                | SENSEth = '011'                                                                              | 158       | 175       | 192    |      |

| V <sub>SENSEth</sub>       | threshold                                                       | SENSEth = '100'                                                                              | 185       | 200       | 215    | — mV |

|                            |                                                                 | SENSEth = '101'                                                                              | 235       | 250       | 268    |      |

|                            |                                                                 | SENSEth = '110'                                                                              | 285       | 300       | 315    |      |

|                            |                                                                 | SENSEth = '111'                                                                              | 380       | 400       | 420    |      |

| SENSE                      | SENSE protection intervention time                              | SENSEth = '111'<br>$0\rightarrow 1 \text{ V}$ step on V <sub>SENSE</sub> Step<br>to OUT1 10% | 50        | 95        | 120    | ns   |

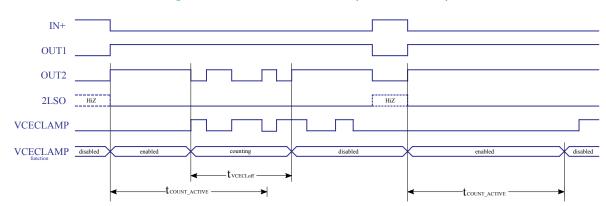

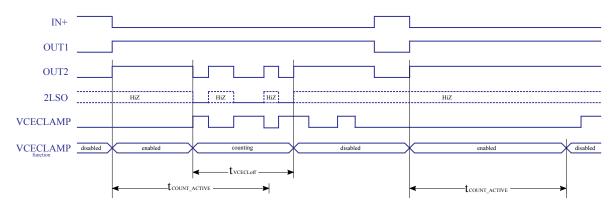

| VCE active clampir         | ng protection                                                   | · ·                                                                                          |           |           |        |      |

| V <sub>CECLth</sub>        | VCE clamping threshold                                          | -                                                                                            | VL + 1.20 | VL + 1.60 | VL + 2 | V    |

| V <sub>CECLhyst</sub>      | VCE clamping hysteresis                                         | -                                                                                            | 0.30      | 0.50      | 0.60   | V    |

| <sup>t</sup> VCECL         | VCE clamping intervetion time                                   | -                                                                                            | 10        | 22        | 35     | ns   |

| t <sub>COUNT_ACTIVE</sub>  | VCE clamping<br>observation window<br>after turn-off<br>command | -                                                                                            | 2.77      | 3         | 3.23   | μs   |

| <sup>t</sup> VCECLoff      | VCE clamping time-<br>out                                       | -                                                                                            | 2         | 2.30      | 2.7    | μs   |

| Diagnostics output         | t                                                               |                                                                                              |           |           |        |      |

| DIAG1,2                    | Fault event to<br>DIAGx Low delay                               | Fault event to DIAGx 90%                                                                     | -         | 4         | -      | μs   |

| DIAG1,2                    | DIAGx low level sink<br>current                                 | V <sub>DIAGx</sub> = 0.4 V                                                                   | 8         | 18        | 30     | mA   |

| RDIAG1,2                   | DIAGx pull-down resistor                                        | -                                                                                            | 330       | 550       | 800    | kΩ   |

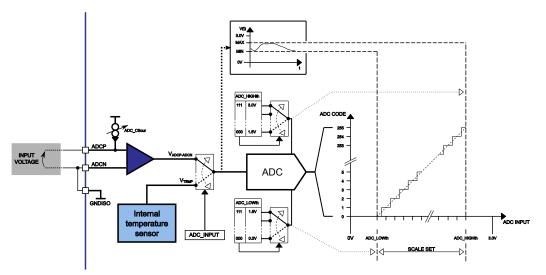

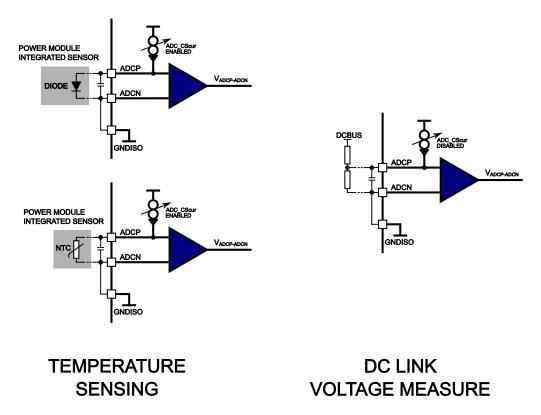

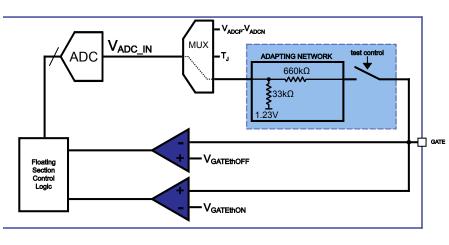

| Analog measureme           | ent function                                                    |                                                                                              |           |           |        |      |

|                            |                                                                 | ADC_CScur = '00'                                                                             |           | Disabled  |        |      |

|                            | Current source                                                  | ADC_CScur = '10'                                                                             | 260       | 300       | 330    |      |

| ADCP                       | connected to ADCP pin                                           | ADC_CScur = '01'                                                                             | 500       | 600       | 660    | – uA |

|                            |                                                                 | ADC_CScur = '11'                                                                             | 850       | 1000      | 1100   |      |

| RES                        | ADC resolution                                                  | ADC_LOWth = '000' and<br>ADC_HIGHth = '111'                                                  | -         | 8         | -      | bit  |

| PER_CONV                   | ADC periodic                                                    | -                                                                                            | 80        | 100       | 120    | μs   |

| Symbol                | Parameter                          | Test condition                                                     | Min.  | Тур.  | Max.  | Unit |  |

|-----------------------|------------------------------------|--------------------------------------------------------------------|-------|-------|-------|------|--|

| fadc                  | PWM ADC output<br>frequency        | ADC_PWM_EN = '1' and<br>ADC_EN = '1'                               | 8     | 10    | 12    | kHz  |  |

| DC1 <sub>ADC</sub>    | ADC signal maximum duty cycle      | ADC_PWM_EN = '1'<br>STATUS5 = 0x00                                 | -     | 90    | -     | %    |  |

| DC2 <sub>ADC</sub>    | ADC signal medium duty cycle       | ADC_PWM_EN = '1'<br>STATUS5 = 0x80                                 | -     | 50    | -     | %    |  |

| DC3 <sub>ADC</sub>    | ADC signal minimum duty cycle      | ADC_PWM_EN = '1'<br>STATUS5 = 0xFF<br>See Section 7.10for details. | -     | 10    | -     | %    |  |

|                       |                                    | ADC_HIGHth = '000'                                                 | 1.470 | 1.500 | 1.530 |      |  |

|                       |                                    | ADC_HIGHth = '001                                                  | 1.685 | 1.715 | 1.745 |      |  |

|                       |                                    | ADC_HIGHth = '010'                                                 | 1.890 | 1.930 | 1.970 |      |  |

|                       | ADC higher input                   | ADC_HIGHth = '011'                                                 | 2.110 | 2.145 | 2.180 | _    |  |

| ADC_HIGHth            | threshold level                    | ADC_HIGHth = '100'                                                 | 2.310 | 2.360 | 2.400 | - V  |  |

|                       |                                    | ADC_HIGHth = '101'                                                 | 2.520 | 2.570 | 2.610 |      |  |

|                       |                                    | ADC_HIGHth = '110'                                                 | 2.730 | 2.785 | 2.830 | -    |  |

|                       |                                    | ADC_HIGHth = '111'                                                 | 2.940 | 3.000 | 3.040 | -    |  |

|                       |                                    | ADC_LOWth = '000'                                                  | -     | 0     | 0.015 |      |  |

| ADC_LOWth             | ADC lower input<br>threshold level | ADC_LOWth = '001                                                   | 0.200 | 0.215 | 0.230 |      |  |

|                       |                                    | <br>ADC_LOWth = '010'                                              | 0.405 | 0.430 | 0.455 |      |  |

|                       |                                    | ADC_LOWth = '011'                                                  | 0.615 | 0.645 | 0.670 | _    |  |

|                       |                                    | ADC LOWth = '100'                                                  | 0.830 | 0.855 | 0.890 | - V  |  |

|                       |                                    | ADC_LOWth = '101'                                                  | 1.035 | 1.070 | 1.105 | -    |  |

|                       |                                    | ADC_LOWth = '110'                                                  | 1.250 | 1.285 | 1.320 | -    |  |

|                       |                                    | ADC_LOWth = '111'                                                  | 1.465 | 1.500 | 1.530 | _    |  |

| ADC_OFFSerr           | ADC offset error                   |                                                                    | -3    | -     | 3     | LSB  |  |

| ADC_GAINerr           | ADC gain error                     | ADC LOWth = '000' and                                              | -7    | -     | 3.5   | LSB  |  |

| <br>INL               | ADC INL                            | ADC_HIGHth = '111'                                                 | -3    | -     | 3     | LSB  |  |

| DNL                   | ADC DNL                            |                                                                    | -1    | _     | 1     | LSB  |  |

| ADC_IN_LEAK           | ADC Input leakage current          | ADC_LOWth = '000' and<br>ADC_HIGHth= '111'<br>ADCP-ADCN=3.3 V      | -     | -     | 0.50  | uA   |  |

| ASC function          |                                    |                                                                    |       |       |       |      |  |

| ASCIL                 | Low logic level voltage            | -                                                                  | 0.80  | 1.10  | 1.40  | V    |  |

| ASCIH                 | High logic level voltage           | -                                                                  | 1.80  | 2.20  | 2.40  | V    |  |

| ASC <sub>hyst</sub>   | Hysteresis                         | -                                                                  | 0.95  | 1.1   | 1.25  | V    |  |

| ASCh                  | ASC logic "1" input bias current   | V <sub>ASC</sub> = 5 V                                             | 25    | 50    | 75    | μA   |  |

| lasci                 | ASC logic "0" input bias current   | V <sub>ASC</sub> = 0 V                                             | -     | -     | 0.10  | μA   |  |

| R <sub>ASC</sub>      | ASC pull-down resistor             | V <sub>ASC</sub> = 1.5 V                                           | 35    | 50    | 70    | kΩ   |  |

| tasc                  | ASC intervention time              | V <sub>ASC</sub> = 5 V<br>SeeFigure 38                             | 30    | 55    | 100   | ns   |  |

| DEFAULT function      |                                    | · · · · · · · · · · · · · · · · · · ·                              |       |       |       |      |  |

| DEFAULT <sub>IL</sub> | Low logic level voltage            | -                                                                  | 0.80  | 1.10  | 1.40  | V    |  |

| Symbol                               | Parameter                                                      | Test condition                 | Min. | Тур. | Max. | Unit |

|--------------------------------------|----------------------------------------------------------------|--------------------------------|------|------|------|------|

| DEFAULT <sub>IH</sub>                | High logic level voltage                                       | -                              | 1.80 | 2.20 | 2.40 | V    |

| DEFAULT <sub>hyst</sub>              | hysteresis                                                     | -                              | 0.95 | 1.1  | 1.25 | V    |

| tdel_hw3ps_on                        | Delay entering into<br>HW3PS state                             | V <sub>DEFAULT</sub> = VREGISO | 80   | 100  | 120  | μs   |

| Functionality chec                   | ks                                                             |                                |      |      |      |      |

| t <sub>Rchk</sub>                    | SENSE resistor check time                                      | -                              | -    | -    | 15   | μs   |

| ISENSERchk                           | SENSE resistor<br>check current                                | V <sub>SENSE</sub> < 1 V       | 8    | 10   | 12   | μΑ   |

| Overtemperature p                    | protection                                                     |                                |      |      |      |      |

| T <sub>WARN</sub>                    | Warning<br>temperature <sup>(1)</sup>                          | -                              | 125  | -    | -    | °C   |

| T <sub>SDN</sub>                     | Shutdown<br>temperature <sup>(1)</sup>                         | -                              | 155  | -    | -    | °C   |

| T <sub>hys</sub>                     | Temperature hysteresis <sup>(1)</sup>                          | -                              | -    | 20   | -    | °C   |

| SPI <sup>(1)</sup>                   |                                                                |                                |      |      |      |      |