Sauls Wharf House Crittens Road Great Yarmouth Norfolk NR31 0AG Telephone +44 (0)1493 602602 Email:sales@midasdisplays.com Email:tech@midasdisplays.com www.midasdisplays.com

| MCCOG128064D6W-FPTLW | 128 x 64  | N/A             | LCD Module |  |  |  |  |

|----------------------|-----------|-----------------|------------|--|--|--|--|

| Specification        |           |                 |            |  |  |  |  |

| Version: 1           |           | Date: 30/10/202 | 20         |  |  |  |  |

|                      | Re        | vision          |            |  |  |  |  |

| 1 30/10/2020         | First Iss | sue             |            |  |  |  |  |

|                      |           |                 |            |  |  |  |  |

| Display F             |                         |              |                  |

|-----------------------|-------------------------|--------------|------------------|

| Resolution            | 128 x 64                |              |                  |

| Appearance            | Black on White          |              |                  |

| Logic Voltage         | 3V                      |              | 1                |

| Interface             | Parallel / SPI          | N TR         | oHS<br>ompliant  |

| Font Set              | N/A                     |              | mpliant          |

| Display Mode          | Transflective           |              | mphane           |

| LC Type               | FSTN                    |              |                  |

| Module Size           | 45.00 x 40.00 x 10.40mm |              |                  |

| Operating Temperature | -20°C ~ +70°C           |              |                  |

| Construction          | COG                     | Box Quantity | Weight / Display |

| LED Backlight         | White                   |              |                  |

\*- For full design functionality, please use this FACTURE • SUPPLY specification in conjunction with the ST7565R specification. (Provided Separately)

| Display Accessories |             |  |  |  |  |

|---------------------|-------------|--|--|--|--|

| Part Number         | Description |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

|                     |             |  |  |  |  |

| Optional Variants  |  |  |  |  |  |  |  |

|--------------------|--|--|--|--|--|--|--|

| Appearances Voltag |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

### 1. FUNCTIONS & FEATURES

MCCOG128064D6W-FPTLW Series LCD Type :

• Viewing Direction : 6 O'clock

• Driving Scheme : 1/65 Duty Cycle, 1/9 Bias

• Power Supply Voltage(Typ.) : 3.0 V

• LCD Operation Voltage :9.0 V

• Display Contents :128x64 Dots

Backlight : LED,Lightguide,White

• Operating temperature :-20°C  $\sim$  +70°C

• Storage temperature :-30°C  $\sim$  +80°C

RoHS Compliant

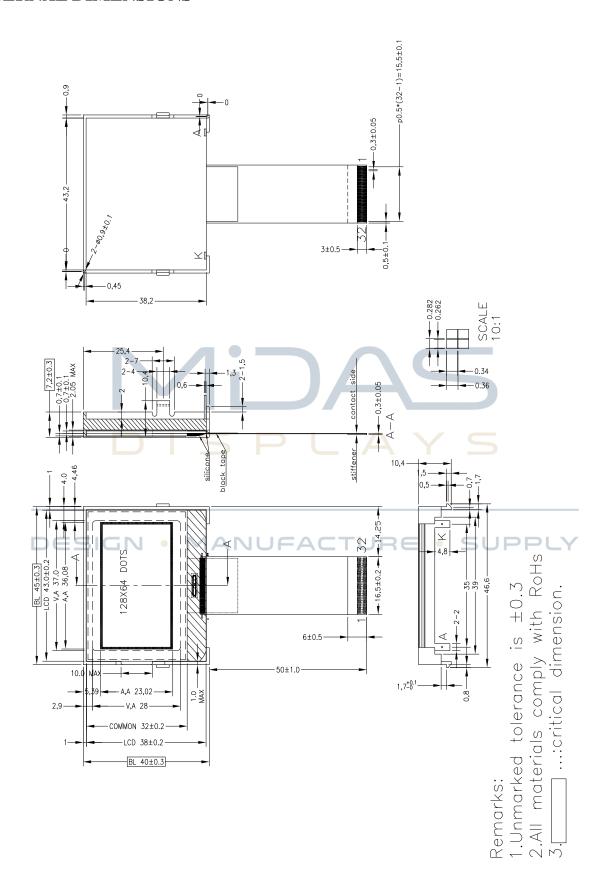

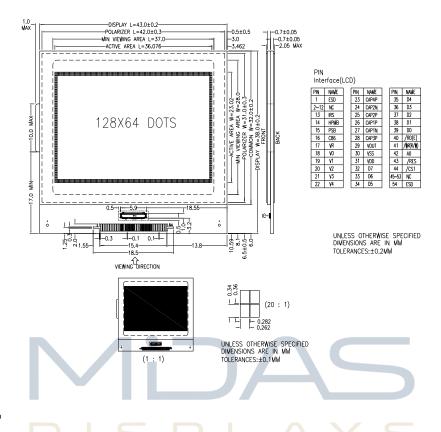

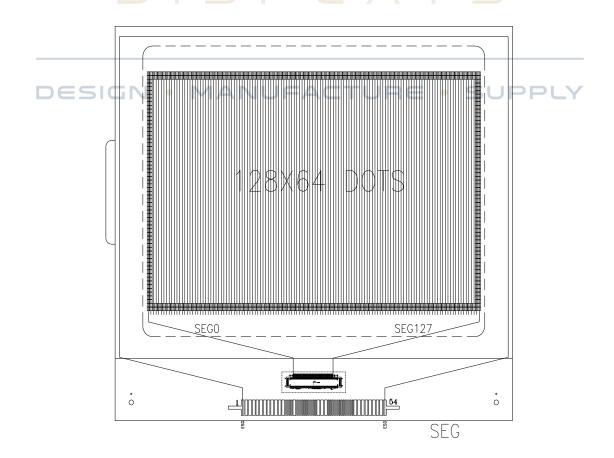

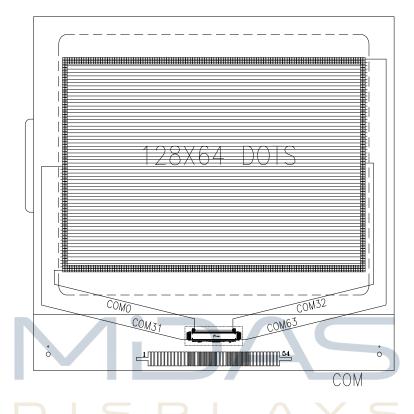

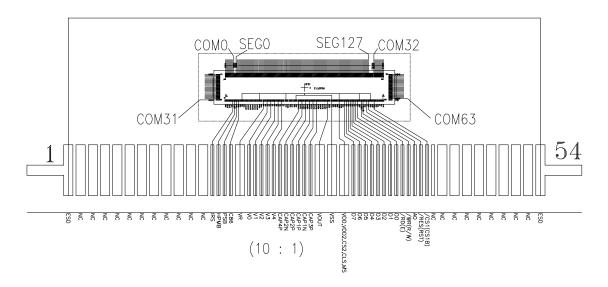

# 2. MECHANICAL SPECIFICATIONS

• Module Size:  $: 45.0(L) \times 40.00(W) \times 10.4(T) \text{mm}$  (without FPC)

• Viewing Area Size: : 37.00(W) x 28.00(H) mm

• Active Area Size MANU: 36.08(W) x 23.02(H)mm • SUPPLY

• Dot pitch: : 0.282(W) x 0.36(H)mm

• Dot Size: : 0.262(W) x 0.34(H) mm

## **EXTERNAL DIMENSIONS**

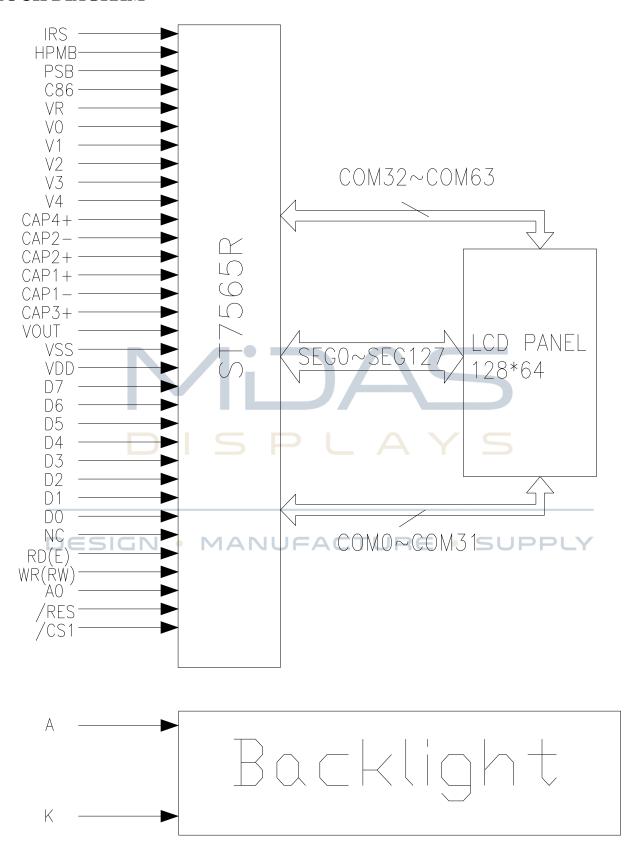

### **BLOCK DIAGRAM**

# PIN DESCRIPTION

| Pin No. | Name   | Description                                                                                                                                              |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |        | This terminal selects the resistors for the V0 voltage level adjustment.                                                                                 |

| 1       | IRS    | IRS = "H": Use the internal resistors                                                                                                                    |

|         |        | IRS = "L": Do not use the internal resistors. The V0 voltage level is regulated by an external resistive voltage divider attached to the VR terminal     |

|         |        | This is the power control terminal for the power supply circuit for liquid crystal drive.                                                                |

| 2       | HPMB   | /HPM = "H": Normal mode                                                                                                                                  |

|         |        | /HPM = "L": High power mode (suggested)  This pin configures the interface to be parallel mode or serial mode.                                           |

| 3       | PSB    | P/S = "H": Parallel data input/output.                                                                                                                   |

|         |        | P/S = "L": Serial data input.                                                                                                                            |

| 4       | C86    | This is the MPU interface selection pin. C86 = "H": 6800 Series MPU interface.                                                                           |

| 4       | C60    | C86 = "L": 8080 Series MPU interface.                                                                                                                    |

| 5       | VR     | This is the internal-output VREG power supply for the LCD power supply voltage                                                                           |

|         |        | regulator.                                                                                                                                               |

| 6       | V0     |                                                                                                                                                          |

| 7       | V1     |                                                                                                                                                          |

| 8       | V2     | LCD driver supplies voltages                                                                                                                             |

| 9       | V3     |                                                                                                                                                          |

| 10      | V4     |                                                                                                                                                          |

| 11      | CAP4+  |                                                                                                                                                          |

| 12      | CAP2-  |                                                                                                                                                          |

| 13      | CAP2+  |                                                                                                                                                          |

| 14      | CAP1+  | DC/DC voltage converter.                                                                                                                                 |

| 15      | CAP1-  |                                                                                                                                                          |

| 16      | CAP3+  |                                                                                                                                                          |

| 17      | VOUT   |                                                                                                                                                          |

| 18      | VSS    | Ground                                                                                                                                                   |

| 19      | VDD    | Voltage supply                                                                                                                                           |

| 20      | D7     |                                                                                                                                                          |

| 21      | D6     |                                                                                                                                                          |

| 22      | D5     | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU                                                                |

| 23      | D4     | data bus. When the serial interface (SPI-4) is selected (P/S = "L"):                                                                                     |

| 24      | D3     | D7: serial data input (SI); D6: the serial clock input (SCL).                                                                                            |

| 25      | D2     | D0 to D5 should be connected to VDD or floating.  When the chip select is not active, D0 to D7 are set to high impedance.                                |

| 26      | D1     |                                                                                                                                                          |

| 27      | D0     |                                                                                                                                                          |

|         |        | • When connected to 8080 series MPU, this pin is treated as the "/RD" signal of the 8080                                                                 |

|         |        | MPU and is LOW-active.  The data bus is in an output status when this signal is "L"                                                                      |

| 28      | RD(E)  | The data bus is in an output status when this signal is "L".  • When connected to 6800 series MPU, this pin is treated as the "E" signal of the 6800     |

|         |        | MPU and is HIGH-active.                                                                                                                                  |

|         |        | This is the enable clock input terminal of the 6800 Series MPU.  When connected to 8080 series MPU, this pip is treated as the "WPP" signal of the 8080. |

|         |        | • When connected to 8080 series MPU, this pin is treated as the "/WR" signal of the 8080 MPU and is LOW-active.                                          |

|         |        | The signals on the data bus are latched at the rising edge of the /WR signal.                                                                            |

| 29      | WR(RW) | • When connected to 6800 series MPU, this pin is treated as the "R/W" signal of the 6800                                                                 |

|         |        | MPU and decides the access type: When R/W = "H": Read.                                                                                                   |

|         |        | When R/W = "L": Write.                                                                                                                                   |

| 30 | A0   | This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or command.  A0 = "H": Indicates that D0 to D7 are display data.  A0 = "L": Indicates that D0 to D7 are control data. |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 | /RES | The RESET signal                                                                                                                                                                                                                                   |

| 32 | /CS1 | This is the Chip Select signal.                                                                                                                                                                                                                    |

| A | Supply voltage for backlight LED+ |

|---|-----------------------------------|

| K | Supply voltage for backlight LED- |

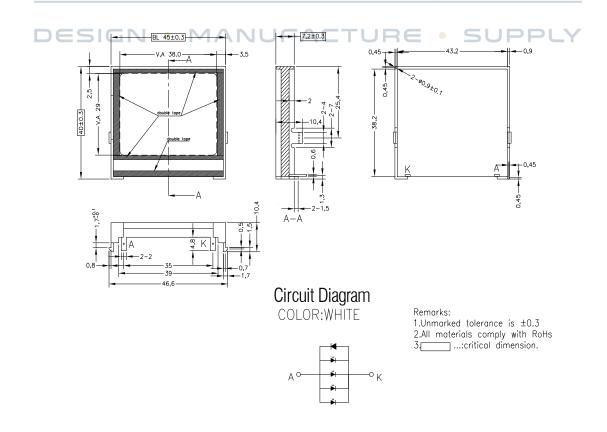

# **BACKLIGHT CHARACTERISTICS**

| Item                | Symbol | min.   | typ.  | max. | Unit              | Condition |

|---------------------|--------|--------|-------|------|-------------------|-----------|

| Forward Voltagt     | Vf     | 2. 9   | 3. 1  | 3. 3 | V                 |           |

| Power Dissipation   | Pd     | 174    | 186   | 198  | mW                |           |

| Luminous Uniformity | ΔLv    | 70     |       |      | %                 | If= 60 mA |

| Luminance           | Lv     | 420    | 500   |      | cd/m <sup>2</sup> |           |

| Color Coordinate    | Х      | 0. 260 |       | 0.30 |                   | T=25° C   |

|                     | Y      | 0. 270 |       | 0.31 |                   | 1 20 0    |

| Lifetime            | 5      | 50     | 0000h |      | Hours             |           |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                           | Symbol         | Conditions  | Unit |

|-------------------------------------|----------------|-------------|------|

| Power Supply Voltage                | VDD            | -0.3 ~ 3.6  | V    |

| Power supply voltage (VDD standard) | V0,VOUT        | -0.3 ~ 13.5 | V    |

| Power supply voltage (VDD standard) | V1, V2, V3, V4 | -0.3 to V0  | V    |

| Operating temperature               | TOPR           | -20 to +70  | °C   |

| Storage temperature                 | TSTR           | -30 to +80  | °C   |

## **ELECTRICAL CHARACTERISTICS**

### 1. DC CHARACTERISTICS

| Item                      | Sym       | Condition       | STA       | units |           |       |

|---------------------------|-----------|-----------------|-----------|-------|-----------|-------|

| Item                      | bol       | Condition       | Min.      | Тур.  | Max.      | uiits |

| Operating Voltage         | $V_{DD}$  | Relative to VSS | 2.7       | 3.0   | 3.3       |       |

| LCD driving voltage       | $V_{LCD}$ | Relative to VSS | 8.7       | 9.0   | 9.3       |       |

| High-level Input Voltage  | $V_{IHC}$ |                 | 0.8 x VDD |       | VDD       | V     |

| Low-level Input Voltage   | $V_{ILC}$ |                 | VSS       |       | 0.2 x VDD | v     |

| High-level Output Voltage | $V_{OHC}$ | IOH = -0.5  mA  | 0.8 x VDD |       | VDD       |       |

| Low-level Output Voltage  | $V_{OLC}$ | IOH = -0.5  mA  | VSS       |       | 0.2 x VDD |       |

| Consumption current       | $I_{DD}$  |                 |           | TBD   |           | mA    |

**DESIGN • MANUFACTURE • SUPPLY**

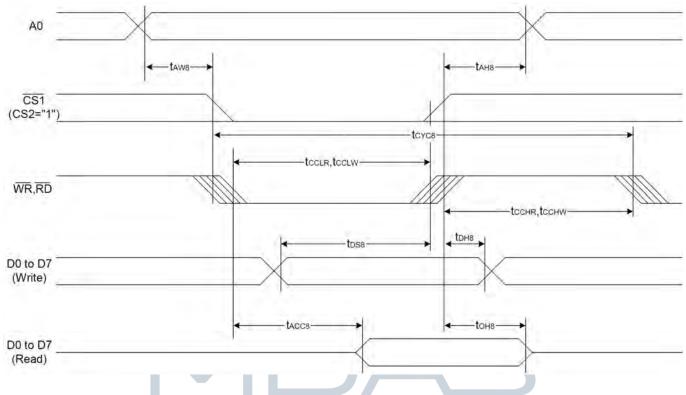

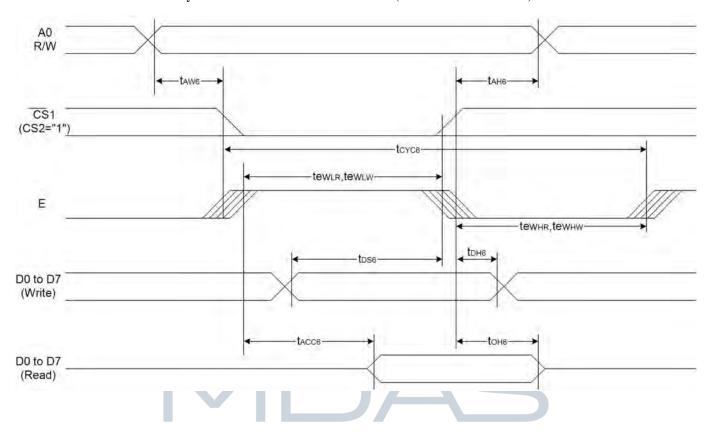

## 2. AC CHARACTERISTICS

System Bus Read/Write Characteristics 1 (For the 8080 Series MPU)

| Item                         | Cianal   | Symbol           | Condition   | Rat  | ting | Units |

|------------------------------|----------|------------------|-------------|------|------|-------|

| item                         | Signal   | Symbol           | Condition   | Min. | Max. |       |

| Address hold time            |          | tah8             |             | 0    | 1000 |       |

| Address setup time           | A0       | taw8             |             | 0    | -    |       |

| System cycle time            |          | tcyc8            |             | 240  | W 0  |       |

| Enable L pulse width (WRITE) | WR       | tcclw            |             | 80   | -    |       |

| Enable H pulse width (WRITE) |          | tcchw            |             | 80   | _    |       |

| Enable L pulse width (READ)  | RD       | tcclr            |             | 140  | 7    | Ns    |

| Enable H pulse width (READ)  |          | tcchr            |             | 80   |      |       |

| WRITE Data setup time        |          | toss             |             | 40   |      |       |

| WRITE Address hold time      | D0 4= D7 | t <sub>DH8</sub> |             | 0    | -    |       |

| READ access time             | D0 to D7 | taccs            | CL = 100 pF |      | 70   |       |

| READ Output disable time     |          | toн8             | CL = 100 pF | 5    | 50   |       |

#### System Bus Read/Write Characteristics 2 (For the 6800 Series MPU)

| Item                         | Cianal   | Cumbal | Condition   | Rat       | ing               | Units |

|------------------------------|----------|--------|-------------|-----------|-------------------|-------|

| itelli                       | Signal   | Symbol | Condition   | Min. Max. |                   | Units |

| Address hold time            |          | tan6   |             | 0         | -                 |       |

| Address setup time           | A0       | taw6   |             | 0         | -                 |       |

| System cycle time            |          | tcyc6  |             | 240       | -                 |       |

| Enable L pulse width (WRITE) | - WR     | tewnw  |             | 80        |                   |       |

| Enable H pulse width (WRITE) |          | tewnw  |             | 80        | -                 |       |

| Enable L pulse width (READ)  | 122      | tewlr  |             | 80        | _                 | ns    |

| Enable H pulse width (READ)  | RD       | tewhr  | 1           | 140       |                   |       |

| WRITE Data setup time        |          | tDS6   |             | 40        | 1 - <del></del> - |       |

| WRITE Address hold time      | D0 4- D7 | tDH6   |             | 0         | -                 |       |

| READ access time             | D0 to D7 | tACC6  | CL = 100 pF | - t-      | 70                |       |

| READ Output disable time     |          | tон6   | CL = 100 pF | 5         | 50                |       |

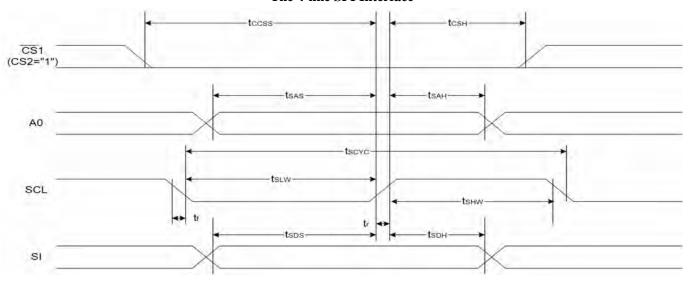

#### **The 4-line SPI Interface**

| Item                    | Signal | Symbol | Condition | Rati | Units     |    |

|-------------------------|--------|--------|-----------|------|-----------|----|

| item                    | Signai | Symbol | Condition | Min. | Min. Max. |    |

| 4-line SPI Clock Period |        | Tscyc  |           | 50   | _         |    |

| SCL "H" pulse width     | SCL    | Tshw   |           | 25   | _         |    |

| SCL "L" pulse width     | ]      | Tstw   |           | 25   | _         | 1  |

| Address setup time      | A0     | Tsas   |           | 20   | _         | 7  |

| Address hold time       | 1 40   | Tsah   |           | 10   | _         | ns |

| Data setup time         | SI     | Tsds   |           | 20   | _         |    |

| Data hold time          | ] 31   | Тѕон   |           | 10   | _         |    |

| CS-SCL time             | CS     | Tcss   |           | 20   | _         | 1  |

| CS-SCL time             |        | Tosh   |           | 40   | _         | 7  |

| Item                    | Cianal | Signal Symbol Condition |           | Rat       | ing   | 11-14-       |  |

|-------------------------|--------|-------------------------|-----------|-----------|-------|--------------|--|

| item                    | Signai | Symbol                  | Condition | Min. Max. |       | Units        |  |

| 4-line SPI Clock Period |        | Tscyc                   |           | 200       | -     | 1            |  |

| SCL "H" pulse width     | SCL    | Тѕнѡ                    |           | 80        | _=    | ns           |  |

| SCL "L" pulse width     |        | Tstw                    |           | 80        | _     |              |  |

| Address setup time      | ۸٥     | Tsas                    |           | 60        | 1     |              |  |

| Address hold time       | A0     | Тѕан                    |           | 30        | T     |              |  |

| Data setup time         | SI     | Tsps                    |           | 60        |       |              |  |

| Data hold time          | 51     | Тѕон                    |           | 30        | 1 3-6 |              |  |

| CS-SCL time             | cs     | Tcss                    |           | 40        |       | XI.          |  |

| CS-SCL time             | CS     | Тсѕн                    |           | 100       |       | ) ( <u> </u> |  |

- $^{*}1$  The input signal rise and fall time (tr, tf) are specified at 15 ns or less.  $^{*}2$  All timing is specified using 20% and 80% of Vpp as the standard.

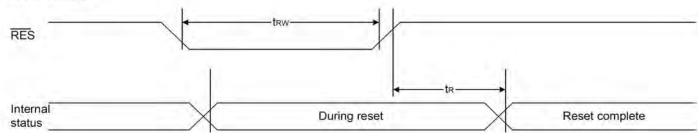

## **Reset Timing**

## **COMMAND TABLE**

#### (COMMAND FOR ST7565R)

| Command Code                                                            |    |     |     |     |     | - Function |              |             |                                |              |              |                                                                                                                                          |

|-------------------------------------------------------------------------|----|-----|-----|-----|-----|------------|--------------|-------------|--------------------------------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Command                                                                 | A0 | /RD | /WR | D7  | D6  | D5         | D4           | D3          | D2                             |              | D0           |                                                                                                                                          |

| (1) Display ON/OFF                                                      | 0  | 1   | 0   | 1   | 0   | 1          | 0            | 1           | 1                              | 1            | 0<br>1       | LCD display ON/OFF<br>0: OFF, 1: ON                                                                                                      |

| (2) Display start line set                                              | 0  | 1   | 0   | 0   | 1   |            | Displ        | ay st       | art a                          | ddre         | ss           | Sets the display RAM display start line address                                                                                          |

| (3) Page address set                                                    | 0  | 1   | 0   | 1   | 0   | 1          | 1            | Р           | age                            | addr         | ess          | Sets the display RAM page address                                                                                                        |

| (4) Column address set<br>upper bit<br>Column address set<br>lower bit  | 0  | 1   | 0   | 0   | 0   | 0          | 1            | co<br>Le    | ost s<br>lumr<br>ast s<br>lumr | add<br>ignif | ress<br>cant | Sets the most significant 4 bits of the display RAM column address. Sets the least significant 4 bits of the display RAM column address. |

| (5) Status read                                                         | 0  | 0   | 1   |     | Sta | itus       |              | 0           | 0                              | 0            | 0            | Reads the status data                                                                                                                    |

| (6) Display data write                                                  | 1  | 1   | 0   |     |     |            |              | W           | rite d                         | ata          |              | Writes to the display RAM                                                                                                                |

| (7) Display data read                                                   | 1  | 0   | 1   |     |     |            |              | Re          | ead d                          | ata          |              | Reads from the display RAM                                                                                                               |

| (8) ADC select                                                          | 0  | 1   | 0   | 1   | 0   | 1          | 0            | 0           | 0                              | 0            | 0            | Sets the display RAM address SEG output correspondence 0: normal, 1: reverse                                                             |

| (9) Display normal/<br>reverse                                          | 0  | 1   | 0   | 1   | 0   | 1          | 0            | 0           | 1                              | 1            | 0            | Sets the LCD display normal/ reverse 0: normal, 1: reverse                                                                               |

| (10) Display all points<br>ON/OFF                                       | 0  | 1   | 0   | 1   | 0   | 1          | 0            | 0           | 1                              | 0            | 0            | Display all points 0: normal display 1: all points ON                                                                                    |

| (11) LCD bias set                                                       | 0  | 1   | 0   | 1   | 0   | 1          | 0            | 0           | 0                              | 1            | 0            | Sets the LCD drive voltage bias ratio<br>0: 1/9 bias, 1: 1/7 bias (ST7565R)                                                              |

| (12) Read-modify-write                                                  | 0  | 1   | 0   | 1   | 1   | 1          | 0            | 0           | 0                              | 0            | 0            | Column address increment<br>At write: +1<br>At read: 0                                                                                   |

| (13) End                                                                | 0  | 1   | 0   | 1   | 1   | 1          | 0            | 1           | 1                              | 1            | 0            | Clear read/modify/write                                                                                                                  |

| (14) Reset                                                              | 0  | 1   | 0   | 1   | 1   | 1          | 0            | 0           | 0                              | 1            | 0            | Internal reset                                                                                                                           |

| (15) Common output mode select                                          | 0  | 1   | 0   | 1   | 1   | 0          | 0            | 0           | *                              | *            | *            | Select COM output scan direction 0: normal direction 1: reverse direction                                                                |

| (16) Power control set                                                  | 0  | 1   | 0   | 0   | 0   | 1          | 0            | 1           | 0                              | pera<br>mod  |              | Select internal power supply operating mode                                                                                              |

| (17) V <sub>0</sub> voltage<br>regulator internal<br>resistor ratio set | 0  | 1   | 0   | 0   | 0   | 1          | 0            | 0           | Re                             | sisto        | ratio        | Select internal resistor ratio(Rb/Ra) mode                                                                                               |

| (18) Electronic volume<br>mode set<br>Electronic volume                 | 0  | 1   | 0   | 1 0 | 0   | 0          | 0<br>Electro | 0<br>onic v | 0<br>volun                     | 0<br>ne va   | 1            | Set the V <sub>0</sub> output voltage electronic volume register                                                                         |

| register set (19) Static indicator                                      |    |     |     | 1   | 0   | 1          | 0            | 1           | 1                              | 0            | 0            | 0: OFF, 1: ON                                                                                                                            |

| ON/OFF<br>Static indicator                                              | 0  | 1   | 0   |     |     |            |              |             |                                |              | 1            | Sat the fleshing made                                                                                                                    |

| register set                                                            |    |     |     | 0   | 0   | 0          | 0            | 0           | 0                              |              | Mode         | select booster ratio                                                                                                                     |

| (20) Booster ratio set                                                  | 0  | 1   | 0   | 0   | 1   | 1          | 1            | 1           | 0                              |              | 0<br>p-up    | 00: 2x,3x,4x<br>01: 5x                                                                                                                   |

| (21) Power save                                                         | 0  | 1   | 0   |     |     |            |              |             |                                | V            | alue         | 11: 6x  Display OFF and display all                                                                                                      |

| (22) NOP                                                                | 0  | 1   | 0   | 1   | 1   | 1          | 0            | 0           | 0                              | 1            | 1            | points ON compound command  Command for non-operation                                                                                    |

| (23) Test                                                               | 0  | 1   | 0   | 1   | 1   | 1          | 1            | *           | *                              | *            | *            | Command for IC test. Do not use this command                                                                                             |

#### **LCD ARTWORK**

#### **SEG LAYOUT**

## **COM LAYOUT**

# DISPLAI

# **IC LAYOUT**

### **DESIGN • MANUFACTURE • SUPPLY**

## **RELIABILITY TEST**

Operating life time: Longer than 50000 hours

(at room temperature without direct irradiation of sunlight)

Reliability characteristics shall meet following requirements.

| TEMPERATURE TESTS               | NORMAL GRADE                                       |  |  |  |  |  |

|---------------------------------|----------------------------------------------------|--|--|--|--|--|

| High temperature storage        | +80°C * 96HR                                       |  |  |  |  |  |

| Low temperature storage         | -30°C * 96HR                                       |  |  |  |  |  |

| High temperature operation      | +70°C * 96HR                                       |  |  |  |  |  |

| Low temperature operation       | -20°C * 96HR                                       |  |  |  |  |  |

| High temperature, High humidity | +60℃ 90%RH 96HR                                    |  |  |  |  |  |

| Thermal shock                   | -20°C * 30 min ◀<br>10s ▼ 5Cycles<br>70°C * 30 min |  |  |  |  |  |

| Vibration test                  | Frequency * Swing * Time<br>40Hz * 4mm * 4hrs      |  |  |  |  |  |

| Drop test                       | Drop height * Times 1.0m * 6 times                 |  |  |  |  |  |

# **QUALITY DESCRIPTION & APPLICATION NOTE**

Please refer to "General Inspection Criteria" document

**DESIGN • MANUFACTURE • SUPPLY**