# 2-Channel, 300 mA Current Source Output 16-Bit SoftSpan DAC

#### **FEATURES**

- ▶ Per channel programmable output ranges: 300 mA, 200 mA, 100 mA, 50 mA, 25 mA, 12.5 mA, 6.25 mA, and 3.125 mA

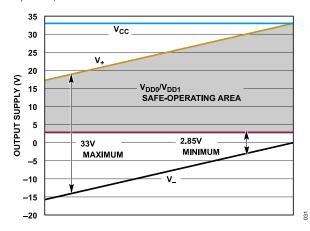

- ▶ Flexible 2.85 V to 33 V supply voltage

- 1 V dropout guaranteed

- Separate voltage supply per output channel

- Internal switches to optional negative supply

- ► Full 16-bit resolution at all ranges

- ▶ Guaranteed operation –40°C to 125°C

- ▶ Precision (10 ppm/°C maximum) internal reference or external reference input

- ▶ Analog mux monitors, voltages, and currents

- A/B toggle via SPI or dedicated pin

- ▶ 1.8 V to 5 V SPI

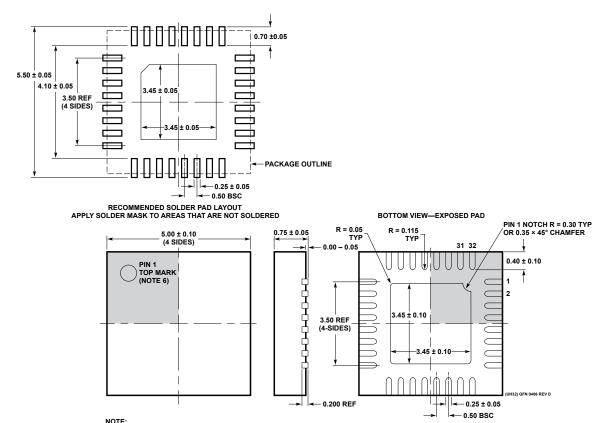

- ▶ 32-lead (5 mm × 5 mm) QFN package

#### **APPLICATIONS**

- ▶ Tunable lasers

- Semiconductor optical amplifiers

- Resistive heaters

- Current-mode biasing

- Proportional solenoid drive

## **GENERAL DESCRIPTION**

The AD5778R is a 2-channel, 16-bit current source digital-to-analog converter (DAC), providing two high-compliance current source outputs with a guaranteed 1 V dropout at 200 mA. The device supports load voltages of up to 32 V. There are eight current ranges, programmable per channel, with full-scale outputs of up to 300 mA. Additionally, the channels can be paralleled to allow for ultrafine adjustments of large currents or for combined outputs of up to 600 mA.

A dedicated supply pin is provided for every output channel. Each channel can be operated from 2.85 V to 33 V, and internal switches allow any output to be pulled to the optional negative supply.

The AD5778R includes a precision integrated 1.25 V reference (10 ppm/°C maximum), with the option to use an external reference.

The SPI-/Microwire-compatible 3-wire serial interface operates on logic levels as low as 1.71 V at clock rates up to 50 MHz.

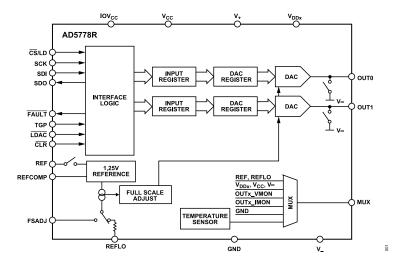

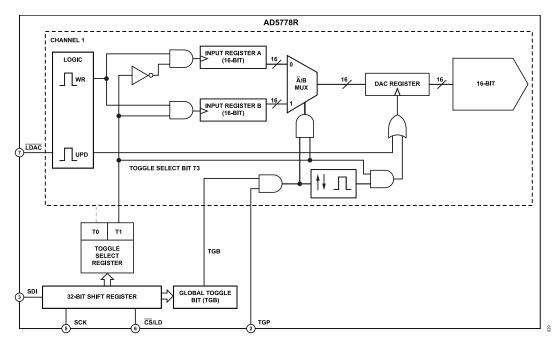

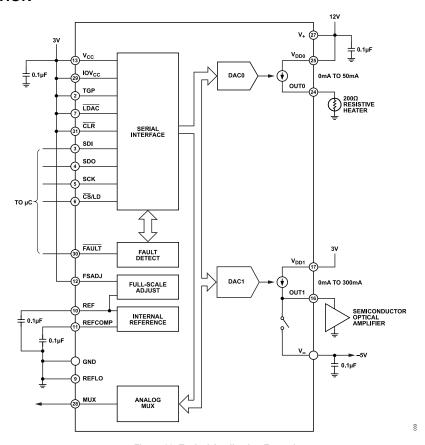

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

## **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Functional Block Diagram                     | 1  |

| Specifications                               | 3  |

| Timing Characteristics                       | 6  |

| Absolute Maximum Ratings                     | 8  |

| Thermal Resistance                           | 8  |

| Electrostatic Discharge (ESD) Ratings        | 8  |

| ESD Caution                                  | 8  |

| Pin Configuration and Function Descriptions. | 9  |

| Typical Performance Characteristics          | 11 |

| Theory of Operation                          | 14 |

| Power-On Reset                               | 14 |

| Power Supply Sequencing and Startup          | 14 |

| Data Transfer Functions                      | 14 |

| Serial Interface                             | 14 |

| Input and DAC Registers                      | 15 |

| Output Ranges and SoftSpan Operation         | 15 |

| Monitor Mux                                  | 17 |

|                                              |    |

| roggie Operations                   | 10 |

|-------------------------------------|----|

| Daisy-Chain Operation               | 20 |

| Echo Readback                       |    |

| Fault Register (FR)                 | 20 |

| CONFIG Command                      |    |

| Power-Down Mode                     | 22 |

| Switch to V_ Mode                   | 22 |

| Gain Adjustment Using the FSADJ Pin | 22 |

| Reference Modes                     | 22 |

| Applications Information            | 23 |

| Valid Supply Ranges                 |    |

| Current Outputs                     | 23 |

| Offset Current and Code Zero        |    |

| Board Layout                        | 23 |

| Typical Application                 |    |

| Related Products                    |    |

| Outline Dimensions                  |    |

| Ordering Guide                      |    |

| Evaluation Boards                   |    |

# **REVISION HISTORY**

4/2024—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 26

## **SPECIFICATIONS**

All specifications applied over the full operating  $T_J$  range, unless otherwise noted. Typical values are at  $T_J$  = 25°C,  $V_{CC}$  =  $IOV_{CC}$  = 5 V,  $V_-$  = -5 V,  $V_{DDX}$  = 5 V,  $V_+$  = 5 V, FSADJ =  $V_{CC}$ , and reference output voltage ( $V_{REF}$ ) = 1.25 V external, unless otherwise specified.

Table 1. Specifications

| Parameter                                                            | Symbol                | Test Conditions/Comments                                                                                                                     | Min   | Тур   | Max   | Unit   |

|----------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| DC PERFORMANCE, AD5778R                                              |                       |                                                                                                                                              |       |       |       |        |

| Resolution                                                           |                       |                                                                                                                                              | 16    |       |       | Bits   |

| Monotonicity                                                         |                       | All current ranges <sup>1</sup>                                                                                                              | 16    |       |       | Bits   |

| Differential Nonlinearity                                            | DNL                   | All current ranges <sup>1</sup>                                                                                                              | -1    | ±0.2  | +1    | LSB    |

| Integral Nonlinearity                                                | INL                   | All current ranges <sup>1</sup>                                                                                                              | -64   | ±12   | +64   | LSB    |

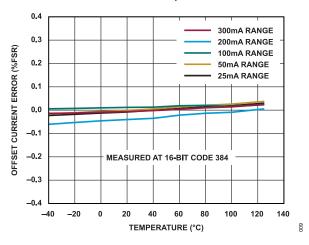

| Current Offset Error                                                 | I <sub>OS</sub>       | All current ranges <sup>1</sup>                                                                                                              | -0.4  | ±0.1  | +0.4  | %FSR   |

| I <sub>OS</sub> Temperature Coefficient                              |                       | All current ranges <sup>1</sup>                                                                                                              |       | ±10   |       | ppm/°C |

| Gain Error <sup>2</sup>                                              | GE                    | 300 mA and 200 mA output current ranges                                                                                                      | -0.9  | ±0.3  | +0.9  | %FSR   |

|                                                                      |                       | 100 mA, 50 mA, and 25 mA output current ranges                                                                                               | -1.2  | ±0.4  | +1.2  | %FSR   |

|                                                                      |                       | 12.5 mA, 6.25 mA, and 3.125 mA output current ranges                                                                                         | -1.5  | ±0.7  | +1.5  | %FSR   |

| Gain Temperature Coefficient                                         |                       | FSADJ = V <sub>CC</sub>                                                                                                                      |       | 30    |       | ppm/°C |

| Total Unadjusted Error <sup>2</sup>                                  | TUE                   | 300 mA and 200 mA output current ranges                                                                                                      | -1.4  | ±0.4  | +1.4  | %FSR   |

|                                                                      |                       | 100 mA, 50 mA, and 25 mA output current ranges                                                                                               | -1.7  | ±0.5  | +1.7  | %FSR   |

|                                                                      |                       | 12.5 mA, 6.25 mA, and 3.125 mA output current ranges                                                                                         | -2    | ±0.8  | +2    | %FSR   |

| Power Supply Rejection Ratio                                         | PSRR                  | Range = 100 mA, OUTx current (I <sub>OUTx</sub> ) = 50 mA                                                                                    |       |       |       |        |

|                                                                      |                       | V <sub>CC</sub> = 4.75 V to 5.25 V                                                                                                           |       | ±2.2  |       | LSB    |

|                                                                      |                       | V <sub>DDx</sub> = 2.85 V to 3.15 V                                                                                                          |       | ±0.6  |       | LSB    |

|                                                                      |                       | V <sub>DDx</sub> = 4.75 V to 5.25 V                                                                                                          |       | ±3.7  |       | LSB    |

|                                                                      |                       | V <sub>+</sub> = 4.75 V to 5.25 V                                                                                                            |       | ±0.09 |       | LSB    |

|                                                                      |                       | V <sub>-</sub> = -5.25 V to -4.75 V                                                                                                          |       | ±0.01 |       | LSB    |

| DC Crosstalk <sup>3</sup>                                            |                       | Result of a 50 mW change in dissipated power                                                                                                 |       | 3     |       | LSB    |

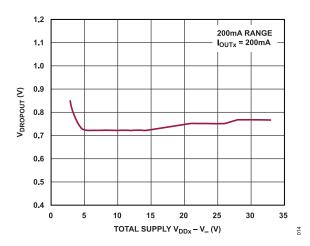

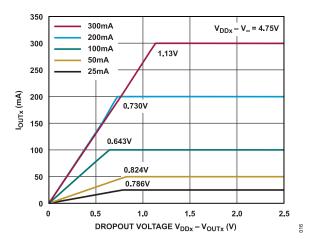

| Dropout Voltage (V <sub>DDx</sub> - V <sub>OUTx</sub> <sup>4</sup> ) | V <sub>DROPOUT</sub>  | 200 mA range, $(V_{DDx} - V_{-}) = 4.75 \text{ V}$                                                                                           |       | 0.72  | 1     | V      |

| 2. open venage (vDDX vooix /                                         | DROPOUT               | 200 mA range, $(V_{DDX} - V_{-}) = 2.85 \text{ V}$                                                                                           |       | 0.85  | ·     | V      |

|                                                                      |                       | 200 mA range, $(V_{DDX} - V_{-}) = 33 \text{ V}$                                                                                             |       | 0.76  | 1.1   | V      |

|                                                                      |                       | 300 mA range, (V <sub>DDx</sub> - V <sub>-</sub> ) = 4.75 V                                                                                  |       | 1.13  |       | v      |

|                                                                      |                       | 300 mA range, (V <sub>DDx</sub> - V <sub>-</sub> ) = 2.85 V                                                                                  |       | 1.35  | 1.95  | v      |

| High 7 Outmant Lankage Comments                                      |                       | , , , ,                                                                                                                                      | 1     |       |       |        |

| High-Z Output Leakage Current <sup>5</sup>                           |                       | $ OUTx = high-Z, 2.85V \le (V_{DDX} - V_{-}) \le 33V$                                                                                        | -1    | +0.1  | +1    | μA     |

| OUTx Switch to V_ Resistance to V_ Supply                            | R <sub>PULLDOWN</sub> | Span code = 1000b, sinking 80 mA                                                                                                             |       | 8     | 12    | Ω      |

| OUTx Switch to V₋ Current                                            | I <sub>PULLDOWN</sub> | Maximum allowable DC current                                                                                                                 |       |       | 80    | mA     |

| AC PERFORMANCE                                                       |                       | T <sub>A</sub> = 25°C for all ac performance specifications                                                                                  |       |       |       |        |

| Settling Time <sup>6, 7</sup>                                        | t <sub>SETTLE</sub>   |                                                                                                                                              |       |       |       |        |

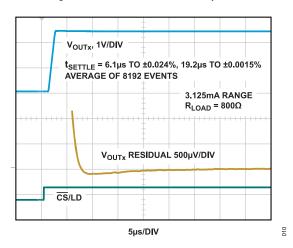

| Full-Scale Step 3.125 mA Range                                       |                       | ±0.0015% (±1 LSB at 16b)                                                                                                                     |       | 19.2  |       | μs     |

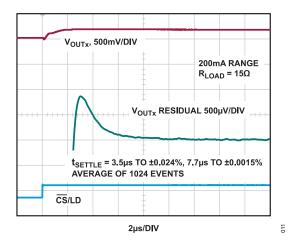

| 145 mA to 155 mA Step 200 mA Range                                   |                       | ±0.0015% (±1 LSB at 16b)                                                                                                                     |       | 7.7   |       | μs     |

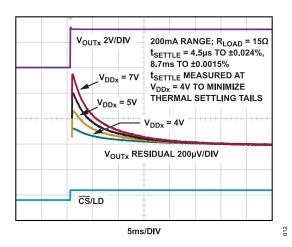

| Full-Scale Step 200 mA Range                                         |                       | ±0.0015% (±1 LSB at 16b)                                                                                                                     |       | 8.7   |       | ms     |

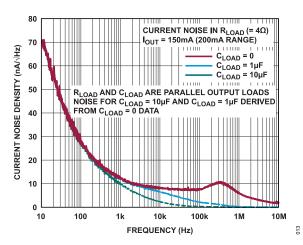

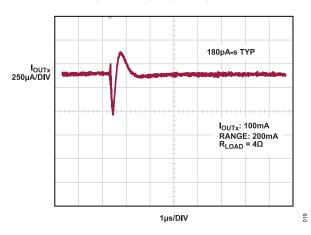

| Glitch Impulse                                                       |                       | At midscale transition, 200 mA range, and resistive load that connects the DAC output to GND ( $R_{LOAD}$ ) = 4 $\Omega$                     |       | 180   |       | pA × s |

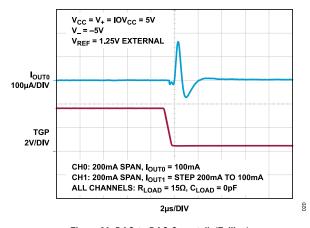

| DAC to DAC Crosstalk <sup>8</sup>                                    |                       | 100 mA to 200 mA step, $R_{LOAD}$ = 15 $\Omega$                                                                                              |       | 121   |       | pA × s |

| Noise Current                                                        | I <sub>NOISE</sub>    | Output current noise density internal reference, $I_{OUTx}$ = 150 mA, $R_{LOAD}$ = 4 $\Omega$ , load capacitance ( $C_{LOAD}$ ) = 10 $\mu$ F |       |       |       |        |

| Frequency (f) = 1 kHz                                                |                       |                                                                                                                                              |       | 12    |       | nA/√Hz |

| f = 10 kHz                                                           |                       |                                                                                                                                              |       | 5     |       | nA/√Hz |

| f = 100 kHz                                                          |                       |                                                                                                                                              |       | 0.5   |       | nA/√Hz |

| f = 1 MHz                                                            |                       |                                                                                                                                              |       | 0.05  |       | nA/√Hz |

| REFERENCE                                                            |                       |                                                                                                                                              |       |       |       |        |

| Internal Reference Mode                                              |                       |                                                                                                                                              |       |       |       |        |

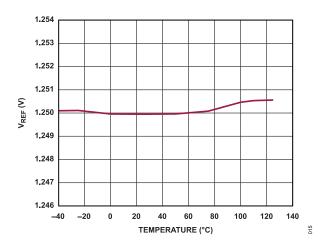

| Reference Output Voltage                                             | V <sub>REF</sub>      |                                                                                                                                              | 1.248 | 1.250 | 1.252 | V      |

analog.com Rev. 0 | 3 of 26

## **SPECIFICATIONS**

Table 1. Specifications (Continued)

| Parameter                                             | Symbol             | Test Conditions/Comments                                                                                   | Min                     | Тур   | Max             | Unit   |

|-------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------|-------------------------|-------|-----------------|--------|

| V <sub>REF</sub> Temperature Coefficient <sup>9</sup> |                    |                                                                                                            | -10                     | ±3    | +10             | ppm/°C |

| V <sub>REF</sub> Line Regulation                      |                    | V <sub>CC</sub> = 5 V ± 10%                                                                                |                         | 50    |                 | μV/V   |

| V <sub>REF</sub> Short-Circuit Current                |                    | V <sub>CC</sub> = 5.5 V, forcing output to GND                                                             |                         | 2.5   |                 | mA     |

| REFCOMP Pin Short-Circuit Current                     |                    | V <sub>CC</sub> = 5.5 V, forcing output to GND                                                             |                         | 65    |                 | μA     |

| V <sub>REF</sub> Load Regulation                      |                    | V <sub>CC</sub> = 5 V ± 10%, reference current (I <sub>REF</sub> ) = 100 μA sourcing                       |                         | 140   |                 | mV/mA  |

| V <sub>REF</sub> Output Voltage Noise Density         |                    | REFCOMP pin capacitance ( $C_{REFCOMP}$ ) = REF pin capacitance ( $C_{REF}$ ) = 0.1 $\mu$ F, at f = 10 kHz |                         | 32    |                 | nV/√Hz |

| External Reference Mode                               |                    |                                                                                                            |                         |       |                 |        |

| Reference Input Voltage                               |                    | REFCOMP pin is tied to GND                                                                                 | 1.225                   |       | 1.275           | ٧      |

| Input Current                                         |                    |                                                                                                            |                         | 0.001 | 1               | μA     |

| Input Capacitance <sup>10</sup>                       |                    |                                                                                                            |                         | 40    |                 | pF     |

| Full-Scale Adjust Resistor                            | R <sub>FSADJ</sub> | R <sub>FSADJ</sub> to GND                                                                                  | 19                      | 20    | 50              | kΩ     |

| DIGITAL INPUT AND OUTPUT                              | 1 OADS             | 1000 -                                                                                                     |                         |       |                 |        |

| Digital Output High Voltage                           | V <sub>OH</sub>    | SDO pin, load current = -100 μA                                                                            | IOV <sub>CC</sub> - 0.2 |       |                 | V      |

| Digital Output Low Voltage                            | V <sub>OL</sub>    | SDO pin, load current = 100 μA                                                                             | 10100 012               |       | 0.2             | V      |

| 2.g                                                   | 100                | FAULT pin, load current = 100 µA                                                                           |                         |       | 0.2             | V      |

| Digital High-Z Output Leakage Current                 |                    | SDO pin leakage current (CS/LD high)                                                                       | -1                      |       | +1              | μA     |

| Digital Fig. 2 Output 20allago Garront                |                    | FAULT pin leakage current (not asserted)                                                                   |                         |       | 1               | μA     |

| Digital Input Current                                 |                    | Input voltage (V <sub>IN</sub> ) = GND to IOV <sub>CC</sub>                                                | -1                      |       | +1              | μA     |

| Digital Input Capacitance <sup>10</sup>               | C <sub>IN</sub>    | input voltage (VIN)                                                                                        | '                       |       | 8               | pF     |

| High-Level Input Voltage                              | V <sub>IH</sub>    | 2.85 ≤ IOV <sub>CC</sub> ≤ V <sub>CC</sub>                                                                 | 0.8 × IOV <sub>CC</sub> |       | Ü               | V      |

| riigii-Leveriiiput voitage                            | ▼IH                | 1.71 ≤ IOV <sub>CC</sub> ≤ 2.85                                                                            | 0.8 × IOV <sub>CC</sub> |       |                 | V      |

| Low-Level Input Voltage                               | $V_{IL}$           | 2.85 ≤ IOV <sub>CC</sub> ≤ V <sub>CC</sub>                                                                 | 0.0 ~ 10 000            |       | 0.5             | V      |

| Low-Level Input Voltage                               | VIL.               | $1.71 \le 10V_{CC} \le 2.85$                                                                               |                         |       | 0.3             | V      |

| POWER SUPPLY                                          |                    | 1.77 = 10 700 = 2.00                                                                                       |                         |       | 0.0             |        |

| Analog Supply Voltage                                 | $V_{CC}$           | V <sub>CC</sub> must not exceed V <sub>+</sub>                                                             | 2.85                    |       | 5.5             | V      |

| Digital Input and Output Supply Voltage               | IOV <sub>CC</sub>  | · CCact.net execut 1.4                                                                                     | 1.71                    |       | V <sub>CC</sub> | V      |

| Negative Supply                                       | V_                 |                                                                                                            | -15.75                  |       | 0               | V      |

| Positive Supply                                       | V <sub>+</sub>     |                                                                                                            | 2.85                    |       | V_ + 33         | V      |

| Output Supply Voltages                                | $V_{DDx}$          |                                                                                                            | 2.85                    |       | V_ · 00         | V      |

|                                                       | ▼ DDX              |                                                                                                            | 2.00                    |       |                 |        |

| V <sub>CC</sub> Supply Current                        |                    | All ranges (code = 0, all channels)                                                                        |                         | 2.6   | 3.8             | mA     |

| IOV <sub>CC</sub> Supply Current                      |                    | All ranges (code = 0, all channels)                                                                        |                         | 0.01  | 1               | μA     |

| V <sub>+</sub> Supply Current                         |                    | All ranges (code = 0, all channels)                                                                        |                         | 385   | 500             | μA     |

| V <sub>−</sub> Supply Current                         |                    | All ranges (code = 0, all channels)                                                                        |                         | 2.3   | 3.2             | mA     |

| V <sub>DDx</sub> Supply Current                       |                    | All ranges (code = 0, per channel)                                                                         |                         | 0.7   | 1.2             | mA     |

|                                                       |                    | 25 mA range (code = full-scale, per channel) <sup>11</sup>                                                 |                         | 26.5  | 27.6            | mA     |

|                                                       |                    | 200 mA range (code = full-scale, per channel)                                                              |                         | 204   | 207             | mA     |

| V <sub>CC</sub> Shutdown Current <sup>12, 13</sup>    | I <sub>SLEEP</sub> |                                                                                                            |                         | 1     | 10              | μA     |

| IOV <sub>CC</sub> Shutdown Current                    |                    |                                                                                                            |                         | 0.01  | 1               | μA     |

| V <sub>+</sub> Shutdown Current                       |                    |                                                                                                            |                         | 20    | 36              | μA     |

| V₋ Shutdown Current                                   |                    |                                                                                                            |                         | 30    | 59              | μA     |

| V <sub>DDx</sub> Shutdown Current                     |                    | Per channel                                                                                                |                         | 4.2   | 8.1             | μA     |

| MONITOR MULTIPLEXER                                   |                    |                                                                                                            |                         |       |                 |        |

| MUX Pin DC Output Impedance                           |                    |                                                                                                            |                         | 15    |                 | kΩ     |

| MUX Pin Leakage Current                               |                    | Monitor multiplexer disabled (high impedance)                                                              | -1                      | +0.1  | +1              | μA     |

| MUX Pin Output Voltage Range                          |                    | Monitor multiplexer selected to OUT0 pin voltage or OUT1 pin voltage                                       | V_                      |       | $V_{+}$         | V      |

analog.com Rev. 0 | 4 of 26

### **SPECIFICATIONS**

#### Table 1. Specifications (Continued)

| Parameter                                | Symbol | Test Conditions/Comments              | Min | Тур | Max | Unit |

|------------------------------------------|--------|---------------------------------------|-----|-----|-----|------|

| MUX Pin Continuous Current <sup>10</sup> |        | T <sub>A</sub> = 25°C (do not exceed) | -1  |     | +1  | mA   |

- 1 The current offset error is measured at Code 384 for the AD5778R. Linearity is defined from Code 384 to Code 65535 for the AD5778R.

- <sup>2</sup> For the full-scale current (I<sub>FS</sub>) = 300 mA, R<sub>LOAD</sub> = 10  $\Omega$ . For I<sub>FS</sub> = 200 mA, R<sub>LOAD</sub> = 15  $\Omega$ . For I<sub>FS</sub> = 100 mA, R<sub>LOAD</sub> = 30  $\Omega$ . For I<sub>FS</sub> = 50 mA, R<sub>LOAD</sub> = 50  $\Omega$ . For I<sub>FS</sub> = 25 mA, R<sub>LOAD</sub> = 100  $\Omega$ . For I<sub>FS</sub> = 12.5 mA, R<sub>LOAD</sub> = 200  $\Omega$ . For I<sub>FS</sub> = 6.25 mA, R<sub>LOAD</sub> = 400  $\Omega$ . For I<sub>FS</sub> = 3.125 mA, R<sub>LOAD</sub> = 800  $\Omega$ .

- <sup>3</sup> I<sub>FS</sub> = 200 mA and R<sub>LOAD</sub> = 15 Ω. The DC crosstalk is measured with a 100 mA to 200 mA current step on an aggressor channel. The monitor channel is held at 3/4 × I<sub>FS</sub> or 150 mA

- V<sub>OUTx</sub> is the channel output (OUTx) voltage.

- <sup>5</sup> The loads attached to the OUTx pins must be terminated to GND.

- 6 V<sub>DDx</sub> = 5 V (3.125 mA range), V<sub>DDx</sub> = 4 V (200 mA range), and V<sub>−</sub> = −5 V for all ranges. For large current output steps, the internal thermal effects result in a final settling tail. In most cases, the tail is too small to affect settling to ±0.024%, but several milliseconds can be needed for full settling to the ±0.0015% level. For optimal results, solder or via all GND and REFLO pins, as well as the exposed pad, to a solid GND plane, and set VDDx as low as practicable for each channel to reduce power dissipation in the device.

- <sup>7</sup> Internal reference mode. The load is 15  $\Omega$  (200 mA range) or 800  $\Omega$  (3.125 mA range) in parallel with 100 pF terminated to GND.

- B DAC to DAC crosstalk is the glitch that appears at the output of one DAC because of a 100 mA to 200 mA step change in an adjacent DAC channel or vice versa. The measured DAC is at midscale (100 mA output current) in the 200 mA span range, with the internal reference, V<sub>DDx</sub> = 5 V, V<sub>−</sub> = −3.3 V.

- <sup>9</sup> The temperature coefficient is calculated by first computing the ratio of the maximum change in the output voltage to the nominal output voltage and then dividing the ratio by the specified temperature range.

- <sup>10</sup> Guaranteed by design and not production tested.

- <sup>11</sup> Single channel at a specified output.

- $^{12}$  V<sub>CC</sub> = IOV<sub>CC</sub> = 5 V, V<sub>DDx</sub> = 5 V, and V<sub>-</sub> = -5 V.

- <sup>13</sup> Digital inputs are at 0 V or IOV<sub>CC</sub>.

analog.com Rev. 0 | 5 of 26

## **SPECIFICATIONS**

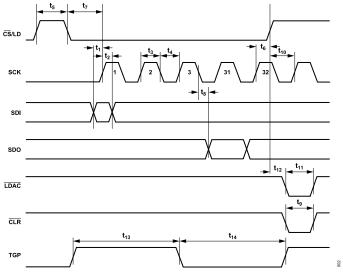

# **TIMING CHARACTERISTICS**

All specifications apply over the full operating  $T_J$  range, unless otherwise noted. Typical values are at  $T_J$  = 25°C, unless otherwise specified. Digital input low and high voltages are 0 V and IOV<sub>CC</sub>, respectively.

Table 2. Timing Characteristics

|                |                                                                        |                                                         | V <sub>+</sub> = V <sub>DDx</sub> = V <sub>CC</sub> = 2.85 V to<br>5.5 V, IOV <sub>CC</sub> = 2.85 V to V <sub>CC</sub> |     |     |     |     |     |      |

|----------------|------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|------|

| Symbol         | Parameter                                                              | Test Conditions/Comments                                | Min                                                                                                                     | Тур | Max | Min | Тур | Max | Unit |

| t <sub>1</sub> | SDI Valid to SCK Setup                                                 |                                                         | 6                                                                                                                       |     |     | 7   |     |     | ns   |

| $t_2$          | SDI Valid to SCK Hold                                                  |                                                         | 6                                                                                                                       |     |     | 7   |     |     | ns   |

| t <sub>3</sub> | SCK HIGH Time                                                          |                                                         | 9                                                                                                                       |     |     | 30  |     |     | ns   |

| $t_4$          | SCK LOW Time                                                           |                                                         | 9                                                                                                                       |     |     | 30  |     |     | ns   |

| 5              | CS/LD Pulse Width                                                      |                                                         | 10                                                                                                                      |     |     | 15  |     |     | ns   |

| 6              | LSB SCK High to CS/LD High                                             |                                                         | 19                                                                                                                      |     |     | 19  |     |     | ns   |

| 7              | CS/LD Low to SCK High                                                  |                                                         | 7                                                                                                                       |     |     | 7   |     |     | ns   |

| 8              | SDO Propagation Delay from SCK Falling Edge, C <sub>LOAD</sub> = 10 pF | $4.5 \text{ V} \leq \text{IOV}_{CC} \leq \text{V}_{CC}$ |                                                                                                                         |     | 20  |     |     |     | ns   |

|                |                                                                        | 2.85 V ≤ IOV <sub>CC</sub> < 4.5 V                      |                                                                                                                         |     | 30  |     |     |     | ns   |

|                |                                                                        | 1.71 V ≤ IOV <sub>CC</sub> < 2.85 V                     |                                                                                                                         |     |     |     |     | 60  | ns   |

| 9              | CLR Pulse Width                                                        |                                                         | 20                                                                                                                      |     |     | 30  |     |     | ns   |

| 10             | CS/LD High to SCK Positive Edge                                        |                                                         | 7                                                                                                                       |     |     | 7   |     |     | ns   |

| 12             | LDAC Pulse Width                                                       |                                                         | 15                                                                                                                      |     |     | 15  |     |     | ns   |

| 13             | CS/LD High to LDAC High or Low Transition                              |                                                         | 15                                                                                                                      |     |     | 15  |     |     | ns   |

|                | SCK Frequency                                                          | 50% Duty Cycle                                          |                                                                                                                         |     | 50  |     |     | 15  | MHz  |

| 14             | TGP High Time <sup>1</sup>                                             |                                                         | 1                                                                                                                       |     |     | 1   |     |     | μs   |

| 15             | TGP Low Time <sup>1</sup>                                              |                                                         | 1                                                                                                                       |     |     | 1   |     |     | μs   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and not production tested.

# **Timing Diagrams**

Figure 2. Serial Interface Timing

analog.com Rev. 0 | 6 of 26

## **SPECIFICATIONS**

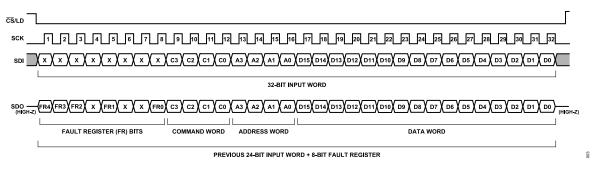

Figure 3. AD5778R 32-Bit Load Sequence

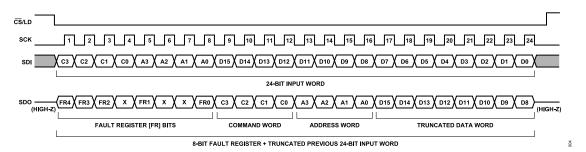

Figure 4. AD5778R 24-Bit Load Sequence

analog.com Rev. 0 | 7 of 26

### **ABSOLUTE MAXIMUM RATINGS**

Table 3. Absolute Maximum Ratings

| Parameter                                                                                                        | Rating                                                   |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| V <sub>CC</sub> to GND                                                                                           | -0.3 V to +6 V                                           |

| IOV <sub>CC</sub> to GND                                                                                         | -0.3 V to +6 V                                           |

| V_ to GND                                                                                                        | -16.5 V to +0.3 V                                        |

| V₊ to GND                                                                                                        | -0.3 V to (V_ + 36 V)                                    |

| V <sub>DDx</sub> to GND                                                                                          | -0.3 V to (V <sub>+</sub> + 0.3 V)                       |

| Output Supply Voltages to GND                                                                                    |                                                          |

| OUT0, OUT1                                                                                                       | $(V_{-} - 0.3 \text{ V})$ to $(V_{DDx} + 0.3 \text{ V})$ |

| MUX                                                                                                              | $(V_{-} - 0.3 \text{ V})$ to $(V_{+} + 0.3 \text{ V})$   |

| REF, REFCOMP, and FSADJ to GND                                                                                   | -0.3 V to minimum (V <sub>CC</sub> + 0.3 V, 6 V)         |

| $\overline{\text{CS}}\text{/LD}$ , SCK, SDI, $\overline{\text{LDAC}}$ , $\overline{\text{CLR}}$ , and TGP to GND | -0.3 V to +6 V                                           |

| FAULT to GND                                                                                                     | -0.3 V to +6 V                                           |

| SDO to GND                                                                                                       | -0.3 V to minimum (IOV <sub>CC</sub> + 0.3 V, 6 V)       |

| Temperature                                                                                                      | ·                                                        |

| Operating T <sub>J</sub> Range                                                                                   | -40°C to +125°C                                          |

| Maximum T <sub>J</sub>                                                                                           | 150°C                                                    |

| Storage Range                                                                                                    | -65°C to +150°C                                          |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

Thermal characteristics are specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. Thermal resistance values specified in Table 4 are simulated based on JEDEC specifications using a 2S2P thermal test board (see JEDEC JESD51), except for  $\theta_{\text{JC-TOP}},$  which uses a JEDEC 1S test board.

$\theta_{JA}$  is the junction to ambient thermal resistance, measured in a JEDEC natural convection environment.

$\theta_{\text{JC-TOP}}$  is the junction to case thermal resistance, measured at the center of the package top surface, with an infinite heat sink attached to the package surface.

$\theta_{JB}$  is the junction to board thermal resistance, measured at a point on the board 1 mm from the package edge, along the package center line, measured in a JEDEC  $\theta_{JB}$  environment.

$\Psi_{JB}$  is the junction to board thermal characterization parameter, measured in a JEDEC natural convection environment.

$\Psi_{JT}$  is the junction to package top thermal characterization parameter, measured in a JEDEC natural convection environment.

Do not use  $\theta_{JA}$ ,  $\theta_{JC\text{-}TOP}$ , and  $\theta_{JB}$  thermal resistances to perform direct calculation or measurement of the die temperature because doing so results in incorrect values. The thermal resistances assume 100% of the power that is dissipated along the specified path between the measurement points. The thermal resistances are directly dependent on the PCB design and environment.

If direct measurement of the package is required, the  $\Psi_{JT}$  and  $\Psi_{JB}$  values must be used because those values more accurately reflect the true thermal dissipation paths.

$\theta_{\text{JC-TOP}}$  must only be used where an external heat sink is attached directly to the package.

System level thermal simulation is highly recommended.

For more details about the thermal resistances, refer to *JE-DEC51-12*: Guidelines for Reporting and Using Electronic Package Thermal Information.

Table 4. Thermal Resistance

| Package Type            | $\theta_{JA}$ | $\theta_{JB}$ | θ <sub>JC-TOP</sub> | $\Psi_{JT}$ | $\Psi_{JB}$ | Unit |

|-------------------------|---------------|---------------|---------------------|-------------|-------------|------|

| 05-08-1693 <sup>1</sup> | 28.34         | 9.27          | 17.33               | 0.11        | 9.20        | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on JEDEC 2S2P thermal test board with no bias. See JEDEC JESD-51.

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charged device model (FICDM) per ANSI/ESDA/JE-DEC JS-002.

## **ESD Ratings for AD5778R**

Table 5. AD5778R, 32-Lead QFN

| ESD Model | Withstand Voltage (V) | Class |

|-----------|-----------------------|-------|

| HBM       | 3000                  | 2     |

| FICDM     | 1500                  | C3    |

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 8 of 26

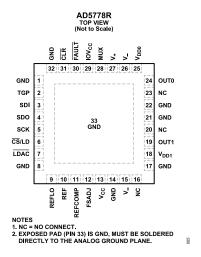

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

Table 6. Pin Function Descriptions

| Pin No.                  | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 8, 14, 17, 21, 22, 32 | GND      | Ground. The ground pins and the exposed pad must be tied directly to a solid ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

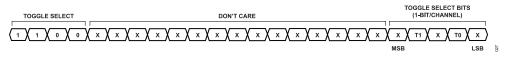

| 2                        | TGP      | Asynchronous Toggle Pin. A falling edge updates the DAC register with data from Input Register A. A rising edge updates the DAC register with data from Input Register B. Toggle operations only affect those DAC channels with their toggle select bit (Tx) set to 1. Tie the TGP pin to IOV <sub>CC</sub> when toggle operations are done through software. Tie the TGP pin to GND if the toggle operations are unused. The logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                          |

| 3                        | SDI      | Serial Data Input. Data on the SDI is clocked into the DAC on the rising edge of the SCK. The AD5778R accepts input word lengths of 24, 32, or multiples of 32 bits. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4                        | SDO      | Serial Data Output. The serial output of the 32-bit shift register appears at the SDO pin. The data transferred to the device via the SDI pin is delayed 32 SCK rising edges before being output at the next falling edge. The SDO pin can be used for data echo readback or daisy-chain operation and becomes high impedance when $\overline{\text{CS}}/\text{LD}$ is high. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                           |

| 5                        | SCK      | Serial Clock Input. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6                        | CS/LD    | Serial Interface Chip Select/Load Input. When the $\overline{\text{CS}}/\text{LD}$ is low, SCK is enabled for shifting SDI data into the register. In addition, the SDO is enabled when the $\overline{\text{CS}}/\text{LD}$ is low. When the $\overline{\text{CS}}/\text{LD}$ is taken high, the SDO and SCK are disabled, and the specified command (see Table 7) is executed. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                       |

| 7                        | LDAC     | Active Low Asynchronous DAC Update Pin. The $\overline{\text{LDAC}}$ pin allows updates independent of SPI timing. If the $\overline{\text{CS}/\text{LD}}$ is high, a falling edge on the $\overline{\text{LDAC}}$ updates all DAC registers with the contents of the input registers. The $\overline{\text{LDAC}}$ is gated by the $\overline{\text{CS}/\text{LD}}$ and has no effect if $\overline{\text{CS}/\text{LD}}$ is low. Logic levels are determined by $ \text{OV}_{\text{CC}} $ . If not used, tie the $\overline{\text{LDAC}}$ to $ \text{OV}_{\text{CC}} $ .                                                                                                                                                                                                |

| 9                        | REFLO    | Reference Low. Signal ground for the reference. Tie the REFLO pin directly to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10                       | REF      | Reference Input and Output. The voltage at the REF pin proportionally scales the full-scale output current of each DAC output channel. By default, the internal 1.25 V reference is routed to the REF pin. The REF pin must be buffered when driving external DC load currents. If the reference is disabled (see the Reference Modes section in the Theory of Operation section), the output is disconnected, and the REF pin becomes a high-impedance input that accepts a precision external reference. For low noise and reference stability, tie a capacitor from the REF pin to GND. The value must be less than the capacitance tied to the REFCOMP pin (C <sub>REFCOMP</sub> ). The allowable external reference input range is 1.225 V to 1.275 V.               |

| 11                       | REFCOMP  | Internal Reference Compensation Pin. For low noise and reference stability, tie a 0.1 µF capacitor from the REFCOMP pin to GND. Tying the REFCOMP pin to GND causes the device to power up with the internal reference disabled, which allows the use of an external reference at startup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12                       | FSADJ    | Full-Scale Current Adjust Pin. The FSADJ pin is used either to produce nominal, internally-calibrated output ranges or to produce incrementally-tunable ranges. In either case, the $V_{REF}$ is forced across a resistor ( $R_{FSADJ}$ ) to define a reference current that scales the outputs for all ranges and channels. Full-scale currents are proportional to the voltage at the REF pin and inversely proportional to $R_{FSADJ}$ . If FSADJ is tied to $V_{CC}$ , an internal $R_{FSADJ}$ (20 k $\Omega$ ) is selected, resulting in nominal output ranges. An external resistor of 19 k $\Omega$ to 41 k $\Omega$ can be used instead by simply connecting the resistor between the FSADJ pin and GND. In this case, the external resistor controls the scaling |

analog.com Rev. 0 | 9 of 26

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 6. Pin Function Descriptions (Continued)

| Pin No.    | Mnemonic               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                        | of ranges, and the internal resistor is automatically disconnected. See Table 9 for details. When using an external resistor, FSADJ is sensitive to stray capacitance, and the pin should be compensated with a snubber network consisting of a series combination of 1 k $\Omega$ and 1 $\mu$ F, connected in parallel to R <sub>FSADJ</sub> . With the recommended compensation, the FSADJ pin is stable, driving stray capacitance of up to 50 pF. |

| 13         | V <sub>CC</sub>        | Analog Supply Voltage. 2.85 V $\leq$ V <sub>CC</sub> $\leq$ 5.5 V. Bypass to GND with a 1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                          |

| 15, 26     | V_                     | Negative Supply Voltage. $-15.75 \text{ V} \le \text{V}\_ \le \text{GND}$ . Bypass to GND with a 1 $\mu\text{F}$ capacitor unless V $\_$ is connected to GND.                                                                                                                                                                                                                                                                                         |

| 16, 20, 23 | NC                     | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 18, 25     | $V_{DD1}$ to $V_{DD0}$ | Output Supply Voltages. 2.85 V $\leq$ V <sub>DD0/1</sub> $\leq$ V <sub>+</sub> . These two positive supply inputs provide independent supplies for each of the two DAC current output pins, OUT0 and OUT1, respectively. Bypass each supply input to GND separately with a 1 $\mu$ F capacitor.                                                                                                                                                       |

| 19, 24     | OUT1 to OUT0           | DAC Analog Current Outputs. Each current output pin has a dedicated analog supply pin, $V_{DD0}$ and $V_{DD1}$ . The operational voltage level range at these pins is $V_{-} \le V_{OUTx} \le V_{DDx}$ .                                                                                                                                                                                                                                              |

| 27         | V <sub>+</sub>         | Positive Supply Voltage. 2.85 V $\leq$ V <sub>+</sub> $\leq$ V <sub>-</sub> + 33 V. The V <sub>+</sub> must always be greater than or equal to the largest of the two DAC positive supply voltages (V <sub>DD0</sub> and V <sub>DD1</sub> ) and V <sub>CC</sub> . The supply voltage difference (V <sub>+</sub> – V <sub>-</sub> ) cannot exceed 33 V maximum. Bypass to GND with a 1 $\mu$ F capacitor.                                              |

| 28         | MUX                    | Analog Multiplexer Output. Pin voltages and currents can be monitored by measuring the voltage at the MUX pin. When the multiplexer (mux) is disabled, the MUX pin becomes high impedance. The available mux selections are given in Table 10.                                                                                                                                                                                                        |

| 29         | IOV <sub>CC</sub>      | Digital Input and Output Supply Voltage. 1.71 V ≤ IOV <sub>CC</sub> ≤ V <sub>CC</sub> + 0.3 V. Bypass to GND with a 0.1 μF capacitor.                                                                                                                                                                                                                                                                                                                 |

| 30         | FAULT                  | Active-Low Fault Detection Pin. This open-drain N-channel output pulls low when any valid fault condition is detected. The $\overline{\text{CLR}}$ pin is released on the next $\overline{\text{CS}}/\text{LD}$ rising edge. A pull-up resistor is required.                                                                                                                                                                                          |

| 31         | CLR                    | Active-Low Asynchronous Clear Input. A logic low at this level-triggered input clears the device to the default reset code and output ranges, which are zero-scale and high-impedance (high-Z) outputs. The control registers are cleared to zero. Logic levels are determined by IOV <sub>CC</sub> .                                                                                                                                                 |

| 33         | EXPOSED PAD            | Ground. Solder this pad directly to the analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                          |

analog.com Rev. 0 | 10 of 26

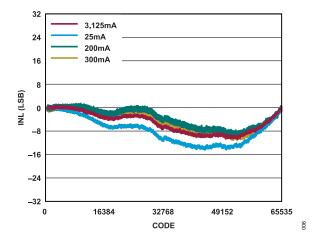

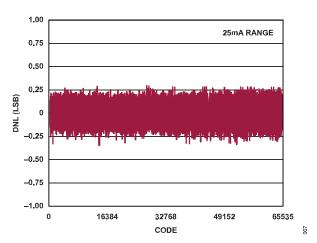

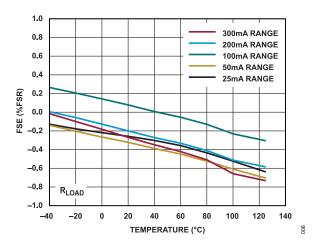

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{CC} = IOV_{CC} = 5 \text{ V}, V_{-} = -5 \text{ V}, V_{DDx} = 5 \text{ V}, V_{+} = 5 \text{ V}, FSADJ = V_{CC}, and V_{REF} = 1.25 \text{ V} external unless otherwise specified.}$

Figure 6. AD5778R Integral Nonlinearity (INL)

Figure 7. AD5778R Differential Nonlinearity (DNL)

Figure 8. Full-Scale Current Error (FSE) vs. Temperature

Figure 9. Offset Current Error vs. Temperature

Figure 10. Settling 0 mA to 3.125 mA Step

Figure 11. Settling 145 mA to 155 mA Step

analog.com Rev. 0 | 11 of 26

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 12. Settling 0 mA to 200 mA Step

Figure 13. Current Noise Density vs. Frequency

Figure 14. V<sub>DROPOUT</sub> vs. Total Supply Voltage

Figure 15. V<sub>REF</sub> vs. Temperature

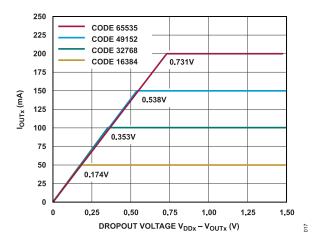

Figure 16. I<sub>OUTx</sub> vs. V<sub>DROPOUT</sub>

Figure 17. I<sub>OUTx</sub> vs. V<sub>DROPOUT</sub>, 200 mA Range

analog.com Rev. 0 | 12 of 26

## TYPICAL PERFORMANCE CHARACTERISTICS

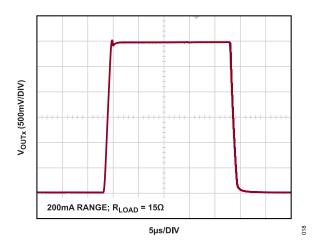

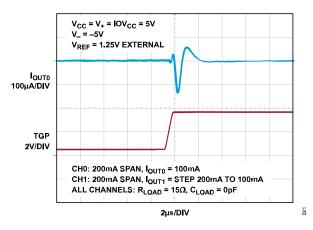

Figure 18. Large Signal Response

Figure 19. Midscale Glitch

Figure 20. DAC-to-DAC Crosstalk (Falling)

Figure 21. DAC-to-DAC Crosstalk (Rising)

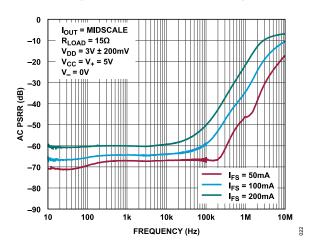

Figure 22. AC PSRR vs. Frequency

analog.com Rev. 0 | 13 of 26

#### THEORY OF OPERATION

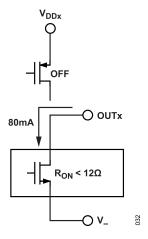

The AD5778R is a 2-channel, current source output DAC with selectable output ranges, precision reference, and a high-voltage mux for surveying the channel output voltages and currents. Each output draws current from a separate dedicated positive supply pin that accepts voltages of 2.85 V to 33 V, allowing the optimization of power dissipation and headroom for a wide range of loads. Internal 12  $\Omega$  switches allow any output pin to be connected to an optional negative V<sup>-</sup> supply voltage and sink up to 80 mA.

### **POWER-ON RESET**

The outputs reset to a high-impedance state on power up, making the system initialization consistent and repeatable. After power-on initialization, select the output range via SPI bus using Table 7, Table 8, and Table 9.

#### POWER SUPPLY SEQUENCING AND STARTUP

The supplies ( $V_{CC}$ ,  $IOV_{CC}$ ,  $V_+$ ,  $V_-$ ,  $V_{DD0}$ , and  $V_{DD1}$ ) may be powered up in any convenient order. If an external reference is used, do not allow the input voltage at the REF pin to rise above  $V_{CC}$  + 0.3 V during supply turn-on and turn-off sequences (see the Absolute Maximum Ratings section).

After startup, the  $IOV_{CC}$  must be within the  $V_{CC}$ , and supplies must not exceed the  $V_+$ . DC reference voltages of 1.225 V to 1.275 V are acceptable.

Supply bypassing is critical to achieving the best possible performance. Use at least 1  $\mu$ F of low-effective series resistance (ESR) capacitance to ground on all supply pins, and position the capacitor as close to the device as possible. A 0.1  $\mu$ F capacitor may be used for the IOV<sub>CC</sub>.

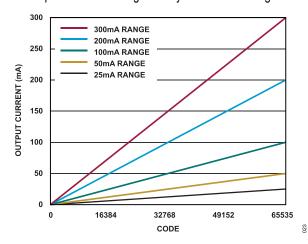

## **DATA TRANSFER FUNCTIONS**

The DAC input-to-output transfer functions for all resolutions and output ranges greater than or equal to 25 mA are shown in Figure 23. The input code is in straight binary format for all ranges.

Figure 23. AD5778R Transfer Function

#### SERIAL INTERFACE

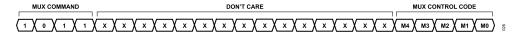

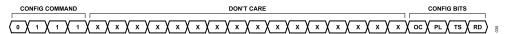

When the  $\overline{\text{CS}}/\text{LD}$  pin is taken low, the data on the SDI pin is loaded into the shift register on the rising edge of the clock (the SCK pin). The 4-bit command [C3:C0] is loaded first, followed by the 4-bit DAC address [A3:A0], and finally, the 16-bit data word in straight binary format. For the AD5778R, the data word comprises the 16-bit input code, ordered MSB-to-LSB. Data can only be transferred to the AD5778R when the  $\overline{\text{CS}}/\text{LD}$  signal is low. The rising edge of  $\overline{\text{CS}}/\text{LD}$  ends the data transfer and causes the device to carry out the action specified in the 24-bit input word.

**Table 7. Command Codes**

|        | Co | mmand |    |                                          |

|--------|----|-------|----|------------------------------------------|

| C3     | C2 | C1    | C0 |                                          |

| 0      | 0  | 0     | 0  | Write code to n                          |

| 1      | 0  | 0     | 0  | Write code to all                        |

| 0      | 1  | 1     | 0  | Write span to n                          |

| 0      | 0  | 0     | 1  | Update n (power up)                      |

| 1      | 0  | 0     | 1  | Update all (power up)                    |

| 0      | 0  | 1     | 1  | Write code to n, update n (power up)     |

| 0      | 0  | 1     | 0  | Write code to n, update all (power up)   |

| 1      | 0  | 1     | 0  | Write code to all, update all (power up) |

| 0      | 1  | 0     | 0  | Power down n                             |

| 0      | 1  | 0     | 1  | Power down chip                          |

| 1      | 0  | 1     | 1  | Monitor mux                              |

| 1      | 1  | 0     | 0  | Toggle select                            |

| 1      | 1  | 0     | 1  | Global toggle                            |

| 0      | 1  | 1     | 1  | CONFIG command                           |

| 1      | 1  | 1     | 1  | No operation                             |

| Others |    |       |    | Invalid command codes                    |

Table 8. DAC Addresses, n

| Address <sup>1</sup> |    |            |    |                       |

|----------------------|----|------------|----|-----------------------|

| А3                   | A2 | <b>A</b> 1 | Α0 |                       |

| 0                    | 0  | 0          | 0  | DAC 0                 |

| 0                    | 0  | 1          | 1  | DAC 1                 |

| Others               |    |            |    | Invalid DAC addresses |

Any DAC address code used other than the codes given in Table 8 causes the command to be ignored.

While the minimum input word is 24 bits, it may optionally be extended to 32 bits. To use the 32-bit word width, 8 don't care bits must be transferred to the device first, followed by the 24-bit word, as described earlier in this section. The 32-bit word is required for daisy-chain operation. It also provides accommodation for processors that have a minimum word width of 16 or more bits. The complete 24-bit and 32-bit sequences are shown in Figure 3 and Figure 4. Note that the fault register outputs appear on the SDO pin for either word width.

analog.com Rev. 0 | 14 of 26

### THEORY OF OPERATION

Note that any write to invalid command codes or invalid DAC addresses can result in unexpected device behavior or fault conditions. It is recommended to avoid writing to invalid command codes and invalid DAC addresses. Reset the device in case of any write to invalid command codes or invalid DAC addresses.

#### INPUT AND DAC REGISTERS

The AD5778R has five internal registers for each DAC, in addition to the main shift register. Each DAC channel has two sets of double-buffered registers: one set for the code data and one set for the span (output range) of the DAC. Double buffering provides the capability to simultaneously update the span and code, which allows smooth current transitions when changing output ranges. It also permits the simultaneous updating of multiple DACs.

Each set of double-buffered registers comprises an input register and a DAC register as follows:

- ▶ Input register: The write operation shifts data from the SDI pin into a chosen register. The input registers are holding buffers, and write operations do not affect the DAC outputs. In the code data path, there are two input registers, A and B, for each DAC register. Register B is an alternate register used only in the toggle operation, while Register A is the default input register.

- DAC register: The update operation copies the contents of an input register to the associated DAC register. The content of a DAC register directly controls the DAC output current or range. The update operation also powers up the selected DAC if it had been in power-down mode.

Note that updates always refresh both code and span data, but the values held in the DAC registers remain unchanged unless the associated input register values have been changed via a write operation. For example, if a new code is written and the channel updated, the code is updated while the span is refreshed unchanged. A channel update can come from a serial update command, an  $\overline{\text{LDAC}}$  negative pulse, or a toggle operation.

# OUTPUT RANGES AND SOFTSPAN OPERATION

The AD5778R is a 2-channel current DAC with selectable output ranges. The full set of current output ranges is available only through SPI programming.

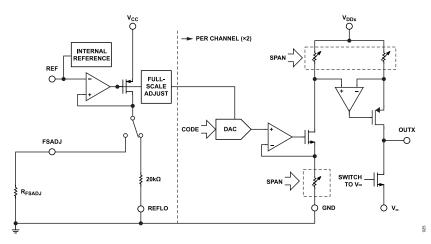

Figure 25 shows a simplified diagram of a single channel of the AD5778R. The full-scale current range of the AD5778R is selected via four control bits [S3:S0] on a per channel basis. Also included is the ability to provide an external reference or to use a precision external resistor at Pin FSADJ to reduce the overall gain drift over temperature of the AD5778R.

The AD5778R initializes at power on with all channel outputs (OUT0 and OUT1) at high-Z. The range and code of each channel are then fully programmable through SoftSpan as given in Table 9.

Each channel has a set of double-buffered registers for range information. Program the span input register using the **write span to n** command or **write span to all** command (0110b and 1110b, respectively). Figure 24 shows the syntax, and Table 9 shows the span codes and ranges.

As with the double-buffered code registers, update operations copy the span input registers to the associated span DAC registers.

Table 9. Span Codes

|    |    |            |    | Output Range                                |                         |  |

|----|----|------------|----|---------------------------------------------|-------------------------|--|

| S3 | S2 | <b>S</b> 1 | S0 | External R <sub>FSADJ</sub>                 | FSADJ = V <sub>CC</sub> |  |

| 0  | 0  | 0          | 0  | (High-Z)                                    |                         |  |

| 0  | 0  | 0          | 1  | 50 × V <sub>REF</sub> /R <sub>FSADJ</sub>   | 3.125 mA                |  |

| 0  | 0  | 1          | 0  | 100 × V <sub>REF</sub> /R <sub>FSADJ</sub>  | 6.25 mA                 |  |

| 0  | 0  | 1          | 1  | 200 × V <sub>REF</sub> /R <sub>FSADJ</sub>  | 12.5 mA                 |  |

| 0  | 1  | 0          | 0  | 400 × V <sub>REF</sub> /R <sub>FSADJ</sub>  | 25 mA                   |  |

| 0  | 1  | 0          | 1  | 800 × V <sub>REF</sub> /R <sub>FSADJ</sub>  | 50 mA                   |  |

| 0  | 1  | 1          | 0  | 1600 × V <sub>REF</sub> /R <sub>FSADJ</sub> | 100 mA                  |  |

| 0  | 1  | 1          | 1  | 3200 × V <sub>REF</sub> /R <sub>FSADJ</sub> | 200 mA                  |  |

| 1  | 1  | 1          | 1  | 4800 × V <sub>REF</sub> /R <sub>FSADJ</sub> | 300 mA                  |  |

| 1  | 0  | 0          | 0  | (Switch to V_)                              |                         |  |

As shown in Table 9, there are two additional selections (Code 0000 and Code 1000) which place the output(s) in a high-Z mode or in a mode where a low on resistance ( $\leq$ 12  $\Omega$ ) negative channel metal-oxide semiconductor (NMOS) device shunts the DAC output to the negative supply V\_. When the NMOS device is enabled, the OUTx pin driver is disabled for that channel(s). Span codes not listed in Table 9 default to the high-Z output range.

analog.com Rev. 0 | 15 of 26

## **THEORY OF OPERATION**

Figure 24. Write Span Syntax

Figure 25. AD5778R Single Channel Simplified Diagram

analog.com Rev. 0 | 16 of 26

## THEORY OF OPERATION

#### **MONITOR MUX**

The AD5778R includes a high-voltage mux for monitoring both the voltages and currents at the two current output pins (OUT0 and OUT1). Additionally, the  $V_{DD0}$  and  $V_{DD1}$ , the  $V_{+}$  and  $V_{-}$ , the  $V_{CC}$ , the  $V_{REF}$ , and the die temperature can all be monitored.

The MUX pin is intended for use with high-impedance inputs only. The impedance at the pin is typically 15 k $\Omega$ . A continuous DC

output current at the MUX pin must be limited to ±1 mA to avoid damaging the internal circuitry.

The operating range of the mux extends rail-to-rail from  $V_{-}$  to  $V_{+}$ , and the output is disabled (high impedance) at power up.

The syntax and codes for the **monitor mux** command are shown in Figure 26 and Table 10.

Table 10. Monitor Mux Control Codes

| M4     | М3 | M2 | M1 | М0 | MUX Pin Output                    | Notes                                                                        |

|--------|----|----|----|----|-----------------------------------|------------------------------------------------------------------------------|

| 0      | 0  | 0  | 0  | 0  | Disabled (high-Z)                 |                                                                              |

| 0      | 0  | 0  | 0  | 1  | OUT0 current measurement          | $I_{OUT0} = I_{FS} \times V_{MUX}/V_{REF}$                                   |

| 0      | 0  | 1  | 0  | 0  | OUT1 current measurement          | $I_{OUT1} = I_{FS} \times V_{MUX}/V_{REF}$                                   |

| 0      | 0  | 1  | 1  | 0  | V <sub>CC</sub>                   |                                                                              |

| 0      | 1  | 0  | 0  | 0  | V <sub>REF</sub>                  |                                                                              |

| 0      | 1  | 0  | 0  | 1  | V <sub>REFLO</sub>                | DAC Reference GND                                                            |

| 0      | 1  | 0  | 1  | 0  | Die temperature (T <sub>J</sub> ) | $T_J = 25^{\circ}C + (1.4 \text{ V} - V_{MUX})/(0.0037 \text{ V/}^{\circ}C)$ |

| 1      | 0  | 0  | 0  | 0  | $V_{DD0}$                         |                                                                              |

| 1      | 0  | 0  | 1  | 1  | V <sub>DD1</sub>                  |                                                                              |