# **NID5100**

1.2 V to 5.5 V, 1.5 A input polarity protected, low quiescent current ideal diode

Rev. 1 — 26 July 2024

Product data sheet

# 1. General description

The NID5100 is an integrated ideal diode capable of replacing traditional diodes in low voltage systems unable to tolerate the high voltage drops of conventional Schottky components.

When enabled and forward biased, the device regulates the voltage between the IN and OUT pins resulting in a forward voltage drop, V<sub>REG</sub>, approximately an order of magnitude smaller than similarly rated Schottky diodes. When OUT voltage is higher than IN voltage, the NID5100 becomes reverse biased with very low leakage current.

Integrated Reverse-Polarity Protection (RPP) prevents damage to components connected to the OUT pin in the event of a supply voltage reversal.

The enable pin, EN determines if NID5100 operates in forward regulation mode or body-diode mode.

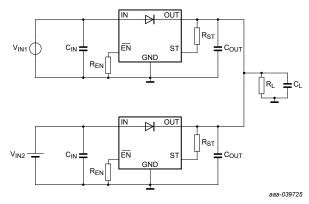

A variety of power OR-ing configurations are supported for system flexibility:

- Two, or more, NID5100 devices in combination

- NID5100s and conventional Schottky diodes

- An NID5100 and an external PMOS

An open-drain status pin, ST, is high-impedance when NID5100 is enabled and in forward conduction and low when disabled or in a reverse biased condition. The ST pin can be used to control an external PMOS to OR an additional supply, or connected to a microcontroller to indicate the status condition of NID5100.

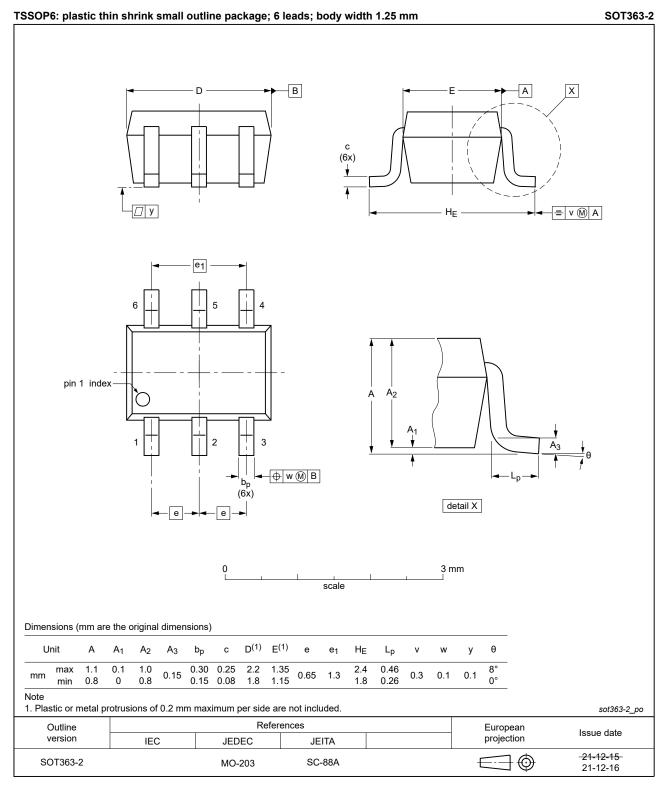

The NID5100 is available in a standard

TSSOP6 (SOT363-2) with 2.1 mm x 1.25 mm x 0.95 mm body package compatible with industry SC88/ SC70-6 packages providing a small PCB footprint compared to conventional low-current diodes.

# 2. Features and benefits

- Low loss replacement for power OR-ing diodes

- Automatic transition between OR-ed supplies

- Operating voltage range: 1.2 V to 5.5 V

- Reverse voltage protection V<sub>IN</sub>: -6 V absolute maximum

- Supports forward current up to 1.5 A

- Forward regulation voltage, V<sub>REG</sub> : 31 mV (typ) at I<sub>OUT</sub> = 10 mA, V<sub>IN</sub> = 3.3 V

- Active LOW control pin, EN

- Output status indication, ST

- Low current consumption:

- 3.3 V shutdown current, I<sub>IN(SD)</sub>: 170 nA (typ)

- 3.3 V quiescent current, I<sub>IN(Q)</sub>: 240 nA (typ)

- Specified over T<sub>amb</sub> -40 °C to +125 °C

# 3. Applications

- **Building automation**

- Smart meters

- OR-ed primary and battery backup

# nexperia

# 4. Ordering information

| Table 1. Ordering information |                   |        |                                                                           |                 |  |  |  |

|-------------------------------|-------------------|--------|---------------------------------------------------------------------------|-----------------|--|--|--|

| Type number                   | nber Package      |        |                                                                           |                 |  |  |  |

|                               | Temperature range | Name   | Description                                                               | Version         |  |  |  |

| NID5100GW                     | -40 °C to +125 °C | TSSOP6 | plastic thin shrink small outline package; 6 leads;<br>body width 1.25 mm | <u>SOT363-2</u> |  |  |  |

# 5. Marking

| Table 2. Marking code |              |  |  |  |  |

|-----------------------|--------------|--|--|--|--|

| Type number           | Marking code |  |  |  |  |

| NID5100GW             | u1           |  |  |  |  |

# 6. Pin configuration and description

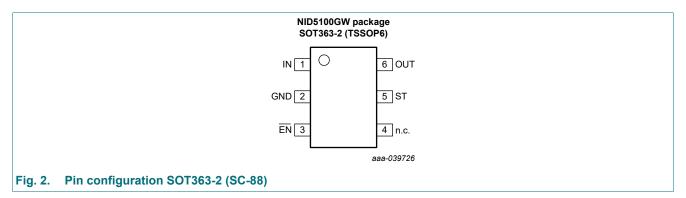

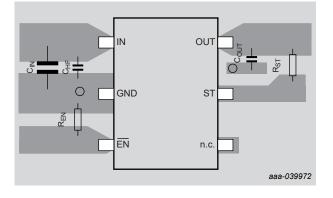

# 6.1. Pin configuration

### 6.2. Pin description

| Symbol | Pin | I/O | Description                                                                                                                                                                                                   |

|--------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN     | 1   | I   | Device input. Analogous to the "anode" pin of a diode.                                                                                                                                                        |

| GND    | 2   | -   | Device ground.                                                                                                                                                                                                |

| EN     | 3   | I   | Active-low enable input. Drive EN low to enable the device. Drive high to disable the device. Drive this pin to a valid high or low level. Do not leave this pin floating.                                    |

| n.c.   | 4   | -   | Not internally connected. Can be tied to GND or left floating.<br>Must be soldered to PCB pad for mechanical reliability.                                                                                     |

| ST     | 5   | 0   | Active-low output. High-Z when chip is enabled and regulating IN to OUT voltage, $V_{REG}$ . Pulled low when the chip is disabled, or reverse current blocking. Connect to GND or leave floating if not used. |

| OUT    | 6   | 0   | Device output. Analogous to the "cathode" pin of a diode.                                                                                                                                                     |

NID5100

# 7. Specifications

### 7.1. Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol               | Parameter                         | Conditions               | Min   | Max   | Unit |

|----------------------|-----------------------------------|--------------------------|-------|-------|------|

| V <sub>IN</sub>      | supply voltage                    |                          | - 6.0 | + 6.0 | V    |

| V <sub>OUT</sub>     | output voltage                    |                          | - 0.3 | + 6.0 | V    |

| $V_{\overline{EN}}$  | enable pin voltage                |                          | - 0.3 | + 6.0 | V    |

| V <sub>ST</sub>      | status pin voltage                |                          | - 0.3 | + 6.0 | V    |

| I <sub>SW(MAX)</sub> | continuous switch current         |                          | -     | + 1.5 | Α    |

| I <sub>SW(PLS)</sub> | maximum pulsed switch current     | ≤120 ms, 2% Duty Cycle   | -     | + 2.5 | A    |

| I <sub>D(PLS)</sub>  | maximum pulsed body diode current | ≤0.1 ms, 0.2% Duty Cycle | -     | + 2.5 | A    |

| I <sub>ST</sub>      | status pin current                |                          | - 1.0 | -     | mA   |

| Tj                   | junction temperature              |                          | - 40  | 150   | °C   |

| T <sub>stg</sub>     | storage temperature               |                          | - 65  | 150   | °C   |

| T <sub>lead</sub>    | lead temperature                  | (10 s soldering time)    | -     | 300   | °C   |

# 7.2. ESD ratings

#### Table 5. ESD ratings

| Symbol           | Parameter               | Conditions                            | Value | Unit |

|------------------|-------------------------|---------------------------------------|-------|------|

| V                | electrostatic discharge | HBM: ANSI/ESDA/JEDEC JS-001 class 2   | ±2000 | V    |

| V <sub>ESD</sub> |                         | CDM: ANSI/ESDA/JEDEC JS-002 class C2a | ±500  | V    |

### 7.3. Recommended operating conditions

#### Table 6. Recommended operating conditions

Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter                                      | Conditions                                                                         | Min | Max | Unit |

|------------------|------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|------|

| V <sub>IN</sub>  | supply voltage                                 |                                                                                    | 1.2 | 5.5 | V    |

| V <sub>OUT</sub> | output voltage                                 | V <sub>IN</sub> ≥ 1.2 V                                                            | 0.5 | 5.5 | V    |

| V <sub>ST</sub>  | status pin voltage                             |                                                                                    | 0   | 5.5 | V    |

| V <sub>EN</sub>  | enable pin voltage                             |                                                                                    | 0   | 5.5 | V    |

| Δt/ΔV            | enable pin input transition rise and fall rate | $V_{IN}$ = 1.2 to 5.5 V;<br>$V_{\overline{EN}}$ = 0 to $V_{IN}$ or $V_{IN}$ to 0 V | 0   | 200 | ms/V |

ent feed

# 7.4. Recommended components

#### Table 7. Recommended components

Nominal component values, not including derating factors.

| Symbol           | Parameter          | Conditions                                            | Min | Nom  | Max | Unit |

|------------------|--------------------|-------------------------------------------------------|-----|------|-----|------|

| C <sub>IN</sub>  | capacitance on IN  |                                                       | 0.1 | 1    | -   | μF   |

| C <sub>OUT</sub> | capacitance on OUT | An output capacitor is required for proper operation. | 0.1 | 0.47 | 100 | μF   |

| R <sub>EN</sub>  | resistor on EN     | Connected to GND [1]                                  | 0   | 50   | 100 | kΩ   |

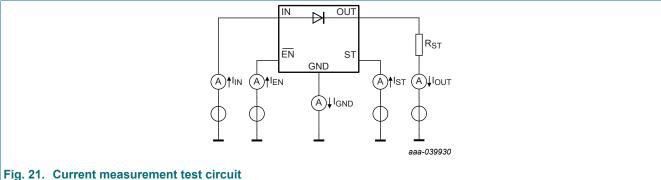

| R <sub>ST</sub>  | resistor on ST     |                                                       | 25  | 50   | 100 | kΩ   |

If the EN pin is driven by a microcontroller, the value of R<sub>EN</sub> should be chosen in accordance with the microcontrollers I/O pin drive capability (V<sub>OH</sub> and V<sub>OL</sub>).

### 7.5. Thermal information

#### Table 8. Thermal information

Thermal resistance according to JEDEC51-5 and -7

| Symbol                | Parameter                                  | SOT363-2 | Unit |

|-----------------------|--------------------------------------------|----------|------|

| R <sub>OJA</sub>      | junction-to-ambient thermal resistance     | 256      | °C/W |

| R <sub>OJC(TOP)</sub> | junction-to-case (top) thermal resistance  | 177      | °C/W |

| $\Psi_{JT}$           | junction-to-top characterization parameter | 78       | °C/W |

ent feedt

# 7.6. Electrical characteristics

#### Table 9. Static characteristics

$C_{IN} = 0.1 \ \mu\text{F}$  in parallel with 1  $\mu\text{F}$ ,  $C_{OUT} = 0.1 \ \mu\text{F}$ ,  $V_{EN} = 0 \ V$ , 1.5 V  $\leq V_{IN} \leq 5.5 \ V$ . Typical values are at  $T_{amb} = 25 \ ^{\circ}\text{C}$  with an input voltage of 3.3 V (unless otherwise noted).

| Symbol              | Parameter                                                                              | Conditions                                                                      |                                                                                 |                                   | Min | Тур    | Max  | Unit |

|---------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------|-----|--------|------|------|

| Input sup           | ply (IN)                                                                               | 1                                                                               |                                                                                 |                                   |     |        |      |      |

| I <sub>IN(SD)</sub> | shutdown current                                                                       | $V_{OUT} = V_{IN} = V_{EN}$                                                     | = 3.3 V                                                                         | T <sub>amb</sub> = 25°C           | -   | 0.17   | 0.24 | μA   |

|                     |                                                                                        | I <sub>OUT</sub> = 0 A (V <sub>OUT</sub>                                        | = open)                                                                         | T <sub>amb</sub> = -40°C to 125°C | -   | -      | 0.30 |      |

| I <sub>IN(Q)</sub>  | quiescent current                                                                      | V <sub>OUT</sub> = V <sub>IN</sub> ; V <sub>EN</sub> =                          |                                                                                 | T <sub>amb</sub> = 25°C           | -   | 0.24   | 0.35 | μA   |

|                     |                                                                                        | $I_{OUT} = 0 A (V_{OUT})$                                                       | = open)                                                                         | T <sub>amb</sub> = -40°C to 125°C | -   | -      | 0.40 |      |

| Forward w           | oltage regulation, V <sub>RE</sub>                                                     | ĒG                                                                              |                                                                                 |                                   |     |        |      |      |

| V <sub>REG</sub>    | forward regulation<br>voltage<br>V <sub>REG</sub> = V <sub>IN</sub> - V <sub>OUT</sub> | V <sub>IN</sub> = 5 V, or<br>V <sub>IN</sub> = 3.3 V                            | V <sub>EN</sub> = 0 V<br>I <sub>OUT</sub> = 10 mA                               | $T_{amb}$ = -40°C to 125°C        | 7   | 31     | 50   | mV   |

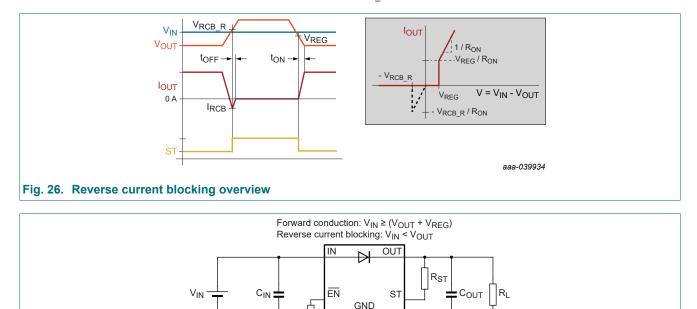

| ON-resist           | ance (R <sub>ON</sub> ). See <u>Fig. 2</u>                                             | <u>6</u> .                                                                      |                                                                                 |                                   |     |        |      |      |

| R <sub>ON</sub>     | on-state resistance                                                                    | transistor fully<br>enhanced                                                    | V <sub>IN</sub> = 3.3 V<br>I <sub>OUT</sub> = - 500 mA<br>V <sub>EN</sub> = 0 V | T <sub>amb</sub> = 25°C           | -   | 115    | -    | mΩ   |

| Reverse C           | Current Blocking (RCE                                                                  | ) and body diode                                                                | characteristics                                                                 |                                   |     |        |      |      |

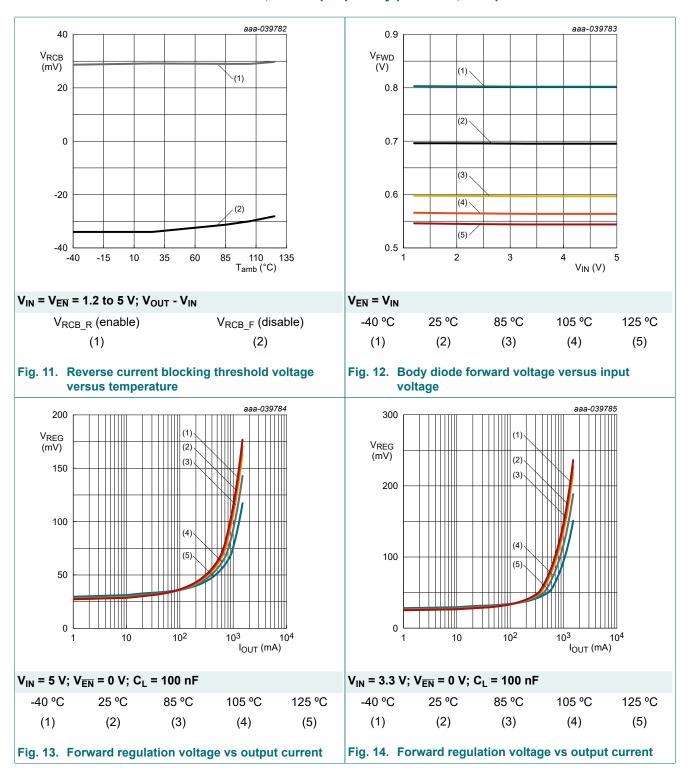

| V <sub>RCB_R</sub>  | reverse current<br>blocking activation<br>voltage                                      | (V <sub>OUT</sub> - V <sub>IN</sub> ), V <sub>OU</sub><br>V <sub>EN</sub> = 0 V | <sub>T</sub> rising above V <sub>IN</sub>                                       | T <sub>amb</sub> = 25°C           | -   | 30.5   | -    | mV   |

| V <sub>RCB_F</sub>  | reverse current<br>blocking deactivation<br>voltage                                    | (V <sub>OUT</sub> - V <sub>IN</sub> ), V <sub>OU</sub><br>V <sub>EN</sub> = 0 V | <sub>T</sub> falling below V <sub>IN</sub>                                      | T <sub>amb</sub> = 25°C           | -   | - 33.5 | -    | mV   |

| V <sub>FWD</sub>    | body diode forward voltage                                                             | I <sub>OUT</sub> = 10 mA<br>V <sub>EN</sub> = V <sub>IN</sub>                   |                                                                                 | T <sub>amb</sub> = -40°C to 125°C | 0.3 | 0.5    | 0.9  | V    |

# NID5100

| Symbol                | Parameter                                         | Conditions                                                             |                                                  |      | Тур | Max  | Unit |

|-----------------------|---------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------|------|-----|------|------|

| Leakage               | currents                                          | ·                                                                      |                                                  |      |     |      |      |

| I <sub>OUT-</sub>     | OUT to IN leakage                                 | V <sub>IN</sub> = 3.3 V; V <sub>OUT</sub> = 4 V; V <sub>EN</sub> = 0 V | T <sub>amb</sub> = 25°C                          | -    | 130 | 180  | nA   |

| IN(REV)               | current<br>(current out of IN,                    |                                                                        | T <sub>amb</sub> = -40°C to 85°C                 | -200 | -   | 200  | nA   |

|                       | reverse biased)                                   |                                                                        | T <sub>amb</sub> = -40°C to 125°C                | -220 | -   | 220  | nA   |

|                       |                                                   | V <sub>IN</sub> = 3.3 V; V <sub>OUT</sub> = 5 V; V <sub>EN</sub> = 0 V | T <sub>amb</sub> = 25°C                          | -    | 130 | 180  | nA   |

|                       | device enabled                                    |                                                                        | T <sub>amb</sub> = -40°C to 85°C                 | -200 | -   | 200  | nA   |

|                       |                                                   |                                                                        | T <sub>amb</sub> = -40°C to 125°C                | -220 | -   | 220  | nA   |

|                       |                                                   | V <sub>IN</sub> = 2 V; V <sub>OUT</sub> = 5.5 V; V <sub>EN</sub> = 0 V | T <sub>amb</sub> = -40°C to 85°C                 | -220 | 130 | 220  | nA   |

| I <sub>OUT(REV)</sub> | current into OUT                                  | V <sub>IN</sub> = 3.3 V; V <sub>OUT</sub> = 4 V; V <sub>EN</sub> = 0 V | T <sub>amb</sub> = 25°C                          | -    | 330 | 410  | nA   |

|                       | (reverse biased)                                  |                                                                        | T <sub>amb</sub> = -40°C to 85°C                 | -    | -   | 500  | nA   |

|                       | device enabled                                    |                                                                        | T <sub>amb</sub> = -40°C to 125°C                | -    | -   | 800  | nA   |

|                       |                                                   | V <sub>IN</sub> = 3.3 V; V <sub>OUT</sub> = 5 V; V <sub>EN</sub> = 0 V | T <sub>amb</sub> = 25°C                          | -    | 420 | 500  | nA   |

|                       |                                                   |                                                                        | T <sub>amb</sub> = -40°C to 85°C                 | -    | -   | 600  | nA   |

|                       |                                                   |                                                                        | T <sub>amb</sub> = -40°C to 125°C                | -    | -   | 1000 | nA   |

|                       |                                                   | V <sub>IN</sub> = 2 V; V <sub>OUT</sub> = 5.5 V; V <sub>EN</sub> = 0 V | T <sub>amb</sub> = -40°C to 85°C                 | -    | 530 | 700  | nA   |

| I <sub>OUT-</sub>     | OUT to IN leakage                                 | V <sub>IN</sub> = V <sub>EN</sub> = 4.5 V; V <sub>OUT</sub> = 5.5 V    | T <sub>amb</sub> = 25°C                          | -    | 150 | 500  | nA   |

| IN(DIS)               | current<br>(current out of IN,<br>reverse biased) |                                                                        | $T_{amb} = -40^{\circ}C \text{ to } 85^{\circ}C$ | -    | -   | 800  | nA   |

|                       |                                                   |                                                                        | $T_{amb} = -40^{\circ}C$ to 125°C                | -    | -   | 825  | nA   |

|                       | device disabled                                   | V <sub>IN</sub> = V <sub>EN</sub> = 1.5 V; V <sub>OUT</sub> = 5.5 V    | T <sub>amb</sub> = -40°C to 85°C                 | -    | -   | 3300 | nA   |

|                       |                                                   |                                                                        | T <sub>amb</sub> = -40°C to 125°C                | -    | -   | 3500 | nA   |

|                       |                                                   | V <sub>IN</sub> = V <sub>EN</sub> = 0 V; V <sub>OUT</sub> = 5.5 V      | T <sub>amb</sub> = -40°C to 85°C                 | -    | -   | 1500 | nA   |

|                       |                                                   |                                                                        | $T_{amb} = -40^{\circ}C$ to $125^{\circ}C$       | -    | -   | 1650 | nA   |

| Enable (E             |                                                   | I                                                                      |                                                  |      | I   | 1    |      |

| V <sub>IL</sub>       | LOW-level input voltage                           | device enabled                                                         | T <sub>amb</sub> = -40°C to 125°C                | -    | -   | 0.4  | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                          | device disabled                                                        | T <sub>amb</sub> = -40°C to 125°C                | 1.2  | -   | -    | V    |

| V <sub>HYS</sub>      | enable pin hysteresis                             |                                                                        | T <sub>amb</sub> = 25°C                          | -    | 45  | -    | mV   |

| IIL                   | LOW-level input                                   | V <sub>EN</sub> = 0 V                                                  | T <sub>amb</sub> = 25°C                          | -30  | 0   | 30   | nA   |

|                       | current                                           |                                                                        | T <sub>amb</sub> = -40°C to 125°C                | -100 | -   | 100  | nA   |

| I <sub>IH</sub>       | HIGH-level input                                  | V <sub>IN</sub> = 3.3 V                                                | T <sub>amb</sub> = 25°C                          | -    | 15  | -    | nA   |

|                       | current                                           | V <sub>EN</sub> = 3.3 V                                                | T <sub>amb</sub> = -40°C to 125°C                | -    | -   | 150  | nA   |

|                       | HIGH-level input                                  | V <sub>IN</sub> = 3.3 V                                                | T <sub>amb</sub> = 25°C                          | -    | 20  | -    | nA   |

|                       | current<br>(V <sub>EN</sub> > V <sub>IN</sub> )   | V <sub>EN</sub> = 5 V                                                  | $T_{amb} = -40^{\circ}C$ to $125^{\circ}C$       | -    | -   | 150  | nA   |

| Status inc            | dication (ST)                                     |                                                                        |                                                  |      |     |      |      |

| V <sub>OL(ST)</sub>   | LOW-level output                                  | I <sub>ST</sub> = 1 mA; V <sub>IN</sub> ≥ 1.8 V                        | T <sub>amb</sub> = -40°C to 125°C                | -    | -   | 0.1  | V    |

|                       |                                                   | I <sub>ST</sub> = 0.1 mA; V <sub>IN</sub> < 1.8 V                      | T <sub>amb</sub> = -40°C to 125°C                | -    | -   | 0.1  | V    |

| I <sub>ST</sub>       | ST pin leakage<br>current                         | V <sub>ST</sub> = V <sub>IN</sub><br>V <sub>EN</sub> = 0 V             | $T_{amb}$ = -40°C to 125°C                       | -150 | -   | 150  | nA   |

### 1.2 V to 5.5 V, 1.5 A input polarity protected, low quiescent current ideal diode

# 7.7. Dynamic characteristics

#### Table 10. Dynamic characteristics

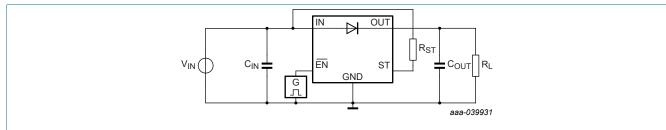

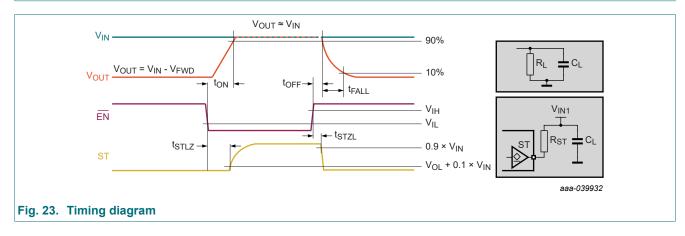

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values at  $T_{amb}$  = 25 °C;  $C_{IN}$  = 0.1 µF in parallel with 1 µF; and a load of  $C_L$  = 100 nF in parallel with  $R_L$  = 1 k $\Omega$ . See Fig. 22 and Fig. 23.

|                   | · · · · · · · · · · · · · · · · · · ·                            |                         |     |     |     |      |  |

|-------------------|------------------------------------------------------------------|-------------------------|-----|-----|-----|------|--|

| Symbol            | Parameter                                                        | Conditions              | Min | Тур | Max | Unit |  |

| t <sub>ON</sub>   | turn-on time                                                     | V <sub>IN</sub> = 1.5 V | -   | 90  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 1.8 V | -   | 100 | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 2.5 V | -   | 130 | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 3.3 V | -   | 165 | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 5 V   | -   | 240 | -   | μs   |  |

| t <sub>OFF</sub>  | turn-off time                                                    | V <sub>IN</sub> = 1.5 V | -   | 60  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 1.8 V | -   | 50  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 2.5 V | -   | 38  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 3.3 V | -   | 30  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 5 V   | -   | 10  | -   | μs   |  |

| t <sub>FALL</sub> | output FALL time                                                 | V <sub>IN</sub> = 1.5 V | -   | 35  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 1.8 V | -   | 25  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 2.5 V | -   | 20  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 3.3 V | -   | 15  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 5 V   | -   | 10  | -   | μs   |  |

| t <sub>STLZ</sub> | status, ST pin, delay time: low to high-impedance                | V <sub>IN</sub> = 1.5 V | -   | 80  | -   | μs   |  |

|                   | EN transitions from high to low<br>R <sub>ST</sub> = 50 kΩ to IN | V <sub>IN</sub> = 1.8 V | -   | 90  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 2.5 V | -   | 125 | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 3.3 V | -   | 160 | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 5 V   | -   | 220 | -   | μs   |  |

| t <sub>STZL</sub> | status, ST pin, delay time: high-impedance to low                | V <sub>IN</sub> = 1.5 V | -   | 38  | -   | μs   |  |

|                   | EN transitions from low to high<br>R <sub>ST</sub> = 50 kΩ to IN | V <sub>IN</sub> = 1.8 V | -   | 33  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 2.5 V | -   | 25  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 3.3 V | -   | 18  | -   | μs   |  |

|                   |                                                                  | V <sub>IN</sub> = 5 V   | -   | 1   | -   | μs   |  |

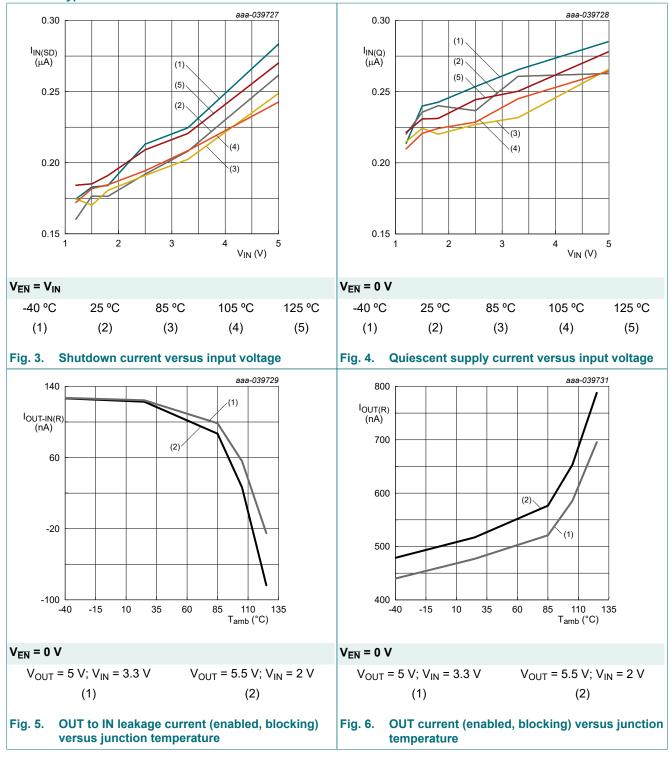

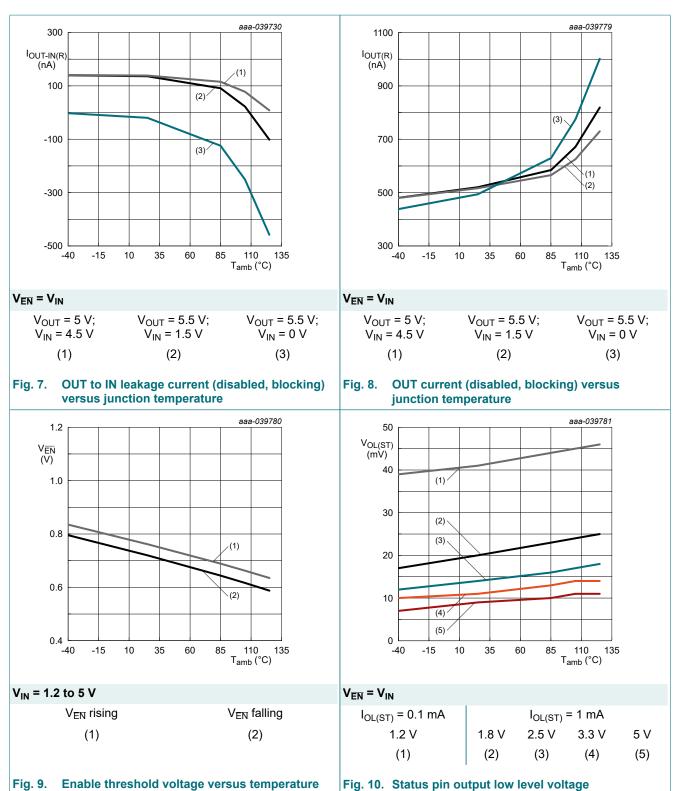

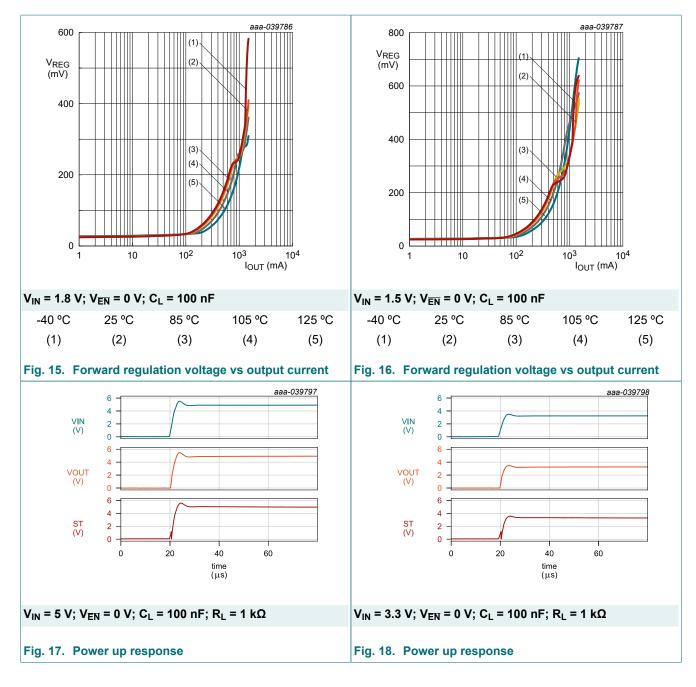

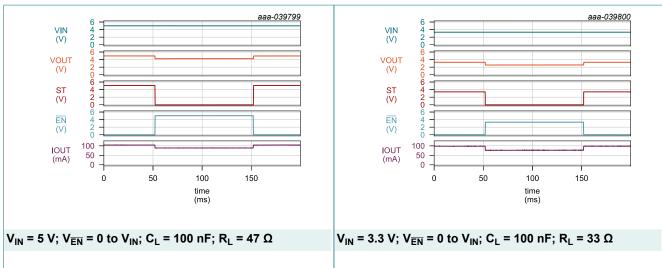

## 7.8. Typical Characteristics

$V_{IN}$  = 3.3 V, GND = 0 V,  $V_{\overline{EN}}$  = 0 V,  $C_{IN}$  = 0.1 + 1  $\mu$ F,  $C_{OUT}$  +  $C_{L}$  = 0.1 + 1  $\mu$ F to GND. Typical values at  $T_{amb}$  = 25 C, unless otherwise noted.

#### **Table 11. Typical Characteristics**

NID5100

© Nexperia B.V. 2024. All rights reserved

nt feedb

Fig. 20. Enable and disable response

#### Fig. 19. Enable and disable response

#### Fig. 22. Timing response measurement circuit

# 8. Functional Description

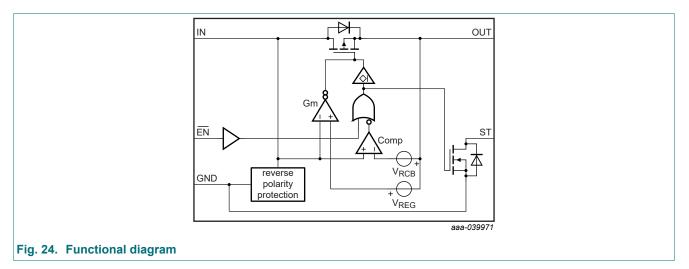

#### 8.1. Functional diagram

### 8.2. Overview

The NID5100 consists of an internal PMOS transistor with its body diode oriented from IN (anode) to OUT (cathode); reverse current protection; reverse polarity protection; gate regulation amplifier; control logic and a status flag, ST. The device conducts from IN to OUT when enabled and forward biased and blocks when reverse biased. It mimics the behavior of low voltage Schottky diodes with a fraction of the forward voltage drop and significantly lower reverse leakage current. It is designed to operate from a 1.2 to 5.5 V supply making it suitable for use in a variety of low voltage applications.

OR-ing: The NID5100 supports a variety of power supply OR-ing, or redundant power backup, scenarios:

- 1. Low loss using "2 to n" NID5100s

- 2. Low loss dual OR-ing circuit consisting of one NID5100 and an external PMOS

- 3. <u>Hybrid</u> with one, or more, NID5100(s) in combination with Schottky diodes

- 4. Paralleling two or more NID5100s for high current loads

See <u>application information</u> sections for suggested implementations.

### 8.3. Feature Description

#### 8.3.1. Enable, control logic and ST pin

The enable pin,  $\overline{EN}$ , determines if the NID5100 operates in regulated conduction mode,  $V_{\overline{EN}} \leq V_{IL}$ , or body diode mode,  $V_{\overline{EN}} \geq V_{IH}$ .

When the  $\overline{EN}$  pin voltage,  $V_{\overline{EN}} \le V_{IL}$ , the gate amplifier and control logic are operational and the device consumes low quiescent current,  $I_{Q(EN)}$ .

The open-drain status, ST, pin provides real-time indication of the internal PMOS. See <u>functional modes</u>. When NID5100 is enabled, the ST pin indicates high when the internal PMOS is conducting. It indicates low when reverse biased and blocking. The ST pin is low when NID5100 is disabled. ST can be connected to a MCU input to provide status information or control an external PMOS in a low-loss dual OR-ing application. If the ST pin is unused, connect to ground.

#### 8.3.2. Device functional modes

Table 12 summarizes the device operating modes.

#### Table 12. Device functional modes

| EN   | State | IN-to-OUT          | Power Dissipation                                        | Status PIN State |

|------|-------|--------------------|----------------------------------------------------------|------------------|

| HIGH | OFF   | Diode              | I <sub>OUT</sub> × V <sub>FWD</sub>                      | L                |

| LOW  | ON    | Forward conduction | I <sub>OUT</sub> × (V <sub>IN</sub> - V <sub>OUT</sub> ) | high-Z           |

| LOW  | RCB   | Diode              | I <sub>OUT(REV)</sub> × V <sub>OUT</sub> [1]             | L                |

[1] OUT current is leakage into device when reverse biased. See electrical characteristics tables.

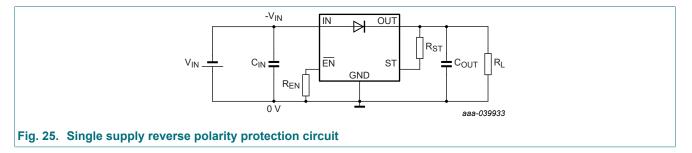

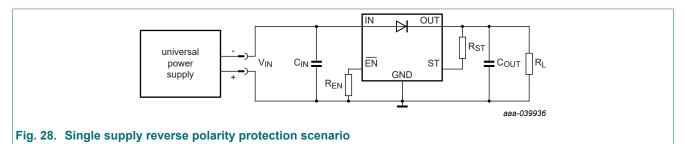

#### 8.3.3. Reverse Polarity Protection (RPP)

Reverse polarity conditions can occur when a power source's terminals are connected with opposite polarity, or a battery is inserted incorrectly. Lossy power diodes and complicated ground connected discrete PMOS transistor circuits have historically been used to protect sensitive downstream circuits from polarity reversal conditions.

The NID5100 operates similarly. If a negative input voltage is applied to an unpowered NID5100, the PMOS will remain off and prevent reverse current flow protecting downstream components. If the NID5100 is initially powered on and subsequently experiences an input polarity reversal, the internal PMOS will turn off preventing the load from negative voltage. RPP is active regardless of the state of the EN pin.

For autonomous operation with RPP, the  $\overline{EN}$  pin must be tied to GND. A pull-down resistor,  $R_{EN}$ , is optional, but recommended. If the ST pin is used for monitoring, it should be connected via a resistor,  $R_{ST}$ , to OUT or another voltage source immune to reverse polarity conditions.  $R_{ST}$  should be sized to prevent exceeding the ST pin leakage current (see  $I_{ST}$ ). Fig. 25 provides an application example.

#### 8.3.4. Gate regulation amplifier

When the NID5100 is enabled and forward biased, the gate regulation amplifier adjusts the internal PMOS gate voltage to maintain the IN to OUT voltage,  $V_{REG}$ . When operating in the forward voltage regulation region, the voltage drop is approximately ten times smaller than a conventional Schottky diode aiding in the reduction of system power losses. At light loads, the forward voltage drop from IN to OUT is maintained at  $V_{REG}$ . As load current increases, the PMOS eventually becomes fully enhanced and the IN to OUT voltage drop becomes proportional to the on-resistance of the PMOS multiplied by the load current. See right side inset of Fig. 26.

#### 8.3.5. Reverse Current Blocking (RCB)

Reverse current blocking (RCB) protection is always active, regardless of the state of EN.

When  $\overline{\text{EN}}$  is low and the output, OUT, is forced above the input, IN, the internal PMOS will switch off to stop the reverse current. When the IN to OUT differential returns below V<sub>RCB F</sub>, the device will turn back on and regulate IN to OUT at V<sub>REG</sub>.

When  $\overline{\text{EN}}$  pin voltage is high, the internal PMOS is turned off and reverse current blocking (RCB) occurs through body diode action when V<sub>OUT</sub> is greater than V<sub>IN</sub> + V<sub>FWD</sub>. Forward conduction through the PMOS body diode resumes when V<sub>IN</sub> + V<sub>FWD</sub> is greater than V<sub>OUT</sub>.

The NID5100 blocks reverse current via two mechanisms when enabled:

- The V<sub>REG</sub> amplifier responds to common transients by naturally increasing the PMOS transistor resistance as the IN to OUT voltage differential decreases. When V<sub>OUT</sub> nears and becomes larger than V<sub>IN</sub> the amplifier is regulating the transistor gate and R<sub>DSON</sub> well below full enhancement increasing the impedance from OUT to IN until the PMOS becomes full disabled.

- In the event of an extremely fast transition to a reverse biased condition, such as a shorted input, the fast trip RCB comparator reacts disabling the PMOS when V<sub>OUT</sub> V<sub>IN</sub> = V<sub>RCB R</sub> to limit reverse current.

$\mathsf{R}_{\mathsf{EN}}$

aaa-039935

#### Fig. 27. Reverse current blocking

# 9. Application information

**Note:** Application implementation information in the following sections is not part of the Nexperia component specification. Nexperia's device users are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

The NID5100 ideal diode is a versatile device suitable for protecting circuits from reverse polarity connections, reverse current conditions, OR-ing and simple power multiplexing. The following sections provide application examples to aid the design of products using NID5100.

### 9.1. Reverse polarity protection

Universal DC power supplies are often used to replace an OEM wall charger which has been lost or broken. Commonly these supplies are capable of reversing voltage polarity and if the user does not take care to ensure proper universal power supply polarity setup, negative voltages could be applied to the device being powered causing it to be damaged. The NID5100 senses reverse polarity connections and protects downstream components from exposure to negative voltages.

When reverse polarity protection is used, the ST pin should be connected to OUT or left floating. Connecting ST to IN may result in device malfunction during supply reversal.

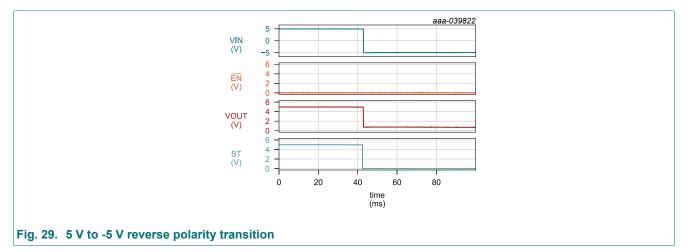

Fig. 29 demonstrates the operation of NID5100 in the event of a positive to negative polarity reversal. V<sub>IN</sub> is initially 5 V, then rapidly reverses to -5 V. V<sub>OUT</sub> drops to 0 V and the ST pin transitions from high to low.

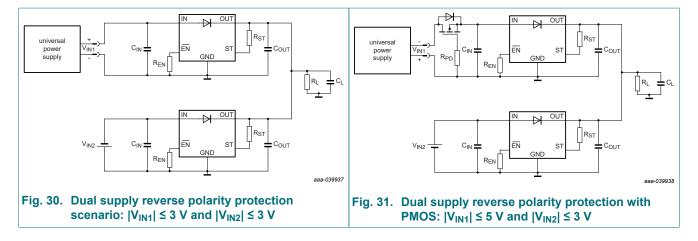

Reverse polarity conditions can also occur in dual supply scenarios. Fig. 30 illustrates a situation in which a wall supply is providing power with an incorrectly installed backup battery. So long as the OUT to IN conditions in <u>limiting values</u> are be observed, the NID5100 can be use as shown without additional protection. For applications requiring a higher OUT to IN differential, an external PMOS can be added in the power path, or paths, where reversal may occur - see Fig. 31.

NID5100

© Nexperia B.V. 2024. All rights reserved

nt feed

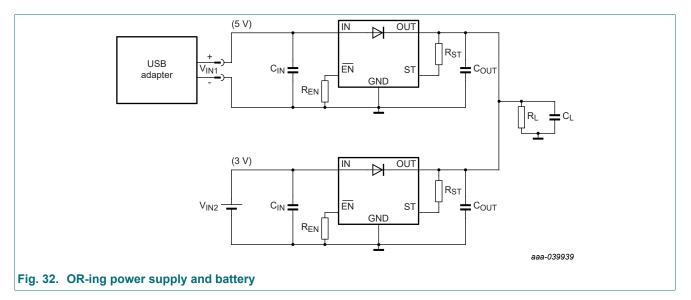

### 9.2. OR-ing examples

#### 9.2.1. n+1 OR-ing using ideal diodes

There is no specific limitation to the number of NID5100 ideal diodes used for power OR-ing. The example below illustrates a common two power supply scenario with smooth transitions between supplies.

Some devices operate from a fixed power supply such as a standard 5 V USB port output in normal conditions but must quickly transition to a 3 V battery backup when the power supply is disabled or unplugged. Using two NID5100 devices in a power OR-ing configuration, the downstream load remains uninterrupted when either the DC supply or the backup battery are disconnected.

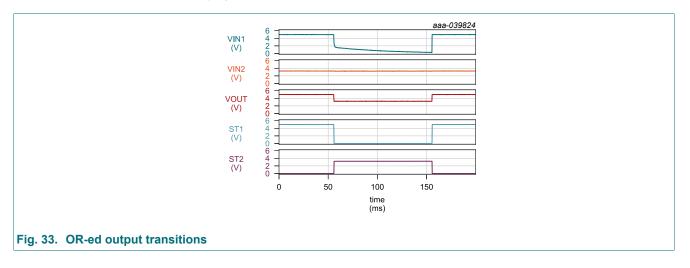

The scope capture shows the output voltage ( $V_{OUT}$ ) being initially powered by  $V_{IN1}$  at 5 V. When  $V_{IN1}$  is removed,  $V_{IN2}$  at 3.3 V powers  $V_{OUT}$ . When  $V_{IN1}$  is reconnected,  $V_{OUT}$  is once again powered by  $V_{IN1}$ . The ST pins of the NID5100's transition to indicate which ideal diode is supplying the load.

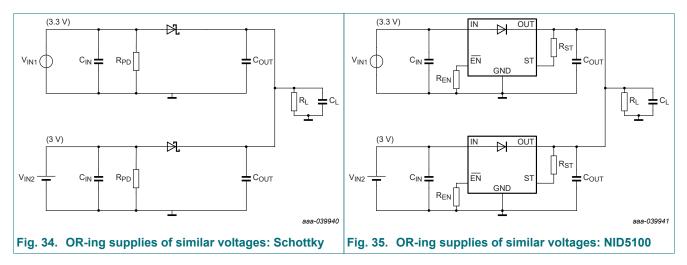

#### 9.2.2. OR-ing similar supply voltages

Some applications may require the OR-ing of supplies with similar voltages. Refer to <u>Fig. 34</u> and <u>Fig. 35</u>. In this example, the primary DC supply is 3.3 V with a 3 V battery backup. Consider the scenario where  $V_{IN1}$  is suppling the load, is removed and subsequently restored.

Schottky circuit: As the two supplies differ by only 300mV, when  $V_{IN1}$  is restored, there may not be enough forward voltage,  $V_F$ , across the diode in the  $V_{IN1}$  path to forward bias it until the battery voltage depletes sufficiently wasting energy in the backup source.

NID5100 circuit: When  $V_{IN1}$  is restored, the reverse current blocking deactivation threshold,  $V_{RCB_F}$ , of the 3.3 V supplied NID5100 is easily exceeded allowing the 3.3 V supply to carry the full load. As the OUT is approximately 300 mV above  $V_{IN2}$ , the 3 V supplied NID5100 becomes reverse biased and the battery drain is minimized.

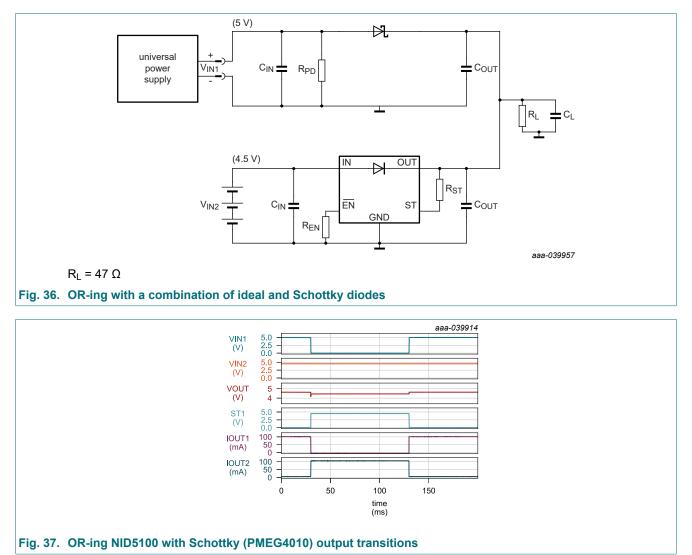

#### 9.2.3. n+1 OR-ing using ideal and conventional diodes

When voltage drops and electrical losses of one of two power sources is not of concern, a combination of ideal diodes and conventional diodes can be implemented as shown in Fig. 36. In this example the AC-DC adapter is the primary power source supplying 5 V to the system with three alkaline cells providing a 4.5 V backup. As stated in the <u>OR-ing similar supply</u> voltages section, consideration should be given to the V<sub>F</sub> rating of the Schottky diode as well as worst case tolerances of the supply voltages to ensure seamless transitions.

A resistor,  $R_{PD}$ , connected to ground in the Schottky diode path is recommended to prevent diode reverse leakage during blocking conditions from charging  $C_{IN1}$  and raising  $V_{IN1}$ .

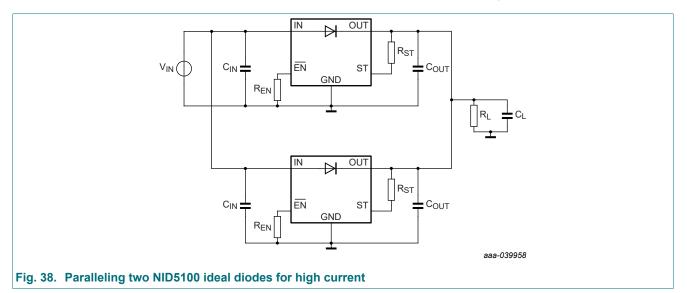

#### 9.2.4. Paralleling NID5100 for thermal and sustained high current considerations

As with using any power semiconductor component, thermal ratings must be observed to maintain device reliability. Refer to the <u>thermal information</u> table. System thermal analysis should be performed to ensure the device junction temperature,  $T_j$ , remains below 150 °C under all operating conditions. If analyses of using a single NID5100 indicate a thermal violation, two NID5100 can be paralleled to share the load current and lower internal power dissipation Fig. 38.

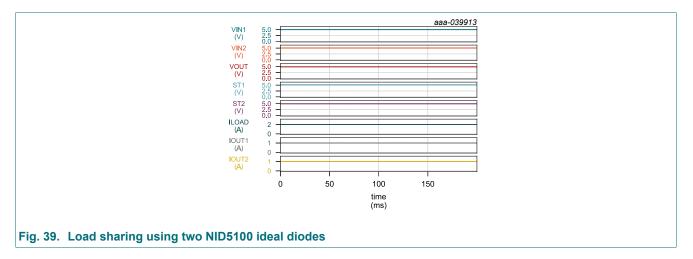

Fig. 39 shows two NID5100's supporting a combined 2 A load current with 1 A current flowing in each NID5100.

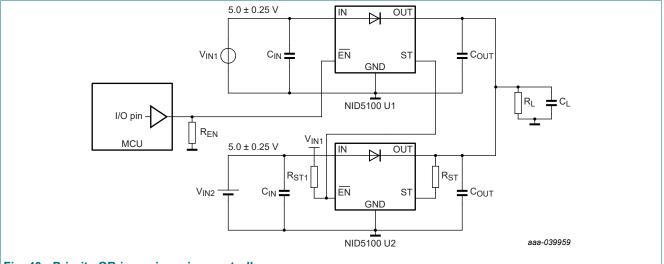

#### 9.2.5. Priority OR-ing

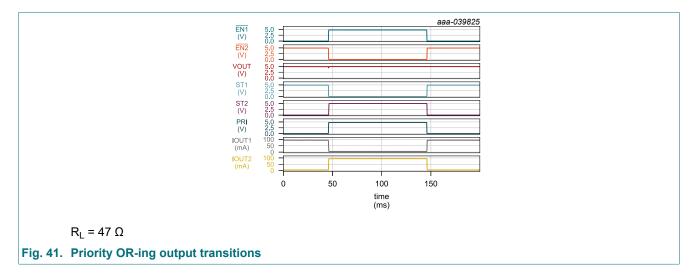

More sophisticated systems may contain a microcontroller able to perform basic power management housekeeping functions such as power source selection from supplies with similar voltages. In the example of figure <u>Fig. 40</u>, two NID5100 ideal diodes are connected in an OR-ing configuration from similar 5 V sources.

Refer to the <u>device functional modes</u> table for operation of the ST pin. In this application example, the ST pin of NID5100 U1 is connected via a pull-up resistor to  $V_{IN1}$  and the  $\overline{EN}$  of NID5100 U2 providing a polarity inversion of the GPIO signal. When device U1 is enabled, device U2 is disabled, and vice-versa allowing the MCU to select which supply sources the load.

When the microcontroller drives the GPIO low, NID5100 U1 is enabled sourcing V<sub>IN1</sub> to OUT while U2 is disabled. Conversely if the GPIO is driven high, NID5100 U2 is enabled sourcing V<sub>IN2</sub> to OUT and NID5100 U1 is disabled. In either scenario the RCB circuity remains active disabling the device with a low  $\overline{EN}$  if V<sub>RCB R</sub> is exceeded.

$R_{EN}$  is recommended to be of high enough resistance to prevent loading the MCU GPIO output while ensuring  $\overline{EN}$  is actively driven in the event the GPIO is in a high impedance condition.

#### Fig. 40. Priority OR-ing using microcontroller

The scope capture shows EN1, EN2, V<sub>OUT</sub>, ST1, ST2, GPIO priority signal (PRI) connected to EN1, and the OUT1 and OUT2 currents.

Initially PRI is driven low pulling  $\overline{EN1}$  low, enabling NID5100 U1. V<sub>OUT</sub> is approximately equal to V<sub>IN1</sub>. Load is supplied from OUT1. ST1, connected to  $\overline{EN2}$  is pulled above the V<sub>IH</sub> of NID5100 U2 with ST2 low indicating the device is disabled.

Next, EN1 is driven high, disabling NID5100 U1 causing ST1 to transition low, enabling NID5100 U2.

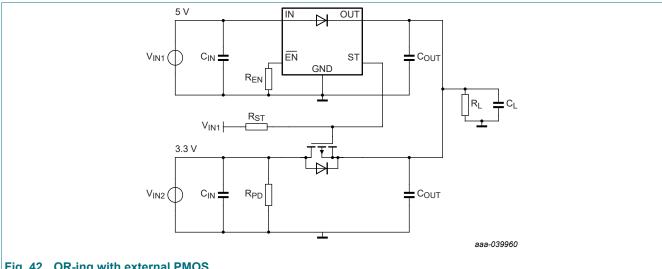

#### 9.2.6. OR-ing with discrete MOSFET

In this application, the EN pin of the NID5100 is always grounded "enabling" the device. When both the 5 V and 3.3 V supplies are present, OUT is initially 5 V and the ST pin is high-Z with the RST resistor pulled up to VIN1, keeping the gate of the external PFET high.

- If V<sub>IN1</sub> is quickly removed, the ST pin output will transition low, enhancing the external PMOS. The load is then supplied from V<sub>IN2</sub>.

- If V<sub>IN1</sub> is a slowly discharging battery, OUT will transition from being supplied by the NID5100 OUT pin to being supplied by the external PMOS when VIN1 decreases below VIN2 by VFWD(ext\_PMOS). Conversely, if VIN1 is slowly recharged, OUT will be supplied from the PMOS until  $V_{IN1} + V_{REG} \ge V_{IN2} + V_{RDSON(ext PMOS)}$

Note: The supply to the NID5100 (VIN1) should be the higher of the two supplies when both VIN1 and VIN2 are present.

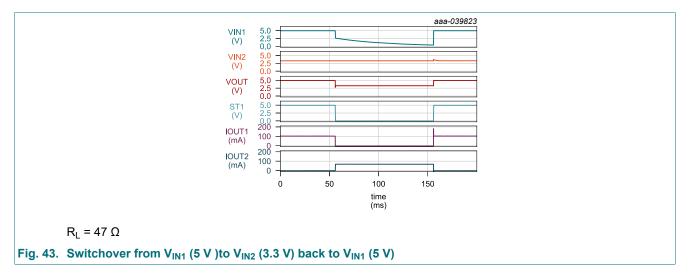

Fig. 42. OR-ing with external PMOS

The figures below show the switchover performance between VIN1 and VIN2. A resistor, RPD, to ground is recommended to prevent any reverse leakage from charging the 3.3 V CIN capacitor and raising the VIN2 voltage in the event the 3.3 V supply is disconnected.

# **10.** Power supply recommendations

The device is designed to operate with a  $V_{IN}$  range of 1.2 V to 5.5 V. The  $V_{IN}$  power supply must be well regulated and placed as close to the device terminal as possible. The power supply must be able to withstand all transient load current steps.

In most situations, using an input capacitance ( $C_{IN}$ ) of 0.1 + 1  $\mu$ F is sufficient to prevent the supply voltage from drooping. In cases where the power supply is slow to respond to a large transient current or large load current step, additional bulk capacitance may be required on the input.

An effective capacitance of  $\ge 0.1 \ \mu$ F, after applying voltage and temperature derating factors, is required on the OUT pin to ensure stability of the control loop Gm amplifier. NID5100 does not have over current protection and the maximum output capacitance should not exceed approximately 100  $\mu$ F.

## 11. Layout

#### Layout guidelines

For best performance, all traces must be as short as possible. To be most effective, the input and output capacitors must be placed close to the device to minimize the effects that parasitic trace inductances may have on normal operation. Using wide traces for  $V_{IN}$ ,  $V_{OUT}$  and GND helps minimize the parasitic electrical effects.

NID5100

# 12. Package information

#### 12.1. Package outline

#### Fig. 44. Package outline SOT363-2 (TSSOP6)

NID5100

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2024. All rights reserved

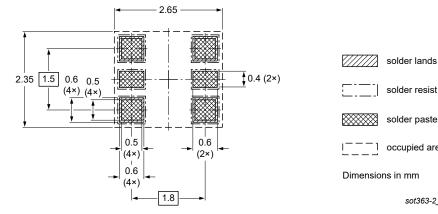

solder resist

<sup>−</sup>1 occupied area

sot363-2\_fr

Fig. 45. Reflow soldering footprint SOT363-2 (TSSOP6)

# 13. Abbreviations

#### Table 13. Abbreviations

| Acronym | Description                                       |  |

|---------|---------------------------------------------------|--|

| CDM     | Charged Device Model                              |  |

| ESD     | ElectroStatic Discharge                           |  |

| FET     | Field-Effect Transistor                           |  |

| HBM     | Human Body Model                                  |  |

| IEC     | International Electrotechnical Commission         |  |

| JEDEC   | Joint Electron Device Engineering Council         |  |

| MOSFET  | Metal-Oxide Semiconductor Field-Effect Transistor |  |

| PCB     | Printed Circuit Board                             |  |

| PMOS    | P-channel Metal-Oxide Semiconductor               |  |

# 14. Revision history

| Table 14. Revision history |              |                    |               |            |  |

|----------------------------|--------------|--------------------|---------------|------------|--|

| Document ID                | Release date | Data sheet status  | Change notice | Supersedes |  |

| NID5100 v.1                | 20240726     | Product data sheet | -             | -          |  |

# 15. Legal information

#### Data sheet status

| Document status<br>[1][2]         | Product<br>status [3] | Definition                                                                                  |

|-----------------------------------|-----------------------|---------------------------------------------------------------------------------------------|

| Objective [short]<br>data sheet   | Development           | This document contains data from<br>the objective specification for<br>product development. |

| Preliminary [short]<br>data sheet | Qualification         | This document contains data from the preliminary specification.                             |

| Product [short]<br>data sheet     | Production            | This document contains the product specification.                                           |

Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <u>https://www.nexperia.com</u>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

**Right to make changes** — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal

injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <u>http://www.nexperia.com/profile/terms</u>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2024. All rights reserved

# Contents

| 1. General description1                                 |

|---------------------------------------------------------|

| 2. Features and benefits1                               |

| 3. Applications1                                        |

| 4. Ordering information2                                |

| 5. Marking2                                             |

| 6. Pin configuration and description2                   |

| 6.1. Pin configuration2                                 |

| 6.2. Pin description2                                   |

| 7. Specifications                                       |

| 7.1. Limiting values                                    |

| 7.2. ESD ratings                                        |

| 7.3. Recommended operating conditions                   |

| 7.4. Recommended components4                            |

| 7.5. Thermal information4                               |

| 7.6. Electrical characteristics                         |

| 7.7. Dynamic characteristics7                           |

| 7.8. Typical Characteristics                            |

| 8. Functional Description13                             |

| 8.1. Functional diagram13                               |

| 8.2. Overview13                                         |

| 8.3. Feature Description 13                             |

| 8.3.1. Enable, control logic and ST pin13               |

| 8.3.2. Device functional modes 14                       |

| 8.3.3. Reverse Polarity Protection (RPP) 14             |

| 8.3.4. Gate regulation amplifier 14                     |

| 8.3.5. Reverse Current Blocking (RCB)15                 |

| 9. Application information 16                           |

| 9.1. Reverse polarity protection16                      |

| 9.2. OR-ing examples                                    |

| 9.2.1. n+1 OR-ing using ideal diodes                    |

| 9.2.2. OR-ing similar supply voltages19                 |

| 9.2.3. n+1 OR-ing using ideal and conventional diodes20 |

| 9.2.4. Paralleling NID5100 for thermal and sustained    |

| high current considerations21                           |

| 9.2.5. Priority OR-ing                                  |

| 9.2.6. OR-ing with discrete MOSFET                      |

| 10. Power supply recommendations24                      |

| 11. Layout                                              |

| 12. Package information 25                              |

| 12.1. Package outline                                   |

| 13. Abbreviations                                       |

| 14. Revision history26                                  |

| 15. Legal information27                                 |

© Nexperia B.V. 2024. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 26 July 2024

nent feedback