Click here to ask an associate for production status of specific part numbers.

## MAX98380

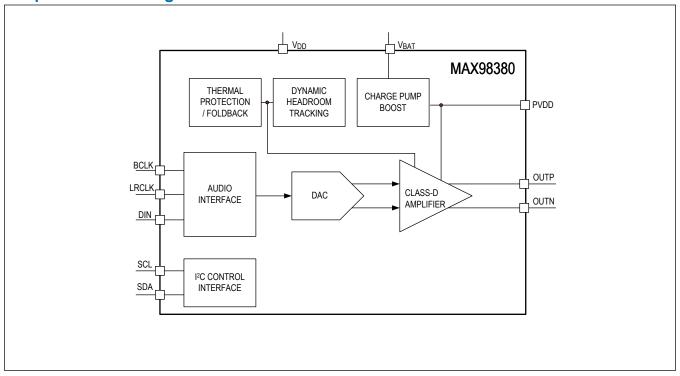

# Small, Boosted, Digital Input Class-D Amplifier

## **General Description**

The MAX98380 is a small, mono Class-D audio amplifier featuring an integrated capacitive boost converter. The device implements a tripler charge pump-based boost converter that efficiently delivers up to 4.85W at 1% THD+N into an  $8\Omega$  load. The capacitive boost replaces the large and expensive inductor required for an inductive boost with smaller, lower-profile capacitors that reduce the total PCB solution.

Additionally, as the power-supply voltage varies due to declining battery life, an on-chip limiter (DHT) automatically optimizes the headroom available to the Class-D amplifier to maintain consistent distortion and listening levels.

Thermal-foldback protection ensures robust behavior when the thermal limits of the device are reached. When enabled, it automatically reduces the output power when the temperature exceeds a user-specified threshold. This allows for uninterrupted music playback even at high ambient temperatures. Traditional thermal protection is also available in addition to robust overcurrent protection.

The device provides a PCM interface for audio data and a standard I<sup>2</sup>C interface for control data communication. The PCM interface supports audio playback using I<sup>2</sup>S, left-justified, and TDM audio data formats. A unique clocking structure eliminates the need for an external master clock for PCM communication. This reduces EMI and possible board coupling issues in addition to reducing the size and pin count.

Active emissions-limiting and edge-rate limiting circuitry greatly reduce EMI. A filterless spread-spectrum modulation scheme eliminates the need for output filtering found in traditional Class-D devices and reduces the component count of the solution.

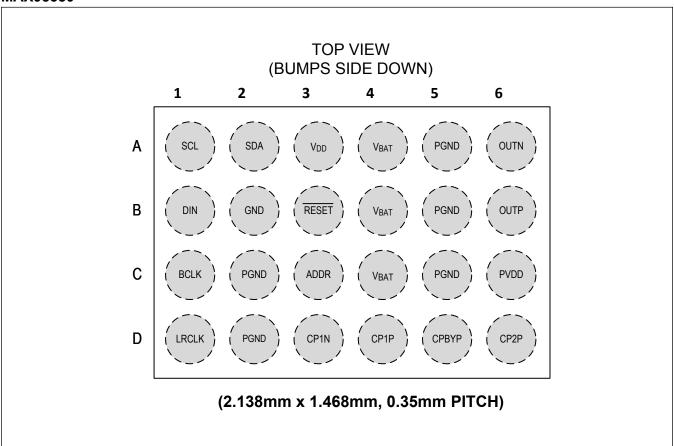

The IC is available in a 0.35mm pitch 24-bump wafer-level package (WLP). It is specified over the extended, -40°C to +85°C temperature range.

## **Applications**

- Smartphones

- Smart Speakers

- IoT Devices

- Tablets

## **Benefits and Features**

- Integrated Capacitive Boost Converter—No Bulky Inductors

- 3.6W Output Power into 6Ω at V<sub>BAT</sub> = 3.7V

- 10mW Total Quiescent Power

- 3ms Turn-On Time

- 80% Efficiency (1.0W into  $R_L = 8\Omega$ ,  $V_{BAT} = 3.7V$ )

- 19.8µV<sub>RMS</sub> Speaker Mode Output Noise

- 16.5µV<sub>RMS</sub> Receiver Mode Output Noise

- Low 0.005% THD+N at 1kHz

- No MCLK Required

- Sample Rates of 8kHz to 192kHz

- Supports Left, Right, or (Left/2 + Right/2) Output in I<sup>2</sup>S and Left-Justified Modes

- Sophisticated Edge Rate Control Enables Filterless Class-D Outputs

- Low RF Susceptibility Rejects TDMA Noise from GSM Radios

- Class-D Switching Frequency Trimmed to 10% for Better EMI Planning

- Extensive Click-and-Pop Reduction Circuitry

- Dynamic Headroom Tracking (DHT)

- Robust Short-Circuit and Thermal Protection

- Available in Space-Saving Package: 1.468mm x 2.138mm, 24-Bump WLP (0.35mm Pitch)

SMBus is a trademark of Intel Corp.

# **Simplified Block Diagram**

# **TABLE OF CONTENTS**

| General Description                              |    |

|--------------------------------------------------|----|

| Applications                                     |    |

| Benefits and Features                            |    |

| Simplified Block Diagram                         |    |

| Absolute Maximum Ratings                         |    |

| Package Information                              |    |

| WLP                                              |    |

| Electrical Characteristics                       |    |

| Typical Operating Characteristics                |    |

| Pin Configuration                                | 26 |

| MAX98380                                         | 26 |

| Pin Description                                  | 26 |

| Functional Diagrams                              | 28 |

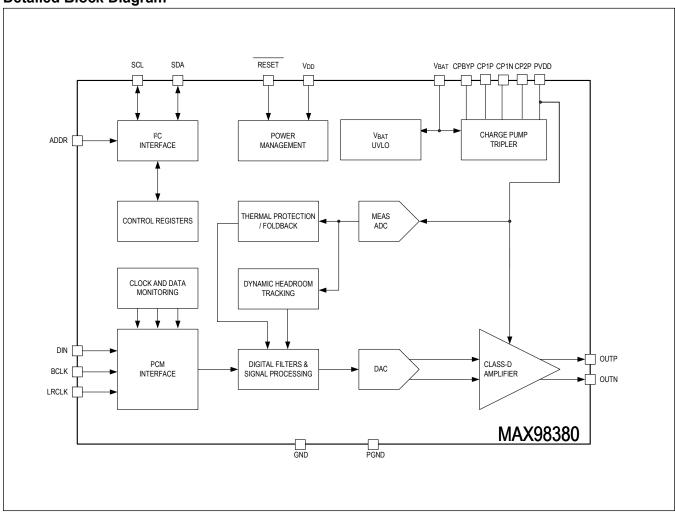

| Detailed Block Diagram                           | 28 |

| Detailed Description                             | 29 |

| Device State Control                             | 29 |

| Hardware Shutdown State                          | 29 |

| Software Shutdown State                          |    |

| Active State                                     |    |

| PCM Interface                                    | 29 |

| PCM Clock Configuration                          | 29 |

| PCM Data Format Configuration                    | 29 |

| I <sup>2</sup> S/Left-Justified Mode             |    |

| TDM Modes                                        |    |

| PCM Data Path Configuration                      |    |

| PCM Data Input                                   |    |

| PCM Interface Timing                             |    |

| Device Status Bits                               |    |

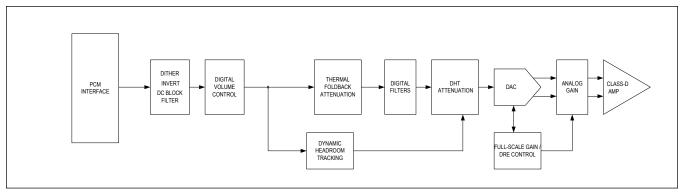

| Speaker Path                                     |    |

| Speaker Path Dither                              |    |

| Speaker Path Data Inversion                      |    |

| Speaker Path DC Blocking Filter                  |    |

| Speaker Path Digital Volume Control              |    |

| Speaker Safe Mode                                |    |

| Speaker Path Maximum Peak Output Voltage Scaling |    |

| DAC Digital Filters                              |    |

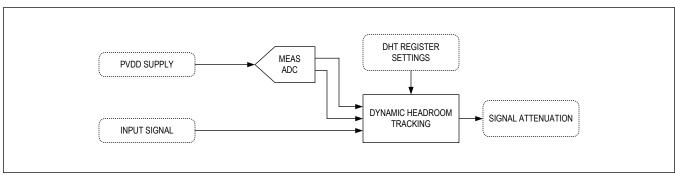

| Dynamic Headroom Tracking (DHT)                  |    |

| DHT Supply Tracking and Headroom                 |    |

| DHT Mode 1—Signal Distortion Limiter (SDL)       |    |

# TABLE OF CONTENTS (CONTINUED)

| DHT Mode 2—Signal Level Limiter (SLL)                 | 43 |

|-------------------------------------------------------|----|

| DHT Attenuation                                       |    |

| DHT Ballistics                                        | 47 |

| Charge Pump Boost                                     | 47 |

| Speaker Amplifier                                     | 48 |

| Class-D Output Short-Circuit Protection               | 48 |

| Click-and-Pop Suppression                             | 48 |

| Ultra-Low EMI Filterless Output Stage                 | 48 |

| Measurement ADC                                       | 49 |

| Measurement ADC Thermal Channel                       | 49 |

| Measurement ADC PVDD Channel                          | 49 |

| Thermal Protection                                    | 49 |

| Thermal Warning and Thermal Shutdown Configuration    | 49 |

| Thermal Shutdown Recovery Configuration               | 50 |

| Thermal Foldback                                      | 50 |

| I <sup>2</sup> C Serial Interface                     | 50 |

| Slave Address                                         | 50 |

| Bit Transfer                                          | 51 |

| START and STOP Conditions                             | 51 |

| Early STOP Conditions                                 | 52 |

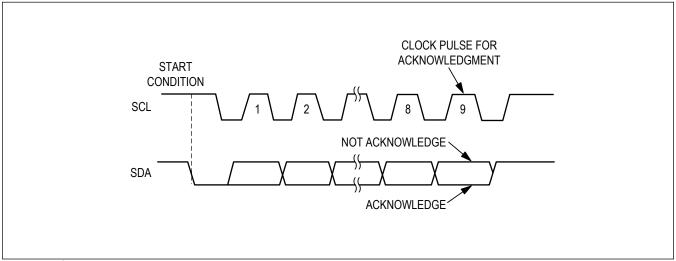

| Acknowledge                                           | 52 |

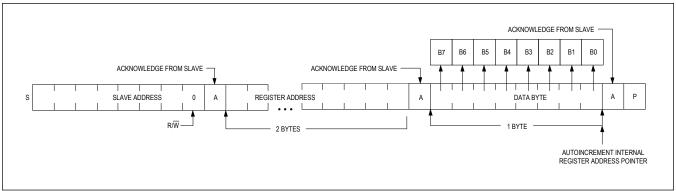

| Write Data Format                                     | 52 |

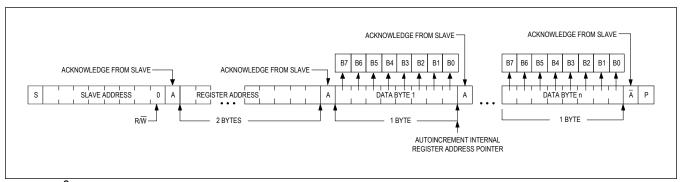

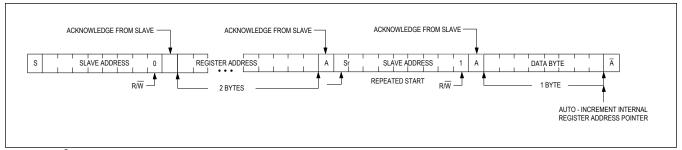

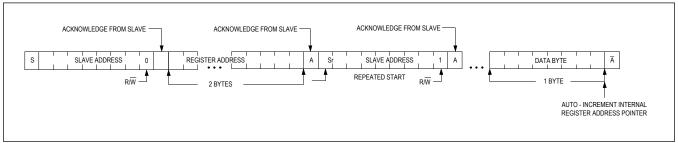

| Read Data Format                                      | 53 |

| I <sup>2</sup> C Register Map                         | 54 |

| Control Bit Field Types and Write Access Restrictions | 54 |

| Register Map                                          | 56 |

| Register Map                                          | 56 |

| Register Details                                      |    |

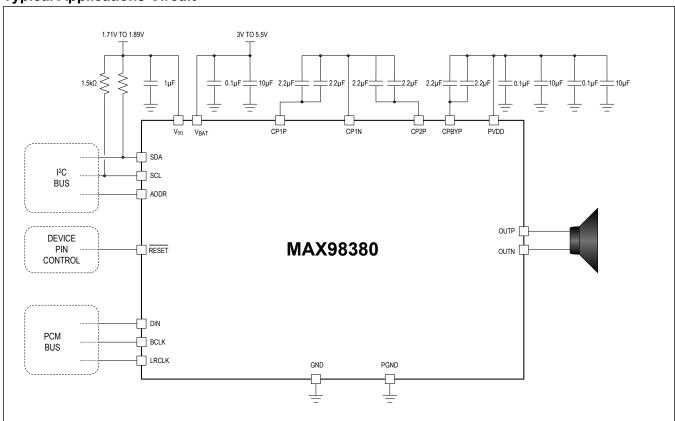

| Applications Information                              | 79 |

| Layout and Grounding                                  | 79 |

| Recommended External Components                       | 79 |

| Typical Application Circuits                          |    |

| Typical Applications Circuit                          | 80 |

| Ordering Information                                  | 80 |

| Revision History                                      | 81 |

# MAX98380

| L | IS' | T ( | ) F | F | IG | U | R | E | S |

|---|-----|-----|-----|---|----|---|---|---|---|

|   |     |     |     |   |    |   |   |   |   |

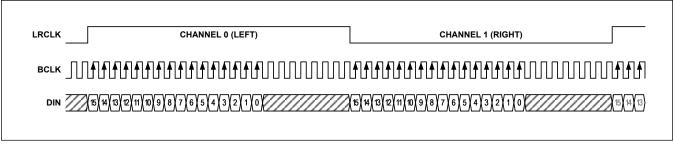

| Figure 1. Standard I <sup>2</sup> S Mode                                                                             | 30 |

|----------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Left-Justified Mode                                                                                        | 30 |

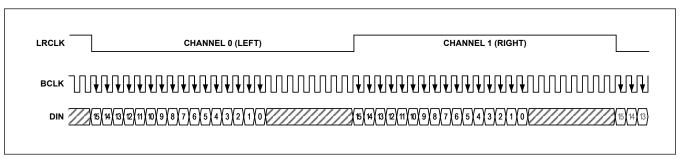

| Figure 3. Left-Justified Mode (LRCLK Inverted)                                                                       | 31 |

| Figure 4. Left-Justified Mode (BCLK Inverted)                                                                        | 31 |

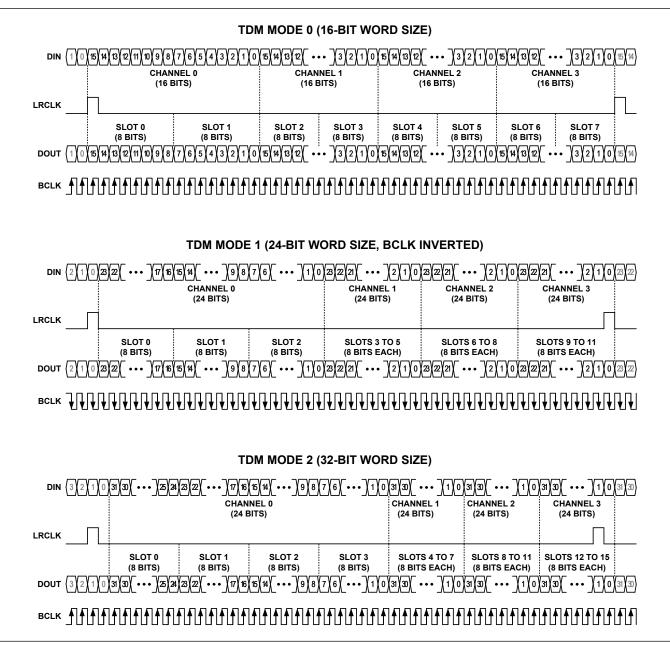

| Figure 5. TDM Modes                                                                                                  | 33 |

| Figure 6. PCM Data Input                                                                                             | 34 |

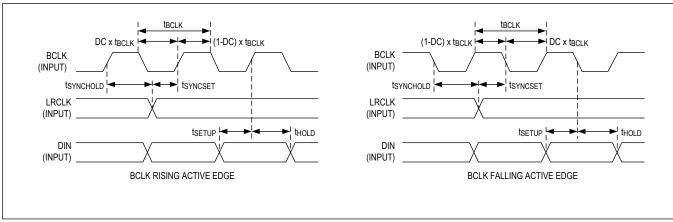

| Figure 7. PCM Interface Timing/Slave Mode—LRCLK, BCLK, DIN Timing Diagram                                            | 34 |

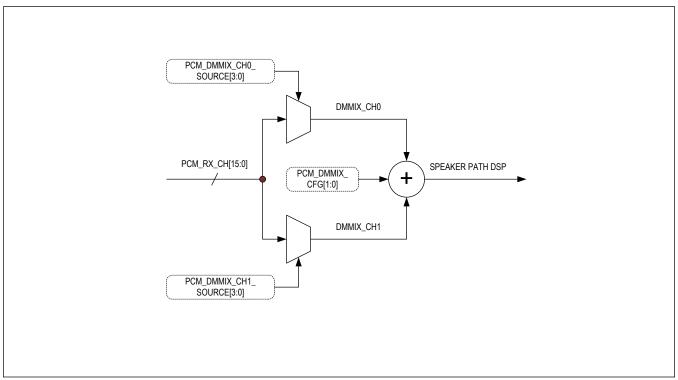

| Figure 8. Speaker Amplifier Path                                                                                     | 36 |

| Figure 9. Simplified Dynamic Headroom Tracking System Block Diagram                                                  | 37 |

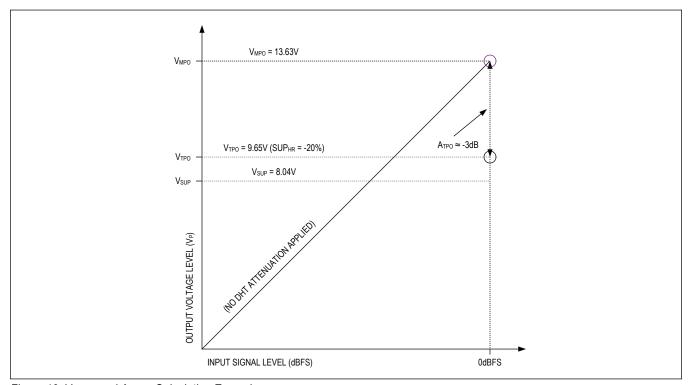

| Figure 10. V <sub>TPO</sub> and A <sub>TPO</sub> Calculation Example                                                 | 38 |

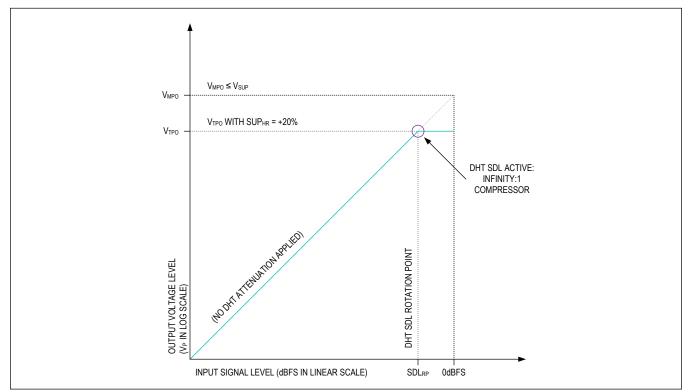

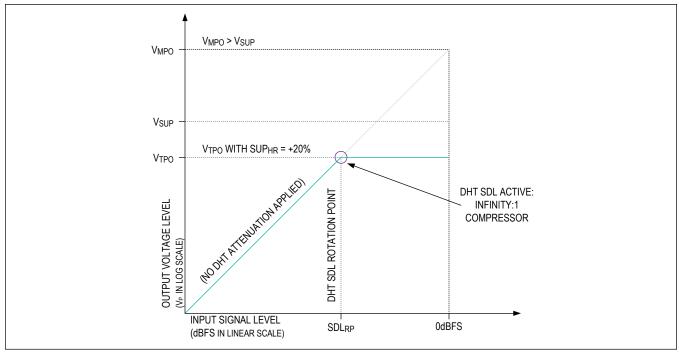

| Figure 11. Signal Distortion Limiter with V <sub>MPO</sub> ≤ V <sub>SUP</sub> and +20% Headroom (SUP <sub>HR</sub> ) | 39 |

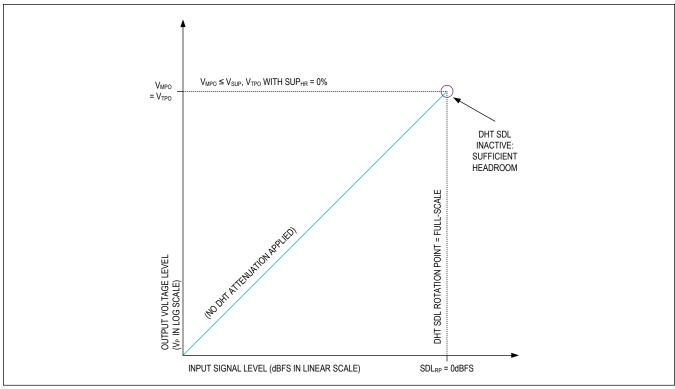

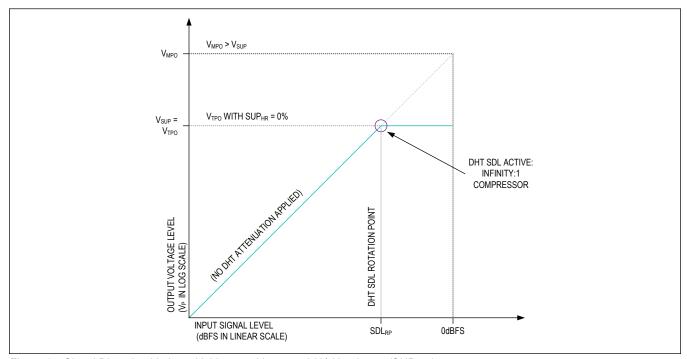

| Figure 12. Signal Distortion Limiter with V <sub>MPO</sub> ≤ V <sub>SUP</sub> and 0% Headroom (SUP <sub>HR</sub> )   | 40 |

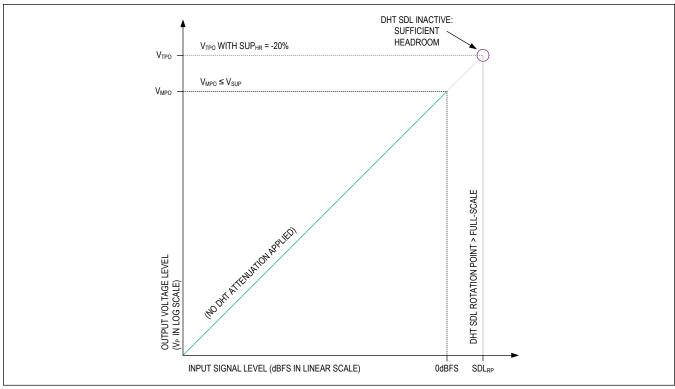

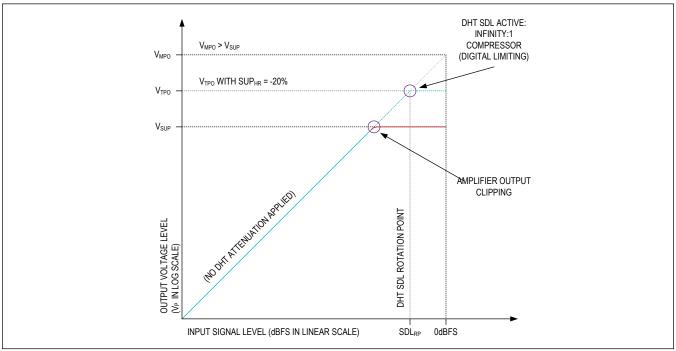

| Figure 13. Signal Distortion Limiter with V <sub>MPO</sub> ≤ V <sub>SUP</sub> and -20% Headroom (SUP <sub>HR</sub> ) | 41 |

| Figure 14. Signal Distortion Limiter with V <sub>MPO</sub> > V <sub>SUP</sub> and +20% Headroom (SUP <sub>HR</sub> ) | 42 |

| Figure 15. Signal Distortion Limiter with V <sub>MPO</sub> > V <sub>SUP</sub> and 0% Headroom (SUP <sub>HR</sub> )   | 42 |

| Figure 16. Signal Distortion Limiter with V <sub>MPO</sub> > V <sub>SUP</sub> and -20% Headroom (SUPHR)              | 43 |

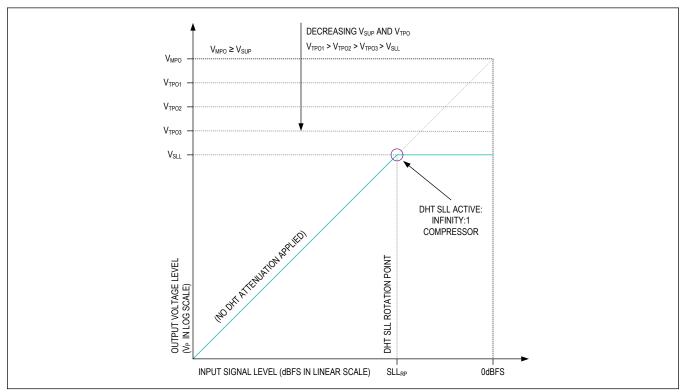

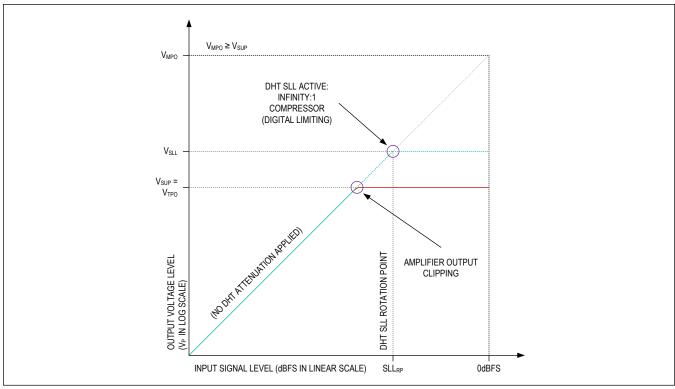

| Figure 17. Signal Level Limiter with V <sub>TPO</sub> > V <sub>SLL</sub> as V <sub>SUP</sub> Decreases               | 44 |

| Figure 18. Signal Level Limiter with V <sub>TPO</sub> < V <sub>SLL</sub> Showing Amplifier Output Clipping           | 45 |

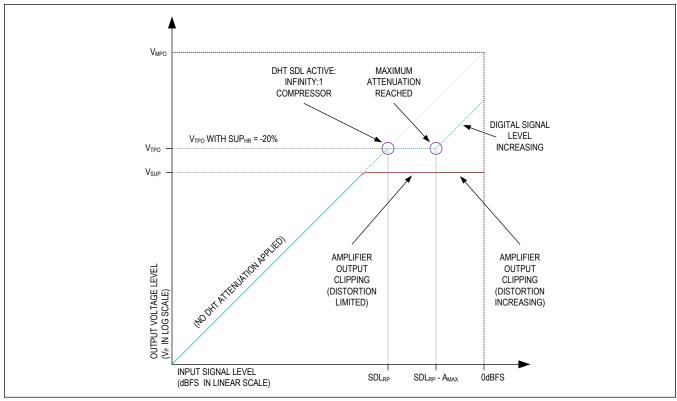

| Figure 19. Distortion Limiter Case with -20% Headroom and A <sub>MAX</sub> Exceeded                                  | 46 |

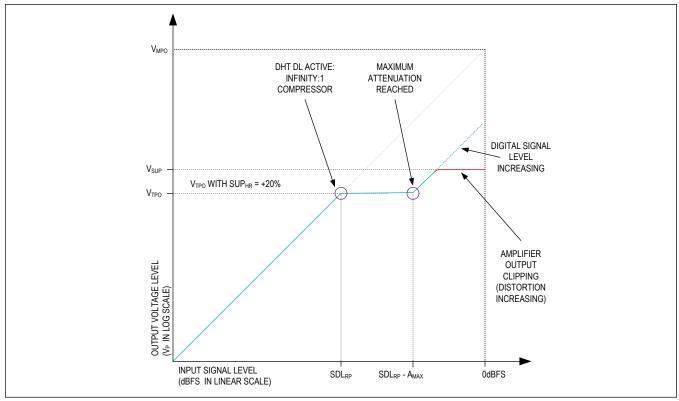

| Figure 20. Distortion Limiter Case with +20% Headroom and A <sub>MAX</sub> Exceeded                                  | 47 |

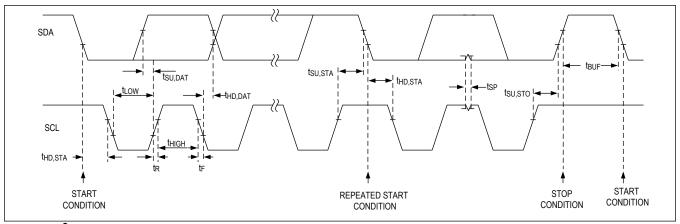

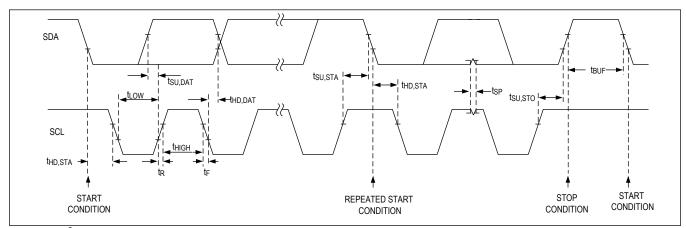

| Figure 21. I <sup>2</sup> C Interface Timing Diagram                                                                 | 51 |

| Figure 22. I <sup>2</sup> C START, STOP, and REPEATED START Conditions                                               | 51 |

| Figure 23. I <sup>2</sup> C Acknowledge                                                                              | 52 |

| Figure 24. I <sup>2</sup> C Writing One Byte of Data to the Slave                                                    | 53 |

| Figure 25. I <sup>2</sup> C Writing n-Bytes of Data to the Slave                                                     | 53 |

| Figure 26. I <sup>2</sup> C Reading One Byte of Data from the Slave                                                  | 54 |

| Figure 27. I <sup>2</sup> C Reading n-Bytes of Data from the Slave                                                   | 54 |

## **LIST OF TABLES**

| Table 1. Supported I <sup>2</sup> S/Left-Justified Mode Configurations |    |

|------------------------------------------------------------------------|----|

| Table 2. Supported TDM Mode Configurations                             | 31 |

| Table 3. Status Bit Event Sources                                      | 35 |

| Table 4. Charge Pump Soft Timer Settings                               | 48 |

| Table 5. I <sup>2</sup> C Slave Address                                | 50 |

| Table 6. Control Bit Types and Write Access Restrictions               | 54 |

| Table 7. Component List                                                | 79 |

## **Absolute Maximum Ratings**

| V <sub>BAT</sub> to PGND         | 0.3V to +6V                                  |

|----------------------------------|----------------------------------------------|

| V <sub>DD</sub> , RESET, ADDR, S | CL, SDA, BCLK, LRCLK, and DIN to             |

| GND                              | 0.3V to +2.2V                                |

| PVDD to PGND                     | CPBYP - 0.3V to min(CPBYP + 6, 16)V          |

| CPBYP to PGND                    | $V_{BAT}$ - 0.3V to min( $V_{BAT}$ + 6, 12)V |

| GND to PGND                      | 0.1V to +0.1V                                |

| Duration of OUTP or Ol           | UTN short circuit to PGND, PVDD, or          |

| VRAT                             | Continuous                                   |

| Duration of OUTP short to OUTN |                                    |

|--------------------------------|------------------------------------|

| Continuous power dissipation ( | $T_A = +70^{\circ}C$ ) WLP (derate |

| 18.87mW/°C above +70°C)        | 1.51W                              |

| Junction temperature           | +150°C                             |

| Operating temperature range    | 40°C to +85°C                      |

| Storage temperature range      | 65°C to +150°C                     |

| Soldering temperature (reflow) | +260°C                             |

|                                |                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### **WLP**

| Package Code                                           | W241J2+1                       |

|--------------------------------------------------------|--------------------------------|

| Outline Number                                         | 21-100569                      |

| Land Pattern Number                                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:                  |                                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 53°C/W                         |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                            |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

$(V_{BAT} = 3.7V,\ V_{VDD} = 1.8V,\ V_{GND} = 0V,\ V_{PGND} = 0V,\ C_{VBAT} = 1\ x\ 10\mu\text{F},\ 1\ x\ 0.1\mu\text{F},\ C_{VDD} = 1\mu\text{F},\ C_{PVDD} = 2\ x\ 10\mu\text{F},\ 1\ x\ 0.1\mu\text{F},\ C_{CPBYP} = 2\ x\ 2.2\mu\text{F},\ 1\ x\ 0.1\mu\text{F},\ C_{CP1} = 2\ x\ 2.2\mu\text{F},\ C_{CP2} = 2\ x\ 2.2\mu\text{F},\ f_{BCLK} = 3.072MHz,\ f_{LRCLK} = 48kHz,\ Z_{SPK} = \infty\ \text{between OUTP}$  and OUTN, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , typical values are at  $T_A = +25^{\circ}\text{C}$ ) (Note 1)

| PARAMETER                                          | SYMBOL           | CONDITIONS                                                        | MIN     | TYP | MAX   | UNITS |

|----------------------------------------------------|------------------|-------------------------------------------------------------------|---------|-----|-------|-------|

| SYSTEM                                             |                  |                                                                   |         |     |       |       |

| V <sub>BAT</sub> Supply Voltage<br>Operating Range | V <sub>BAT</sub> | Guaranteed by PSRR test                                           | 3.0     |     | 5.5   | V     |

| V <sub>BAT</sub> Supply Voltage                    | V <sub>BAT</sub> | Device is functional but parametric performance is not guaranteed | 2.5     |     |       | V     |

| V <sub>DD</sub> Supply Voltage<br>Range            | V <sub>DD</sub>  | Guaranteed by PSRR test                                           | 1.71    | 1.8 | 1.89  | V     |

| V <sub>BAT</sub> Undervoltage V <sub>UVLO</sub>    |                  | V <sub>BAT</sub> rising                                           | 2.6     |     | 2.8   | V     |

|                                                    |                  | V <sub>BAT</sub> falling                                          | 2.3 2.5 |     | V     |       |

| Outros and Davis                                   | D-               | T <sub>A</sub> = +25°C, BST_BYPASS_MODE = 0                       | 30      |     | mW    |       |

| Quiescent Power                                    | PQ               | T <sub>A</sub> = +25°C, BST_BYPASS_MODE = 1                       | 10      |     | 11100 |       |

$(V_{BAT} = 3.7V, \ V_{VDD} = 1.8V, \ V_{GND} = 0V, \ V_{PGND} = 0V, \ C_{VBAT} = 1 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{VDD} = 1\mu\text{F}, \ C_{PVDD} = 2 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ Z_{SPK} = \infty \ \text{between OUTP} \ \text{and OUTN, AC Measurement Bandwidth} = 20Hz \ \text{to } 20kHz, \ T_A = T_{MIN} \ \text{to } T_{MAX}, \ \text{typical values are at } T_A = +25^{\circ}\text{C}) \ (\text{Note 1})$

| PARAMETER                                     | SYMBOL                       | CONE                                                                                      | OITIONS                                                           | MIN | TYP   | MAX   | UNITS |

|-----------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-------|-------|-------|

|                                               | lo ver                       | T <sub>A</sub> = +25°C, V <sub>BAT</sub> ,<br>BST_BYPASS_MOI                              | DE = 0                                                            |     | 7.2   |       |       |

| Quiescent Current                             | I <sub>Q_VBAT</sub>          | T <sub>A</sub> = +25°C, V <sub>BAT</sub> ,<br>BST_BYPASS_MOI                              | T <sub>A</sub> = +25°C, V <sub>BAT</sub> ,<br>BST_BYPASS_MODE = 1 |     |       |       | mA    |

|                                               | I <sub>Q_VDD</sub>           | $T_A = +25^{\circ}C, V_{DD}$                                                              |                                                                   |     | 2.8   |       |       |

| V <sub>BAT</sub> Hardware<br>Shutdown Current | IVBAT_HW_SH<br>DN            | T <sub>A</sub> = +25°C                                                                    |                                                                   |     | 0.3   | 1.0   | μA    |

| V <sub>DD</sub> Hardware<br>Shutdown Current  | IVDD_HW_SHD<br>N             | T <sub>A</sub> = +25°C                                                                    |                                                                   |     | 0.1   | 1     | μA    |

| V <sub>BAT</sub> Software<br>Shutdown Current | IVBAT_SW_SH<br>DN            | T <sub>A</sub> = +25°C                                                                    |                                                                   |     | 0.3   | 1.0   | μA    |

| V <sub>DD</sub> Software Shutdown<br>Current  | VDD_SW_SHD<br>N              | T <sub>A</sub> = +25°C                                                                    |                                                                   |     | 1.4   | 2.5   | μA    |

|                                               |                              | Software Shutdown volume ramp disable                                                     | to full gain audio out,<br>ed                                     |     | 2     | 3     |       |

| Turn-On Time                                  | t <sub>ON</sub>              | Software Shutdown volume ramp enable                                                      | to full gain audio out,<br>ed                                     |     | 5.5   | 6.5   | ms    |

|                                               |                              | From SPK_EN bit so operation, volume ra                                                   |                                                                   |     | 0.75  |       |       |

|                                               |                              | From full operation to software shutdown (RESET = V <sub>DD</sub> ), volume ramp disabled |                                                                   |     | 30    | 100   | μs    |

| Turn-Off Time                                 | <sup>t</sup> OFF             | From full operation t<br>(RESET = V <sub>DD</sub> ), f <sub>S</sub><br>ramp enabled       |                                                                   | 8.4 | 10.5  | mo    |       |

| Turri-On Time                                 |                              | From full operation t<br>(RESET = V <sub>DD</sub> ), f <sub>S</sub><br>ramp enabled       |                                                                   | 6   | 6.5   | ms ms |       |

|                                               |                              | From SPK_EN bit so disabled, volume rai                                                   |                                                                   |     | 0.025 |       | ms    |

|                                               | f = 1kHz, Z <sub>SPK</sub> = |                                                                                           | P <sub>OUT</sub> = 1.0W,<br>BST_BYPASS_MO<br>DE = 0               | 80  |       |       |       |

| System Efficiency                             | η                            | 6Ω + 33μΗ                                                                                 | P <sub>OUT</sub> = 1.0W,<br>BST_BYPASS_MO<br>DE = 1               |     | 87    |       | 0/    |

|                                               |                              | f = 1kHz, Z <sub>SPK</sub> =                                                              | P <sub>OUT</sub> = 1.0W,<br>BST_BYPASS_MO<br>DE = 0               |     | 80    | %     |       |

|                                               |                              | 8Ω + 33μΗ                                                                                 | P <sub>OUT</sub> = 0.8W,<br>BST_BYPASS_MO<br>DE = 1               |     | 88    |       |       |

| CHARGE PUMP BOOST                             | CONVERTER                    |                                                                                           |                                                                   |     |       |       |       |

| Maximum Soft-Start<br>Time                    | tstr                         | CP_SOFT_TIMER = (2x2.2µF/2x2.2µF)                                                         | = 0x3, nominal caps                                               |     | 1.725 |       | ms    |

$(V_{BAT} = 3.7V, \ V_{VDD} = 1.8V, \ V_{GND} = 0V, \ V_{PGND} = 0V, \ C_{VBAT} = 1 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{VDD} = 1\mu\text{F}, \ C_{PVDD} = 2 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ Z_{SPK} = \infty \ \text{between OUTP} \ \text{and OUTN, AC Measurement Bandwidth} = 20Hz \ \text{to } 20kHz, \ T_A = T_{MIN} \ \text{to } T_{MAX}, \ \text{typical values are at } T_A = +25^{\circ}\text{C}) \ (\text{Note 1})$

| PARAMETER                            | SYMBOL            | СО                                                                                                                                                                                                                                                                                                                                                 | NDITIONS                                                                                                                                                  | MIN   | TYP                  | MAX                                                                                                                                            | UNITS |  |  |  |       |

|--------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|-------|

| Startup Input Current<br>Limit       | ISTARTUP          |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |       | 0.5                  |                                                                                                                                                | А     |  |  |  |       |

| Switching Frequency                  | f <sub>SW</sub>   |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           | 0.998 | 1.024                | 1.05                                                                                                                                           | MHz   |  |  |  |       |

|                                      |                   | V <sub>BAT</sub> = 3.0V to 4.<br>BST_BYPASS_M                                                                                                                                                                                                                                                                                                      | .5V,<br>1ODE = 0                                                                                                                                          |       | 3 x V <sub>BAT</sub> |                                                                                                                                                |       |  |  |  |       |

| Output Voltage                       | V <sub>PVDD</sub> | V <sub>BAT</sub> > 4.5V, BS                                                                                                                                                                                                                                                                                                                        | T_BYPASS_MODE = 0                                                                                                                                         |       | 13.5                 |                                                                                                                                                | V     |  |  |  |       |

|                                      |                   | V <sub>BAT</sub> = 3.0V to 5.<br>BST_BYPASS_M                                                                                                                                                                                                                                                                                                      | AT = 3.0V to 5.5V,<br>T_BYPASS_MODE = 1                                                                                                                   |       |                      |                                                                                                                                                |       |  |  |  |       |

| Overvoltage Protection               | OVP               | Rising edge                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                           | 15    | 15.5                 | 16                                                                                                                                             | V     |  |  |  |       |

| Overvoitage Protection               | OVF               | Falling edge                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                           | 14.9  | 15.4                 | 15.8                                                                                                                                           | \ \ \ |  |  |  |       |

| CLASS-D AMPLIFIER                    |                   |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |       |                      |                                                                                                                                                |       |  |  |  |       |

| Output Offset Voltage                | V <sub>OS</sub>   | T <sub>A</sub> = +25°C                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           | -3.0  | ±0.3                 | +3.0                                                                                                                                           | mV    |  |  |  |       |

| Click-and-Pop Level                  | K <sub>CP</sub>   | Peak voltage, A-weighted, 32 samples per second, digital silence used for input signal, $Z_{SPK} = 8\Omega + 33\mu H$ or $6\Omega + 33\mu H$ , into Standby or Shutdown  Peak voltage, A-weighted, 32 samples per second, digital silence used for input signal, $Z_{SPK} = 8\Omega + 33\mu H$ or $6\Omega + 33\mu H$ , out of Standby or Shutdown |                                                                                                                                                           |       |                      | Peak voltage, A-weighted, 32 samples per second, digital silence used for input signal, $Z_{SPK} = 8\Omega + 33\mu H$ or $6\Omega + 33\mu H$ , |       |  |  |  | - dBV |

| Click-aliu-r op Level                | KCb               |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |       |                      |                                                                                                                                                | ub v  |  |  |  |       |

| V <sub>BAT</sub> Supply Rejection DC | PSRR              | $T_A = +25^{\circ}C$ , digital signal, $Z_{SPK} = \infty$ , 5.5V                                                                                                                                                                                                                                                                                   | T <sub>A</sub> = +25°C, digital silence used for input signal, Z <sub>SPK</sub> = ∞, DC, V <sub>VBAT</sub> = 3.0V to 5.5V                                 |       | 80                   |                                                                                                                                                | dB    |  |  |  |       |

|                                      |                   |                                                                                                                                                                                                                                                                                                                                                    | $f_{RIPPLE}$ = 217Hz,<br>$T_{A}$ = +25°C, digital<br>silence used for<br>input signal, Z <sub>SPK</sub><br>= 8Ω + 33μH or 6Ω<br>+ 33μH                    |       | 75                   |                                                                                                                                                |       |  |  |  |       |

| V <sub>BAT</sub> Supply Rejection AC | PSRR              | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub>                                                                                                                                                                                                                                                                                                          | $f_{RIPPLE}$ = 1kHz, $T_{A}$ = +25°C, digital silence used for input signal, $Z_{SPK}$ = 8Ω + 33μH or 6Ω + 33μH                                           |       | 75                   |                                                                                                                                                | dB    |  |  |  |       |

|                                      |                   |                                                                                                                                                                                                                                                                                                                                                    | $f_{RIPPLE}$ = 10kHz,<br>$T_A$ = +25°C, digital<br>silence used for<br>input signal, $Z_{SPK}$<br>= 8 $\Omega$ + 33 $\mu$ H or 6 $\Omega$<br>+ 33 $\mu$ H |       | 75                   |                                                                                                                                                |       |  |  |  |       |

| V <sub>DD</sub> Supply Rejection DC  | PSRR              | $T_A$ = +25°C, digital signal, $Z_{SPK}$ = $\infty$ , 1.89V                                                                                                                                                                                                                                                                                        | al silence used for input<br>DC, V <sub>DD</sub> = 1.71V to                                                                                               | 60    | 83                   |                                                                                                                                                | dB    |  |  |  |       |

$(V_{BAT} = 3.7V, \ V_{VDD} = 1.8V, \ V_{GND} = 0V, \ V_{PGND} = 0V, \ C_{VBAT} = 1 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{VDD} = 1\mu\text{F}, \ C_{PVDD} = 2 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ Z_{SPK} = \infty \ \text{between OUTP} \ \text{and OUTN, AC Measurement Bandwidth} = 20Hz \ \text{to } 20kHz, \ T_A = T_{MIN} \ \text{to } T_{MAX}, \ \text{typical values are at } T_A = +25^{\circ}\text{C}) \ (\text{Note 1})$

| PARAMETER                            | SYMBOL | COND                                                                         | ITIONS                                                                                                                                                    | MIN | TYP  | MAX | UNITS |  |

|--------------------------------------|--------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|--|

| V <sub>DD</sub> Supply Rejection AC  |        |                                                                              | $f_{RIPPLE}$ = 217Hz,<br>$T_A$ = +25°C, digital<br>silence used for<br>input signal, $Z_{SPK}$<br>= 8 $\Omega$ + 33 $\mu$ H or 6 $\Omega$<br>+ 33 $\mu$ H |     | 89   |     |       |  |

|                                      | PSRR   | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub>                                    | $f_{RIPPLE}$ = 1kHz, $T_A$<br>= +25°C, digital<br>silence used for<br>input signal, $Z_{SPK}$<br>= 8 $\Omega$ + 33 $\mu$ H or 6 $\Omega$<br>+ 33 $\mu$ H  |     | 87   |     | dB    |  |

|                                      |        |                                                                              | $f_{RIPPLE}$ = 10kHz,<br>$T_A$ = +25°C, digital<br>silence used for<br>input signal, $Z_{SPK}$<br>= 8 $\Omega$ + 33 $\mu$ H or 6 $\Omega$<br>+ 33 $\mu$ H |     | 75   |     |       |  |

|                                      | Роит   | $V_{BAT} = 3.7V,$<br>$THD+N \le 10\%,$<br>$Z_{SPK} = 6\Omega + 33\mu H$      | BST_BYPASS_MO<br>DE = 0                                                                                                                                   |     | 4.2  |     |       |  |

|                                      |        | $V_{BAT}$ = 3.7V,<br>THD+N $\leq$ 1%,<br>$Z_{SPK}$ = 6 $\Omega$ + 33 $\mu$ H | BST_BYPASS_MO<br>DE = 0                                                                                                                                   |     | 3.6  |     | w     |  |

|                                      |        |                                                                              | BST_BYPASS_MO<br>DE = 1                                                                                                                                   |     | 0.88 |     |       |  |

| Output Power                         |        | $V_{BAT} = 3.7V,$<br>$THD+N \le 10\%,$<br>$Z_{SPK} = 6\Omega + 33\mu H$      | BST_BYPASS_MO<br>DE = 1                                                                                                                                   |     | 1.1  |     |       |  |

|                                      |        | $V_{BAT} = 4.4V,$<br>$THD+N \le 1\%,$<br>$Z_{SPK} = 8\Omega + 33\mu H$       | BST_BYPASS_MO<br>DE = 0                                                                                                                                   |     | 4.85 |     |       |  |

|                                      |        | $V_{BAT} = 3.7V,$<br>$THD+N \le 10\%,$<br>$Z_{SPK} = 8\Omega + 33\mu H$      | BST_BYPASS_MO<br>DE = 0                                                                                                                                   |     | 4.1  |     |       |  |

| Total Harmonic<br>Distortion + Noise | THD+N  |                                                                              | $P_{OUT}$ = 1W, $Z_{SPK}$<br>= 6Ω + 33μH, (Note<br>3)                                                                                                     |     | -86  |     | dB    |  |

|                                      |        | f = 1kHz, T <sub>A</sub> =<br>+25°C                                          | $P_{OUT}$ = 1W, $Z_{SPK}$<br>= 8Ω + 33μH                                                                                                                  |     | -85  |     |       |  |

|                                      |        | 200                                                                          | $P_{OUT}$ = 500mW,<br>$Z_{SPK}$ = 6 $\Omega$ + 33 $\mu$ H,<br>BST_BYPASS_MO<br>DE = 1                                                                     |     | -85  |     |       |  |

| Intermodulation<br>Distortion        | IMD    | ITU-R, 19kHz/20kHz<br>$Z_{SPK}$ = 8 $\Omega$ + 33 $\mu$ H                    | z, 1:1, V <sub>IN</sub> = -3dBFS,                                                                                                                         |     | -60  |     | dB    |  |

$(V_{BAT} = 3.7V, \ V_{VDD} = 1.8V, \ V_{GND} = 0V, \ V_{PGND} = 0V, \ C_{VBAT} = 1 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{VDD} = 1\mu\text{F}, \ C_{PVDD} = 2 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ Z_{SPK} = \infty \ \text{between OUTP} \ \text{and OUTN, AC Measurement Bandwidth} = 20Hz \ \text{to } 20kHz, \ T_A = T_{MIN} \ \text{to } T_{MAX}, \ \text{typical values are at } T_A = +25^{\circ}\text{C}) \ (\text{Note 1})$

| PARAMETER                                 | SYMBOL           | COND                                                                                                                                   | ITIONS                  | MIN                       | TYP  | MAX                   | UNITS             |

|-------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------|------|-----------------------|-------------------|

| Output Naisa                              |                  | A-weighted, 24-bit                                                                                                                     | BST_BYPASS_MO<br>DE = 0 |                           | 19.8 |                       | \                 |

| Output Noise                              | e <sub>Nd</sub>  | or 32-bit data                                                                                                                         | BST_BYPASS_MO<br>DE = 1 |                           | 16.5 |                       | μV <sub>RMS</sub> |

| Dynamic Range                             | DR               | A-weighted, -60dB<br>1kHz output signal,<br>normalized to full<br>scale (THD+N =<br>1%), 24- or 32-bit<br>data T <sub>A</sub> = +25°C  | BST_BYPASS_MO<br>DE = 0 |                           | -108 |                       | dB                |

| Dynamic Range                             | DK .             | A-weighted, -60dB<br>1kHz output signal,<br>normalized to full<br>scale (THD+N =<br>1%), 24- or 32-bit<br>data, T <sub>A</sub> = +25°C | BST_BYPASS_MO<br>DE = 1 |                           | -103 |                       | ub                |

| Full-Scale Output                         | FC               | BST_BYPASS_MOD                                                                                                                         | DE = 0                  |                           | 13.4 |                       | 4D\/              |

| Voltage                                   | FS               | BST_BYPASS_MOD                                                                                                                         | DE = 1                  |                           | 1.67 |                       | dBV               |

| Output Current Limit                      | I <sub>LIM</sub> |                                                                                                                                        |                         | 2.7                       |      |                       | Α                 |

| Output Current Limit<br>Auto-Restart Time |                  |                                                                                                                                        |                         |                           | 27   |                       | ms                |

| Frequency Response                        |                  |                                                                                                                                        |                         | -0.2                      |      | +0.3                  | dB                |

| Class-D Switching Frequency               | f <sub>SW</sub>  |                                                                                                                                        |                         | 270                       | 300  | 315                   | kHz               |

| Spread-Spectrum<br>Bandwidth              | f <sub>SSM</sub> |                                                                                                                                        |                         |                           | ±14  |                       | kHz               |

| Minimum Load<br>Resistance                | RL               |                                                                                                                                        |                         |                           | 6    |                       | Ω                 |

| Maximum Device to Device Phase Error      |                  | Output phase shift be devices from 20Hz to sample rates and DA                                                                         | 20kHz across all        |                           | 3    |                       | deg               |

| DAC DIGITAL FILTER (L                     | RCLK < 50kHz)    |                                                                                                                                        |                         |                           |      |                       |                   |

| December of Custoff                       | f <sub>PLP</sub> | Ripple < δ <sub>P</sub>                                                                                                                |                         | 0.452 x<br>f <sub>S</sub> |      |                       | Hz                |

| Passband Cutoff                           |                  | Droop < -3dB                                                                                                                           |                         | 0.457 x<br>f <sub>S</sub> |      |                       | Hz                |

| Passband Ripple                           | $\delta_{P}$     | f < f <sub>PLP</sub> , referenced<br>1kHz                                                                                              | to signal level at      | -0.1                      |      | +0.1                  | dB                |

| Stopband Cutoff                           | f <sub>SLP</sub> | Attenuation > δ <sub>S</sub>                                                                                                           |                         |                           |      | 0.49 x f <sub>S</sub> | Hz                |

| Stopband Attenuation                      | δ <sub>S</sub>   | f > f <sub>SLP</sub>                                                                                                                   |                         | 75                        |      |                       | dB                |

| Group Delay                               |                  | f = 1kHz                                                                                                                               |                         |                           | 5    |                       | samples           |

$(V_{BAT} = 3.7V, \ V_{VDD} = 1.8V, \ V_{GND} = 0V, \ V_{PGND} = 0V, \ C_{VBAT} = 1 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{VDD} = 1\mu\text{F}, \ C_{PVDD} = 2 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPBYP} = 2 \ x \ 2.2\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CP1} = 2 \ x \ 2.2\mu\text{F}, \ C_{CP2} = 2 \ x \ 2.2\mu\text{F}, \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ Z_{SPK} = \infty \ \text{between OUTP}$  and OUTN, AC Measurement Bandwidth = 20Hz to 20kHz, \ T\_A = T\_{MIN} \text{ to } T\_{MAX}, \text{ typical values are at } T\_A = +25^{\circ}\text{C}) \text{ (Note 1)}

| PARAMETER                       | SYMBOL                | CONDITIONS                                                        | MIN                        | TYP   | MAX                        | UNITS   |

|---------------------------------|-----------------------|-------------------------------------------------------------------|----------------------------|-------|----------------------------|---------|

| DAC DIGITAL FILTER (L           | RCLK > 50kHz          | 2)                                                                | •                          |       |                            | •       |

|                                 | f <sub>PLP</sub>      | Ripple $< \delta_P$ , $88.2$ kHz $\le f_S \le 96$ kHz             | 0.227 x<br>f <sub>S</sub>  |       |                            | Hz      |

| Passband Cutoff                 |                       | Droop < -3dB, 88.2kHz ≤ f <sub>S</sub> ≤ 96kHz                    | 0.314 x<br>f <sub>S</sub>  |       |                            | Hz      |

| Passband Culon                  | f <sub>PLP</sub>      | Ripple < $\delta_P$ , 176.4kHz ≤ $f_S$ ≤ 192kHz                   | 0.1135 x<br>f <sub>S</sub> |       |                            | Hz      |

|                                 |                       | Droop < -3dB cutoff, 176.4kHz ≤ f <sub>S</sub> ≤ 192kHz           | 0.232 x<br>f <sub>S</sub>  |       |                            | Hz      |

| Passband Ripple                 | δρ                    | f < f <sub>PLP</sub> , referenced to signal level at 1kHz         | -0.25                      |       | +0.25                      | dB      |

| Stopband Cutoff                 | f <sub>SLP</sub>      | Attenuation < δ <sub>S</sub>                                      |                            |       | 0.495 x<br>f <sub>S</sub>  | Hz      |

| Stopband Attenuation            | $\delta_{\mathrm{S}}$ | f > f <sub>SLP</sub>                                              | 75                         |       |                            | dB      |

| Max Group Delay                 |                       | f = 1kHz                                                          |                            | 5.5   |                            | samples |

| DAC DIGITAL FILTERS/            | DIGITAL DC BI         | LOCKING FILTER                                                    | •                          |       |                            |         |

| DC Attenuation                  |                       |                                                                   | 80                         |       |                            | dB      |

| DC Blocking Filter -3dB         | f <sub>C</sub>        | For f <sub>s</sub> = 8kHz, 16kHz, 32kHz, 48kHz, 96kHz, and 192kHz |                            | 1.872 |                            | Hz      |

| Cutoff Frequency                |                       | For f <sub>S</sub> = 44.1kHz, 88.2kHz                             |                            | 1.72  |                            |         |

| DIGITAL I/O / INPUT—DI          | IN, BCLK, LRC         | LK                                                                |                            |       |                            |         |

| Input Voltage High              | V <sub>IH</sub>       |                                                                   | 0.7 x<br>V <sub>VDD</sub>  |       |                            | V       |

| Input Voltage Low               | V <sub>IL</sub>       |                                                                   |                            |       | 0.3 x<br>V <sub>VDD</sub>  | V       |

| Input Leakage Current           |                       |                                                                   | -1                         |       | +1                         | μA      |

| Input Hysteresis                | V <sub>HYS</sub>      | Note 3                                                            | 75                         |       |                            | mV      |

| Maximum Input<br>Capacitance    | C <sub>IN</sub>       |                                                                   |                            | 10    |                            | pF      |

| Internal Pulldown<br>Resistance | R <sub>PD</sub>       | BCLK, LRCLK and DIN                                               |                            | 3     |                            | ΜΩ      |

| DIGITAL I/O / INPUT—R           | ESET                  |                                                                   | ·                          |       |                            |         |

| Input Voltage High              | V <sub>IH</sub>       |                                                                   | 0.75 x<br>V <sub>VDD</sub> |       |                            | V       |

| Input Voltage Low               | V <sub>IL</sub>       |                                                                   |                            |       | 0.25 x<br>V <sub>VDD</sub> | V       |

| Input Leakage Current           |                       |                                                                   | -1                         |       | +1                         | μA      |

| Input Hysteresis                | V <sub>HYS</sub>      | Note 3                                                            | 75                         |       |                            | mV      |

| Maximum Input<br>Capacitance    | C <sub>IN</sub>       |                                                                   |                            | 10    |                            | pF      |

$(V_{BAT} = 3.7V, \ V_{VDD} = 1.8V, \ V_{GND} = 0V, \ V_{PGND} = 0V, \ C_{VBAT} = 1 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{VDD} = 1\mu\text{F}, \ C_{PVDD} = 2 \ x \ 10\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ 1 \ x \ 0.1\mu\text{F}, \ C_{CPD} = 2 \ x \ 2.2\mu\text{F}, \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ Z_{SPK} = \infty \ \text{between OUTP} \ \text{and OUTN, AC Measurement Bandwidth} = 20Hz \ \text{to } 20kHz, \ T_A = T_{MIN} \ \text{to } T_{MAX}, \ \text{typical values are at } T_A = +25^{\circ}\text{C}) \ (\text{Note 1})$

| PARAMETER                                             | SYMBOL               | CONDITIONS                                                                                                       | MIN                       | TYP | MAX                       | UNITS  |

|-------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|--------|

| DIGITAL I/O / INPUT—SO                                | CL, SDA, ADDR        |                                                                                                                  | •                         |     |                           |        |

| Input Voltage High                                    | V <sub>IH</sub>      |                                                                                                                  | 0.7 x<br>V <sub>VDD</sub> |     |                           | V      |

| Input Voltage Low                                     | $V_{IL}$             |                                                                                                                  |                           |     | 0.3 x<br>V <sub>VDD</sub> | ٧      |

| Input Leakage Current                                 |                      | T <sub>A</sub> = +25°C, input high                                                                               | -1                        |     | +1                        | μA     |

| Input Hysteresis                                      | $V_{HYS}$            | Note 3                                                                                                           | 75                        |     |                           | mV     |

| Maximum Input<br>Capacitance                          | C <sub>IN</sub>      |                                                                                                                  |                           | 10  |                           | pF     |

| DIGITAL I/O / OPEN DRA                                | IN OUTPUT—S          | DA                                                                                                               |                           |     |                           |        |

| Output Voltage Low                                    | V <sub>OL</sub>      | I <sub>SINK</sub> = 3mA                                                                                          |                           |     | 0.4                       | V      |

| Output High Leakage<br>Current                        | Іон                  | T <sub>A</sub> = +25°C                                                                                           | -1                        |     | +1                        | μA     |

| PCM AUDIO INTERFACE                                   | TIMING               |                                                                                                                  | •                         |     |                           |        |

| BCLK Frequency Range                                  | f                    | I <sup>2</sup> S/left-justified modes                                                                            | 0.256                     |     | 12.288                    | MHz    |

| BOLK Frequency Range                                  | fBCLK                | TDM mode                                                                                                         | 0.256                     |     | 24.576                    | IVITIZ |

| BCLK Duty Cycle                                       | DC                   |                                                                                                                  | 45                        |     | 55                        | %      |

| BCLK Period                                           | 4                    | I <sup>2</sup> S/left-justified only                                                                             | 81.3                      |     |                           | ns     |

| BOLK Pellou                                           | t <sub>BCLK</sub>    | TDM mode                                                                                                         | 40                        |     |                           |        |

| Maximum BCLK Input<br>Low-Frequency Jitter            |                      | Maximum allowable jitter before a -20dBFS, 20kHz input has a 1dB reduction in THD+N, RMS jitter ≤ 40kHz          |                           | 0.2 |                           | ns     |

| Maximum BCLK Input<br>High-Frequency Jitter           |                      | Maximum allowable jitter before a<br>-60dBFS, 20kHz input has a 1dB<br>reduction in THD+N,<br>RMS jitter > 40kHz |                           | 1   |                           | ns     |

| PCM AUDIO INTERFACE                                   | TIMING / INTE        | RFACE TIMING                                                                                                     |                           |     |                           |        |

| LRCLK to BCLK Active<br>Edge Setup Time               | t <sub>SYNCSET</sub> |                                                                                                                  | 4                         |     |                           | ns     |

| LRCLK to BCLK Active<br>Edge Hold Time                | tsynchold            |                                                                                                                  | 4                         |     |                           | ns     |

| DIN to BCLK Active<br>Edge Setup Time                 | <sup>t</sup> SETUP   |                                                                                                                  | 4                         |     |                           | ns     |

| DIN to BCLK Active<br>Edge Hold Time                  | tHOLD                |                                                                                                                  | 4                         |     |                           | ns     |

| DIN Frame Delay After LRCLK Edge                      |                      | Measured in number of BCLK cycles, set by selected TDM mode                                                      | 0                         |     | 2                         | cycles |

| I <sup>2</sup> C INTERFACE TIMING                     |                      |                                                                                                                  |                           |     |                           |        |

| Serial Clock Frequency                                | f <sub>SCL</sub>     |                                                                                                                  |                           |     | 1000                      | kHz    |

| Bus Free Time Between<br>STOP and START<br>Conditions | t <sub>BUF</sub>     |                                                                                                                  | 0.5                       |     |                           | μs     |

$(V_{BAT} = 3.7V, \ V_{VDD} = 1.8V, \ V_{GND} = 0V, \ V_{PGND} = 0V, \ C_{VBAT} = 1 \ x \ 10 \mu F, \ 1 \ x \ 0.1 \mu F, \ C_{VDD} = 1 \mu F, \ C_{PVDD} = 2 \ x \ 10 \mu F, \ 1 \ x \ 0.1 \mu F, \ C_{CPBYP} = 2 \ x \ 2.2 \mu F, \ 1 \ x \ 0.1 \mu F, \ C_{CP1} = 2 \ x \ 2.2 \mu F, \ C_{CP2} = 2 \ x \ 2.2 \mu F, \ f_{BCLK} = 3.072 MHz, \ f_{LRCLK} = 48 kHz, \ Z_{SPK} = \infty \ between \ OUTP \ and \ OUTN, \ AC \ Measurement \ Bandwidth = 20 Hz \ to \ 20 kHz, \ T_A = T_{MIN} \ to \ T_{MAX}, \ typical \ values \ are \ at \ T_A = +25 ^{\circ}C) \ (Note \ 1)$

| PARAMETER                                       | SYMBOL                  | CONDITIONS                                                                          | MIN                               | TYP | MAX | UNITS |

|-------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------|-----------------------------------|-----|-----|-------|

| Hold Time (Repeated)<br>START Condition         | t <sub>HD,STA</sub>     |                                                                                     | 0.26                              |     |     | μs    |

| SCL Pulse-Width Low                             | t <sub>LOW</sub>        |                                                                                     | 0.5                               |     |     | μs    |

| SCL Pulse-Width High                            | tHIGH                   |                                                                                     | 0.26                              |     |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition | <sup>t</sup> SU,STA     |                                                                                     | 0.26                              |     |     | μs    |

| Data Hold Time                                  | t <sub>HD,DAT</sub>     |                                                                                     | 0                                 |     | 450 | ns    |

| Data Setup Time                                 | tsu,dat                 |                                                                                     | 50                                |     |     | ns    |

| SDA and SCL Receiving Rise Time                 | t <sub>R</sub>          |                                                                                     | 20                                |     | 120 | ns    |

| SDA and SCL Receiving Fall Time                 | t <sub>F</sub>          |                                                                                     | 20 x<br>V <sub>DD</sub> /5.5<br>V |     | 120 | ns    |

| SDA Transmitting Fall<br>Time                   | t <sub>F</sub>          |                                                                                     | 20 x<br>V <sub>DD</sub> /5.5<br>V |     | 120 | ns    |

| Setup Time for STOP<br>Condition                | tsu,sto                 |                                                                                     | 0.26                              |     |     | μs    |

| Bus Capacitance                                 | C <sub>B</sub>          |                                                                                     |                                   |     | 550 | pF    |

| Pulse Width of<br>Suppressed Spike              | t <sub>SP</sub>         |                                                                                     | 0                                 |     | 50  | ns    |

| THERMAL PROTECTION                              | ı                       |                                                                                     | •                                 |     |     |       |

| Thermal Shutdown<br>Trigger Point               |                         | THERMSHDN_THRESH = 0x64                                                             | 140                               | 150 | 160 | °C    |

| RESET TIMING                                    |                         |                                                                                     | •                                 |     |     | •     |

| RESET Low                                       | treset_low              | Minimum low time for RESET to ensure device enters hardware shutdown                |                                   | 7.5 |     | μs    |

| Release from RESET                              | t <sub>I</sub> 2C_READY | Time from RESET = 1 to I <sup>2</sup> C communication available (software shutdown) |                                   |     | 1.5 | ms    |

- Note 1: Limits are 100% tested at  $T_A = +25$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

- Note 2: See the <u>Digital Audio Interface Configuration</u> and <u>Valid Clock Frequencies</u> sections for more information.

- **Note 3:** Minimum and/or maximum limit is guaranteed by design and by statistical analysis of device characterization data. The specification is not guaranteed by production testing.

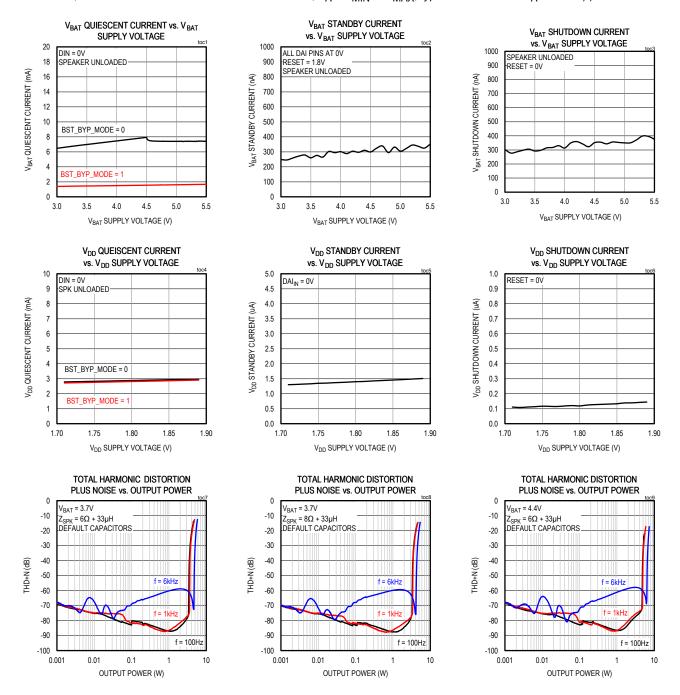

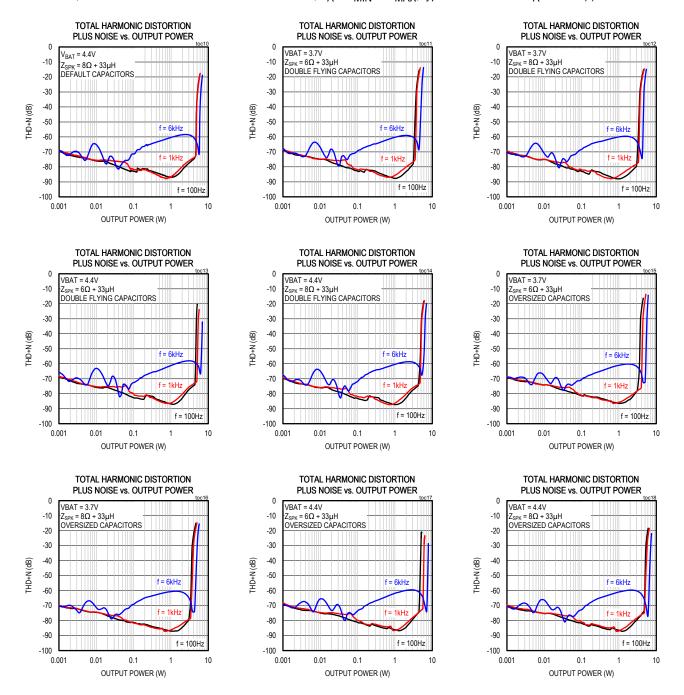

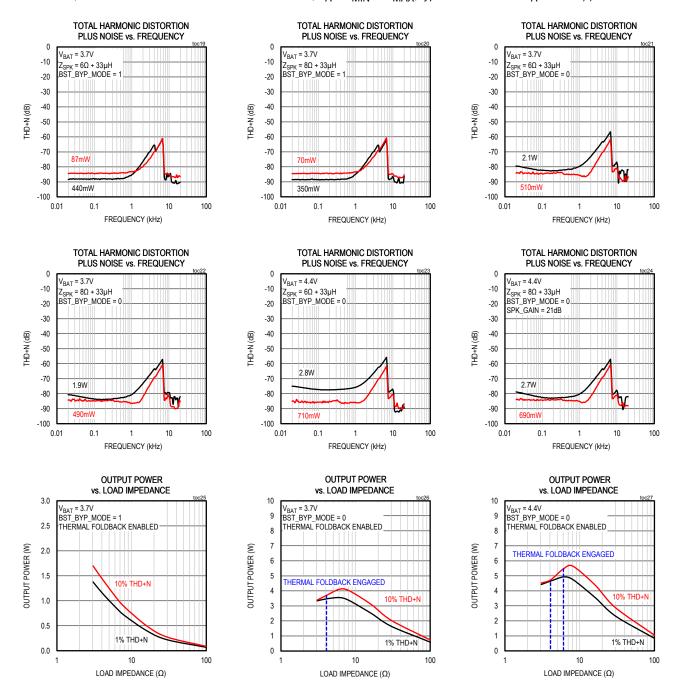

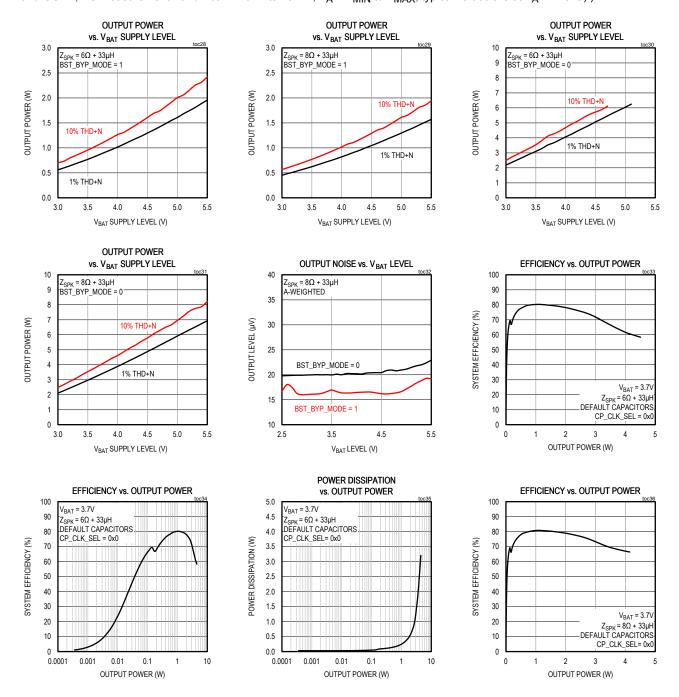

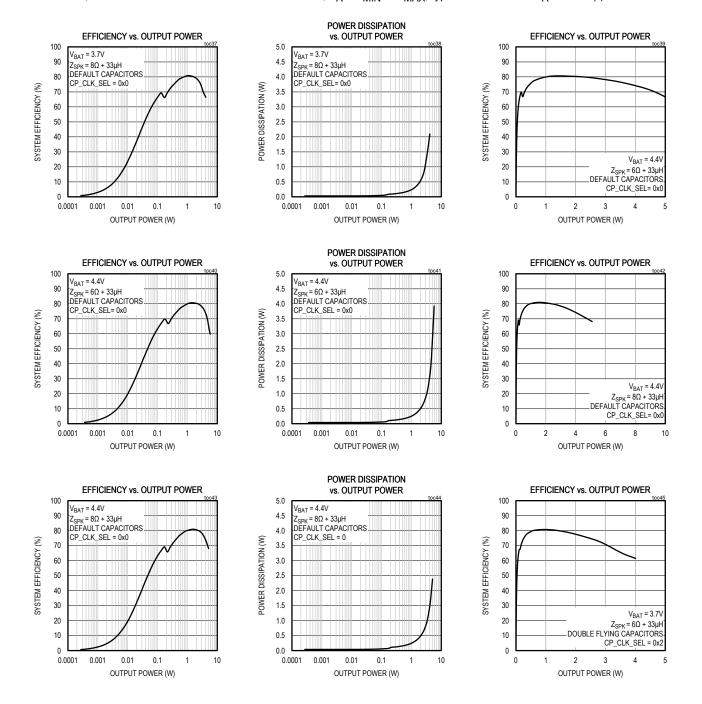

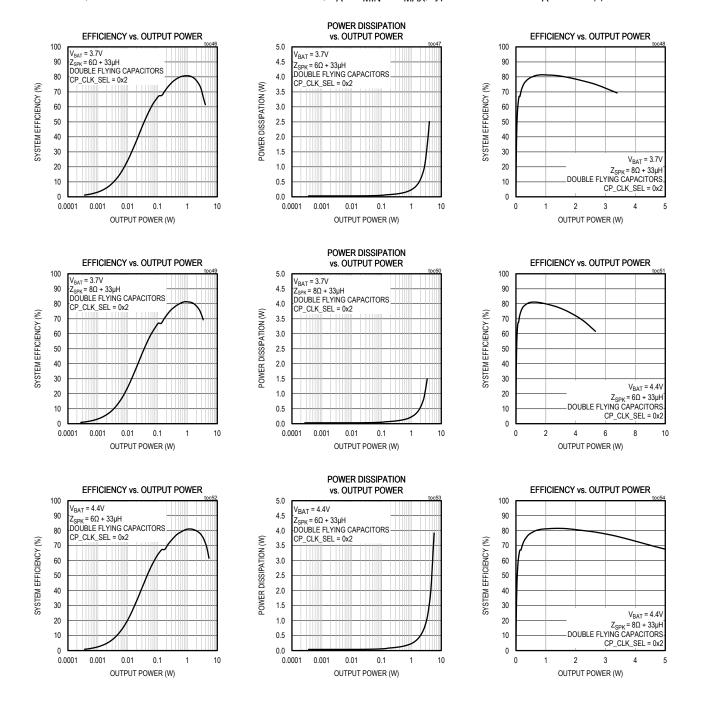

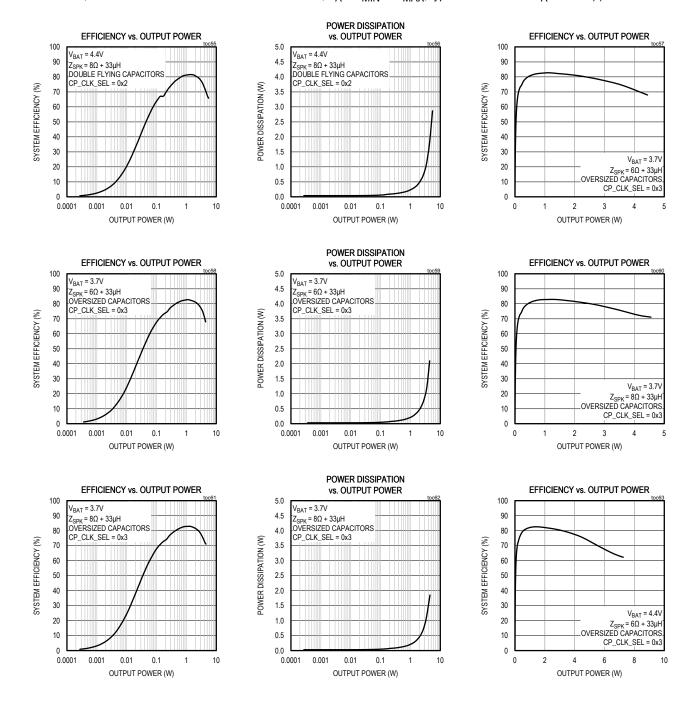

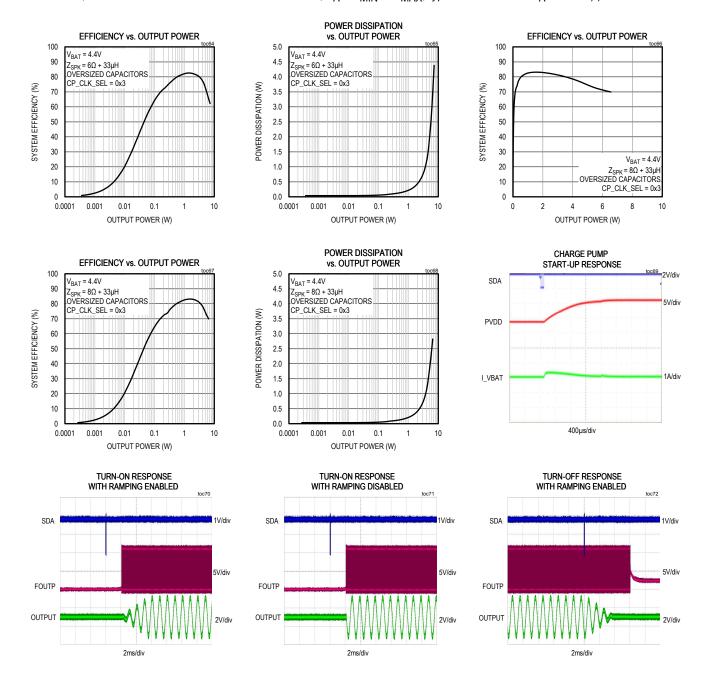

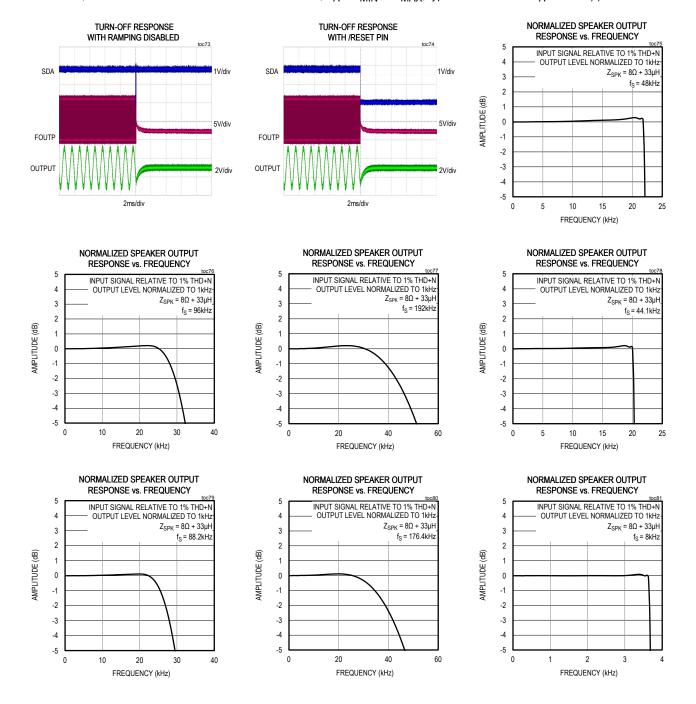

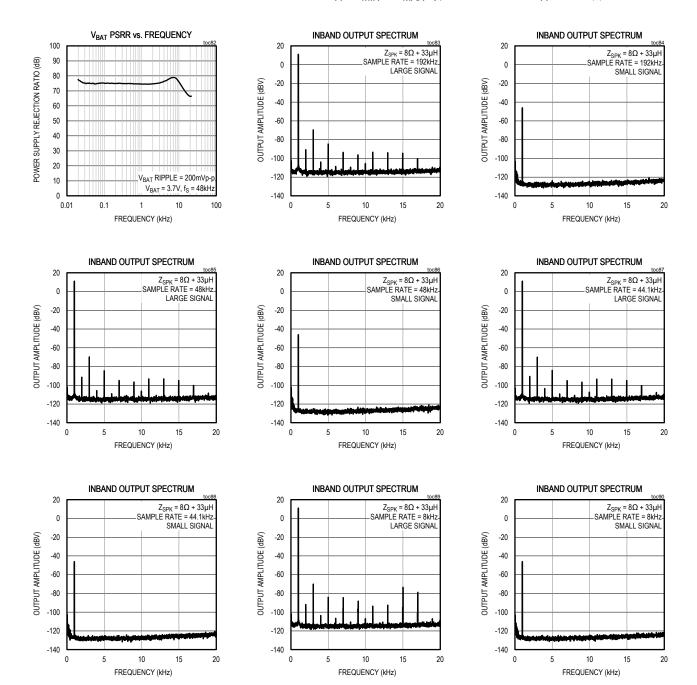

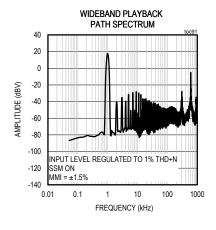

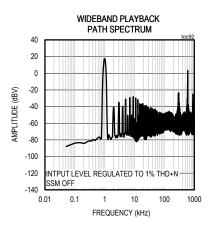

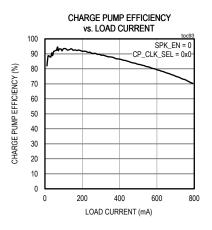

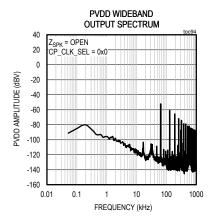

## **Typical Operating Characteristics**

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \times 10 \mu \text{F}, 1 \times 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \times 10 \mu \text{F}, 1 \times 0.1 \mu \text{F}, C_{CPBYP} = 2 \times 2.2 \mu \text{F}, 1 \times 0.1 \mu \text{F}, C_{CP1} = 2 \times 2.2 \mu \text{F}, C_{CP2} = 2 \times 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP}$  and OUTN, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , typical values are at  $T_A = +25^{\circ}\text{C}$ )

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$

$(V_{BAT} = 3.7 \text{V}, V_{VDD} = 1.8 \text{V}, V_{GND} = 0 \text{V}, V_{PGND} = 0 \text{V}, C_{VBAT} = 1 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{VDD} = 1 \mu \text{F}, C_{PVDD} = 2 \text{ x } 10 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CPBYP} = 2 \text{ x } 2.2 \mu \text{F}, 1 \text{ x } 0.1 \mu \text{F}, C_{CP1} = 2 \text{ x } 2.2 \mu \text{F}, C_{CP2} = 2 \text{ x } 2.2 \mu \text{F}, f_{BCLK} = 3.072 \text{MHz}, f_{LRCLK} = 48 \text{kHz}, Z_{SPK} = \infty \text{ between OUTP and OUTN, AC Measurement Bandwidth} = 20 \text{Hz} \text{ to } 20 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ typical values are at } T_A = +25 ^{\circ}\text{C})$