### **General Description**

The MAX11080 is a battery-pack fault-monitor IC capable of monitoring up to 12 lithium-ion (Li+) battery cells. This device is designed to provide an overvoltage or undervoltage fault indication when any of the cells cross the user-selectable threshold for longer than the set program-delay interval. The overvoltage levels are pin selectable from +3.3V to +4.8V in 100mV increments, and have a guaranteed accuracy of  $\pm 25$ mV over the entire temperature range. The undervoltage level is also user selectable from +1.6V to +2.8V in 200mV increments. These levels are guaranteed to  $\pm 100$ mV over the entire temperature range. Undervoltage detection can be disabled as one of the user-configuration options.

The MAX11080 has a built-in level-shifter that allows up to 31 MAX11080 devices to be connected in a daisychain fashion to reduce the number of interface signals needed for large stacks of series batteries. Each cell is monitored differentially and compared to the overvoltage and undervoltage thresholds. When any of the cells exceed this threshold for longer than the set program delay interval, the MAX11080 inhibits the heartbeat signal from being passed down the daisy chain. Built-in comparator hysteresis prevents threshold chattering.

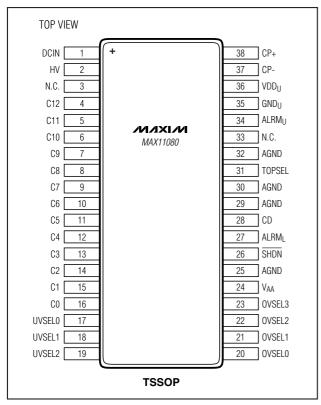

The MAX11080 is designed to be the perfect complement to the MAX11068 high-voltage measurement IC for redundant fault-monitoring applications. This device is offered in a 9.7mm x 4.4mm, 38-pin TSSOP package with 0.5mm pin spacing. The package is lead-free and RoHS compliant with an extended operating temperature range of -40°C to +105°C.

### Applications

- High-Voltage, Multicell-Series-Stacked Battery Systems

- Electric Vehicles

- Hybrid Electric Vehicles

- Electric Bikes

- High-Power Battery Backup

- Solar Cell Battery Backup

- Super-Cap Battery Backup

### \_Features

- Up to 12-Cell Li+ Battery Voltage Fault Detection

- ♦ Operation from 6.0V to 72V

- Pin-Selectable Overvoltage Threshold from +3.3V to +4.8V in 100mV Increments ±25mV Overvoltage-Detection Accuracy

- Pin-Selectable Undervoltage Threshold from +1.6V to +2.8V in 200mV Increments ±100mV Undervoltage-Detection Accuracy

- 300mV Over/Undervoltage-Threshold Detection Hysteresis

- Programmable Delay Time of Alarm Detection from 3.0ms to 3.32s with an External Capacitor

- Daisy-Chained Alarm and Shutdown Functions with Heartbeat Status Signal Up to 31 Devices Can Be Connected

- Ultra-Low-Power Dissipation

Operating-Mode Current Drain: 80µA

Shutdown-Mode Current: 2µA

- Wide Operating Temperature Range from -40°C to +105°C (AEC-Q100 Type 2)

- 9.7mm x 4.4mm, 38-Pin TSSOP Package

- Lead(Pb) Free and RoHS Compliant

### **Ordering Information**

| PART                                             | TEMP RANGE      | PIN-PACKAGE |  |  |  |

|--------------------------------------------------|-----------------|-------------|--|--|--|

| MAX11080GUU+                                     | -40°C to +105°C | 38 TSSOP    |  |  |  |

| MAX11080GUU/V+                                   | -40°C to +105°C | 38 TSSOP    |  |  |  |

| + Denotes a lead(Pb)-free/RoHS-compliant package |                 |             |  |  |  |

+Denotes a lead(PD)-tree/RoHS-compliant package /V denotes an automotive qualified part.

### Pin Configuration appears at end of data sheet.

### /M/IXI/M

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### ABSOLUTE MAXIMUM RATINGS

| HV, VDD <sub>U</sub> , GND <sub>U</sub> , DCIN to AGND0.3V to +80V         HV to DCIN and C12      0.3V to +6V         C2-C12 to AGND      0.3V to (V <sub>DCIN</sub> + 0.6V)         Cn+1 to Cn, where n = 2 to 12      0.3V to +20V (Note 1)         C1 to CO      0.3V to +20V (Note 2)         C0 to AGND      0.3V to (V <sub>DCIN</sub> + 0.6V) (Note 2)         C0 to AGND      0.3V to +0.9V         SHDN, V <sub>AA</sub> to AGND      0.3V to +40V         VDD <sub>U</sub> to GND <sub>U</sub> 0.3V to +40V         OVSEL_, UVSEL_, TOPSEL to AGND      0.3V to (+V <sub>AA</sub> + 0.3V)         ALRM <sub>L</sub> to AGND      0.3V to (+VAA + 0.3V)         CP+ to AGND      0.3V to (VDD <sub>U</sub> + 0.3V)         CP- to AGND      0.3V to (GND <sub>U</sub> + 0.3V) |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CP- to AGND(GND <sub>U</sub> - 0.3V) to (VDD <sub>U</sub> + 0.3V)<br>CP- to AGND0.3V to (GND <sub>U</sub> + 0.3V)<br>CP- to VDD <sub>U</sub> +0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

Note 1: The C1 to C0 differential input path is tolerant to 80V as long as the SHDN pin is deasserted. Note 2: The C1 input is tolerant to a maximum V<sub>DCIN</sub> + 0.6V. If SHDN is asserted, 20V is the maximum rating. Note 3: Human Body Model to Specification MIL-STD-883 Method 3015.7.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } V_{DCIN} = V_{GND_u} = +6.0V \text{ to } +72V, \text{ typical values are at } T_A = +25^{\circ}C, \text{ unless otherwise specified from } -40^{\circ}C \text{ to } +105^{\circ}C.)$

| PARAMETER                            | SYMBOL            | CONDITIONS                                                     | MIN  | ТҮР  | MAX  | UNITS |

|--------------------------------------|-------------------|----------------------------------------------------------------|------|------|------|-------|

| C_INPUTS                             |                   |                                                                |      |      |      |       |

| Common-Mode Input Range              | VC <sub>XIN</sub> | Any two inputs Cn to Cn+1 for full threshold accuracy (Note 4) | 1.5  |      | 72   | V     |

| Input Current                        | IC <sub>XIN</sub> | $V_{CELL} = 3.0V$                                              | -1   | 0.05 | +1   | μA    |

| Overvoltage Threshold                | Vov               |                                                                | +3.3 |      | +4.8 | V     |

| Overvoltage-Threshold Accuracy       |                   |                                                                |      | ±5   | ±25  | mV    |

| Undervoltage Threshold               | VUV               |                                                                | +1.6 |      | +2.8 | V     |

| Undervoltage-Threshold<br>Accuracy   |                   |                                                                |      | ±20  | ±100 | mV    |

| Comparator Hysteresis                | V <sub>HYS</sub>  |                                                                |      | 300  |      | mV    |

| CD PIN                               |                   |                                                                |      |      |      |       |

| CD Current                           | ICD               | $V_{CD} = 0.4 V$                                               | 4.35 | 6.1  | 7.65 | μA    |

| CD Trip Voltage                      | V <sub>CD</sub>   | Internal at comparator                                         |      | 1.23 |      | V     |

| Delay-Time Accuracy                  |                   | Excluding C <sub>DLY</sub> variation                           |      | ±20  |      | %     |

| STATUS/CONTROL PORT                  |                   |                                                                |      |      |      |       |

| Shutdown Disable (SHDN High Voltage) | SHDN/VIH          |                                                                | 2.1  |      |      | V     |

| Shutdown Asserted (SHDN Low Voltage) | SHDN/VIL          |                                                                |      |      | 0.6  | V     |

M/IXI/M

### ELECTRICAL CHARACTERISTICS (continued)

(T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.  $V_{DCIN} = V_{GND_u} = +6.0V$  to +72V, typical values are at T<sub>A</sub> = +25°C, unless otherwise specified from -40°C to +105°C.)

| PARAMETER                                     | SYMBOL                               | CONDITIONS                                                                                                                   | MIN                       | TYP  | MAX                       | UNITS |  |

|-----------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|---------------------------|-------|--|

| VDDU Output High                              | VDD <sub>U</sub><br>V <sub>OH</sub>  | Output voltage of VDDU after the $20k\Omega/200k\Omega$ resistor-divider to SHDN                                             | GND∪<br>+ 2.4             |      |                           | V     |  |

| VDDU Output Low                               | VDD <sub>U</sub><br>V <sub>OL</sub>  | Output voltage of VDDU after the $20k\Omega/200k\Omega$ resistor-divider for SHDN                                            |                           |      | GND <sub>U</sub><br>+ 0.3 | V     |  |

| ALRM <sub>L</sub> Output-Voltage High         | ALRM <sub>L</sub><br>V <sub>OH</sub> | ISOURCE = 150µA                                                                                                              | 2.4                       |      |                           | V     |  |

| ALRM <sub>L</sub> Output-Voltage Low          | ALRM <sub>L</sub><br>V <sub>OL</sub> | I <sub>SINK</sub> = 150μΑ                                                                                                    |                           |      | 0.6                       | V     |  |

| ALRMU Input-Voltage High                      | ALRMU<br>VIH                         | Daisy-chained ALRMU signal as coupled through a 3.3nF high-voltage capacitor and a $150k\Omega$ resistor as referred to GNDU | GND <sub>U</sub><br>+ 2.1 |      |                           | V     |  |

| ALRMU Input-Voltage Low                       | ALRMU<br>VIL                         | Daisy-chained ALRMU signal as coupled through a 3.3nF high-voltage capacitor and a $150k\Omega$ resistor as referred to GNDU |                           |      | GNDU<br>+ 0.9             | V     |  |

| Alarm Voltage Output "Heartbeat"<br>Frequency | ALRM <sub>L</sub><br>fout            | Heartbeat clock rate with no alarm condition                                                                                 | 4032                      | 4096 | 4157                      | Hz    |  |

| Alarm Voltage Output Duty Cycle               |                                      | Heartbeat clock rate with no alarm condition                                                                                 | 49.0                      |      | 51.0                      | %     |  |

| LINEAR REGULATOR (VAA)                        | •                                    |                                                                                                                              |                           |      |                           |       |  |

| Input Voltage Range                           | VDCIN                                |                                                                                                                              | 6                         |      | 72                        | V     |  |

| Output Voltage                                | Vaaout                               | $6V < V_{DCIN} < 72V, I_{LOAD} = 0$                                                                                          | 3.0                       | 3.3  | 3.6                       | V     |  |

| Short-Circuit Current                         | <b>I</b> AASHORTCIRCUIT              | $V_{AA} = 0,  6V < V_{DCIN} < 36V$                                                                                           |                           |      | 50                        | mA    |  |

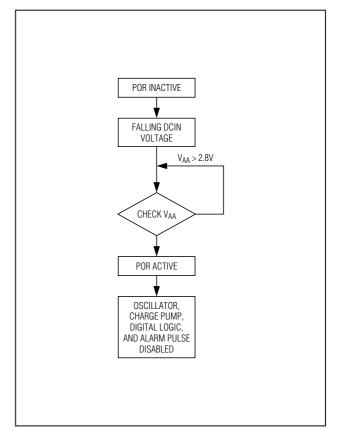

|                                               | VAARESET                             | Falling V <sub>AA</sub>                                                                                                      |                           | 2.8  |                           | V     |  |

| Power-On-Reset Trip Level<br>(Note 4)         | Vaavalid                             | Rising V <sub>AA</sub>                                                                                                       |                           | 3.0  |                           | v     |  |

|                                               | VAAHYS                               | Hysteresis on rising VAA                                                                                                     |                           | 37   |                           | mV    |  |

| Thermal Shutdown                              | TSHUT                                | Rising temperature                                                                                                           |                           | +145 |                           | °C    |  |

| POWER-SUPPLY REQUIREMEN                       | rs (dcin)                            |                                                                                                                              |                           |      |                           |       |  |

| Current Consumption                           | IDCIN                                | Operating mode, <del>SHDN</del> = 1, 12<br>battery cells, alarm inactive,<br>V <sub>DCIN</sub> = V <sub>GNDU</sub> = 36V     |                           | 35   | 40                        | μA    |  |

|                                               |                                      | Shutdown mode, $\overline{SHDN} = 0$ , 12<br>battery cells, $V_{DCIN} = V_{GND_U} = 36V$                                     |                           | 1.3  | 2                         |       |  |

| I <sub>GNDu</sub> Operating Mode              |                                      | $\overline{\text{SHDN}}$ = 1, battery cells, alarm inactive, V <sub>DCIN</sub> = V <sub>GNDU</sub> = 36V                     |                           | 35   | 40                        | μA    |  |

| LOGIC INPUTS AND OUTPUTS                      |                                      |                                                                                                                              |                           |      |                           |       |  |

| Threshold Setting                             | VIH                                  | UVSEL0/UVSEL1/UVSEL2, TOPSEL                                                                                                 | VAA -<br>0.1              |      |                           | V     |  |

| The shou betting                              |                                      |                                                                                                                              |                           |      |                           |       |  |

Note 4: Guaranteed by design and not production tested.

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

MAX11080

**UNDERVOLTAGE SET THRESHOLD CD CHARGING CURRENT CD CURRENT DISTRIBUTION** vs. TEMPERATURE vs. TEMPERATURE 1 64 6.03 35 1.6V SET POINT  $V_{CD} = 0.4V$ 1.63 UNDERVOLTAGE SET THRESHOLD (V) 6.02 30 1.62 MAX 25 6.01 CD CURRENT (µA) 1.61 DEVICE COUNT 20 6.00 1.60 . MEAN 1.59 15 5.99 1.58 5.98 10 1.57 MIN 5 5.97 1.56 1.55 0 5.96 -40 -20 0 20 40 60 80 100 5.6 6.6 -40 -20 0 20 40 60 80 100 5.4 5.8 6.0 6.2 6.4 TEMPERATURE (°C) CD PIN CURRENT (µA) TEMPERATURE (°C) **GND<sub>II</sub> SUPPLY CURRENT OVERVOLTAGE CLEAR THRESHOLD** DCIN SUPPLY CURRENT vs. Vncin vs. GND<sub>U</sub> VOLTAGE vs. TEMPERATURE 55 4.54 4.8V OVERVOLTAGE THRESHOLD 4.8V SET POINT 70 MAX 50 DVERVOLTAGE CLEAR THRESHOLD (V) V<sub>CELL</sub> = V<sub>DCIN</sub>/12 4.53  $T_{A} = +105$ 45 60 4.52 MEAN 40 lpcin (µA) (AM) (MA) 4.51 50 +25°( TΔ 35  $T_A = -40^{\circ}C$ 4.50 40 +105°C 30 4.49 25 MIN 30 4.48 -40°C 20 T<sub>A</sub> : +25°C Δ 20 15 4.47 0 10 20 30 40 50 60 70 80 10 20 30 40 50 60 70 80 -20 0 20 60 100 0 -40 40 80 V<sub>DCIN</sub> (V) VGNDU (V) TEMPERATURE (°C) **OVERVOLTAGE SET THRESHOLD UNDERVOLTAGE CLEAR THRESHOLD** vs. TEMPERATURE vs. TEMPERATURE 4.806 1.94 4.8V SET POINT 1.6V SET POINT UNDERVOLTAGE CLEAR THRESHOLD (V) 4.804 OVERVOLTAGE SET THRESHOLD (V) 1.92 MAX MAX 4.802 1.90 . MEAN 4.800 1.88 MEAN 4.798 MIN 1.86 4.796 MIN 1.84 4.794 4.792 1.82 -40 -20 -40 100 0 20 40 60 80 100 -20 0 20 40 60 80 TEMPERATURE (°C) TEMPERATURE (°C)

**Typical Operating Characteristics**

M/IXI/M

### \_Pin Description

| PIN               | NAME          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

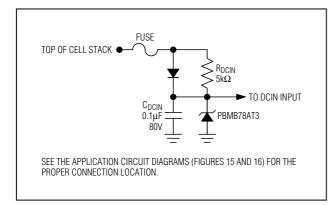

| 1                 | DCIN          | DC Power-Supply Input. DCIN supplies the internal 3.3V regulator. This pin should be connected as shown in the application diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2                 | HV            | High-Voltage Bias. HV is biased by the output of the charge pump to provide a DC supply above the DCIN level. It is used internally to bias the cell-comparator circuitry. Bypass to DCIN with a 1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                 |

| 3, 33             | N.C.          | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4                 | C12           | Cell 12 Plus Connection. Top of battery module stack.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5                 | C11           | Cell 12 Minus Connection and Cell 11 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6                 | C10           | Cell 11 Minus Connection and Cell 10 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7                 | C9            | Cell 10 Minus Connection and Cell 9 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8                 | C8            | Cell 9 Minus Connection and Cell 8 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9                 | C7            | Cell 8 Minus Connection and Cell 7 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10                | C6            | Cell 7 Minus Connection and Cell 6 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11                | C5            | Cell 6 Minus Connection and Cell 5 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12                | C4            | Cell 5 Minus Connection and Cell 4 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13                | C3            | Cell 4 Minus Connection and Cell 3 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14                | C2            | Cell 3 Minus Connection and Cell 2 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15                | C1            | Cell 2 Minus Connection and Cell 1 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16                | CO            | Cell 1 Minus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17                | <b>UVSEL0</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18                | UVSEL1        | Undervoltage Threshold Select 2 to 0. Used to select one of eight undervoltage alarm threshold settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 19                | UVSEL2        | The parts have internal pulldown; these pins should only be tied to VAA or AGND to set the logic state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20                | <b>OVSEL0</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21                | OVSEL1        | Overvoltage Threshold Select 3 to 0. Used to select one of 16 overvoltage alarm threshold settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22                | OVSEL2        | The parts have internal pulldown; these pins should only be tied to VAA or AGND to set the logic state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23                | OVSEL3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24                | VAA           | +3.3V Analog Supply Output. Bypass with a 1µF capacitor to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25, 29,<br>30, 32 | AGND          | Analog Ground. Should be connected to the negative terminal of cell 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 26                | SHDN          | Active-Low Shutdown Input. This pin completely shuts down the MAX11080 internal regulator and oscillators when the pin is less than 0.6V as referenced to AGND. The host controller should drive $\overline{SHDN}$ for the first pack. $\overline{SHDN}$ for daisy-chained modules should be connected to the lower neighboring module's VDDU through a 20k $\Omega$ series resistor.                                                                                                                                                                                           |

| 27                | ALRML         | Lower Port Alarm Output. This output is an alarm indicator for overvoltage, undervoltage, and setup faults. The alarm signal is daisy chained and driven from the highest module down to the lowest. The alarm output is nominally a clocked "heartbeat" signal that provides a 4kHz clock when no alarm is present. The ALRML can also be configured as level signal and set to "low" for no alarm and "high" for alarm state. See the <i>TOPSEL Function</i> section for details. This signal swings between V <sub>AA</sub> and AGND, and is active high in the alarm state. |

| 28                | CD            | Programmable Delay Time. Connect a capacitor from this pin to AGND to set the hold time required for a fault condition before the alarm is set. The capacitor should be a ceramic capacitor in the 15nF to $16.5\mu$ F range.                                                                                                                                                                                                                                                                                                                                                   |

### **Pin Description (continued)**

| PIN    | NAME     | FUNCTION                                                                                                                                                                                                                                                                            |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31     | TOPSEL   | Input to Indicate Topmost Device in the Daisy Chain. This pin should be connected to AGND for all devices except the topmost. For the top device, this pin should be connected to V <sub>AA</sub> .                                                                                 |

| 34     | ALRMU    | Upper Port Alarm Input. This input receives the ALRM $_{\rm L}$ output signal from an upper neighboring module. It swings between VDD $_{\rm U}$ and GND $_{\rm U}$ .                                                                                                               |

| 35     | GNDU     | Level-Shifted Upper Port Ground. Upper port-supply return and supply input for the charge pump and HV supplies. This pin should be connected to the DCIN takeoff point on the battery stack as shown in the application diagrams.                                                   |

| 36     | VDDU     | Level-Shifted Upper Port Supply. Upper port-supply output for the daisy-chained bus. This is a regulated output voltage from the internal charge pump that is level-shifted above the DCIN pin voltage level. It should be bypassed with a $1\mu$ F capacitor to GND <sub>U</sub> . |

| 37, 38 | CP-, CP+ | Charge-Pump Capacitor. Negative/positive input for the internal charge pump. Connect a 0.01µF high-<br>voltage capacitor between CP+ and CP                                                                                                                                         |

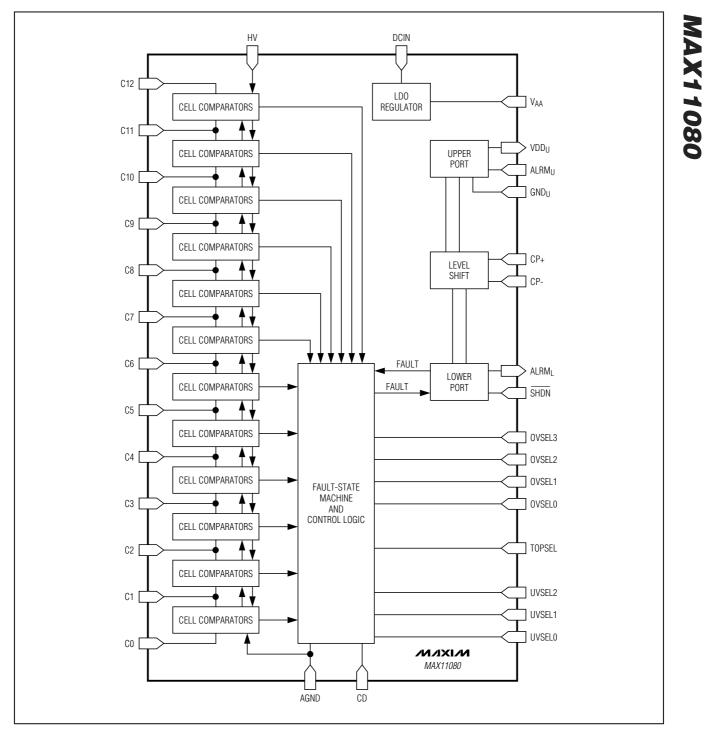

Figure 1. Functional Diagram

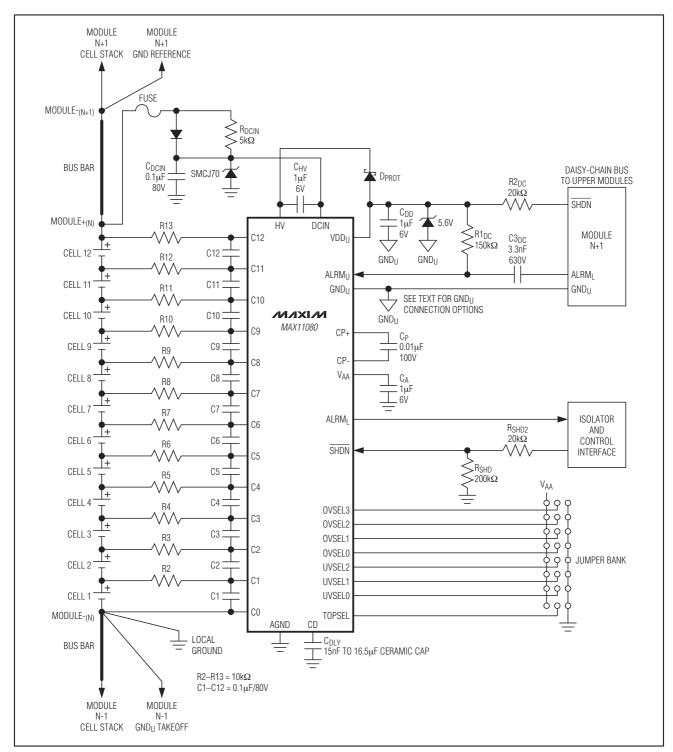

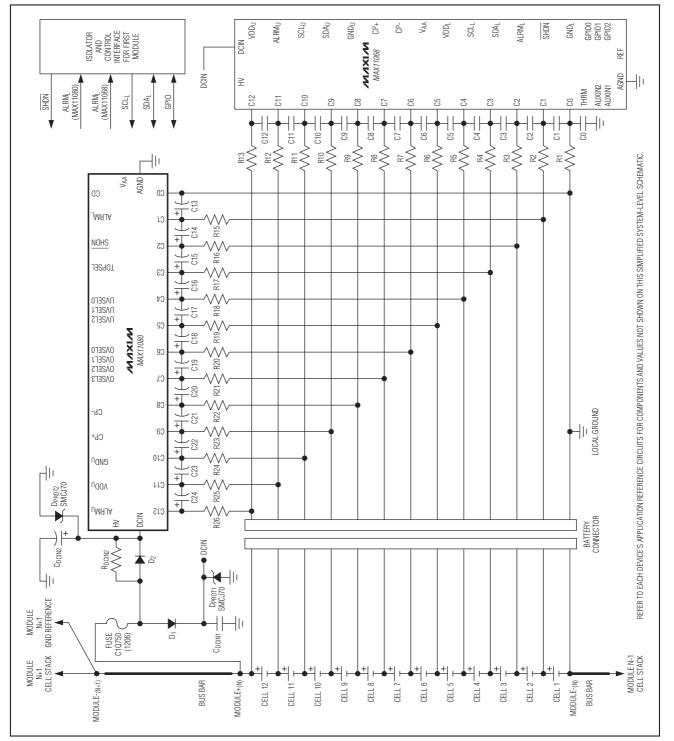

Figure 2. Application Circuit Diagram for a 12-Cell System

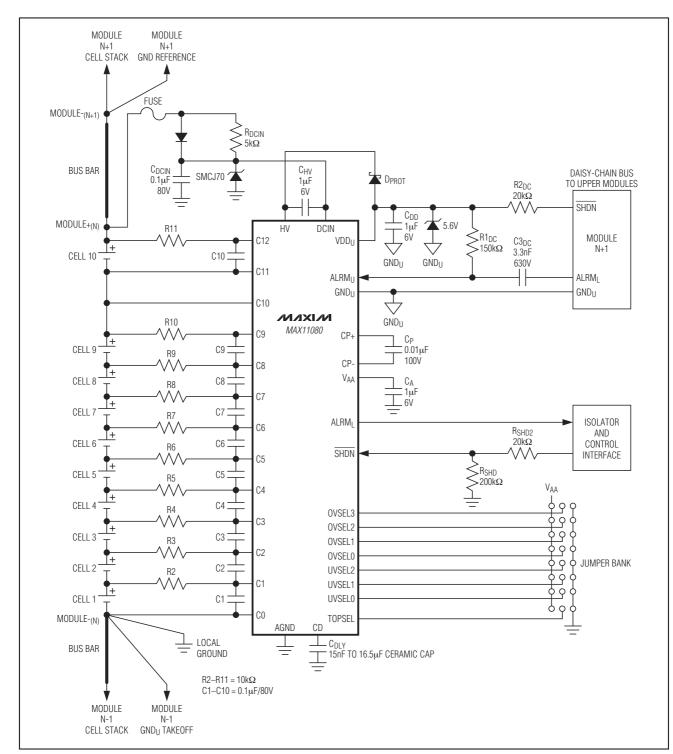

Figure 3. Application Circuit Diagram for a 10-Cell System

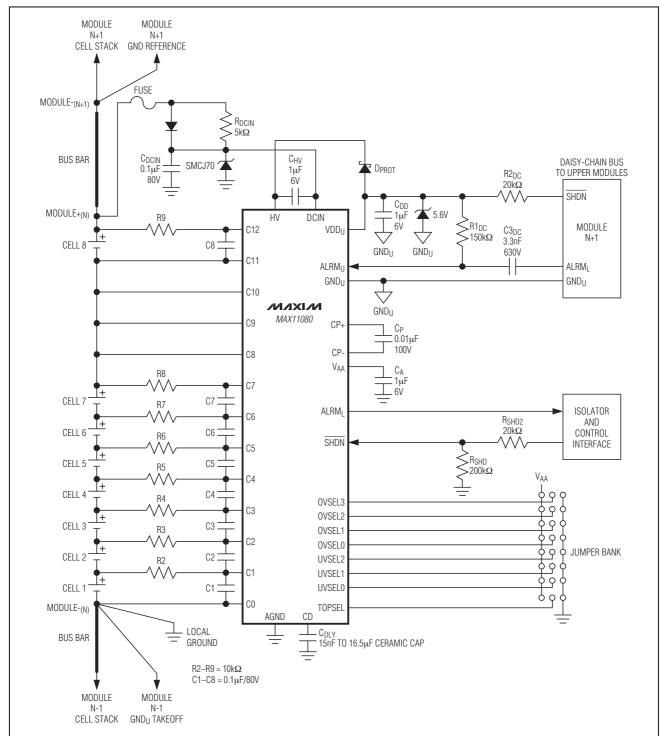

Figure 4. Application Circuit Diagram for an 8-Cell System

10

Figure 5. Battery Module System with Redundant Fault-Detection Application Schematic

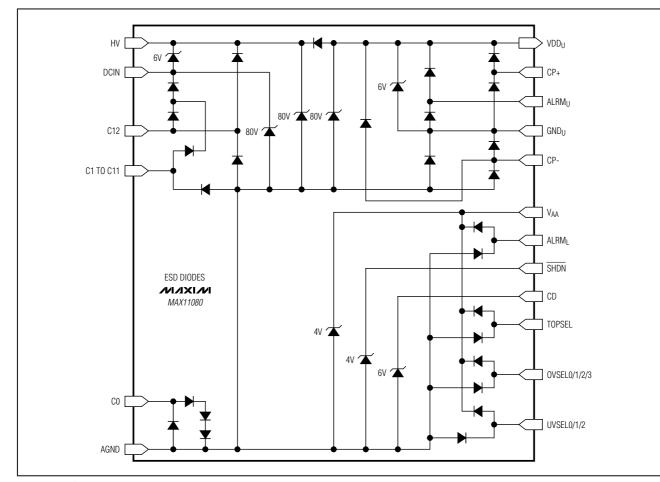

Figure 6. ESD Diode Diagram

### **Detailed Description**

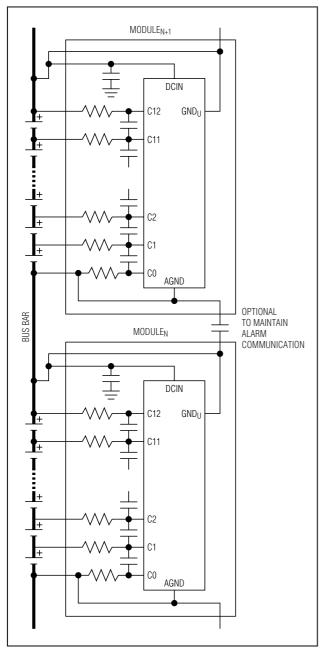

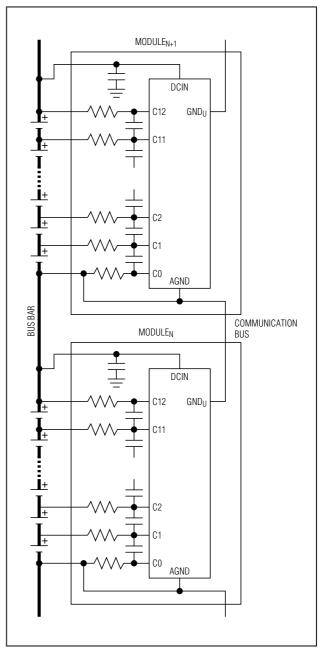

Figure 1 shows the functional diagram; Figure 2 shows the application circuit diagram for a 12-cell system while Figure 3 shows the application circuit design for a 10-cell system and Figure 4 for an 8-cell system. Figure 5 is the application schematic for the battery module system with redundant fault detection.

### **Architectural Overview**

The MAX11080 is a battery-pack fault-monitor IC capable of monitoring up to 12 Li+ battery cells. This device is designed to provide an overvoltage or undervoltage alarm indicator when any of the cells cross the userselectable threshold for longer than the configured decision delay interval. The MAX11080 also incorporates a daisy-chain bus for use in high-voltage stackedbattery operation. The daisy-chain bus relays shutdown and alarm communication across up to 31 stacked modules without the need for isolation between each module. This results in a simplified system with reduced cost. The MAX11080 is ideal as an ultra-low-power, redundant cell fault monitor that is the perfect complement to the MAX11068 high-voltage battery measurement IC. Both ICs in concert form a powerful Li+ battery system monitor with redundant overvoltage and undervoltage fault detection.

### Overvoltage and Undervoltage Fault Detection

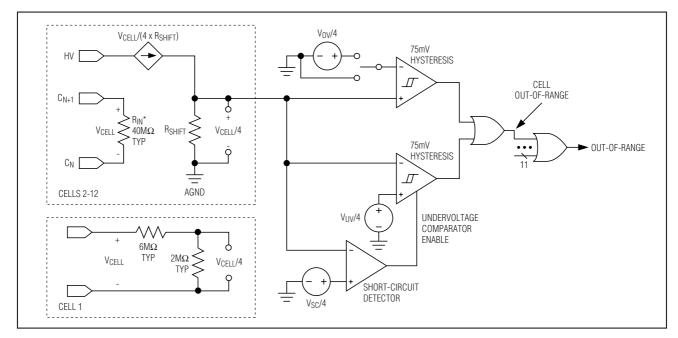

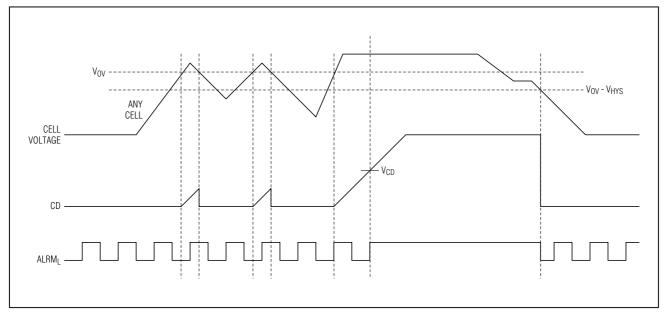

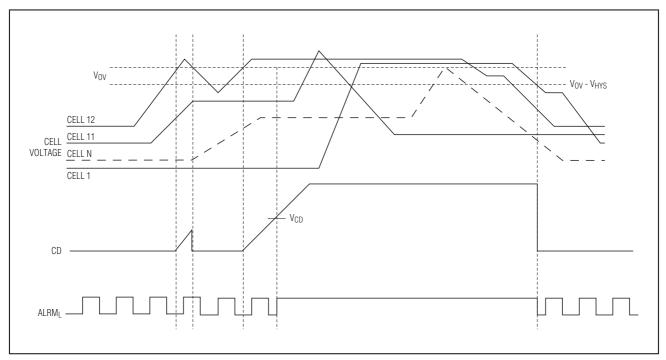

Figure 7 summarizes the fault-detection mechanism for a set of differential cell inputs in the MAX11080.

First, the differential cell inputs are attenuated by a factor of four while being level-shifted and converted to a single-ended voltage referenced to AGND. The ground-

referenced voltage is then connected to a set of overvoltage and undervoltage comparators. The threshold references for the comparators are set by the UVSEL\_ and OVSEL\_ input pins. When one of the cell voltages exceeds V<sub>OV</sub> or is below V<sub>UV</sub> when V<sub>UV</sub> is enabled, the internal cell out-of-range signal for the given cell is set and logically ORed with the same signal for the other cell positions to create an overall out-of-range signal.

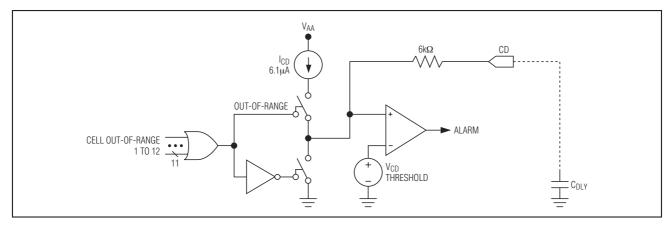

When any cells are out-of-range as indicated by the internal out-of-range signal, an internal current source begins to charge the capacitor  $C_{DLY}$  connected to the

CD pin. If the voltage at the CD pin reaches V<sub>CD</sub>, the ALRM<sub>L</sub> line is set to V<sub>AA</sub> (+2.4V minimum as referred to AGND). Normally, the ALRM<sub>L</sub> line is a heartbeat signal with pulses occurring every 250µs. If all cell voltages transition from out-of-range to in-range before the voltage at pin CD reaches V<sub>CD</sub>, an internal switch clamps the CD pin to GND. This action discharges C<sub>DLY</sub> and, because the delay had not yet expired, no alarm occurs. Discharging C<sub>DLY</sub> ensures that the full delay time occurs for the next overvoltage or undervoltage event. Figure 8 summarizes the C<sub>DLY</sub> circuit.

Figure 7. Cell Differential Input and Comparator Block Diagram

Figure 8. C<sub>DLY</sub> Circuit Block Diagram

Once the ALRM<sub>L</sub> pin is forced high due to an alarm (+2.4V minimum as referred to AGND), it transitions back to a heartbeat signal only after all battery cells meet the following condition:

$(V_{OV} - V_{HYS}) > V_{CELL(ALL)} > (V_{UV} + V_{HYS})$

Examples of cell-voltage readings and their effect on the alarm status are shown in Figures 9 and 10 for single- and multiple-cell systems. In the case where an upper module is forwarding an active alarm condition down the daisy chain, that condition continues to be propagated toward the host regardless of the alarm state of any lower module. Furthermore, to circumvent the possibility of a short-circuited capacitor connected to CD preempting the fault-time validation process, a redundant built-in delay of 4s nominal is asserted as a backup. If the V<sub>CD</sub> threshold is not reached within 4s of an out-of-range event, the alarm becomes active.

### **Programmable Delay Time**

The alarm trigger delay time is calculated according to the following equations:

$t_{DLY} = (V_{CD} \times C_{DLY})/I_{CD}$  $C_{DLY} = (t_{DLY} \times I_{CD})/V_{CD}$  The effective I<sub>CD</sub> value of the current source is  $6.1\mu$ A typical and the threshold voltage, V<sub>CD</sub>, is 1.23V typical. The VCD threshold is specified at an internal node prior to the resistor in series with the CD pin as shown in Figure 8. The threshold voltage seen at the pin is approximately 1.18V due to the drop associated with the typical ICD value and the 6k $\Omega$  resistor. The MAX11080 can operate with capacitor values from 15nF (3.0ms) to 16.5 $\mu$ F (3.32s). Each capacitor should have a voltage tolerance of 5V minimum.

### **Cell-Voltage Threshold Selection**

The overvoltage and undervoltage threshold selection is configured through the OVSEL\_ and UVSEL\_ inputs. The overvoltage selection can be configured from 3.3V to 4.8V in 100mV increments. The undervoltage threshold can be configured from 1.6V to 2.8V in 200mV increments. The undervoltage detection can also be disabled. See Tables 1 and 2 for the proper configuration settings.

Immunity to unintended changes in the threshold voltage setting (due to accidental pin-to-pin short circuits, for example) is provided. The customer-programmed selection is sensed and stored at power-up and any subsequent change to the input pin status is ignored.

| THRESHOLD (V) | OVERVOLTAGE SELECTION |        |        |        |  |

|---------------|-----------------------|--------|--------|--------|--|

|               | OVSEL3                | OVSEL2 | OVSEL1 | OVSEL0 |  |

| 3.3           | 0                     | 0      | 0      | 0      |  |

| 3.4           | 0                     | 0      | 0      | 1      |  |

| 3.5           | 0                     | 0      | 1      | 0      |  |

| 3.6           | 0                     | 0      | 1      | 1      |  |

| 3.7           | 0                     | 1      | 0      | 0      |  |

| 3.8           | 0                     | 1      | 0      | 1      |  |

| 3.9           | 0                     | 1      | 1      | 0      |  |

| 4.0           | 0                     | 1      | 1      | 1      |  |

| 4.1           | 1                     | 0      | 0      | 0      |  |

| 4.2           | 1                     | 0      | 0      | 1      |  |

| 4.3           | 1                     | 0      | 1      | 0      |  |

| 4.4           | 1                     | 0      | 1      | 1      |  |

| 4.5           | 1                     | 1      | 0      | 0      |  |

| 4.6           | 1                     | 1      | 0      | 1      |  |

| 4.7           | 1                     | 1      | 1      | 0      |  |

| 4.8           | 1                     | 1      | 1      | 1      |  |

### Table 1. Overvoltage Threshold Selection

Figure 9. Single-Cell Overvoltage Detection Example

Figure 10. Multiple-Cell Overvoltage Detection Example

|               |        | UNDERVOLTAGE SELECTION |        |

|---------------|--------|------------------------|--------|

| THRESHOLD (V) | UVSEL2 | UVSEL1                 | UVSEL0 |

| Disabled      | 0      | 0                      | 0      |

| 1.6           | 0      | 0                      | 1      |

| 1.8           | 0      | 1                      | 0      |

| 2.0           | 0      | 1                      | 1      |

| 2.2           | 1      | 0                      | 0      |

| 2.4           | 1      | 0                      | 1      |

| 2.6           | 1      | 1                      | 0      |

| 2.8           | 1      | 1                      | 1      |

### Table 2. Undervoltage Threshold Selection

### **Internal Linear Regulator**

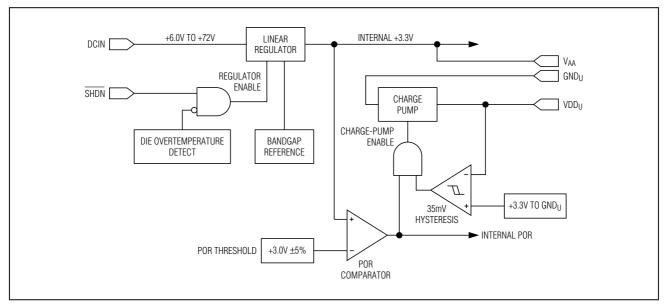

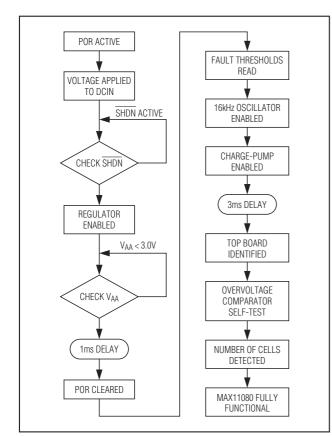

The MAX11080 has an internal linear regulator for generating the internal supply from DCIN (Figure 11). The regulator can accept a supply voltage on the DCIN pin from +6.0V to +72V, which it regulates to 3.3V to run the voltage-detection system, control logic, and lowside alarm-pulse interface. When the SHDN pin is not active and a sufficient voltage is applied to DCIN, the output of the regulator becomes active. The regulator is paired with a power-on-reset (POR) circuit that senses its output voltage and holds the MAX11080 in a reset state until the internal supply has reached a sustainable threshold of  $+3.0V (\pm 5\%)$ . The internal comparators have built-in hysteresis that can reject noise on the supply line. Because secondary metal batteries are never fully discharged to 0V, the MAX11080 is designed for a hot-swap insertion of the battery cells. Once the POR threshold is reached, approximately 1ms later the internal reset signal disables, the internal oscillator starts, and the charge pump begins operating. The charge

Figure 11. Internal Linear Regulator Block Diagram

# MAX11080

# 12-Channel, High-Voltage Battery-Pack Fault Monitor

pump reaches regulation in approximately 3ms. The MAX11080 associated with the top module in the battery pack is identified as detailed in the *TOPSEL Function* section. This is followed by a self-test of the overvoltage comparators and detection of the number of cells connected. At this time in the power-on sequence, the MAX11080 is ready for operation. When the charge pump achieves regulation of 3.3V between VDDU and GNDU, it switches to a standby mode until the voltage drops by about 35mV. The specified accuracy and full operation of the MAX11080 are not guaranteed until a minimum of 6.0V is applied to the DCIN pin.

The linear regulator also incorporates a thermal shutdown feature. If the MAX11080 die temperature rises above +145°C, the device shuts down. After a thermal shutdown, the die temperature must cool 15°C below the shutdown temperature before the device restarts.

Figure 12 shows the linear regulator power-up sequence and Figure 13 shows the low DCIN POR event.

Figure 12. Linear Regulator Power-Up Sequence

Figure 13. Low DCIN POR Event

Figure 14. Battery Module Surge and Overvoltage Protection Circuit

### **DCIN and GNDU Supply Connections**

A surge voltage is produced by the electric motor during regenerative braking conditions. The MAX11080 is designed to tolerate an absolute maximum of 80V under this condition. The MAX11080 should be protected against higher voltages with an external voltage suppressor such as the PBMB78AT3 on the DCIN connection point. This protection circuit also helps to reduce power spikes that can occur during the insertion of the battery cells. During negative voltage excursions, the protection circuit stores enough charge to power the regulator through the transient. Figure 14 shows the clamp configuration to protect the DCIN supply input.

The DCIN input contains a comparator circuit to detect an open circuit on this pin for fault-management purposes. Whenever a nominal voltage of two silicon diode drops appears between C12 and DCIN following the power-up sequence, the ALRML output is asserted as a fault indication. This voltage drop must appear for at least the delay time set by CDLY to result in a fault. The voltage drop from C12 to DCIN during normal operation should be kept at no more than 0.5V to prevent erroneous tripping of the DCIN open-circuit comparator under worst-case circumstances (lowest silicon diode forward bias voltage). The diode DDCIN is used to supply the transient current demanded at startup by the decoupling circuit. In parallel with this diode, RDCIN provides the supply path during normal operation. It is selected to be  $5k\Omega$  so that the maximum voltage drop between C12 and DCIN is about 0.25V with nominal supply currents.

High-power batteries are often used in noisy environments subject to high dV/dt or dI/dt supply noise and EMI noise. For example, the supply noise of a power inverter driving a high horse-power motor produces a large square wave at the battery terminals, even though the battery is also a high-power battery. Typically, the battery dominates the task of absorbing this noise, since it is impractical to put hundreds of farads at the inverter.

The MAX11080 is designed with several mechanisms to deal with extremely noisy environments. First, the major power-supply inputs that see the full battery-stack voltage are 80V tolerant. This is high enough to handle the large voltage changes on the battery stack that can occur when the batteries transition between charge and discharge conditions. Next, the linear regulator has high PSRR to produce a clean low-voltage power supply for the internal circuitry. This allows DCIN to be connected directly to the stack voltage. Finally, GNDU serves two purposes. It supplies the internal charge pump with its power and acts as the reference ground for the upper alarm communication port. The charge pump creates a secondary low-voltage supply that is referenced to GNDU. Because the level-shifted supply VDDU is referenced to GNDU, the entire upper alarm communication port glides smoothly on GNDU and it is effectively immune to noise on GNDU. The upper alarm signal is internally shifted down to AGND level where it is processed by the digital logic. There are two connection methods that can be used for GNDU depending on application requirements.

For the top module in a system, or where GNDU cannot be DC-coupled to the next higher module for other reasons, GNDU should be connected to the same location as DCIN. This connection is valid as long as the voltage difference between the top of Stack(n) and the bottom of Stack(n+1) during worst-case conditions does not exceed the margin of the alarm pin signaling levels. When GNDU is not DC-coupled to the far side of the bus bar, it can be AC-coupled to the far side to maintain alarm communication when the bus bar is open-circuit. In that case, the two sides of the AC-coupling capacitor can be at different DC potentials, but the alarm communication signal continues to be passed across the capacitor connection. It is recommended that an AC- or DC-coupled version of GND() is paired with the alarm signal through the communication bus wiring, possibly by twisted pair wire, for maximum noise immunity and minimum emissions.

The preferred connection to reject noise between modules is when a DC connection can be made from GND<sub>U</sub> to AGND of the next module. It is again recommended that the DC-coupled GND<sub>U</sub> signal is routed adjacent to the alarm signal as part of the communication bus for maximum noise immunity and minimum emissions.

Figure 15. GND<sub>U</sub> Connection: AC-Coupled to Next Module, DC-Coupled to Present Module

Figure 16.  $GND_U$  Connection: DC-Coupled with the Communication Bus

###

### **Shutdown Control**

The SHDN pin connections of the MAX11080 operate in a manner that allows the shutdown/wake-up command to trickle up through the series of daisy-chained packs. Because the internal linear regulator is powered down during shutdown, the shutdown function must operate when VAA is absent and it, therefore, cannot depend on a Schmitt trigger input. A special low-current, high-voltage circuit is used to detect the state of the SHDN pin. The shutdown pin has a +1.8V minimum threshold for the inactive state. When SHDN > 1.8V, the MAX11080 turns on and begins regulating VDDU and VDDL. If SHDN < 0.6V, the MAX11080 shuts down. For automatic shutdown when the pack is removed from the system, connect a 200k $\Omega$  resistor from SHDN to AGND.

Once SHDN is driven high, the power-up sequence follows that described for the internal linear regulator. The SHDN signal of the next higher module should be connected to VDDU through a  $20k\Omega$  resistor pullup. This connection ensures that the next module in the daisy chain is enabled as VDDU of the lower module powers up. This action propagates up the daisy chain until the last battery module is enabled. The shutdown of a VDDU supply pulls the connected SHDN pin of the upper module toward GNDL and propagates the shutdown signal up the daisy chain.

A shutdown signal propagated from the first daisychain device to the last incurs a certain amount of delay. A deasserted shutdown signal is not propagated to the next higher module until the charge pump has regulated the level-shifted upper port supply, VDDU, to a value greater than the SHDN V<sub>IH</sub> level. This time depends on both the charge-pump capacitor used and the value of the VDDU decoupling capacitor. A typical time delay of 10ms can be expected from the time the SHDN pin reaches the deasserted state until VDDU reaches its full specified value.

### **C1 Input Absolute Maximum Rating**

The C1 input is limited to  $V_{DCIN}$  - 0.6V above AGND or a maximum of 20V if the SHDN pin is asserted. If an application requires that the 20V restriction be removed during active shutdown, then a 4.0V zener diode can be added from V<sub>AA</sub> to AGND. This protects V<sub>AA</sub> and allows the C1 input to go to V<sub>DCIN</sub> - 0.6V regardless of the SHDN state. It also allows the differential C1 to C0 voltage to range from -0.3V to +80V.

### **Cell-Connection Detection**

An individual MAX11080 can be connected to as many as 12 series-connected cells. To accommodate configurations with fewer cells, unused cell inputs must be shorted together. The designer can choose which cell inputs to leave unused. The example application circuits in this document have chosen to populate the uppermost cell position and group the unused inputs just under this cell.

At power-up, the part compares the voltage applied to each cell input with a nominal cell-detection threshold voltage of 0.7V. If the cell voltage is less than the celldetection threshold, undervoltage detection is disabled for that cell input. If the voltage at the input is 0.7V or greater, undervoltage detection is specified by the state of the UVSEL\_ inputs. Overvoltage detection is always enabled for all cell-voltage inputs. The cell-connection detection occurs just before the MAX11080 is fully functional as shown in Figure 12 under "Number of Cells Detected."

### **TOPSEL** Function

The TOPSEL pin is used to indicate to a device whether it is the top device in the daisy-chain stack. The top daisy-chain device is responsible for generating the heartbeat signal at the top of the ALRM\_ pin bus. This heartbeat propagates along the chain toward the host. To designate a device as the top device, the TOPSEL pin should be connected to VAA. For all other devices in a daisy chain, this pin should be connected to AGND. The TOPSEL pin has a weak internal pulldown resistor, but this resistor should not be relied upon as the sole means of setting the TOPSEL logic level. The logic level of the TOPSEL pin is not latched internally at startup and is continuously sampled during operation. The ALRMU input should be connected to GNDU for the top module as good design practice to prevent noise pickup even though the input logic level is ignored.

For the single device application, the device enters the "level" mode when the TOPSEL is connected to AGND. The ALRM<sub>L</sub> shows the level of AGND for no alarm state and VAA for alarm state. ALRM<sub>U</sub> has to be tied to GND<sub>U</sub> for this mode. The following table summarizes the operation of TOPSEL and ALRM<sub>L</sub>:

| TOPSEL |       | ALRML     |       |  |

|--------|-------|-----------|-------|--|

| TOPSEL | ALRMU | No alarm  | alarm |  |

| 0      | 0     | 0         | 1     |  |

| 1      | Х     | Heartbeat | 1     |  |

### **Internal Self-Test**

The MAX11080 performs an internal self-test during power-up according to the linear regulator power-up flowchart (Figure 12). Each overvoltage comparator is tested for the ability to detect an internally generated overvoltage test condition. This is done by using the ground voltage level as the threshold reference in place of the usual threshold level. Figure 8 shows the connec-

tion for this test-mode compare level. If all comparators can detect the internally generated overvoltage test event, part operation continues. If any comparator fails to detect the internally generated overvoltage test event, a fault is signaled using the ALRML pin. The device must be power cycled to retest the comparators and attempt to clear this fault condition.

### **Failure Mode and Effects Analysis**

High-voltage battery-pack systems can be subjected to severe stresses during in-service fault conditions and could experience similar conditions during the manufacturing and assembly process. The MAX11080 is designed with high regard to these potential states. Open and short circuits at the package level must be readily detected for fault diagnosis and should be tolerated whenever possible. A number of circuits are employed within the MAX11080 specifically to detect such conditions and progress to a known device state. Table 3 summarizes other conditions typical in a normal manufacturing process along with their effect on the MAX11080 device.

See Table 4 for the FEMA analysis of the MAX11080. If the cell voltage is within the monitor range, the heartbeatsignal on the ALRML resumes once the fault condition (either open or short) is removed, unless specified.

| CONDITION                                                                               | EFFECT                                                                          | DESIGN RECOMMENDATION                                                                                                                                                               |  |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCB or IC package open or short circuit—<br>no stack load                               | Refer to the pin-level FMEA analysis spreadsheet available from the factory     | The built-in features of the MAX11080 should ensure low FMEA risk in most cases.                                                                                                    |  |

| Random connection of cells to IC—<br>no stack load                                      | No effect                                                                       | The series resistors on the cell inputs of<br>the MAX11080 as well as the internal<br>design ensure protection against random<br>power supply or ground connections.                |  |

| Random connection of modules—<br>no stack load                                          | No effect                                                                       | Each module is referenced to its neighbo<br>so no special connection order is<br>necessary.                                                                                         |  |

| Random connect/disconnect of<br>communication bus—no stack load;<br>AC- or DC-coupled   | Communication from host to the first break in the daisy-chain bus               | The level-shifted interface design of the MAX11080 ensures that the SHDN, GND, and ALRM_ communication bus can be connected at any time with no load.                               |  |

| Random connect/disconnect of<br>communication bus—with stack load;<br>AC- or DC-coupled | Communication from host to the first break in the daisy-chain bus               | The level-shifted interface design of the MAX11080 ensures that the SHDN, GND, ALRM_ communication bus can be connected at any time as long as the power bus is properly connected. |  |

| Connect/disconnect module interconnect<br>(bus bar)—no stack load                       | No effect for DC- or AC-coupled communication bus                               | A break in the power bus does not cause<br>a problem as long as there is no load on<br>the stack.                                                                                   |  |

| Removal/fault of module interconnect<br>(bus bar)—with stack load                       | No effect for AC-coupled communication bus; device damage for DC-coupled bus    | An AC-coupled bus with isolation on the SHDN pin or a redundant bus-bar connection should be used to protect against this case.                                                     |  |

| Removal/fault of module interconnect<br>(bus bar)—with stack under charge               | No effect for AC-coupled communication<br>bus; device damage for DC-coupled bus | An AC-coupled bus with isolation on the SHDN pin or a redundant bus-bar connection should be used to protect against this case.                                                     |  |

### **Table 3. System Fault Modes**

| PIN<br>NUMBER | NAME  | ACTION                 | EFFECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

|---------------|-------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1             | DCIN  | Open (or Disconnected) | ALRM <sub>L</sub> goes high (see Note 6).                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

| 1             | DOIN  | Short to Pin 2         | ALRML goes high.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

| 2             | HV    | Open (or Disconnected) | ALRM <sub>L</sub> goes high.                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| ۷             | IIV   | Short to Pin 3         | No effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

| 3             | N.C.  | Open (or Disconnected) | No effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

| 5             | N.C.  | Short to Pin 4         | No effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

| 4             | 4 C12 | Open (or Disconnected) | <ul> <li>If open occurs before power-up, the part works as if C12 does not exist because the internal circuit detects the situation and assumes it is what the application intended to do. The monitoring of C12 to C11 is disabled and is not enabled even if the pin is reconnected.</li> <li>If open occurs after power-up, it is considered a zero voltage input. ALRML goes high when the undervoltage is enabled.</li> </ul>                                    |                                                                                                                                        |

| 4             |       | Short to Pin 5         | <ul> <li>If short occurs before power-up, the part works as if C12 does not exist because the internal circuit detects the situation and assumes it is what the application intended to do. The monitoring of C12 to C11 is disabled and is not enabled even if the short is removed.</li> <li>If short occurs after power-up, the situation is treated as a zero voltage input for C12 to C11. ALRML goes high when the undervoltage is enabled.</li> </ul>          |                                                                                                                                        |

|               |       |                        | Open (or Disconnected)                                                                                                                                                                                                                                                                                                                                                                                                                                                | ALRM <sub>L</sub> goes high because it causes an overvoltage to the affected input pair even if the overvoltage is set to the maximum. |

| 5             | C11   | Short to Pin 6         | <ul> <li>If short occurs before power-up, the part works as if C11 does not exist because the internal circuit detects the situation and assumes it is what the application intended to do. The monitoring of C11 to C10 is disabled and is not enabled even if the short is removed.</li> <li>If short occurs after power-up, the situation is treated as a zero voltage input for C11 to C10. ALRML goes high when the undervoltage is enabled.</li> </ul>          |                                                                                                                                        |

|               |       | Open (or Disconnected) | $ALRM_L$ goes high as it causes an overvoltage to the affected input pair even if the overvoltage is set to the maximum.                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

| 6             | 6 C10 | Short to Pin 7         | <ul> <li>If short occurs before power-up, the part works as if C10 does not exist because the internal circuit detects the situation and assumes it is what the application intended to do. The monitoring of C10 to C9 is disabled and is not enabled even if the short is removed.</li> <li>If short occurs after power-up, the situation is treated as a zero voltage input for C10 to C9. ALRM<sub>L</sub> goes high when the undervoltage is enabled.</li> </ul> |                                                                                                                                        |

|               |       | Open (or Disconnected) | ${\sf ALRM}_{\sf L}$ goes high as it causes an overvoltage to the affected input pair even if the overvoltage is set to the maximum.                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |

| 7             | C9    | Short to Pin 8         | <ul> <li>If short occurs before power-up, the part works as if C9 does not exist because the internal circuit detects the situation and assumes it is what the application intended to do. The monitoring of C9 to C8 is disabled and is not enabled even if the short is removed.</li> <li>If short occurs after power-up, the situation is treated as a zero voltage input for C9 to C8. ALRM<sub>L</sub> goes high when the undervoltage is enabled.</li> </ul>    |                                                                                                                                        |

### Table 4. FEMA Analysis (Note 5)

| PIN<br>NUMBER | NAME            | ACTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EFFECT                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                 | Open (or Disconnected)                                                                                                                                                                                                                                                                                                                                                                                                                                             | ${\sf ALRM}_{\sf L}$ goes high as it causes an overvoltage to the affected input pair even if the overvoltage is set to the maximum.                                                                                                                                                                                                                                                                                                                    |