# Single Supply 3.0 V to 44 V, Low Power Operational Amplifiers

Quality bipolar fabrication with innovative design concepts are employed for the MC33171/72/74 series of monolithic operational amplifiers. These devices operate at 180  $\mu A$  per amplifier and offer 1.8 MHz of gain bandwidth product and 2.1 V/ $\mu s$  slew rate without the use of JFET device technology. Although this series can be operated from split supplies, it is particularly suited for single supply operation, since the common mode input voltage includes ground potential (V $_{\rm EE}$ ). With a Darlington input stage, these devices exhibit high input resistance, low input offset voltage and high gain. The all NPN output stage, characterized by no deadband crossover distortion and large output voltage swing, provides high capacitance drive capability, excellent phase and gain margins, low open loop high frequency output impedance and symmetrical source/sink AC frequency response.

The MC33171/72/74 are specified over the industrial/automotive temperature ranges. The complete series of single, dual and quad operational amplifiers are available in plastic as well as the surface mount packages.

#### **Features**

- Low Supply Current: 180 µA (Per Amplifier)

- Wide Supply Operating Range: 3.0 V to 44 V or ±1.5 V to ±22 V

- Wide Input Common Mode Range, Including Ground (V<sub>FF</sub>)

- Wide Bandwidth: 1.8 MHz

- High Slew Rate: 2.1 V/µs

- Low Input Offset Voltage: 2.0 mV

- Large Output Voltage Swing: -14.2 V to +14.2 V (with ±15 V Supplies)

- Large Capacitance Drive Capability: 0 pF to 500 pF

- Low Total Harmonic Distortion: 0.03%

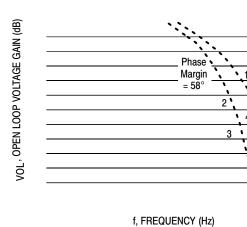

- Excellent Phase Margin: 60°

- Excellent Gain Margin: 15 dB

- Output Short Circuit Protection

- ESD Diodes Provide Input Protection for Dual and Quad

- Pb-Free Packages are Available

- NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes

### ON Semiconductor®

http://onsemi.com

PDIP-8 P SUFFIX CASE 626

SO-8 D, VD SUFFIX CASE 751

PDIP-14 P, VP SUFFIX CASE 646

SO-14 D, VD SUFFIX CASE 751A

TSSOP-14 DTB SUFFIX CASE 948G

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 10 of this data sheet.

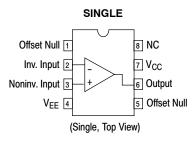

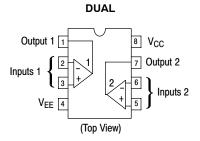

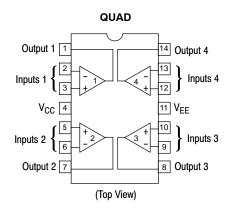

## **PIN CONNECTIONS**

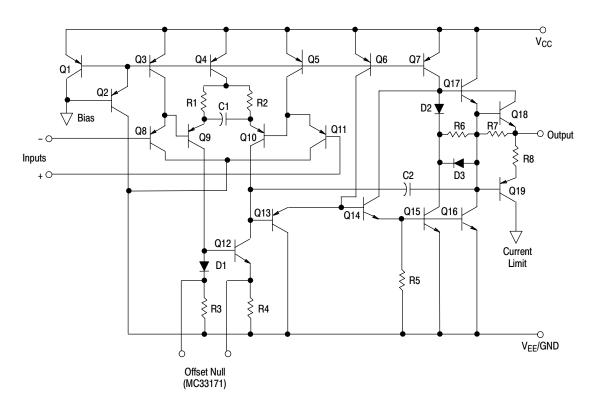

Figure 1. Representative Schematic Diagram (Each Amplifier)

#### **MAXIMUM RATINGS**

| Rating                                 | Symbol                           | Value       | Unit |

|----------------------------------------|----------------------------------|-------------|------|

| Supply Voltage                         | V <sub>CC</sub> /V <sub>EE</sub> | ±22         | V    |

| Input Differential Voltage Range       | V <sub>IDR</sub>                 | (Note 1)    | V    |

| Input Voltage Range                    | V <sub>IR</sub>                  | (Note 1)    | V    |

| Output Short Circuit Duration (Note 2) | t <sub>SC</sub>                  | Indefinite  | sec  |

| Operating Ambient Temperature Range    | T <sub>A</sub>                   | (Note 3)    | °C   |

| Operating Junction Temperature         | TJ                               | +150        | °C   |

| Storage Temperature Range              | T <sub>stg</sub>                 | -65 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# **DC ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = +15 V, $V_{EE}$ = -15 V, $R_L$ connected to ground, $T_A$ = +25°C, unless otherwise noted.)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                   | Symbol                   | Min                                                                                    | Тур                | Max                    | Unit  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------|--------------------|------------------------|-------|

| Input Offset Voltage ( $V_{CM} = 0 \text{ V}$ ) $V_{CC} = +15 \text{ V}, V_{EE} = -15 \text{ V}, T_A = +25^{\circ}\text{C}$ $V_{CC} = +5.0 \text{ V}, V_{EE} = 0 \text{ V}, T_A = +25^{\circ}\text{C}$ $V_{CC} = +15 \text{ V}, V_{EE} = -15 \text{ V}, T_A = T_{low} \text{ to } T_{high} \text{ (Note 3)}$                                                                                                                                      | V <sub>IO</sub>          | -<br>-<br>-                                                                            | 2.0<br>2.5<br>–    | 4.5<br>5.0<br>6.5      | mV    |

| Average Temperature Coefficient of Offset Voltage                                                                                                                                                                                                                                                                                                                                                                                                 | $\Delta V_{IO}/\Delta T$ | -                                                                                      | 10                 | -                      | μV/°C |

| Input Bias Current ( $V_{CM} = 0 \text{ V}$ ) $T_A = +25^{\circ}C$ $T_A = T_{low} \text{ to } T_{high} \text{ (Note 3)}$                                                                                                                                                                                                                                                                                                                          | I <sub>IB</sub>          | -<br>-                                                                                 | 20<br>-            | 100<br>200             | nA    |

| Input Offset Current ( $V_{CM} = 0 \text{ V}$ ) $T_A = +25^{\circ}\text{C}$ $T_A = T_{low} \text{ to } T_{high} \text{ (Note 3)}$                                                                                                                                                                                                                                                                                                                 | I <sub>IO</sub>          | _<br>_                                                                                 | 5.0<br>–           | 20<br>40               | nA    |

| Large Signal Voltage Gain ( $V_O = \pm 10 \text{ V}$ , $R_L = 10 \text{ k}$ )<br>$T_A = +25^{\circ}\text{C}$<br>$T_A = T_{low} \text{ to } T_{high} \text{ (Note 3)}$                                                                                                                                                                                                                                                                             | A <sub>VOL</sub>         | 50<br>25                                                                               | 500<br>-           | -<br>-                 | V/mV  |

| Output Voltage Swing $ \begin{array}{l} V_{CC} = +5.0 \text{ V}, \ V_{EE} = 0 \text{ V}, \ R_L = 10 \text{ k}, \ T_A = +25^{\circ}\text{C} \\ V_{CC} = +15 \text{ V}, \ V_{EE} = -15 \text{ V}, \ R_L = 10 \text{ k}, \ T_A = +25^{\circ}\text{C} \\ V_{CC} = +15 \text{ V}, \ V_{EE} = -15 \text{ V}, \ R_L = 10 \text{ k}, \ T_A = T_{low} \text{ to } T_{high} \text{ (Note 3)} \\ \end{array} $                                               | V <sub>OH</sub>          | 3.5<br>13.6<br>13.3                                                                    | 4.3<br>14.2<br>–   | -<br>-<br>-            | V     |

| $\begin{split} &V_{CC} = +5.0 \text{ V}, \text{ V}_{EE} = 0 \text{ V}, \text{ R}_{L} = 10 \text{ k}, \text{ T}_{A} = +25^{\circ}\text{C} \\ &V_{CC} = +15 \text{ V}, \text{ V}_{EE} = -15 \text{ V}, \text{ R}_{L} = 10 \text{ k}, \text{ T}_{A} = +25^{\circ}\text{C} \\ &V_{CC} = +15 \text{ V}, \text{ V}_{EE} = -15 \text{ V}, \text{ R}_{L} = 10 \text{ k}, \text{ T}_{A} = \text{T}_{low} \text{ to T}_{high} \text{ (Note 3)} \end{split}$ | V <sub>OL</sub>          | -<br>-<br>-                                                                            | 0.05<br>-14.2<br>- | 0.15<br>-13.6<br>-13.3 |       |

| Output Short Circuit (T <sub>A</sub> = +25°C) Input Overdrive = 1.0 V, Output to Ground Source Sink                                                                                                                                                                                                                                                                                                                                               | I <sub>SC</sub>          | 3.0<br>15                                                                              | 5.0<br>27          | -<br>-                 | mA    |

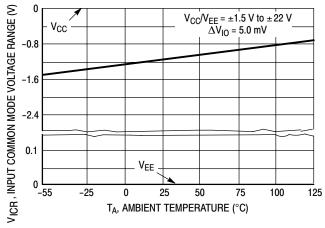

| Input Common Mode Voltage Range  T <sub>A</sub> = +25°C  T <sub>A</sub> = T <sub>low</sub> to T <sub>high</sub> (Note 3)                                                                                                                                                                                                                                                                                                                          | V <sub>ICR</sub>         | V <sub>EE</sub> to (V <sub>CC</sub> -1.8)<br>V <sub>EE</sub> to (V <sub>CC</sub> -2.2) |                    | V                      |       |

| Common Mode Rejection Ratio (R <sub>S</sub> ≤ 10 k), T <sub>A</sub> = +25°C                                                                                                                                                                                                                                                                                                                                                                       | CMRR                     | 80                                                                                     | 90                 | -                      | dB    |

| Power Supply Rejection Ratio (R <sub>S</sub> = 100 $\Omega$ ), T <sub>A</sub> = +25°C                                                                                                                                                                                                                                                                                                                                                             | PSRR                     | 80                                                                                     | 100                | -                      | dB    |

| Power Supply Current (Per Amplifier) $V_{CC} = +5.0 \text{ V, } V_{EE} = 0 \text{ V, } T_A = +25^{\circ}\text{C}$ $V_{CC} = +15 \text{ V, } V_{EE} = -15 \text{ V, } T_A = +25^{\circ}\text{C}$ $V_{CC} = +15 \text{ V, } V_{EE} = -15 \text{ V, } T_A = T_{low} \text{ to } T_{high} \text{ (Note 3)}$                                                                                                                                           | I <sub>D</sub>           | _<br>_<br>_                                                                            | 180<br>220<br>–    | 250<br>250<br>300      | μΑ    |

Either or both input voltages must not exceed the magnitude of V<sub>CC</sub> or V<sub>EE</sub>.

Power dissipation must be considered to ensure maximum junction temperature (T<sub>J</sub>) is not exceeded.

MC3317x T<sub>low</sub> = -40°C T<sub>high</sub> = +85°C T<sub>high</sub> = +125°C

$\textbf{AC ELECTRICAL CHARACTERISTICS} \ (V_{CC} = +15 \ \text{V}, \ V_{EE} = -15 \ \text{V}, \ R_L \ connected to ground,} \ T_A = +25 ^{\circ}C, \ unless \ otherwise \ noted.)$

| Characteristics                                                                                             | Symbol          | Min      | Тур        | Max    | Unit       |

|-------------------------------------------------------------------------------------------------------------|-----------------|----------|------------|--------|------------|

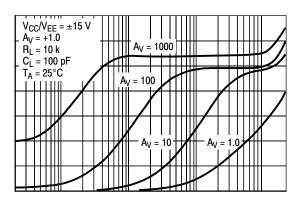

| Slew Rate ( $V_{in}$ = -10 V to +10 V, $R_L$ = 10 k, $C_L$ = 100 pF) $A_V$ +1 $A_V$ -1                      | SR              | 1.6<br>- | 2.1<br>2.1 | -      | V/µs       |

| Gain Bandwidth Product (f = 100 kHz)                                                                        | GBW             | 1.4      | 1.8        | -      | MHz        |

| Power Bandwidth $A_V = +1.0 R_L = 10 k$ , $V_O = 20 V_{pp}$ , THD = 5%                                      | BWp             | -        | 35         | -      | kHz        |

| Phase Margin $R_L = 10 \text{ k}$ $R_L = 10 \text{ k}, C_L = 100 \text{ pF}$                                | фт              | -<br>-   | 60<br>45   | -<br>- | Deg        |

| Gain Margin $R_L = 10 \text{ k}$ $R_L = 10 \text{ k}, C_L = 100 \text{ pF}$                                 | A <sub>m</sub>  | -<br>-   | 15<br>5.0  | -<br>- | dB         |

| Equivalent Input Noise Voltage $R_S = 100 \Omega$ , $f = 1.0 \text{ kHz}$                                   | e <sub>n</sub>  | -        | 32         | -      | nV∦Hz<br>— |

| Equivalent Input Noise Current (f = 1.0 kHz)                                                                | In              | -        | 0.2        | -      | pA∜Hz      |

| Differential Input Resistance<br>V <sub>cm</sub> = 0 V                                                      | R <sub>in</sub> | -        | 300        | -      | МΩ         |

| Input Capacitance                                                                                           | C <sub>in</sub> | -        | 0.8        | -      | pF         |

| Total Harmonic Distortion $A_V = +10$ , $R_L = 10$ k, $2.0$ $V_{pp} \le V_O \le 20$ $V_{pp}$ , $f = 10$ kHz | THD             | -        | 0.03       | -      | %          |

| Channel Separation (f = 10 kHz)                                                                             | CS              | -        | 120        | -      | dB         |

| Open Loop Output Impedance (f = 1.0 MHz)                                                                    | z <sub>o</sub>  | -        | 100        | -      | Ω          |

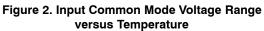

Figure 3. Split Supply Output Saturation versus Load Current

Gain

Margin

= 15 dB

220

Figure 4. Open Loop Voltage Gain and **Phase versus Frequency**

Figure 5. Phase Margin and Percent **Overshoot versus Load Capacitance**

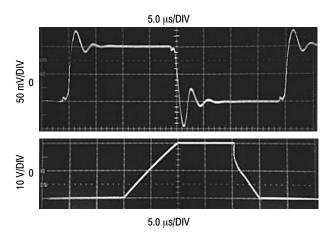

Figure 7. Small and Large Signal

**Transient Response**

Figure 6. Normalized Gain Bandwidth Product and Slew Rate versus Temperature

Figure 8. Output Impedance and Frequency

1.  $T_A = -55^{\circ}C$ 2.  $T_A = 25^{\circ}C$ Quad 2 3.  $T_A = 125^{\circ}C$ 3 Dual 2 3 Single 2 3

Figure 9. Supply Current versus Supply Voltage

#### APPLICATIONS INFORMATION - CIRCUIT DESCRIPTION/PERFORMANCE FEATURES

Although the bandwidth, slew rate, and settling time of the MC33171/72/74 amplifier family is similar to low power op amp products utilizing JFET input devices, these amplifiers offer additional advantages as a result of the PNP transistor differential inputs and an all NPN transistor output stage.

Because the input common mode voltage range of this input stage includes the  $V_{EE}$  potential, single supply operation is feasible to as low as 3.0 V with the common mode input voltage at ground potential.

The input stage also allows differential input voltages up to ±44 V, provided the maximum input voltage range is not exceeded. Specifically, the input voltages must range between V<sub>CC</sub> and V<sub>EE</sub> supply voltages as shown by the maximum rating table. In practice, although not recommended, the input voltages can exceed the V<sub>CC</sub> voltage by approximately 3.0 V and decrease below the V<sub>EE</sub> voltage by 0.3 V without causing product damage, although output phase reversal may occur. It is also possible to source up to 5.0 mA of current from V<sub>EE</sub> through either inputs' clamping diode without damage or latching, but phase reversal may again occur. If at least one input is within the common mode input voltage range and the other input is within the maximum input voltage range, no phase reversal will occur. If both inputs exceed the upper common mode input voltage limit, the output will be forced to its lowest voltage state.

Since the input capacitance associated with the small geometry input device is substantially lower (0.8 pF) than that of a typical JFET (3.0 pF), the frequency response for a given input source resistance is greatly enhanced. This becomes evident in D-to-A current to voltage conversion applications where the feedback resistance can form a pole with the input capacitance of the op amp. This input pole creates a 2nd Order system with the single pole op amp and is therefore detrimental to its settling time. In this context, lower input capacitance is desirable especially for higher values of feedback resistances (lower current DACs). This input pole can be compensated for by creating a feedback zero with a capacitance across the feedback resistance, if necessary, to reduce overshoot. For 10 k $\Omega$  of feedback resistance, the MC33171/72/74 family can typically settle to within 1/2 LSB of 8 bits in 4.2 µs, and within 1/2 LSB of 12 bits in 4.8 µs for a 10 V step. In a standard inverting unity gain fast settling configuration, the symmetrical slew rate is typically  $\pm 2.1$  V/ $\mu$ s. In the classic noninverting unity gain configuration the typical output positive slew rate is also 2.1 V/μs, and the corresponding negative slew rate will usually exceed the positive slew rate as a function of the fall time of the input waveform.

The all NPN output stage, shown in its basic form on the equivalent circuit schematic, offers unique advantages over the more conventional NPN/PNP transistor Class AB output stage. A 10 k $\Omega$  load resistance can typically swing within

0.8~V of the positive rail ( $V_{CC}$ ) and negative rail ( $V_{EE}$ ), providing a 28.4~Vpp swing from  $\pm 15~V$  supplies. This large output swing becomes most noticeable at lower supply voltages.

The positive swing is limited by the saturation voltage of the current source transistor Q7, the  $V_{BE}$  of the NPN pull-up transistor Q17, and the voltage drop associated with the short circuit resistance, R5. For sink currents less than 0.4 mA, the negative swing is limited by the saturation voltage of the pull-down transistor Q15, and the voltage drop across R4 and R5. For small valued sink currents, the above voltage drops are negligible, allowing the negative swing voltage to approach within millivolts of  $V_{EE}$ . For sink currents (> 0.4 mA), diode D3 clamps the voltage across R4. Thus the negative swing is limited by the saturation voltage of Q15, plus the forward diode drop of D3 ( $\approx V_{EE} + 1.0 \text{ V}$ ). Therefore an unprecedented peak–to–peak output voltage swing is possible for a given supply voltage as indicated by the output swing specifications.

If the load resistance is referenced to  $V_{CC}$  instead of ground for single supply applications, the maximum possible output swing can be achieved for a given supply voltage. For light load currents, the load resistance will pull the output to  $V_{CC}$  during the positive swing and the output will pull the load resistance near ground during the negative swing. The load resistance value should be much less than that of the feedback resistance to maximize pull–up capability.

Because the PNP output emitter–follower transistor has been eliminated, the MC33171/72/74 family offers a 15 mA minimum current sink capability, typically to an output voltage of ( $V_{\rm EE}$  +1.8 V). In single supply applications the output can directly source or sink base current from a common emitter NPN transistor for current switching applications.

In addition, the all NPN transistor output stage is inherently faster than PNP types, contributing to the bipolar amplifier's improved gain bandwidth product. The associated high frequency low output impedance (200  $\Omega$  typ @ 1.0 MHz) allows capacitive drive capability from 0 pF to 400 pF without oscillation in the noninverting unity gain configuration. The 60° phase margin and 15 dB gain margin, as well as the general gain and phase characteristics, are virtually independent of the source/sink output swing conditions. This allows easier system phase compensation, since output swing will not be a phase consideration. The AC characteristics of the MC33171/72/74 family also allow excellent active filter capability, especially for low voltage single supply applications.

Although the single supply specification is defined at 5.0 V, these amplifiers are functional to at least 3.0 V @ 25°C. However slight changes in parametrics such as bandwidth, slew rate, and DC gain may occur.

If power to this integrated circuit is applied in reverse polarity, or if the IC is installed backwards in a socket, large unlimited current surges will occur through the device that may result in device destruction.

As usual with most high frequency amplifiers, proper lead dress, component placement and PC board layout should be exercised for optimum frequency performance. For example, long unshielded input or output leads may result in unwanted input/output coupling. In order to preserve the relatively low input capacitance associated with these amplifiers, resistors connected to the inputs should be immediately adjacent to the input pin to minimize additional stray input capacitance. This not only minimizes the input

pole for optimum frequency response, but also minimizes extraneous "pick up" at this node. Supply decoupling with adequate capacitance immediately adjacent to the supply pin is also important, particularly over temperature, since many types of decoupling capacitors exhibit great impedance changes over temperature.

The output of any one amplifier is current limited and thus protected from a direct short to ground. However, under such conditions, it is important not to allow the device to exceed the maximum junction temperature rating. Typically for  $\pm 15~V$  supplies, any one output can be shorted continuously to ground without exceeding the maximum temperature rating.

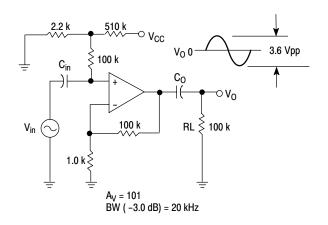

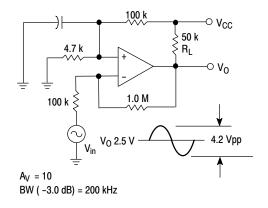

Figure 10. AC Coupled Noninverting Amplifier with Single +5.0 V Supply

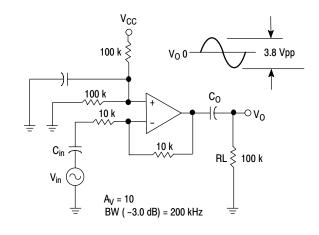

Figure 12. DC Coupled Inverting Amplifier

Maximum Output Swing with Single

+5.0 V Supply

Figure 14. Active High-Q Notch Filter

Figure 11. AC Coupled Inverting Amplifier with Single +5.0 V Supply

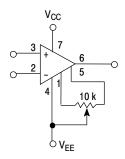

Offset Nulling range is approximately ±80 mV with a 10 k potentiometer, MC33171 only.

Figure 13. Offset Nulling Circuit

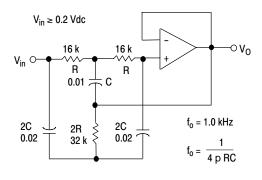

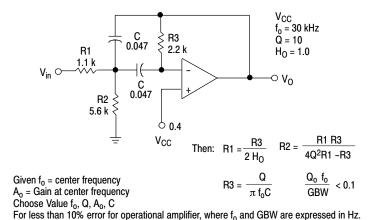

Figure 15. Active Bandpass Filter

## **ORDERING INFORMATION**

| Op Amp<br>Function | Device        | Operating<br>Temperature Range                      | Package                  | Shipping <sup>†</sup> |

|--------------------|---------------|-----------------------------------------------------|--------------------------|-----------------------|

|                    | MC33171D      |                                                     | SO-8                     |                       |

|                    | MC33171DG     |                                                     | SO-8<br>(Pb-Free)        | 98 Units/Rail         |

|                    | MC33171DR2    |                                                     | SO-8                     |                       |

| Single             | MC33171DR2G   | $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | SO-8<br>(Pb-Free)        | 2500 / Tape & Reel    |

|                    | MC33171P      |                                                     | Plastic DIP              |                       |

|                    | MC33171PG     | ]                                                   | Plastic DIP<br>(Pb-Free) | 50 Units/Rail         |

|                    | MC33172D      |                                                     | SO-8                     |                       |

|                    | MC33172DG     | ]                                                   | SO-8<br>(Pb-Free)        | 98 Units/Rail         |

|                    | MC33172DR2    |                                                     | SO-8                     |                       |

|                    | MC33172DR2G   | $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | SO-8<br>(Pb-Free)        | 2500 / Tape & Reel    |

|                    | MC33172P      |                                                     | Plastic DIP              |                       |

| Dual               | MC33172PG     |                                                     | Plastic DIP<br>(Pb-Free) | 50 Units/Rail         |

|                    | MC33172VD     | T <sub>A</sub> = -40° to +125°C                     | SO-8                     |                       |

|                    | MC33172VDG    |                                                     | SO-8<br>(Pb-Free)        | 98 Units/Rail         |

|                    | MC33172VDR2   |                                                     | SO-8                     | 2500 / Tape & Reel    |

|                    | MC33172VDR2G  |                                                     | SO-8<br>(Pb-Free)        |                       |

|                    | NCV33172DR2** |                                                     | SO-8                     | 2500 / Tape & Reel    |

|                    | MC33174D      |                                                     | SO-14                    |                       |

|                    | MC33174DG     |                                                     | SO-14<br>(Pb-Free)       | 55 Units/Rail         |

|                    | MC33174DR2    |                                                     | SO-14                    |                       |

|                    | MC33174DR2G   |                                                     | SO-14<br>(Pb-Free)       | 2500 / Tape & Reel    |

|                    | MC33174DTB    | $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | TSSOP-14*                | 06 Unito/Poil         |

|                    | MC33174DTBG   |                                                     | TSSOP-14*                | 96 Units/Rail         |

|                    | MC33174DTBR2  |                                                     | TSSOP-14*                | 2500 / Tana & Book    |

| Quad               | MC33174DTBR2G |                                                     | TSSOP-14*                | 2500 / Tape & Reel    |

|                    | MC33174P      |                                                     | Plastic DIP              |                       |

|                    | MC33174PG     |                                                     | Plastic DIP<br>(Pb-Free) | 25 Units/Rail         |

|                    | MC33174VDR2   | T <sub>A</sub> = -40° to +125°C                     | SO-14                    |                       |

|                    | MC33174VDR2G  |                                                     | SO-14<br>(Pb-Free)       | 2500 / Tape & Reel    |

|                    | MC33174VP     |                                                     | Plastic DIP              |                       |

|                    | MC33174VPG    |                                                     | Plastic DIP<br>(Pb-Free) | 25 Units/Rail         |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*This package is inherently Pb–Free.

\*\*NCV prefix for automotive and other applications requiring site and control changes.

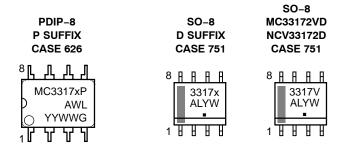

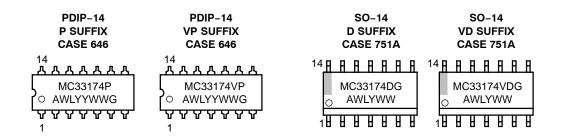

#### **MARKING DIAGRAMS**

x = 1 or 2

A = Assembly Location

WL, L = Wafer Lot YY, Y = YearWW, W = Work Week

G or ■ = Pb-Free Package

(Note: Microdot may be in either location)

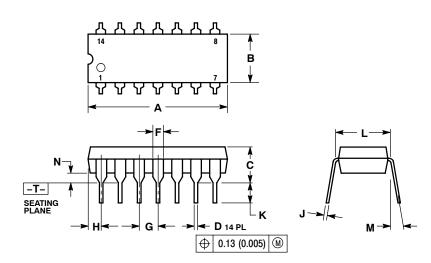

# PACKAGE DIMENSIONS

PDIP-8 **P SUFFIX** CASE 626-05 ISSUE L

- NOTES:

1. DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

2. PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CORNERS).

3. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

# PACKAGE DIMENSIONS

SOIC-8 NB CASE 751-07 ISSUE AH

# **PACKAGE DIMENSIONS**

PDIP-14 CASE 646-06 ISSUE P

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

|     | INCHES |       | MILLIMETERS |       |  |

|-----|--------|-------|-------------|-------|--|

| DIM | MIN    | MAX   | MIN         | MAX   |  |

| Α   | 0.715  | 0.770 | 18.16       | 19.56 |  |

| В   | 0.240  | 0.260 | 6.10        | 6.60  |  |

| O   | 0.145  | 0.185 | 3.69        | 4.69  |  |

| D   | 0.015  | 0.021 | 0.38        | 0.53  |  |

| F   | 0.040  | 0.070 | 1.02        | 1.78  |  |

| G   | 0.100  | BSC   | 2.54 BSC    |       |  |

| Н   | 0.052  | 0.095 | 1.32        | 2.41  |  |

| ſ   | 0.008  | 0.015 | 0.20        | 0.38  |  |

| K   | 0.115  | 0.135 | 2.92        | 3.43  |  |

| ٦   | 0.290  | 0.310 | 7.37        | 7.87  |  |

| М   |        | 10 °  |             | 10 °  |  |

| N   | 0.015  | 0.039 | 0.38        | 1.01  |  |

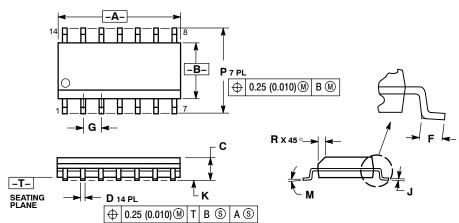

#### **PACKAGE DIMENSIONS**

SOIC-14 CASE 751A-03 **ISSUE H**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- PER SIDE.

5. DIMENSION D DOES NOT INCLUDE

DAMBAR PROTRUSION. ALLOWABLE

DAMBAR PROTRUSION SHALL BE 0.127

(0.005) TOTAL IN EXCESS OF THE D

DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 8.55        | 8.75 | 0.337     | 0.344 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.054     | 0.068 |

| D   | 0.35        | 0.49 | 0.014     | 0.019 |

| F   | 0.40        | 1.25 | 0.016     | 0.049 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| J   | 0.19        | 0.25 | 0.008     | 0.009 |

| K   | 0.10        | 0.25 | 0.004     | 0.009 |

| М   | 0 °         | 7°   | 0 °       | 7 °   |

| Р   | 5.80        | 6.20 | 0.228     | 0.244 |

| R   | 0.25        | 0.50 | 0.010     | 0.019 |

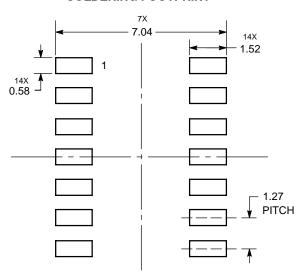

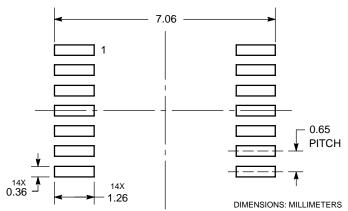

#### **SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

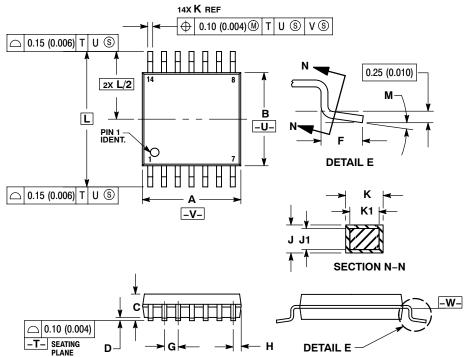

#### **PACKAGE DIMENSIONS**

TSSOP-14 CASE 948G-01 ISSUE B

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT

- MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

5. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMIIM MATERIAL DIMENSION AT MAXIMIIM MATERIAL DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY. 7. DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE –W–.

|     | MILLIN            | IETERS | INCHES    |       |

|-----|-------------------|--------|-----------|-------|

| DIM | MIN               | MAX    | MIN       | MAX   |

| Α   | 4.90              | 5.10   | 0.193     | 0.200 |

| В   | 4.30              | 4.50   | 0.169     | 0.177 |

| С   |                   | 1.20   |           | 0.047 |

| D   | 0.05              | 0.15   | 0.002     | 0.006 |

| F   | 0.50              | 0.75   | 0.020     | 0.030 |

| G   | 0.65 BSC          |        | 0.026 BSC |       |

| Н   | 0.50              | 0.60   | 0.020     | 0.024 |

| J   | 0.09              | 0.20   | 0.004     | 0.008 |

| J1  | 0.09              | 0.16   | 0.004     | 0.006 |

| Κ   | 0.19              | 0.30   | 0.007     | 0.012 |

| K1  | 0.19              | 0.25   | 0.007     | 0.010 |

| L   | 6.40 BSC 0.252 BS |        | BSC       |       |

| М   | 0 °               | 8 °    | 0 °       | 8 °   |

### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and una are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative