# **Product Change Notification / SYST-04TNIL668**

| ١ ـ | 1 | _ |   |

|-----|---|---|---|

| ıa  | т | Δ | ۰ |

|     |   | · |   |

15-Jan-2024

# **Product Category:**

**Ethernet PHYs**

# **PCN Type:**

Document Change

# **Notification Subject:**

LAN8670/1/2 Silicon Errata and Data Sheet Clarification

# **Affected CPNs:**

SYST-04TNIL668\_Affected\_CPN\_01152024.pdf SYST-04TNIL668\_Affected\_CPN\_01152024.csv

# **Notification Text:**

SYST-04TNIL668

Microchip has released a new Document for the LAN8670/1/2 Silicon Errata and Data Sheet Clarification of devices. If you are using one of these devices please read the document located at LAN8670/1/2 Silicon Errata and Data Sheet Clarification.

**Notification Status: Final**

Description of Change: Updated for Rev C2 Silicon/Package Marking.

Impacts to Data Sheet: None

Reason for Change: To improve productivity

Change Implementation Status: Complete

Date Document Changes Effective: 15 Jan 2024

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices::N/A

| Attachments:                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAN8670/1/2 Silicon Errata and Data Sheet Clarification                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

| Please contact your local Microchip sales office with questions or concerns regarding this notification.                                                                                                                                                                                    |

| Terms and Conditions:                                                                                                                                                                                                                                                                       |

| If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section. |

| If you wish to <u>change your PCN profile, including opt out,</u> please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.                                       |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

# Affected Catalog Part Numbers (CPN)

LAN8670B1-E/LMX

LAN8670B1T-E/LMX

LAN8670C1-E/LMX

LAN8670C2-E/LMX

LAN8670C1-E/LMXVAO

LAN8670C2-E/LMXVAO

LAN8670C1T-E/LMX

LAN8670C2T-E/LMX

LAN8670C1T-E/LMXVAO

LAN8670C2T-E/LMXVAO

LAN8671B1-E/U3B

LAN8671B1T-E/U3B

LAN8671C1-E/U3B

LAN8671C2-E/U3B

LAN8671C1-E/U3BVAO

LAN8671C2-E/U3BVAO

LAN8671C1T-E/U3B

LAN8671C2T-E/U3B

LAN8671C1T-E/U3BVAO

LAN8671C2T-E/U3BVAO

LAN8672B1-E/LNX

LAN8672B1T-E/LNX

LAN8672C1-E/LNX

LAN8672C2-E/LNX

LAN8672C1-E/LNXVAO

LAN8672C2-E/LNXVAO

LAN8672C1T-E/LNX

LAN8672C2T-E/LNX

LAN8672C1T-E/LNXVAO

LAN8672C2T-E/LNXVAO

# LAN8670/1/2

# **Silicon Errata and Data Sheet Clarifications**

The LAN8670/1/2 devices that you have received conform functionally to the Device Data Sheet (DS60001573H), except for the anomalies described in this document.

The issues discussed in the following pages are for hardware revisions listed in Table 1. The silicon issues are summarized in Table 2. Items relating to data sheet changes are summarized in Table 3 of the Data Sheet Clarifications section.

TABLE 1: SILICON PART ID AND HARDWARE REVISION VALUES

| Part Number | Part ID <sup>1</sup> | Hardware Revision <sup>1</sup> | Package Marking |

|-------------|----------------------|--------------------------------|-----------------|

| LAN8670     | 010110               | 0101                           | C2              |

| LAN8671     | 010110               | 0100                           | C1              |

| LAN8672     | 010110               | 0010                           | B1              |

**Note 1:** The Part ID and Hardware Revision are located in the PHY\_ID2 register Model Number and Revision Number fields, respectively. See Data Sheet (DS60001573H) for details.

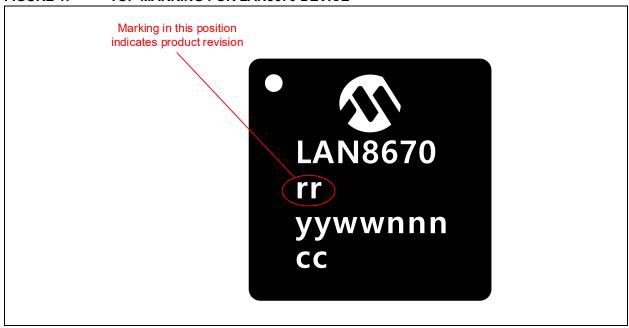

# FIGURE 1: TOP MARKING FOR LAN8670 DEVICE

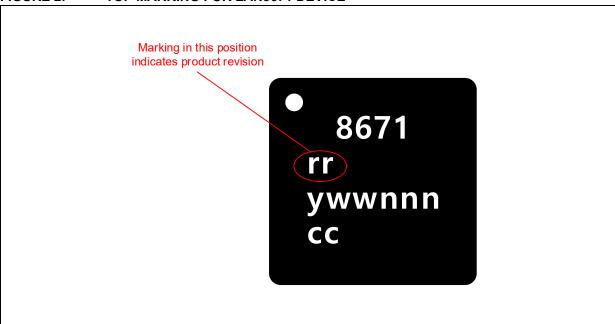

FIGURE 2: TOP MARKING FOR LAN8671 DEVICE

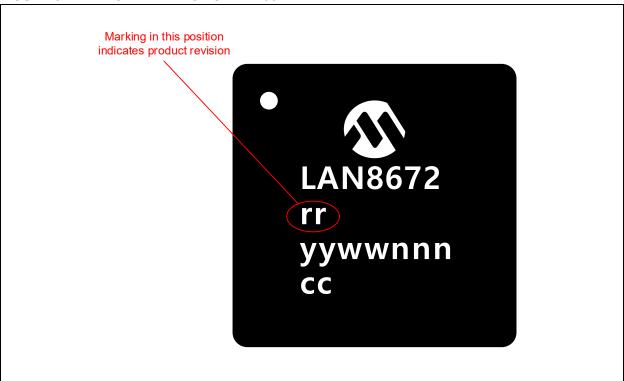

# FIGURE 3: TOP MARKING FOR LAN8672 DEVICE

TABLE 2: SILICON ISSUE SUMMARY

| Item   | Issue Summary                                                                                                             |                    | Affected Devices   |                    |  |

|--------|---------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--|

| Number |                                                                                                                           |                    | Rev C1             | Rev C2             |  |

| s1.    | Media interface mode (RMII) identification                                                                                | LAN8671            | -                  | -                  |  |

| s2.    | Package Type identification                                                                                               | LAN8671            | -                  | -                  |  |

| s3.    | RMII CSMA/CD operation in mixed PLCA segments                                                                             | LAN8670<br>LAN8671 | LAN8670<br>LAN8671 | LAN8670<br>LAN8671 |  |

| s4.    | Incorrect reset indication on IRQ_N                                                                                       | ALL                | -                  | -                  |  |

| s5.    | Multi-coordinator PLCA action                                                                                             | ALL                | ALL                | ALL                |  |

| s6.    | Transmission of collision fragments with PLCA and RMII                                                                    | LAN8670<br>LAN8671 | LAN8670<br>LAN8671 | LAN8670<br>LAN8671 |  |

| s7.    | In RMII mode: incorrect assertion of Carrier Sense may occur following a logical collision                                | LAN8670<br>LAN8671 | LAN8670<br>LAN8671 | -                  |  |

| s8.    | Revert to CSMA/CD when PLCA Beacons are missing                                                                           | ALL                | -                  | -                  |  |

| s9.    | Packet pattern matcher incorrectly matches for all message types                                                          | ALL                | -                  | -                  |  |

| s10.   | SLPCAL field of SLPCTL0 register may deliver invalid result on read                                                       | -                  | ALL                | ALL                |  |

| s11.   | When configured as a PLCA coordinator, the device does not stop transmitting beacons immediately upon entering sleep mode | -                  | ALL                | ALL                |  |

| s12.   | A trade-off exists between noise immunity and carrier sense latency                                                       | -                  | ALL                | ALL                |  |

Legend

- Erratum is not applicable.

### Silicon Errata Issues:

# s1. Module: Media interface mode (RMII) identification

Resolved with the release of Silicon Rev C1.

# s2. Module: Package Type identification

Resolved with the release of Silicon Rev C1.

### s3. Module: RMII CSMA/CD operation in mixed PLCA segments

### **DESCRIPTION**

The LAN8670/1 RMII cannot be operated with PLCA disabled on a network with other PLCA-enabled nodes. When the device is configured for CSMA/CD operation (i.e., PLCA is disabled), then the reception of PLCA BEACON and COM-MIT symbols from the network will be improperly transferred via the RMII to the MAC resulting in undefined behavior including dropped packets.

The LAN8672 does not support RMII operation.

### **END USER IMPLICATIONS**

The RMII may only be used with PLCA disabled when all other nodes on the mixing segment are also configured for pure CSMA/CD operation.

### **Work Around**

None.

# LAN8670/1/2

# s4. Module: Incorrect reset indication on IRQ\_N

Resolved with the release of Silicon Rev C1.

# s5. Module: Multi-coordinator PLCA action

### **DESCRIPTION**

When operating as a PLCA Coordinator, if the PHY receives an unexpected BEACON from an additional coordinator on the segment, it will set the Unexpected BEACON Received (UNEXPB) bit in the Status 1 (STS1) register. The PHY will then enter a recovery state in which it can receive packets but will transmit neither packets nor BEACONs for the next two PLCA bus cycles. Should the duplicate Coordinator continue sending periodic BEACONs, then the PHY will remain in the recovery state unable to transmit to avoid collisions with the duplicate Coordinator in Transmit Opportunity 0.

Clause 148 of the IEEE 802.3cg-2019™ specification describes that when this condition occurs, the PHY should avoid transmitting in its transmit opportunity until the end of the current bus cycle when the PHY will again transmit its BEA-CON to the segment.

### **END USER IMPLICATIONS**

The PHY will halt transmitting packets and BEACONs to the network when configured as a PLCA Coordinator and an unexpected BEACON is detected. This results in the node becoming an inactive Coordinator.

# **Work Around**

The station management entity should monitor the Unexpected BEACON Received bit and configure the PHY as a PLCA Follower.

### s6. Module: Transmission of collision fragments with PLCA and RMII

### **DESCRIPTION**

Clause 4 of the IEEE Std 802.3-2018<sup>™</sup> specifies the MAC shall implement an Inter-Packet Gap (IPG) delay of 96 bit times (BT) between packets. This IPG is split into two parts. The first part, IPG part 1, requires that no carrier be sensed. If carrier is sensed during IPG part 1, then the timer is restarted. Once IPG part 1 is complete, the MAC may transmit following IPG part 2. The IPG part 1 is nominally 64 BT, but may be less, including zero. The IPG part 2 timing is nominally 32 BT, but is always equal to the full IPG duration minus the IPG part 1.

Some MACs implement an IPG part 1 of very small duration. If the IPG part 1 time is too small, then the MAC may attempt to transmit after the PHY has asserted carrier indication with CRSDV. The result is that the MAC will quickly detect a collision and send a collision fragment to the PHY. When PLCA is enabled, the PHY, not expecting the MAC to transmit after carrier was indicated, will not detect the collision and end up transmitting the collision fragment to the network.

#### **END USER IMPLICATIONS**

Use of a MAC with an IPG part 1 time of less than 18 bits will result in the transmission of short 10.4 µs packets onto the network.

### **Work Around**

While the transmission of the collision fragments to the network are benign, they may be eliminated by reducing the size of the PLCA delay line buffer with the register configuration provided below. This will cause the PHY to detect a normal logical collision preventing the transmission of the collision fragment. Additionally, the PHY will capture the next transmit opportunity guaranteeing the MAC the ability to transmit according to the PLCA algorithm.

| <b>Access</b><br>RMW | <b>MMD</b><br>0x1F | <b>Address</b><br>0x008F | <b>Data</b><br>0x00D0 | <b>Mask</b><br>0x07F0 |

|----------------------|--------------------|--------------------------|-----------------------|-----------------------|

| Legend:              |                    |                          |                       |                       |

| R - Read             |                    |                          |                       |                       |

| W - Write            |                    |                          |                       |                       |

| RMW - Read-Mo        | odified Write      |                          |                       |                       |

# s7. Module: In RMII mode: incorrect assertion of Carrier Sense may occur following a logical collision

Resolved with the release of Silicon Rev C2.

### s8. Module: Revert to CSMA/CD when PLCA Beacons are missing

Resolved with the release of Silicon Rev C1.

# s9. Module: Packet pattern matcher incorrectly matches for all message types

Resolved with the release of Silicon Rev C1.

# LAN8670/1/2

### s10. Module: SLPCAL field of SLPCTL0 register may deliver invalid result on read

### **DESCRIPTION**

When reading the SLPCTL0 register, the SLPCAL field returns 0x0001. This bitfield must always be written as 0x0000.

### **END USER IMPLICATIONS**

Sleep mode may not function properly if this bitfield is set to anything other than 0.

### **Work Around**

When writing to the SLPCTL0, including when performing read-modify-write sequences, ensure that the SLPCAL bitfield is always written as 0x0000.

# s11. Module: When configured as a PLCA coordinator, the device does not stop transmitting beacons immediately upon entering sleep mode

#### DESCRIPTION

The device does not stop transmitting beacons immediately upon entering sleep mode when configured as a PLCA coordinator. The coordinator node, NODE\_ID = 0, transmits a beacon at the start of each PLCA bus cycle. When sleep mode begins, the transmitter is not disabled until VDDA drops below its valid level. When configured to sleep on the inactivity timeout, the coordinator node will recognize the beacon as bus activity and wake itself back up.

#### **END USER IMPLICATIONS**

The coordinator mode will not reliably remain in sleep mode when configured to sleep on an inactivity timeout, as it will interpret its own beacon as network activity. Continued presence of beacons will cause other devices on the mixing segment to detect signal activity, so any other devices that are configured to sleep on inactivity will not sleep.

### Work Around

The coordinator node (NODE\_ID = 0) must never be configured to sleep on inactivity timers. It must be put into sleep mode by its station controller. In addition, immediately before entering sleep, the coordinator must have PLCA disabled to stop the beacon.

- 1. Clear the EN bit of the PLCA CTRL0 to disable the beacon.

- 2. Enter sleep mode and configure a non-zero delay by writing to the following bitfields of SLPCTL0:

- Set SLPEN to 1

- Set WKINEN and MDIWKEN to configure desired wake source(s)

- SLPCAL must be written as 0x0.

- · Set SLPINHDLY to 1 or greater.

### s12. Module: A trade-off exists between noise immunity and carrier sense latency

### **DESCRIPTION**

When configured to work in noisy environments, such as those required to pass standard EMI/EMC tests, it is necessary to use additional filtering, which increases carrier sense latency. The recommended default configuration, which is required to pass these tests, results in a longer carrier assertion time, which imposes a limitation on the usable range of the PLCA Transmit Opportunity Timer. As a reminder, this value must be configured equally among all nodes in the mixing segment. Values below the default can, theoretically, provide insignificant increases in throughput at the cost of system robustness.

### **END USER IMPLICATIONS**

- The default value, in the specification and for this device, is 3.2us (TO\_TMR=32). Using this value is strongly recommended except when collisions are detected on a PLCA enabled multidrop mixing segment containing third party devices.

- This device should never be configured with TO\_TMR < 29, and values less than 32 require the user thoroughly

test the final system for robustness.</li>

### **Workaround:**

The Transmit Opportunity timer (TO\_TMR) should be configured with the default value of 32. In the event that a smaller value is used, it must always be 29 or greater.

If collisions are detected during operation with devices from third-party vendors on the mixing segment, the Transmit Opportunity Timer may need to be increased to greater than 32. As the necessary value will be dependent upon various latency characteristics of other devices on the mixing segment, as well as the propagation delay on the physical medium, contact Microchip support.

TABLE 3: DATA SHEET CLARIFICATION SUMMARY

| Item<br>Number | Port/Function                                                              | Issue Summary                                                                                 | Resolved with Data<br>Sheet Revision |

|----------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------|

| d1.            | Table 3-7. Miscellaneous Pins                                              | The table incorrectly states that clock oscillators may be used in MII mode.                  | DS60001573F                          |

| d2.            | Section 4.1 Media Independent Interface (MII)                              | Text does not clearly state that a crystal must be used in MII mode.                          | DS60001573F                          |

| d3.            | Section 4.8.1 Crystal Pins (XTI/XTO)                                       | Text incorrectly states that clock oscillators may be used in MII mode.                       | DS60001573F                          |

| d4.            | Figure 4-4. Crystal Oscillator Input                                       | Figure incorrectly states that clock oscillators may be used in MII mode.                     | DS60001573F                          |

| d5.            | Table 7-7. DC Electrical<br>Characteristics (other than<br>10BASE-T1S PMA) | Note 3 incorrectly states that the MII crystal input XTI may be driven by a clock oscillator. | DS60001573F                          |

# **Data Sheet Clarifications:**

The following typographic corrections and clarifications are to be noted for the data sheet (DS60001573H):

**Note:** Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

# d1. Module: Table 3-7. Miscellaneous Pins

Resolved with the release of Data Sheet DS60001573F.

# d2. Module: Section 4.1 Media Independent Interface (MII)

Resolved with the release of Data Sheet DS60001573F.

# d3. Module: Section 4.8.1 Crystal Pins (XTI/XTO)

Resolved with the release of Data Sheet DS60001573F.

# d4. Module: Figure 4-4. Crystal Oscillator Input

Resolved with the release of Data Sheet DS60001573F.

# d5. Module: Table 7-7. DC Electrical Characteristics (other than 10BASE-T1S PMA)

Resolved with the release of Data Sheet DS60001573F.

# **APPENDIX A: DOCUMENT REVISION HISTORY**

| Revision Level & Date | Section/Figure/Entry | Correction                                                    |

|-----------------------|----------------------|---------------------------------------------------------------|

| DS80000962E, 12/2023  | s7                   | Updated for Rev C2 Silicon                                    |

| DS80000962D, 7/2023   | s7<br>s11            | Updated details Clarified issue summary                       |

| DS80000962C, 6/2023   |                      | Updated for Rev C1 Silicon Data Sheet Clarifications resolved |

| DS80000962B, 1/2023   |                      | Added Data Sheet Clarification section                        |

| DS80000962A, 7/2021   | All                  | Initial Release of Errata                                     |

NOTES:

### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and

under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at https://www.microchip.com/en-us/support/design-help/client-support-services

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2023, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-3614-4

# **Worldwide Sales and Service**

### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address:

www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi. MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000

**China - Chengdu** Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou

Tel: 86-186-6233-1526 China - Wuhan

Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore

Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Garching** Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana

Tel: 972-9-744-7705

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340 Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820