**Datasheet**

### Triple half-bridge gate driver with programmable currents

# STORMEROZAN

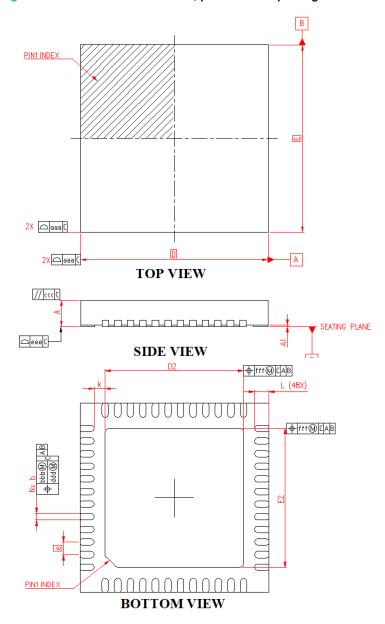

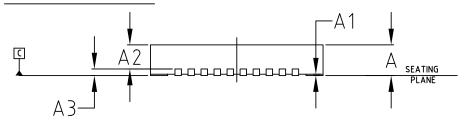

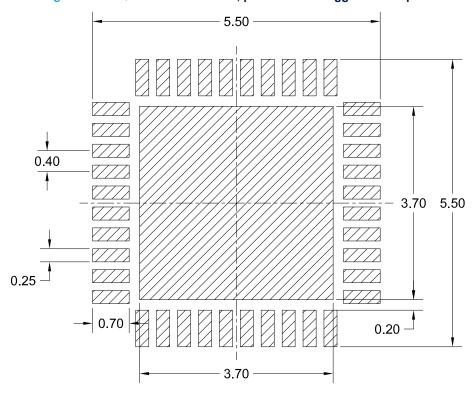

VFQFPN 48L, 6x6x1 mm

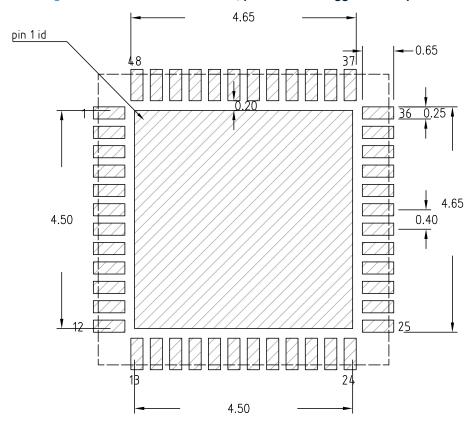

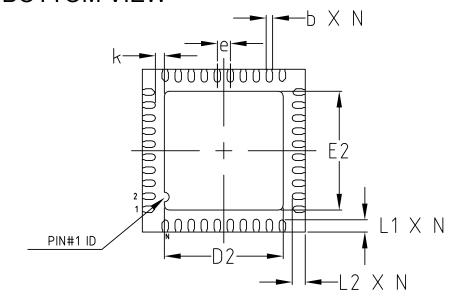

VFQFPN 40L, 5x5x1 mm

# STDRIVE

#### Product status link

STDRIVE102BH

STDRIVE102H

#### Product label

#### **Features**

- Operating voltage from 6 to 50 V

- Gate drivers with programmable current capability up to:

- 1 A source current

- 2 A sink current

- High robustness against below-ground and overshoot

- Charge pump for 100 % duty cycle operation with dedicated undervoltage lockout protection

- Flexible power management:

- 12 V LDO linear regulator with dedicated undervoltage lockout protection

- 3.3 V LDO linear regulator with dedicated undervoltage lockout protection

- Standby mode for low consumption less than 50 nA

- Thermal shutdown protection

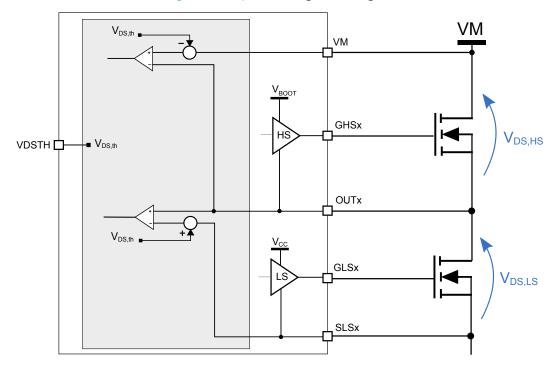

- V<sub>DS</sub> monitoring for safe driving operation of the power MOSFETs

- Flexible analog front-end:

- Up to three wide-bandwidth operational amplifiers

- Up to three high-speed comparators

- Dual control modes:

- ENx/INx

- INHx/INLX with interlocking

- Matched propagation delay for all channels

- Logic inputs up to 5 V, TTL compatible

#### **Applications**

- Battery supplied power tools

- Portable vacuum cleaners

- E-bikes

- Industrial automation

- Robotics

- Pumps and fans

#### **Description**

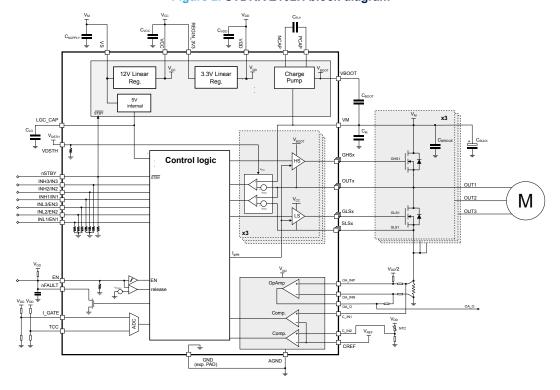

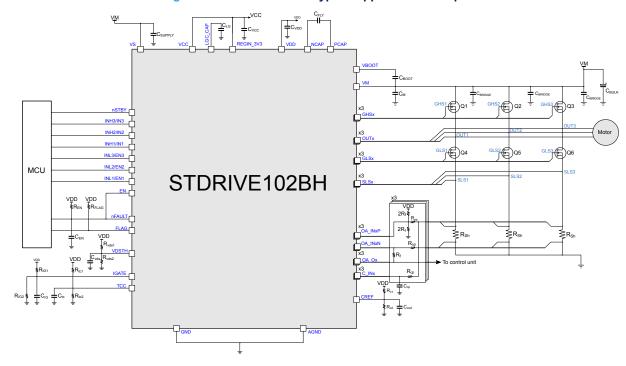

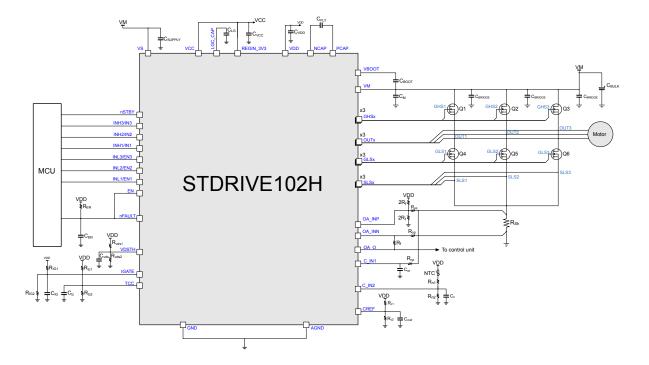

The STDRIVE102BH and the STDRIVE102H are triple half-bridge gate drivers suitable for 3-phase brushless motor driving.

The STDRIVE102BH/H is the optimal solution for battery supplied motor driver applications such as power tools, vacuum cleaner and small appliances thanks to its very efficient stand-by mode, that strongly reduce the current consumption when the device is not active.

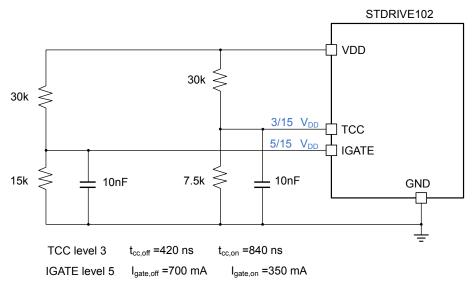

The gate drivers are designed to drive, with a programmable gate current, six external N-channel power MOSFETs, allowing a superior performance of the power stage and regulating the slew rate of power outputs without the need of external gate resistors. The different configurations of the drivers can be selected through two analog pins (IGATE and TCC).

An integrated charge pump supplies the three high-side drivers, enabling unlimited on-time of the high-side MOSFETs.

An embedded 12 V LDO linear regulator provides the supply of the three low-side drivers and its output is available on the VCC pin, to also supply external loads.

Another LDO linear regulator provides a 3.3 V on the VDD pin to supply external low-voltage components and the embedded analog front-end (AFE), which has a different configuration, depending on the device part number: the STDRIVE102BH integrates three operational amplifiers and three comparators, the STDRIVE102H integrates one operational amplifier and two comparators. In a typical application, the operational amplifiers can be used to monitor the voltage across the shunt resistor(s) sensing the current flowing in the motor phases. Concurrently, the comparators can be used to detect dangerous overcurrent conditions.

A full set of embedded protections is present to increase the overall application robustness: undervoltage lockout (UVLO) on each supply (VCC, VDD, and charge pump voltage), thermal shutdown, and a  $V_{DS}$  monitoring on both high-side and low-side MOSFETs. In case a protection is triggered, the nFAULT open-drain pin signals the event. The STDRIVE102BH has another dedicated open-drain pin (FLAG) which indicates whether the gate driver supply  $V_{CC}$  falls below the guard limit. The device integrates a smart shutdown function which allows immediate turn-off of the outputs of the gate driver in the case of fault, by minimizing the propagation delay between the fault detection event and the actual output switch-off.

In addition to the main supply pin (VS), the STDRIVE102BH/H has dedicated pin VM, which should be connected to the motor supply voltage, in correspondence of the drains of the high side N-channel MOSFETs. The VM pin is used for the integrated  $V_{DS}$  monitoring as well as a reference voltage for the charge pump. To increase device's flexibility, the VS and VM pin can operate at different voltages.

DS14545 - Rev 1 page 2/56

# 1 Block diagram

Control logic

SH3NN

SH3NN

SH3NN

SH2NN

SH3NN

S

Figure 1. STDRIVE102BH block diagram

DS14545 - Rev 1 page 3/56

# 2 Device ratings

#### 2.1 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in Table 1 may cause permanent damage to the device. Exposure to maximum rating conditions for extended periods may affect device reliability.

Two separated reference grounds are present in the device: GND and AGND. All voltages reported in Table 1 are considered shorting AGND and GND pins, unless otherwise specified.

Table 1. Absolute maximum ratings

| Symbol                                                                                                                                     | Parameter                                                                                                        | Test condition                                                 | Value                                            | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|------|

| Power supply                                                                                                                               |                                                                                                                  |                                                                |                                                  |      |

| V <sub>M</sub>                                                                                                                             | Motor supply voltage                                                                                             |                                                                | -0.3 to 55                                       | V    |

| Vs                                                                                                                                         | 12 V LDO linear regulator input and main supply                                                                  |                                                                | -0.3 to 55                                       | V    |

| V <sub>CC</sub>                                                                                                                            | 12 V LDO linear regulator output and gate drivers supply voltage                                                 |                                                                | -0.3 to 18                                       | V    |

| V <sub>REGIN_3V3</sub>                                                                                                                     | 3.3 V LDO linear regulator input                                                                                 |                                                                | -0.3 to 18                                       | V    |

| V <sub>DD</sub>                                                                                                                            | 3.3 V LDO linear regulator output and analog front-end supply                                                    |                                                                | -0.3 to 4                                        | V    |

| V <sub>NCAP</sub>                                                                                                                          | Charge pump switching capacitor negative side                                                                    |                                                                | -0.3 to V <sub>S</sub> +0.3                      | V    |

| V <sub>PCAP</sub>                                                                                                                          | Charge pump switching capacitor                                                                                  |                                                                | V <sub>M</sub> -0.3 to V <sub>BOOT</sub> +0.3    | V    |

| VPCAP                                                                                                                                      | positive side                                                                                                    |                                                                | 65                                               | V    |

| V <sub>BOOT</sub>                                                                                                                          | Charge pump output/ high-side boot                                                                               |                                                                | V <sub>M</sub> -0.3 to V <sub>M</sub> +18        | V    |

| <b>▲</b> BOO1                                                                                                                              | supply                                                                                                           |                                                                | 65                                               | V    |

| Gate drivers                                                                                                                               |                                                                                                                  |                                                                |                                                  |      |

|                                                                                                                                            |                                                                                                                  | DC                                                             | -2 to +2                                         | V    |

| V <sub>SLSx</sub>                                                                                                                          | Low-side reference pin voltage                                                                                   | Transient pulse duration 200 ns Repetition frequency 20 kHz    | -8 to +8                                         | V    |

| V <sub>GLSx</sub>                                                                                                                          | Low-side driver's output voltage                                                                                 |                                                                | V <sub>SLSx</sub> -0.3 to V <sub>CC</sub> +0.3   | V    |

| V <sub>GS_LSx</sub>                                                                                                                        | Differential voltage between low-side driver's output and its reference (V <sub>GLSx</sub> - V <sub>SLSx</sub> ) |                                                                | -0.3 to 18                                       | V    |

| V <sub>supply_LS</sub>                                                                                                                     | Supply rail of the low-side driver (V <sub>CC</sub> - $V_{SLSx}$ )                                               |                                                                | -0.3 to 18                                       | V    |

|                                                                                                                                            |                                                                                                                  | DC                                                             | -4 to V <sub>M</sub> +4                          | V    |

| V                                                                                                                                          | OUTunis valtara                                                                                                  | Transient pulse duration between 200 ns and 5 µs               | -8 to V <sub>M</sub> +8                          | V    |

| V <sub>OUTx</sub>                                                                                                                          | OUTx pin voltage                                                                                                 | Repetition frequency 20 kHz                                    |                                                  |      |

|                                                                                                                                            |                                                                                                                  | Transient pulse duration 200 ns<br>Repetition frequency 20 kHz | -10 to V <sub>M</sub> +10                        | V    |

| V <sub>GHSx</sub>                                                                                                                          | High-side driver's output                                                                                        |                                                                | V <sub>OUTx</sub> -0.3 to V <sub>BOOT</sub> +0.3 | V    |

| V <sub>GO_HSx</sub> Differential voltage between high-side gate driver's output and its reference (V <sub>GHSx</sub> - V <sub>OUTx</sub> ) |                                                                                                                  | (2)                                                            | -0.3 to 16                                       | V    |

DS14545 - Rev 1 page 4/56

| Symbol                 | Parameter                                                                    | Test condition                         | Value                        | Unit |

|------------------------|------------------------------------------------------------------------------|----------------------------------------|------------------------------|------|

| V <sub>BO,x</sub>      | Supply rail of the high-side driver (V <sub>BOOT</sub> - V <sub>OUTx</sub> ) |                                        | -0.3 to 65                   | V    |

| Analog pins a          | nd digital I/O                                                               |                                        |                              |      |

| V <sub>IO</sub>        | Logic IO voltage (INHx/INx, INLx/ENx, nSTBY, EN pins)                        |                                        | -0.3 to 5.5                  | V    |

| V <sub>in_analog</sub> | Analog input pins for device configuration (IGATE, TCC, VDSTH)               |                                        | -0.3 to 5.5                  | V    |

| V <sub>OD</sub>        | Open-drain pins voltage (nFAULT, FLAG)                                       |                                        | -0.3 to 5.5                  | V    |

| V <sub>C_IN</sub>      | C_INx input                                                                  |                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>CREF</sub>      | CREF input                                                                   |                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>OA_INxP</sub>   | Operational amplifiers positive inputs                                       |                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>OA_INxN</sub>   | Operational amplifiers negative inputs                                       |                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>OA_Ox</sub>     | Operational amplifiers output                                                |                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Temperature            |                                                                              |                                        |                              |      |

| T <sub>stg</sub>       | Storage temperature                                                          |                                        | -55 to 150                   | °C   |

| Тј                     | Junction temperature                                                         |                                        | -40 to 150                   | °C   |

| Reference gro          | punds                                                                        |                                        |                              |      |

| $\Delta V_{GND}$       | GND misalignment                                                             | AGND with respect to GND (exposed pad) | -0.3 to +0.3                 | V    |

<sup>1.</sup>  $V_{supply\_LS}$  AMR must be also considered.

# 2.2 Recommended operating conditions

All voltages must be considered shorting AGND and GND pins.

Table 2. Recommended operating conditions

| Symbol                 | Parameter                                  | Test condition                            | Min.            | Тур.                             | Max. | Unit |

|------------------------|--------------------------------------------|-------------------------------------------|-----------------|----------------------------------|------|------|

| $V_{M}$                | Motor supply voltage                       |                                           | 6               |                                  | 50   | V    |

| V <sub>S</sub>         | 12 V LDO linear regulator input            | (1)                                       | V <sub>CC</sub> |                                  | 50   | V    |

| Vaa                    | VCC gate drivers' events voltage           | VCC supplied by internal linear regulator |                 | 12                               |      | V    |

| V <sub>CC</sub>        | VCC gate drivers' supply voltage           | VS shorted to VCC and externally supplied | 6               |                                  | 15   | V    |

| Icc                    | 12 V linear regulator output current       | (1) (2)                                   |                 |                                  | 50   | mA   |

| C <sub>VCC</sub>       | 12 V LDO linear regulator output capacitor | (3)                                       |                 | 4.7                              |      | μF   |

| V <sub>BOOT</sub>      | Charge pump output voltage                 |                                           |                 | V <sub>M</sub> + V <sub>CC</sub> |      | V    |

| I <sub>BOOT</sub>      | Charge pump current                        | (2)                                       |                 |                                  | 35   | mA   |

| V <sub>REGIN_3V3</sub> | 3.3 V LDO linear regulator input           |                                           | $V_{DD}$        |                                  | 15   | V    |

| $V_{DD}$               | 3.3 V LDO linear regulator output          | VDD supplied by internal linear regulator |                 | 3.3                              |      | V    |

DS14545 - Rev 1 page 5/56

<sup>2.</sup> Limit to avoid  $V_{GS}$  clamp turn-on.

| Symbol                 | Parameter                                                               | Test condition                                   | Min. | Тур. | Max.                 | Unit |

|------------------------|-------------------------------------------------------------------------|--------------------------------------------------|------|------|----------------------|------|

| $V_{DD}$               | 3.3 V LDO linear regulator output                                       | REGIN_3V3 shorted to VDD and externally supplied | 3.1  | 3.3  | 3.6                  | ٧    |

| I <sub>DD</sub>        | 3.3 V LDO linear regulator output current                               | (1) (2)                                          |      |      | 30                   | mA   |

| C <sub>VDD</sub>       | 3.3 V output capacitor                                                  | (3)                                              |      | 4.7  |                      | μF   |

| $C_LG$                 | Output capacitor for internal logic supply regulator (LGC_CAP pin)      | (3)                                              |      | 4.7  |                      | μF   |

| dV <sub>OUTx</sub> /dt | OUTx slew rate                                                          |                                                  |      |      | 2.5                  | V/ns |

| V <sub>IN,logic</sub>  | Logic input voltage (INHx/INx, INLx/ENx, nSTBY, EN pins)                | (4)                                              | 0    |      | 5                    | V    |

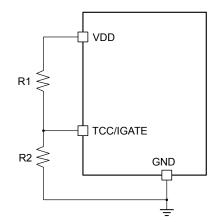

| V <sub>IN,analog</sub> | Analog configuration pins (IGATE, TCC)                                  |                                                  | 0    |      | $V_{DD}$             | V    |

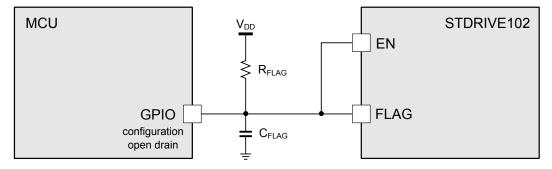

| V <sub>OD</sub>        | nFAULT, FLAG pins pull-up voltage                                       | (4)                                              | 0    |      | 5                    | V    |

| I <sub>OD</sub>        | nFAULT, FLAG pins sink current                                          |                                                  |      |      | 8                    | mA   |

| $V_{DSTH}$             | V <sub>DS</sub> monitoring reference voltage                            | Protection enabled                               | 0.05 |      | 2                    | V    |

| VDSTH                  | V <sub>DS</sub> monitoring reference voltage                            | Protection disabled                              | 3    |      | 3.3                  | V    |

| $V_{SLSx}$             | LSx driver sense pin                                                    |                                                  | -1   |      | +1                   | V    |

| V <sub>OA_INxP</sub>   | Operational amplifiers positive inputs                                  |                                                  | -0.2 |      | V <sub>DD</sub> +0.2 | V    |

| V <sub>OA_INxN</sub>   | Operational amplifiers negative inputs                                  |                                                  | -0.2 |      | V <sub>DD</sub> +0.2 | V    |

| V <sub>OP,icm</sub>    | Input common-mode voltage range                                         |                                                  | -0.2 |      | V <sub>DD</sub> +0.2 | V    |

| R <sub>eqL,out</sub>   | Equivalent load resistor connected to the operational amplifiers output | Resistor to AGND or to VDD                       | 1    |      |                      | kΩ   |

| V <sub>C_IN</sub>      | Comparator input (C_INx pins)                                           |                                                  | 0    |      | $V_{DD}$             | V    |

| V <sub>CREF</sub>      | CREF input                                                              |                                                  | 0    |      | $V_{DD}$             | V    |

| T <sub>amb</sub>       | Operative ambient temperature                                           | (1)                                              | -40  |      | 85                   | °C   |

- 1. Actual operative range can be limited by thermal shutdown.

- 2. Consumption of internal circuitry included.

- 3. An additional 100 nF low-ESR bypass capacitor could be added to improve the noise immunity.

- 4. All digital inputs are compliant with TTL/CMOS thresholds and 5 V tolerant. They can be biased within the respective AMR whatever the supply condition of the device (supplied, floating, or shorted to ground) without causing damage to the device.

DS14545 - Rev 1 page 6/56

#### 2.3 Thermal data

Thermal values are calculated by simulation.

Table 3. STDRIVE102BH thermal data (VFQFPN 48L, 6x6x1 mm)

| Symbol               | Parameter                                         | Test condition                                    | Value | Unit |

|----------------------|---------------------------------------------------|---------------------------------------------------|-------|------|

| R <sub>thJA</sub>    | Junction-to-ambient thermal resistance            | Natural convection according to JESD51-2a         | 32.1  | °C/W |

| R <sub>thJCtop</sub> | Junction-to-case thermal resistance (top side)    | Cold plate on top, according to JESD51-12         | 15.8  | °C/W |

| R <sub>thJCbot</sub> | Junction-to-case thermal resistance (bottom side) | Cold plate on exposed pad, according to JESD51-12 | 3.4   | °C/W |

| R <sub>thJB</sub>    | Junction-to-board thermal resistance              | According to JESD51-8                             | 15.3  | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter        | According to JESD51-2a                            | 0.1   | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter      | According to JESD51-2a                            | 15    | °C/W |

Table 4. STDRIVE102H thermal data (VFQFPN 40L, 5x5x1 mm)

| Symbol               | Parameter                                         | Test condition                                    | Value | Unit |

|----------------------|---------------------------------------------------|---------------------------------------------------|-------|------|

| R <sub>thJA</sub>    | Junction-to-ambient thermal resistance            | Natural convection according to JESD51-2a         | 36.3  | °C/W |

| R <sub>thJCtop</sub> | Junction-to-case thermal resistance (top side)    | Cold plate on top, according to JESD51-12         | 19.5  | °C/W |

| R <sub>thJCbot</sub> | Junction-to-case thermal resistance (bottom side) | Cold plate on exposed pad, according to JESD51-12 | 4.0   | °C/W |

| R <sub>thJB</sub>    | Junction-to-board thermal resistance              | According to JESD51-8                             | 18.0  | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter        | According to JESD51-2a                            | 0.1   | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter      | According to JESD51-2a                            | 17.7  | °C/W |

# 2.4 Electrical sensitivity characteristics

Table 5. ESD protection ratings

| Symbol | Parameter                                                  | Parameter Test condition (                                    |   | Value | Unit |

|--------|------------------------------------------------------------|---------------------------------------------------------------|---|-------|------|

| HBM    | Human Body Model Conforming to ANSI/ESDA/JEDEC JS-001-2017 |                                                               | 2 | 2000  | V    |

| CDM    | Charge Device Model                                        | Charge Device Model Conforming to ANSI/ESDA/JEDEC JS-002-2018 |   | 1000  | V    |

DS14545 - Rev 1 page 7/56

# Electrical characteristics

Testing conditions:  $V_M$  = 24 V,  $V_S$  = 12 V,  $V_{CC}$  = 12 V,  $V_{REGIN\_3V3}$  = 3.3 V,  $V_{DD}$  = 3.3 V,  $V_{DSTH}$  = 3.3 V, all gate drivers LOW (sinking current) unless otherwise specified.

Typical values are tested at  $T_j$  = 25 °C, minimum and maximum values are guaranteed by thermal characterization in the temperature range of -40 to 125 °C, unless otherwise specified.

**Table 6. Electrical characteristics**

| Symbol                    | Parameter Test condition                                   |                                                  |       | Тур. | Max.  | Unit |

|---------------------------|------------------------------------------------------------|--------------------------------------------------|-------|------|-------|------|

| Supply and U              | VLO protection                                             |                                                  |       |      |       |      |

| V <sub>CC(On)</sub>       | V <sub>CC</sub> UVLO turn-on threshold                     | V <sub>CC</sub> rising                           |       | 5.5  | 5.8   | ٧    |

| V <sub>CC(Hyst)</sub>     | V <sub>CC</sub> UVLO hysteresis                            | V <sub>CC</sub> falling                          |       | 0.25 |       | ٧    |

| V <sub>CC(Off)</sub>      | V <sub>CC</sub> UVLO turn-off threshold                    | V <sub>CC</sub> falling                          | 5.0   | 5.25 |       | V    |

| V <sub>P_GOOD(On)</sub>   | V <sub>CC</sub> power-good warning release threshold       | V <sub>CC</sub> rising                           |       | 7.75 |       | ٧    |

| V <sub>P_GOOD(Hyst)</sub> | V <sub>CC</sub> power-good warning hysteresis              | V <sub>CC</sub> falling                          |       | 0.25 |       | ٧    |

| V <sub>P_GOOD(Off)</sub>  | V <sub>CC</sub> power-good warning threshold               | V <sub>CC</sub> falling                          |       | 7.50 |       | V    |

| V <sub>CPump(On)</sub>    | V <sub>BOOT</sub> - V <sub>M</sub> UVLO turn-on threshold  | 'V <sub>BOOT</sub> - V <sub>M</sub> ' rising     |       | 4.5  | 5.2   | ٧    |

| V <sub>CPump(Hyst)</sub>  | V <sub>BOOT</sub> - V <sub>M</sub> UVLO hysteresis         | 'V <sub>BOOT</sub> - V <sub>M</sub> ' falling    |       | 0.2  |       | ٧    |

| V <sub>CPump(Off)</sub>   | V <sub>BOOT</sub> - V <sub>M</sub> UVLO turn-off threshold | 'V <sub>BOOT</sub> - V <sub>M</sub> ' falling    | 3.6   | 4.3  |       | V    |

| V <sub>DD(On)</sub>       | V <sub>DD</sub> UVLO turn-on threshold                     | V <sub>DD</sub> rising                           |       | 2.6  | 2.9   | V    |

| V <sub>DD(Hyst)</sub>     | V <sub>DD</sub> UVLO hysteresis                            | V <sub>DD</sub> falling                          |       | 0.2  |       | ٧    |

| V <sub>DD(Off)</sub>      | V <sub>DD</sub> UVLO turn-off threshold                    | V <sub>DD</sub> falling                          | 2.2   | 2.4  |       | ٧    |

| I <sub>STBY</sub>         | Standby current consumption                                | V <sub>M</sub> = V <sub>S</sub> = 50 V           |       |      | 50    | nA   |

| iSIBA                     | Standby current consumption                                | T <sub>j</sub> = 25 °C                           |       |      | 30    | IIA  |

| 12 V LDO line             | ar regulator                                               |                                                  |       |      |       |      |

| V <sub>CC</sub>           | 12 V linear regulator output                               | $V_S = 15 \text{ V}, I_{CC} = 40 \text{ mA}$     | 11.45 | 12   | 12.55 | V    |

| I <sub>CC,lim</sub>       | 12 V linear regulator current limitation                   | V <sub>CC</sub> shorted to AGND                  | 55    | 85   | 115   | mA   |

| 3.3 V LDO line            | ear regulator                                              |                                                  |       |      |       |      |

| V <sub>DD</sub>           | 3.3 V linear regulator output                              | $V_{REGIN\_3V3} = 12 V$ $I_{DD} = 25 \text{ mA}$ | 3.13  | 3.3  | 3.47  | V    |

| I <sub>DD,lim</sub>       | 3.3 V linear regulator current limit                       | V <sub>DD</sub> shorted to AGND                  | 36    | 45   | 65    | mA   |

| Charge pump               |                                                            |                                                  |       |      |       |      |

| f <sub>SW,CP</sub>        | Charge pump switching frequency                            |                                                  |       | 90   |       | kHz  |

| Thermal shute             | down                                                       |                                                  |       |      |       |      |

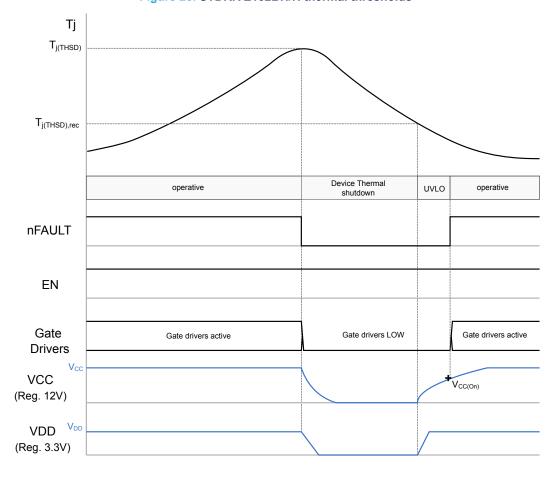

| T <sub>j(THSD),rec</sub>  | Thermal shutdown recovery temperature                      |                                                  |       | 135  |       | °C   |

| T <sub>j(THSD)</sub>      | Thermal shutdown temperature                               |                                                  |       | 150  |       | °C   |

| Gate drivers              |                                                            |                                                  |       |      |       |      |

| I <sub>GATE,on</sub>      | Gate driver source current capability                      | IGATE = V <sub>DD</sub>                          |       | 1000 |       | mA   |

| I <sub>GATE,off</sub>     | Gate driver sink current capability IGATE = $V_{DD}$       |                                                  |       | 2000 |       | mA   |

| I <sub>hold,on</sub>      | Gate driver hold current (source)                          |                                                  |       | 25   |       | mA   |

| I <sub>hold,off</sub>     | Gate driver hold current (sink)                            |                                                  |       | 50   |       | mA   |

DS14545 - Rev 1 page 8/56

Electrical

characteristics

| Symbol                   | Parameter                                                         | Test condition                                     | Min. | Тур. | Max.  | Unit |

|--------------------------|-------------------------------------------------------------------|----------------------------------------------------|------|------|-------|------|

| I <sub>clamp</sub>       | Gate driver clamp current                                         |                                                    |      | 2140 |       | mA   |

|                          |                                                                   | TCC at level 1, see Table 10                       |      | 280  |       | ns   |

| t <sub>cc,on</sub>       | Constant source current time                                      | TCC at level 15, see Table 10                      |      | 4800 |       | ns   |

|                          |                                                                   | TCC at level 1, see Table 10                       |      | 140  |       | ns   |

| t <sub>cc,off</sub>      | Constant sink current time                                        | TCC at level 15, see Table 10                      |      | 2400 |       | ns   |

| V <sub>GS, clamp</sub>   | Clamping voltage protection on the high-side driver's output      | I <sub>GS,clamp</sub> = 25 mA                      |      | 17.5 |       | V    |

| I <sub>OUTx,bias</sub>   | OUTx bias current                                                 | $V_{OUTx} = V_{M} = 40 \text{ V}$ $IGATE = V_{DD}$ |      | 300  |       | μA   |

| t <sub>d,on</sub>        | Turn-on propagation delay (input to output) (1)                   | C <sub>LOAD</sub> = 1 nF, IGATE = V <sub>DD</sub>  |      | 50   |       | ns   |

| t <sub>d,off</sub>       | Turn-off propagation delay (input to output) (1)                  | C <sub>LOAD</sub> = 1 nF, IGATE = V <sub>DD</sub>  |      | 45   |       | ns   |

| MT <sub>on-off</sub>     | Propagation delay matching between turn-on and off <sup>(2)</sup> | C <sub>LOAD</sub> = 1 nF, IGATE = V <sub>DD</sub>  |      | 5    |       | ns   |

| MT <sub>HL</sub>         | Propagation delay matching between HS and LS (3)                  | C <sub>LOAD</sub> = 1 nF, IGATE = V <sub>DD</sub>  |      | 7    |       | ns   |

| MT <sub>CH</sub>         | Propagation delay matching between channels                       | C <sub>LOAD</sub> = 1 nF, IGATE = V <sub>DD</sub>  |      | 0    |       | ns   |

| V <sub>DS</sub> monitori | ng protection                                                     |                                                    |      |      |       |      |

| Vzeu                     | V <sub>DS</sub> monitor protection threshold                      | VDSTH = 0.05 V                                     | 0.02 | 0.05 | 0.083 | V    |

| $V_{DS,th}$              | VDS monitor protection threshold                                  | VDSTH = 2 V                                        | 1.8  | 2    | 2.2   | V    |

| V <sub>DSTH,en</sub>     | V <sub>DS</sub> monitor protection enable voltage                 |                                                    |      |      | 2.4   | V    |

| V <sub>DSTH,dis</sub>    | V <sub>DS</sub> monitor protection disable voltage                |                                                    | 3    |      |       | V    |

| R <sub>PD,VDSTH</sub>    | VDSTH pin pull-down resistor                                      |                                                    |      | 450  |       | kΩ   |

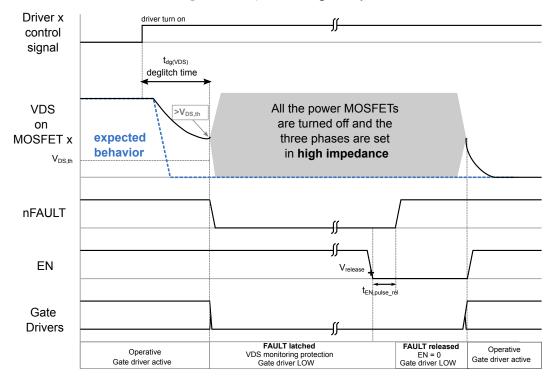

| t <sub>dg(VDS)</sub>     | V <sub>DS</sub> monitor protection deglitch filter time           | TCC short to GND see Table 10                      |      | 3.5  |       | μs   |

| Operational a            | amplifiers                                                        |                                                    |      |      |       |      |

| V <sub>OP,io</sub>       | Input offset voltage                                              |                                                    | -5   | 0    | 5     | mV   |

| I <sub>OP,ib</sub>       | Input bias current                                                | T <sub>j</sub> = 25 °C                             |      |      | 100   | pА   |

| V <sub>OH</sub>          | High level output voltage (V <sub>DD</sub> - V <sub>OA_Ox</sub> ) | Output source current IOA_Ox = +1 mA               |      | 30   | 100   | mV   |

| V <sub>OL</sub>          | Low level output voltage                                          | Output sink current  I <sub>OA_Ox</sub> = -1 mA    |      | 30   | 100   | mV   |

| GBWP                     | Gain bandwidth product                                            | $R_L = 10k\Omega$ , $C_L = 100 pF$                 |      | 12   |       | MHz  |

| _                        |                                                                   | R <sub>L</sub> = 10 kΩ, C <sub>L</sub> = 100 pF    |      |      |       |      |

| SR                       | Slew rate                                                         | Buffer configuration                               |      | 12   |       | V/µs |

| Comparators              |                                                                   |                                                    |      |      |       |      |

| $V_{\text{COMP,io}}$     | Input offset voltage                                              | CREF = 1.65 V                                      | -15  | 0    | 15    | mV   |

| I <sub>CREF</sub>        | CREF pin input current                                            | T <sub>j</sub> = 25 °C                             |      |      | 1     | nA   |

| I <sub>C_IN</sub>        | C_INx pins input current                                          | T <sub>j</sub> = 25 °C (5)                         |      |      | 1     | nA   |

DS14545 - Rev 1 page 9/56

| Symbol                    | Parameter                                           | Test condition          | Min. | Тур.                | Max. | Unit |

|---------------------------|-----------------------------------------------------|-------------------------|------|---------------------|------|------|

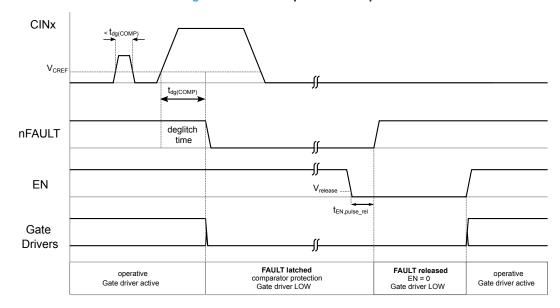

| t <sub>dg(COMP)</sub>     | Comparator deglitch filter time                     |                         |      | 1.3                 |      | μs   |

| Logic inputs              | and outputs                                         |                         |      |                     |      |      |

| $V_{IL}$                  | Low logic input voltage                             |                         |      |                     | 0.8  | V    |

| V <sub>IH</sub>           | High logic input voltage                            |                         | 2    |                     |      | ٧    |

| $V_{IL,stby}$             | nSTBY pin low logic input voltage                   |                         |      |                     | 0.6  | ٧    |

| V <sub>IH,stby</sub>      | nSTBY pin high logic input voltage                  |                         | 2    |                     |      | ٧    |

| $R_{\text{PD,in}}$        | Input lines pull-down resistor (INHx/INx, INLx/ENx) |                         |      | 220                 |      | kΩ   |

| R <sub>PD,STBY</sub>      | nSTBY pin pull-down resistor                        |                         |      | 440                 |      | kΩ   |

| R <sub>PD,EN</sub>        | EN pin pull-down resistor                           |                         |      | 440                 |      | kΩ   |

| $V_{\text{OD,L}}$         | Open-drain output low voltage (nFAULT, FLAG)        | I <sub>OD</sub> = 8 mA  |      |                     | 0.35 | V    |

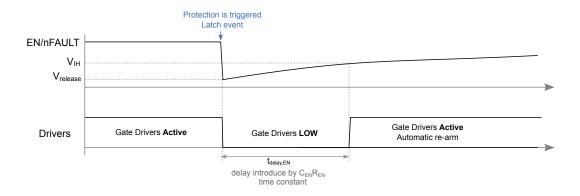

| V <sub>release</sub>      | EN pin latch release threshold                      |                         | 0.37 |                     |      | V    |

| t <sub>EN,pulse_rel</sub> | Latch release time                                  |                         | 400  |                     |      | ns   |

| t <sub>STBY</sub>         | Standby time                                        | From nSTBY falling edge |      |                     | 100  | μs   |

| Analog contr              | ol pins (IGATE and TCC pins)                        |                         |      |                     |      |      |

| $\Delta V_{Actrl,in}$     | Analog intervals                                    |                         |      | V <sub>DD</sub> /15 |      | ٧    |

- 1. Refer to Figure 17, Figure 18, and Figure 19

- 2. The matching time, on the <u>same driver</u>, between the on and off transition is defined as  $|t_{d,on} t_{d,off}|$

- 3. The matching of the same parameter ( $t_{d,on}$  or  $t_{d,off}$ ) between the two drivers (HS and LS) of the same half-bridge is defined as

- $|t_{d,on,HS} t_{d,on,LS}|$  or  $|t_{d,off,HS} t_{d,off,LS}|$ .

- 4. The matching of the same parameter  $(t_{d,on} \text{ or } t_{d,off})$  between the two drivers (HS and LS) of two different half-bridges (channels) "x" and "y" is defined as  $|t_{d,on,HSx} t_{d,on,HSy}|$ ,  $|t_{d,off,HSx} t_{d,off,HSy}|$ ,  $|t_{d,on,LSx} t_{d,on,LSy}|$ ,  $|t_{d,off,LSx} t_{d,off,LSy}|$

- 5. Guaranteed by design.

DS14545 - Rev 1 page 10/56

# 4 Pin description

# 4.1 STDRIVE102BH pin description

LGC\_CAP INH2/IN2 INH3/IN3 VDSTH FLAG 48 37 TCC 36 1 GHS1 **IGATE** EPAD (GND) OUT1 C\_IN1 GHS2 C\_IN2 OUT2 C\_IN3 GHS3 OA\_01 OUT3 OA\_IN1N GLS1 OA\_IN1P SLS1 OA\_02 GLS2 OA\_IN2N SLS2 OA\_IN2P GLS3 AGND 12 25 SLS3 OA\_IN3N OA\_IN3P PCAP NCAP VS CREF VDD REGIN\_3V3 VBOOT

Figure 3. STDRIVE102BH pin description

Table 7. STDRIVE102BH pin list

| Pin N. | Name    | Type       | Function                                                                                 |

|--------|---------|------------|------------------------------------------------------------------------------------------|

| 1      | TCC     | Analog In  | Analog input setting the constant-current time (refer to Section 5.2.1).                 |

| 2      | IGATE   | Analog In  | Analog input setting the gate drivers current (refer to Section 5.2.1).                  |

| 3      | C_IN1   | Analog In  | Non-inverting input of the comparator 1.                                                 |

| 4      | C_IN2   | Analog In  | Non-inverting input of the comparator 2.                                                 |

| 5      | C_IN3   | Analog In  | Non-inverting input of the comparator 3.                                                 |

| 6      | OA_01   | Analog Out | Output of the op amp 1.                                                                  |

| 7      | OA_IN1N | Analog In  | Inverting input of the op amp 1.                                                         |

| 8      | OA_IN1P | Analog In  | Non-inverting input of the op amp 1.                                                     |

| 9      | OA_02   | Analog Out | Output of the op amp 2.                                                                  |

| 10     | OA_IN2N | Analog In  | Inverting input of the op amp 2.                                                         |

| 11     | OA_IN2P | Analog In  | Non-inverting input of the op amp 2.                                                     |

| 12     | AGND    | Power      | Analog ground of the device. Connect this pin to EPAD or a suitable reference GND point. |

| 13     | OA_O3   | Analog Out | Output of the op amp 3.                                                                  |

| 14     | OA_IN3N | Analog In  | Inverting input of the op amp 3.                                                         |

| 15     | OA_IN3P | Analog In  | Non-inverting input of the op amp 3.                                                     |

DS14545 - Rev 1 page 11/56

| Pin N. | Name      | Туре        | Function                                                                                                             |

|--------|-----------|-------------|----------------------------------------------------------------------------------------------------------------------|

| 16     | CREF      | Analog In   | Common reference voltage for the three comparators (inverting input).                                                |

| 17     | VDD       | Power       | 3.3 V LDO linear regulator output and supply voltage of the Analog Front-End (AFE).                                  |

| 18     | REGIN_3V3 | Power       | 3.3 V LDO linear regulator input.                                                                                    |

| 19     | VM        | Power       | Motor supply voltage: reference for the internal charge pump and V <sub>DS</sub> monitoring protection.              |

| 20     | VBOOT     | Power       | Charge pump output voltage: high-side drivers supply.                                                                |

| 21     | PCAP      | Power       | Charge pump fly capacitor positive pin.                                                                              |

| 22     | NCAP      | Power       | Charge pump fly capacitor negative pin.                                                                              |

| 23     | VS        | Power       | Device power supply and 12 V LDO linear regulator input.                                                             |

| 24     | VCC       | Power       | 12 V LDO linear regulator output and supply voltage of the low-side drivers.                                         |

| 25     | SLS3      | Analog      | Phase 3 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 3).                    |

| 26     | GLS3      | Analog      | Phase 3 low-side driver output.                                                                                      |

| 27     | SLS2      | Analog      | Phase 2 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 2).                    |

| 28     | GLS2      | Analog      | Phase 2 low-side driver output.                                                                                      |

| 29     | SLS1      | Analog      | Phase 1 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 1).                    |

| 30     | GLS1      | Analog      | Phase 1 low-side driver output.                                                                                      |

| 31     | OUT3      | Analog      | Phase 3 high-side reference voltage (external half-bridge 3 output).                                                 |

| 32     | GHS3      | Analog      | Phase 3 high-side driver output.                                                                                     |

| 33     | OUT2      | Analog      | Phase 2 high-side reference voltage (external half-bridge 2 output).                                                 |

| 34     | GHS2      | Analog      | Phase 2 high-side driver output.                                                                                     |

| 35     | OUT1      | Analog      | Phase 1 high-side reference voltage (external half-bridge 1 output).                                                 |

| 36     | GHS1      | Analog      | Phase 1 high-side driver output.                                                                                     |

| 37     | FLAG      | Digital Out | Open-drain pin for VCC warning event.                                                                                |

| 38     | VDSTH     | Analog In   | V <sub>DS</sub> monitoring threshold. Internal pull-down.                                                            |

| 39     | INH3/IN3  | Digital In  | Digital control signal for the high-side of the phase 3 or control of the OUT3 voltage level. Internal pull-down.    |

| 40     | INH2/IN2  | Digital In  | Digital control signal for the high-side of the phase 2 or control of the OUT2 voltage level. Internal pull-down.    |

| 41     | INH1/IN1  | Digital In  | Digital control signal for the high-side of the phase 1 or control of the OUT1 voltage level. Internal pull-down.    |

| 42     | INL3/EN3  | Digital In  | Digital control signal for the low-side of the phase 3 or enable of the half-bridge on OUT3. Internal pull-down.     |

| 43     | INL2/EN2  | Digital In  | Digital control signal for the low-side of the phase 2 or enable of the half-bridge on OUT2. Internal pull-down.     |

| 44     | INL1/EN1  | Digital In  | Digital control signal for the low-side of the phase 1 or enable of the half-bridge on OUT1. Internal pull-down.     |

| 45     | nSTBY     | Digital In  | Digital control for the standby mode (active low). Internal pull-down.                                               |

| 46     | LGC_CAP   | Power       | Pin for external bypass capacitor – internal logic supply stabilization (not intended for external supply purposes). |

| 47     | EN        | Digital In  | Drivers enable with "FAULT release" feature. Internal pull-down.                                                     |

| 48     | nFAULT    | Digital Out | Open-drain pin to signal failure/protection events.                                                                  |

| EPAD   | GND       | Power       | Ground.                                                                                                              |

DS14545 - Rev 1 page 12/56

# 4.2 STDRIVE102H pin description

LGC\_CAP INL2/EN2 INL3/EN3 INH2/IN2 INH3/IN3 INL1/EN1 GHS1 31 OUT1 ΕN 1 30 nFAULT GHS2 EPAD (GND) TCC OUT2 **IGATE** GHS3 C\_IN1 OUT3 C\_IN2 GLS1 OA\_O SLS1 OA\_INN GLS2 OA\_INP SLS2 21 AGND 10 GLS3 2 PCAP NCAP VBOOT REGIN\_3V3

Figure 4. STDRIVE102H pin description

Table 8. STDRIVE102H pin list

| Pin N. | Name      | Туре        | Function                                                                                                |  |  |

|--------|-----------|-------------|---------------------------------------------------------------------------------------------------------|--|--|

| 1      | EN        | Digital In  | Drivers enable with "FAULT release" feature. Internal pull-down.                                        |  |  |

| 2      | nFAULT    | Digital Out | Open-drain pin to signal failure/protection events.                                                     |  |  |

| 3      | TCC       | Analog In   | Analog setting for the constant-current time (refer to Section 5.2.1).                                  |  |  |

| 4      | IGATE     | Analog In   | Analog setting for the gate drivers current (refer to Section 5.2.1).                                   |  |  |

| 5      | C_IN1     | Analog In   | Non-inverting input of the comparator 1.                                                                |  |  |

| 6      | C_IN2     | Analog In   | Non-inverting input of the comparator 2.                                                                |  |  |

| 7      | OA_O      | Analog Out  | Output of the op amp.                                                                                   |  |  |

| 8      | OA_INN    | Analog In   | Inverting input of the op amp.                                                                          |  |  |

| 9      | OA_INP    | Analog In   | Non-inverting input of the op amp.                                                                      |  |  |

| 10     | AGND      | Power       | Analog ground of the device. Connect this pin to EPAD or a suitable reference GND point.                |  |  |

| 11     | CREF      | Analog In   | Common reference voltage for the two comparators (inverting input).                                     |  |  |

| 12     | VDD       | Power       | 3.3 V LDO linear regulator output and supply voltage of the Analog Front-End (AFE).                     |  |  |

| 13     | REGIN_3V3 | Power       | 3.3 V LDO linear regulator input.                                                                       |  |  |

| 14     | VM        | Power       | Motor supply voltage: reference for the internal charge pump and $V_{\text{DS}}$ monitoring protection. |  |  |

| 15     | VBOOT     | Power       | Charge pump output voltage: high-side drivers supply.                                                   |  |  |

| 16     | PCAP      | Power       | Charge pump fly capacitor positive pin.                                                                 |  |  |

| 17     | NCAP      | Power       | Charge pump fly capacitor negative pin.                                                                 |  |  |

| 18     | VS        | Power       | Device power supply and 12 V LDO linear regulator input.                                                |  |  |

| 19     | VCC       | Power       | 12 V LDO linear regulator output and supply voltage of the low-side drivers                             |  |  |

DS14545 - Rev 1 page 13/56

| Pin N. | Name     | Type       | Function                                                                                                             |  |  |  |

|--------|----------|------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| 20     | SLS3     | Analog     | Phase 3 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 3).                    |  |  |  |

| 21     | GLS3     | Analog     | hase 3 low-side driver output.                                                                                       |  |  |  |

| 22     | SLS2     | Analog     | Phase 2 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 2).                    |  |  |  |

| 23     | GLS2     | Analog     | Phase 2 low-side driver output.                                                                                      |  |  |  |

| 24     | SLS1     | Analog     | Phase 1 low-side reference voltage (source of the external low-side MOSFET in the half-bridge 1).                    |  |  |  |

| 25     | GLS1     | Analog     | Phase 1 low-side driver output.                                                                                      |  |  |  |

| 26     | OUT3     | Analog     | Phase 3 high-side reference voltage (external half-bridge 3 output).                                                 |  |  |  |

| 27     | GHS3     | Analog     | Phase 3 high-side driver output.                                                                                     |  |  |  |

| 28     | OUT2     | Analog     | Phase 2 high-side reference voltage (external half-bridge 2 output).                                                 |  |  |  |

| 29     | GHS2     | Analog     | Phase 2 high-side driver output.                                                                                     |  |  |  |

| 30     | OUT1     | Analog     | Phase 1 high-side reference voltage (external half-bridge 1 output).                                                 |  |  |  |

| 31     | GHS1     | Analog     | Phase 1 high-side driver output.                                                                                     |  |  |  |

| 32     | VDSTH    | Analog In  | V <sub>DS</sub> monitoring threshold. Internal pull-down.                                                            |  |  |  |

| 33     | INH3/IN3 | Digital In | Digital control signal for the high-side of the phase 3 or control of the OUT3 voltage level. Internal pull-down.    |  |  |  |

| 34     | INH2/IN2 | Digital In | Digital control signal for the high-side of the phase 2 or control of the OUT2 voltage level. Internal pull-down.    |  |  |  |

| 35     | INH1/IN1 | Digital In | Digital control signal for the high-side of the phase 1 or control of the OUT1 voltage level. Internal pull-down.    |  |  |  |

| 36     | INL3/EN3 | Digital In | Digital control signal for the low-side of the phase 3 or enable of the half-bridge on OUT3. Internal pull-down.     |  |  |  |

| 37     | INL2/EN2 | Digital In | Digital control signal for the low-side of the phase 2 or enable of the half-bridge on OUT2. Internal pull-down.     |  |  |  |

| 38     | INL1/EN1 | Digital In | Digital control signal for the low-side of the phase 1 or enable of the half-bridge on OUT1. Internal pull-down.     |  |  |  |

| 39     | nSTBY    | Digital In | Digital control for the standby mode (active low). Internal pull-down.                                               |  |  |  |

| 40     | LGC_CAP  | Power      | Pin for external bypass capacitor – internal logic supply stabilization (not intended for external supply purposes). |  |  |  |

| EPAD   | GND      | Power      | Ground.                                                                                                              |  |  |  |

DS14545 - Rev 1 page 14/56

# 5 Device description

The STDRIVE102BH and the STDRIVE102H are triple half-bridge gate drivers suitable for 3-phase brushless motor driving. From now on the naming convention STDRIVE102BH/H is adopted to indicate indistinctly one or the other.

#### 5.1 Power management section

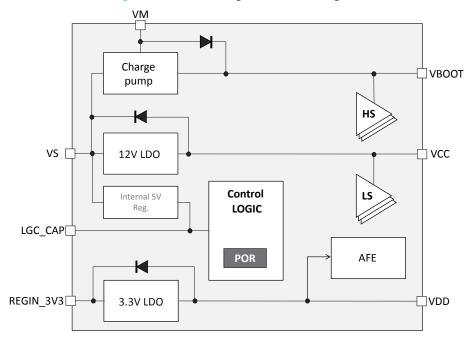

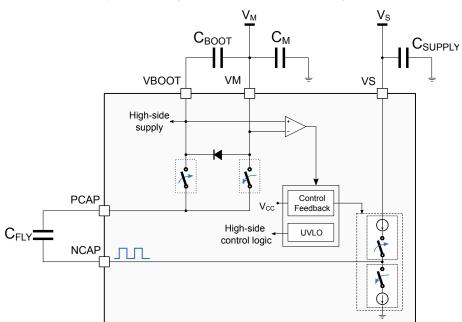

The power management section of the STDRIVE102BH/H (Figure 5) is composed by:

- One LDO linear regulator with 12 V output; it is used to generate the VCC for the gate drivers' supply. Its input VS can be connected to VM or to an external voltage (up to 50 V operative).

- One LDO linear regulator, which generates the 3.3 V supply (VDD). Its input REGIN\_3V3 ranges between 3.6 V and 15 V. It can also be connected to the VCC or be fed by an external supply.

- One internal regulator, which supplies the STDRIVE102BH/H control logic at 5 V. This voltage is for internal use only: no external load or circuitry can be connected to the LGC\_CAP pin, which must be used only to connect an external decoupling capacitor (low-ESR ceramic, 4.7 μF / 16 V). This capacitor stabilizes all the internal control circuits, including the power-on reset (POR).

- A charge pump, supplied by VS and referenced to VM, which generates the VBOOT supply rail for the high side gate drivers.

Figure 5. Power management block diagram

DS14545 - Rev 1 page 15/56

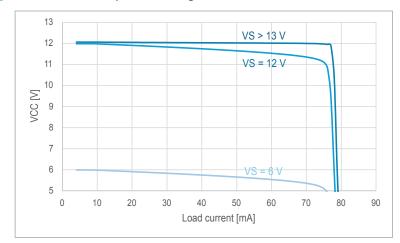

#### 5.1.1 12 V LDO linear regulator

This regulator generates the voltage on the VCC pin, which is the supply of the low-side gate drivers and the set point for the  ${}^{\prime}V_{BOOT}$  -  ${}^{\prime}V_{M}$  voltage provided by the charge pump (refer to Section 5.1.3). A low ESR ceramic capacitor of 4.7  $\mu$ F, 25 V must be placed as close as possible to the VCC pin, to ensure the stability of the  ${}^{\prime}V_{CC}$  and support the currents required by the low-side gate drivers.

In addition, external loads can be connected to VCC pin, taking care to stay within the operating range. The output current of the regulator is limited at I<sub>CC,lim</sub> protecting it against short circuit and overload. The overall consumption of the external loads plus the drivers must be smaller than this current limitation.

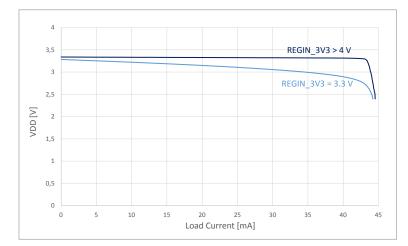

Figure 6. 12 V LDO output according to the current load at different VS input

The linear regulator input is connected to the main supply VS. The regulator can be bypassed by connecting the VCC and the VS together and forcing an external voltage equal to the target VCC value, which must be in any case within the operative range of the VCC pin.

The regulator is disabled in standby mode in order to reduce the current consumption.

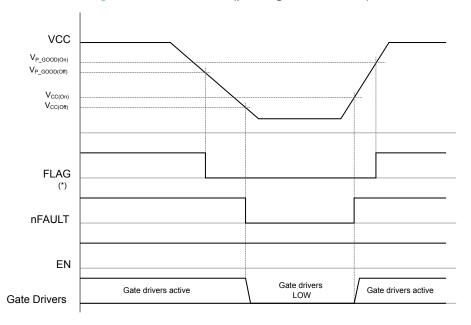

In case the VCC voltage falls below the UVLO threshold ( $V_{CC(Off)}$ ), the gate drivers turn off all the external MOSFETs, forcing the power stage into a safe condition. Concurrently, the nFAULT open-drain pin is forced low to signal that the UVLO protection has been triggered. As soon as the VCC voltage rises above the  $V_{CC(On)}$  threshold, the nFAULT is released and the drivers return to an active condition, according to the status of the digital inputs.

In the STDRIVE102BH only when the VCC voltage falls below the "power-good" threshold ( $V_{P\_GOOD(Off)}$ ), the FLAG open-drain pin is forced low, but there are no other effects on the functional blocks of the devices. The FLAG pin is then released as soon as the VCC voltage rises above the  $V_{P\_GOOD(On)}$  threshold.

An example of the V<sub>CC</sub> thresholds management is shown in Figure 7.

DS14545 - Rev 1 page 16/56

Figure 7. V<sub>CC</sub> thresholds (power-good and UVLO)

Note: (\*) The FLAG pin is available only in the STDRIVE102BH.

#### 5.1.2 3.3 V LDO linear regulator

The device integrates a 3.3 V regulator, which supplies the embedded analog front-end (AFE). In addition, external loads can be connected to the VDD pin, taking care to stay within the operating range. It is recommended to place a low ESR ceramic capacitor of 4.7  $\mu$ F 16 V as close as possible to the VDD pin, to guarantee the stability of the VDD voltage.

The output current of the regulator is limited at  $I_{DD,lim}$ , protecting it against short-circuit and overload. The overall consumption of the external loads plus the AFE must be smaller than this current limitation.

Figure 8. 3.3 V LDO output according to the current load at different REGIN 3V3 input

The regulator is disabled in standby mode in order to reduce the current consumption.

The regulator can be bypassed by connecting the VDD and the REGIN\_3V3 pins together and forcing externally a voltage equal to the target VDD value, and in any case within the operative range of the VDD pin.

The 3.3 V regulator has a dedicated UVLO protection. The UVLO helps to avoid unexpected behavior related to all the circuitries supplied by the VDD, in particular it avoids spurious events coming from the AFE comparators and unstable sampling of the TCC and/or IGATE pins.

DS14545 - Rev 1 page 17/56

In case of UVLO condition (VDD falls below the  $V_{DD(off)}$  threshold), the drivers turn off all the external MOSFETs, forcing the power stage into a safe condition. Concurrently, the nFAULT open-drain pin is forced low. As soon as the VDD voltage rises above the  $V_{DD(On)}$  threshold, the nFAULT is released and the drivers return to an active condition, depending on the status of the digital inputs.

#### 5.1.3 Charge pump

The embedded charge pump supplies the high-side gate drivers and ensures an unlimited on-time of the high-side MOSFETs and a PWM duty cycle of 100%.

Figure 9. Charge pump simplified block diagram

The charge pump is supplied directly by the VS pin and generates the voltage  $V_{BOOT}$  referenced to the motor supply  $V_M$ . The  $V_{BOOT}$  is the supply of the three high-side gate drivers and it must be greater than  $V_M$  to properly turn on the high-side MOSFETs. The internal feedback circuit of the charge pump tracks the value of the voltage on the VCC pin and regulates the  $V_{BOOT}$  to be equal to  $V_M + V_{CC}$ . In this way, both the low-side and the high-side MOSFETs are driven with the same  $V_{GS}$ , thus ensuring a more balanced behavior of the power stage.

The circuit on the NCAP pin charges the capacitor  $C_{FLY}$ ; the charge is then transferred to the  $C_{BOOT}$  capacitor through the PCAP pin. The amount of charge stored in the  $C_{FLY}$  capacitor is controlled by the internal feedback, in order to meet the target voltage on VBOOT pin.

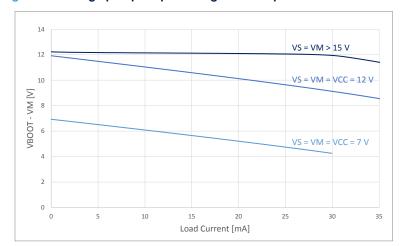

The drop between the target value of  $V_{BOOT}$  and its actual value depends on the voltage on the VS pin and the average load current required by the high-side drivers. The drop increases for lower  $V_S$  and higher current load. Figure 10 shows the charge pump output voltage with respect to the load current at  $T_{amb}$  = 25 °C, using the recommended values for  $C_{FLY}$  = 220 nF and  $C_{BOOT}$  = 1  $\mu$ F.

The pulsed current required by the high-side drivers is provided by the  $C_{BOOT}$  capacitor. This capacitor should be sized according to the maximum allowed ripple and total gate charge of the external MOSFETs. A ceramic low ESR capacitor of the same value of  $C_{BOOT}$  must be placed close to the VM pin and the exposed pad (GND) of the STDRIVE102BH/H.

The high-side drivers are connected to VBOOT by an internal connection: for no reason can other external loads be connected to the VBOOT pin. The VBOOT pin is referred to the VM pin: any external event forcing a  $V_{BOOT}$  -  $V_{M}$  voltage below the limit reported in Table 1. Absolute maximum ratings, results in the device breakdown.

In case of undervoltage (' $V_{BOOT}$  -  $V_{M}$ ' <  $V_{CPump(Off)}$ ), the UVLO protection turns off the high-side MOSFETs, while the low-side drivers keep on operating. The high-side drivers return operative when ' $V_{BOOT}$  -  $V_{M}$ ' >  $V_{CPump(On)}$ .

DS14545 - Rev 1 page 18/56

Figure 10. Charge pump output voltage with respect to the load current

#### 5.2 Gate drivers

The gate drivers use a constant-current approach enabling the following advantages:

- No external components are required between the MOSFETs' gates and the drivers.

- The slew rate of the half-bridge outputs is better controlled.

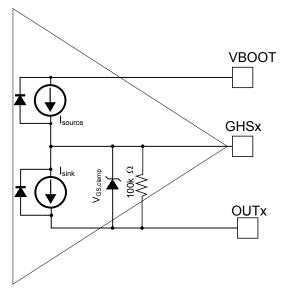

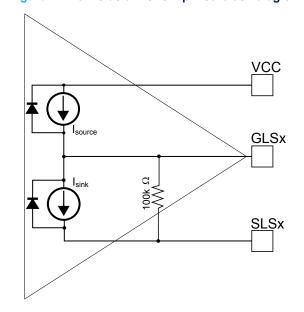

The high-side drivers (Figure 11) and the low-side drivers (Figure 12) have a similar structure:

- A reference pin for the low level (OUTx for the high-side and SLSx for the low-side).

- The output pin (GHSx for the high-side or GLSx for the low-side), which directly drives the external MOSFET's gate.

- The supply pin (VBOOT in common to the three high side drivers and VCC in common to the three low side drivers)

When the driver is not operative (for example, in standby mode or for very low supply), an equivalent 100 k $\Omega$  resistor keeps the external MOSFETs off. In normal conditions, the gate driver must force a voltage on the gate of its respective MOSFET, in order to keep it in a well-defined state. This datasheet adopts the following definitions:

- Setting <u>HIGH</u> the gate driver means that the driver sources a controlled current to increase the V<sub>GS</sub> of the MOSFET and turn it on. The gate current comes from the supply VCC in case of the low-side driver or from VBOOT in case of the high-side driver.

- Setting <u>LOW</u> the gate driver means that the driver sinks a controlled current from the gate of the MOSFET to turn it off. The sink circuitry of the driver is referred to the OUTx pin for the high-side, and to the SLSx pin for the low-side. This approach ensures that the MOSFET is kept off, even in the presence of below-GND transients

In normal mode operation, when a high-side driver is set HIGH, the voltage on the GHSx pin increases up to its target level  $V_{BOOT}$ . At the same time the OUTx voltage increases up to  $V_{M}$ , so that the  $V_{GS}$  of the external MOSFET is kept under control (less or equal to  $V_{CC}$ ). In case the OUTx pin cannot follow the GHSx pin, the gate driver protects the gate of the external MOSFET from breakdown clamping the  $V_{GS}$  at  $V_{GS, clamp}$ .

The six gate drivers (three low-side and three high-side) are controlled by six digital inputs, INH1/IN1, INH2/IN2, INH3/IN3, INL1/EN1, INL2/EN2, INL3/EN3. Each digital input has an internal pull-down resistor R<sub>PD,in</sub>. Each half-bridge (driven by a low-side driver and a high-side driver) is controlled by a couple of inputs: for example, INH1/IN1 and INL1/EN1 refer to half-bridge 1. The label INHx/INx or INLx/ENx can be used to indicate one of the three half-bridges, with no specific reference to a particular channel. Note that the terms "channel" or "phase" could be used similarly to refer to the half-bridge output.

DS14545 - Rev 1 page 19/56

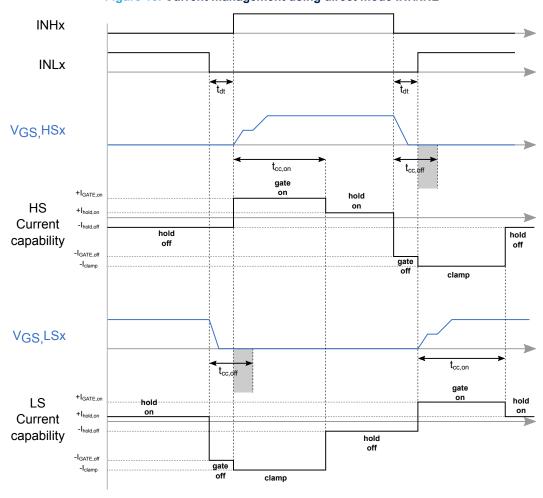

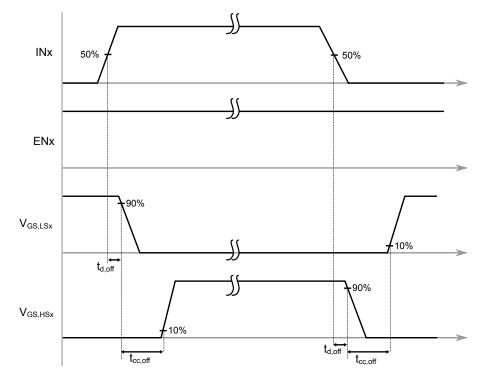

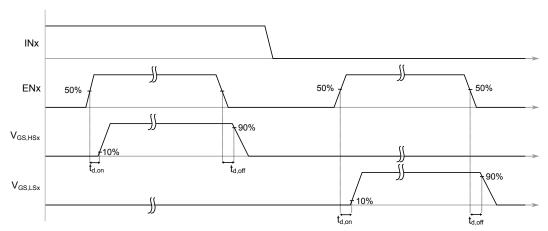

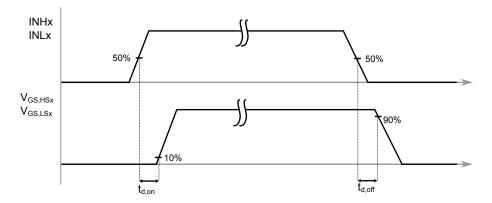

The STDRIVE102BH/H implements two control modes: the enable/input mode (EN/IN) or the direct mode (INH/INL), respectively explained in Section 5.2.1.1 and Section 5.2.1.2. The digital inputs assume a different function according to the input mode selected:

- In case the device is configured in Enable/Input mode:

- INHx/INx  $\rightarrow$  INx

- INLx/ENx  $\rightarrow$  ENx

- In case the device is configured in Direct mode:

- INHx/INx  $\rightarrow$  INHx

- INLx/ENx → INLx

In addition to the six digital inputs mentioned above, another digital input named EN (pin 47 for the STDRIVE102BH and pin 1 for the STDRIVE102H) is used as general enable: in case it is forced to 0, all the six gate drivers are set LOW, turning off all the external power MOSFETs. Setting EN to 1 activates the gate drivers, which behave according to their related digital inputs. The EN pin also integrates an analog threshold  $V_{release}$ , to release the latched condition after a FAULT event (refer to Section 5.6.1).

Figure 11. High-side driver simplified block diagram

Figure 12. Low-side driver simplified block diagram

DS14545 - Rev 1 page 20/56

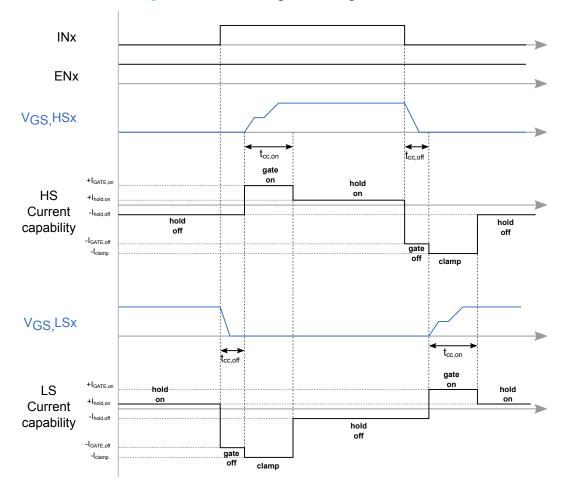

#### 5.2.1 Driving current management

The gate driver turns on the respective MOSFET by sourcing the programmed current  $I_{GATE,on}$  for a time equal to the programmed  $t_{cc,on}$  time. After this time, the MOSFET's gate should be completely charged, so the driver reduces the source current to a holding value  $I_{hold,on}$ .

The gate driver turns off the respective MOSFET by sinking the programmed current  $I_{GATE,off}$  for a time equal to the programmed  $t_{cc,off}$  time. After this time, the MOSFET's gate should be completely discharged, so the driver reduces the sink current to a holding value  $I_{hold,off}$ .

To avoid induced turn-on effects, during the turn-on phase of a MOSFET (that is, when a driver is forcing  $I_{GATE,on}$ ) the complementary driver sinks the maximum available current  $I_{clamp}$  for the entire  $t_{cc,on}$  duration.

Note that the current capability is the maximum current that the driver is able to source/sink: when the gate of the external MOSFET is completely charged/discharged the driver is no longer able to source/sink current.

The current levels can be summarized as below:

- The value of the source current and the sink current is set by the analog voltage on IGATE input (see Table 9).

- The I<sub>hold.on</sub> current is 25 mA typical value.

- The I<sub>hold off</sub> current is 50 mA typical value.

- The I<sub>clamp</sub> current is 2140 mA typical value.

Table 9. Programmable gate current typical values

| IGATE level<br>refer to Table 11 | I <sub>GATE,on</sub> (source)<br>[mA] | I <sub>GATE,off</sub> (sink)<br>[mA] |

|----------------------------------|---------------------------------------|--------------------------------------|

| 0 (GND)                          | 25                                    | 50                                   |

|                                  |                                       |                                      |

| 1                                | 75                                    | 150                                  |

| 2                                | 150                                   | 300                                  |

| 3                                | 250                                   | 500                                  |

| 4                                | 300                                   | 600                                  |

| 5                                | 350                                   | 700                                  |

| 6                                | 400                                   | 800                                  |

| 7                                | 500                                   | 1000                                 |

| 8                                | 550                                   | 1100                                 |

| 9                                | 600                                   | 1200                                 |

| 10                               | 650                                   | 1300                                 |

| 11                               | 700                                   | 1400                                 |

| 12                               | 800                                   | 1600                                 |

| 13                               | 850                                   | 1700                                 |

| 14                               | 900                                   | 1800                                 |

| 15 (VDD)                         | 1000                                  | 2000                                 |

The turn-on and turn-off timings (respectively  $t_{cc,on}$  and a  $t_{cc,off}$ ) are set by the voltage on TCC input (see Table 10).

Moreover, the input mode and the deglitch filter time of the  $V_{DS}$  monitoring protection ( $t_{dg(VDS)}$ ) are adjusted according to the configuration of the TCC (see Section 5.2.3).

DS14545 - Rev 1 page 21/56

15 (VDD)

| TCC level<br>refer to Table 11 | Input mode                                 | t <sub>cc,on</sub><br>[ns] | t <sub>cc,off</sub><br>[ns] | t <sub>dg[VDS]</sub><br>[µs] |

|--------------------------------|--------------------------------------------|----------------------------|-----------------------------|------------------------------|

| 0 (GND)                        | INH/INL mode<br>(refer to Section 5.2.1.2) | 2240                       | 1120                        | 3.5                          |

| 1                              |                                            | 280                        | 140                         | 3.5                          |

| 2                              |                                            | 560                        | 280                         | 3.5                          |

| 3                              |                                            | 840                        | 420                         | 3.5                          |

| 4                              |                                            | 1120                       | 560                         | 3.5                          |

| 5                              |                                            | 1400                       | 700                         | 3.5                          |

| 6                              |                                            | 1680                       | 840                         | 3.5                          |

| 7                              | EN/IN mode (refer to Section 5.2.1.1)      | 1960                       | 980                         | 3.5                          |

| 8                              |                                            | 2240                       | 1120                        | 3.5                          |

| 9                              | (refer to Section 3.2.1.1)                 | 2520                       | 1260                        | 4.5                          |

| 10                             |                                            | 2800                       | 1400                        | 4.5                          |

| 11                             |                                            | 3080                       | 1540                        | 4.5                          |

Table 10. Programmable constant-current time (TCC) typical values